Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                             |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 3.5KB (2K x 14)                                                              |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | 128 x 8                                                                      |

| RAM Size                   | 128 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 20-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lce625-04i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.0 MEMORY ORGANIZATION

### 4.1 <u>Program Memory Organization</u>

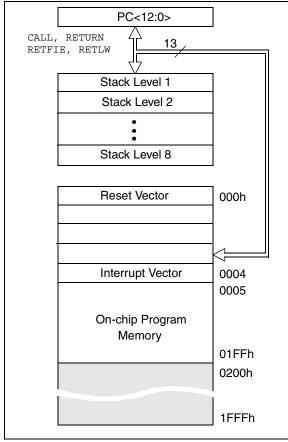

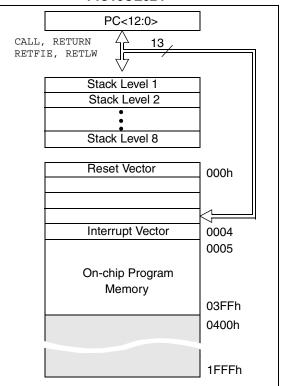

The PIC16CE62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16CE623, 1K x 14 (0000h - 03FFh) for the PIC16CE624 and 2K x 14 (0000h - 07FFh) for the PIC16CE625 are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 space (PIC16CE623) or 1K x 14 space (PIC16CE624) or 2K x 14 space (PIC16CE625). The reset vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2, Figure 4-3).

### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16CE623

### FIGURE 4-2: PROGRAM MEMORY MAP AND STACK FOR THE PIC16CE624

### FIGURE 4-3: PROGRAM MEMORY MAP AND STACK FOR THE PIC16CE625

### 4.2 Data Memory Organization

The data memory (Figure 4-4 and Figure 4-5) is partitioned into two Banks which contain the General Purpose Registers and the Special Function Registers. Bank 0 is selected when the RP0 bit is cleared. Bank 1 is selected when the RP0 bit (STATUS <5>) is set. The Special Function Registers are located in the first 32 locations of each Bank. Register locations 20-7Fh (Bank0) on the PIC16CE623/624 and 20-7Fh (Bank0) and A0-BFh (Bank1) on the PIC16CE625 are General Purpose Registers implemented as static RAM. Some special purpose registers are mapped in Bank 1. In all three microcontrollers, address space F0h-FFh (Bank1) is mapped to 70-7Fh (Bank0) as common RAM.

### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $96 \times 8$  in the PIC16CE623/624 and 128 x 8 in the PIC16CE625. Each is accessed either directly or indirectly through the File Select Register FSR (Section 4.4).

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (Table 4-1). These registers are static RAM. The special registers can be classified into two sets (core and peripheral). The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address | Name          | Bit 7                  | Bit 6              | Bit 5       | Bit 4         | Bit 3        | Bit 2        | Bit 1        | Bit 0      | Value on<br>POR Reset | Value on all<br>other<br>resets <sup>(1)</sup> |

|---------|---------------|------------------------|--------------------|-------------|---------------|--------------|--------------|--------------|------------|-----------------------|------------------------------------------------|

| Bank 0  |               |                        |                    |             |               |              |              |              |            |                       |                                                |

| 00h     | INDF          | Addressin<br>register) | ig this locat      | ion uses co | ontents of F  | SR to addre  | ess data me  | emory (not a | a physical | xxxx xxxx             | xxxx xxxx                                      |

| 01h     | TMR0          | Timer0 M               | odule's Reg        | jister      |               |              |              |              |            | xxxx xxxx             | uuuu uuuu                                      |

| 02h     | PCL           | Program (              | Counter's (F       | PC) Least S | Significant B | yte          |              |              |            | 0000 0000             | 0000 0000                                      |

| 03h     | STATUS        | IRP <sup>(2)</sup>     | RP1 <sup>(2)</sup> | RP0         | TO            | PD           | Z            | DC           | С          | 0001 1xxx             | 000q quuu                                      |

| 04h     | FSR           | Indirect da            | ata memory         | address p   | ointer        |              | I            |              | I          | xxxx xxxx             | uuuu uuuu                                      |

| 05h     | PORTA         |                        |                    |             | RA4           | RA3          | RA2          | RA1          | RA0        | x 0000                | u 0000                                         |

| 06h     | PORTB         | RB7                    | RB6                | RB5         | RB4           | RB3          | RB2          | RB1          | RB0        | xxxx xxxx             | uuuu uuuu                                      |

| 07h     | Unimplemented |                        | 1                  |             | 1             |              | 1            |              | 1          | -                     | -                                              |

| 08h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | _                                              |

| 09h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | _                                              |

| 0Ah     | PCLATH        | _                      |                    | _           | Write buff    | er for upper | 5 bits of pr | ogram cou    | nter       | 0 0000                | 0 0000                                         |

| 0Bh     | INTCON        | GIE                    | PEIE               | TOIE        | INTE          | RBIE         | TOIF         | INTF         | RBIF       | 0000 000x             | 0000 000u                                      |

| 0Ch     | PIR1          | —                      | CMIF               | —           | —             | —            | —            | —            | —          | -0                    | -0                                             |

| 0Dh-1Eh | Unimplemented |                        |                    |             |               |              |              |              |            | —                     | _                                              |

| 1Fh     | CMCON         | C2OUT                  | C10UT              | _           |               | CIS          | CM2          | CM1          | CM0        | 00 0000               | 00 0000                                        |

| Bank 1  |               |                        |                    |             |               |              |              |              |            |                       |                                                |

| 80h     | INDF          | Addressin<br>register) | ig this locat      | ion uses co | ontents of F  | SR to addre  | ess data me  | emory (not a | a physical | xxxx xxxx             | xxxx xxxx                                      |

| 81h     | OPTION        | RBPU                   | INTEDG             | TOCS        | T0SE          | PSA          | PS2          | PS1          | PS0        | 1111 1111             | 1111 1111                                      |

| 82h     | PCL           | Program (              | Counter's (F       | PC) Least S | Significant B | yte          | 1            |              | 1          | 0000 0000             | 0000 0000                                      |

| 83h     | STATUS        | IRP                    | RP1                | RP0         | TO            | PD           | Z            | DC           | С          | 0001 1xxx             | 000q quuu                                      |

| 84h     | FSR           | Indirect da            | ata memory         | address p   | ointer        |              | 1            |              | 1          | xxxx xxxx             | uuuu uuuu                                      |

| 85h     | TRISA         | _                      |                    |             | TRISA4        | TRISA3       | TRISA2       | TRISA1       | TRISA0     | 1 1111                | 1 1111                                         |

| 86h     | TRISB         | TRISB7                 | TRISB6             | TRISB5      | TRISB4        | TRISB3       | TRISB2       | TRISB1       | TRISB0     | 1111 1111             | 1111 1111                                      |

| 87h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 88h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 89h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 8Ah     | PCLATH        | _                      |                    | _           | Write buff    | er for upper | 5 bits of pr | ogram cou    | nter       | 0 0000                | 0 0000                                         |

| 8Bh     | INTCON        | GIE                    | PEIE               | TOIE        | INTE          | RBIE         | TOIF         | INTF         | RBIF       | 0000 000x             | 0000 000u                                      |

| 8Ch     | PIE1          | _                      | CMIE               | _           | —             | _            | —            | _            | —          | -0                    | -0                                             |

| 8Dh     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 8Eh     | PCON          | —                      | —                  | —           | _             | —            | —            | POR          | BOD        | 0x                    | uq                                             |

| 8Fh-9Eh | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 90h     | EEINTF        | —                      | —                  | —           | _             | —            | EESCL        | EESDA        | EEVDD      | 111                   | 111                                            |

| 9Fh     | VRCON         | VREN                   | VROE               | VRR         | _             | VR3          | VR2          | VR1          | VR0        | 000- 0000             | 000- 0000                                      |

### TABLE 4-1: SPECIAL REGISTERS FOR THE PIC16CE62X

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: Other (non power-up) resets include MCLR reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

Note 2: IRP & RPI bits are reserved; always maintain these bits clear.

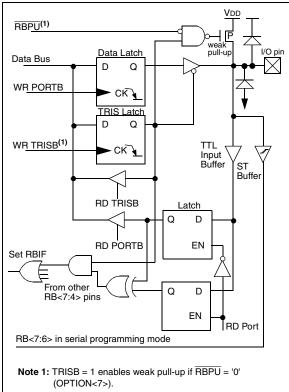

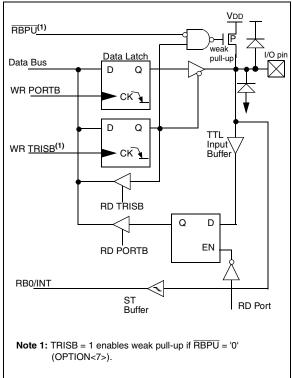

### 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a high impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

Reading PORTB register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A$  typical). A single control bit can turn on all the pull-ups. This is done by clearing the  $\overline{RBPU}$  (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB<7:4>, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupt on change comparison). The input pins of RB<7:4> are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552, "Implementing Wake-Up on Key Strokes".)

| Note: | If a change on the I/O pin should occur       |

|-------|-----------------------------------------------|

|       | when the read operation is being executed     |

|       | (start of the Q2 cycle), then the RBIF inter- |

|       | rupt flag may not get set.                    |

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 7-1) must be executed when changing the prescaler assignment from Timer0 to WDT.

# EXAMPLE 7-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| 1.BCF    | STATUS, RPO | ;Skip if already in      |

|----------|-------------|--------------------------|

|          |             | ; Bank 0                 |

| 2.CLRWDT |             | ;Clear WDT               |

| 3.CLRF   | TMR0        | ;Clear TMR0 & Prescaler  |

| 4.BSF    | STATUS, RPO | ;Bank 1                  |

| 5.MOVLW  | '00101111'b | ;These 3 lines (5, 6, 7) |

| 6.MOVWF  | OPTION      | ; are required only if   |

|          |             | ; desired PS<2:0> are    |

| 7.CLRWDT |             | ; 000 or 001             |

| 8.MOVLW  | '00101xxx'b | ;Set Postscaler to       |

| 9.MOVWF  | OPTION      | ; desired WDT rate       |

| 10.BCF   | STATUS, RPO | ;Return to Bank 0        |

|          |             |                          |

To change prescaler from the WDT to the TMR0 module, use the sequence shown in Example 7-2. This precaution must be taken even if the WDT is disabled.

# EXAMPLE 7-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and<br>;prescaler |

|--------|-------------|------------------------------|

|        |             | /prebearer                   |

| BSF    | STATUS, RPO |                              |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new            |

|        |             | ;prescale value and          |

|        |             | ;clock source                |

| MOVWF  | OPTION_REG  |                              |

| BCF    | STATUS, RPO |                              |

### TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7  | Bit 6                  | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR | Value on<br>All Other<br>Resets |

|---------|--------|--------|------------------------|-------|--------|--------|--------|--------|--------|------------------|---------------------------------|

| 01h     | TMR0   | Timer0 | Fimer0 module register |       |        |        |        |        |        | xxxx xxxx        | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE    | PEIE                   | T0IE  | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x        | 0000 000u                       |

| 81h     | OPTION | RBPU   | INTEDG                 | TOCS  | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111        | 1111 1111                       |

| 85h     | TRISA  |        |                        | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111           | 1 1111                          |

Legend: — = Unimplemented locations, read as '0', x = unknown, u = unchanged.

Note: Shaded bits are not used by TMR0 module.

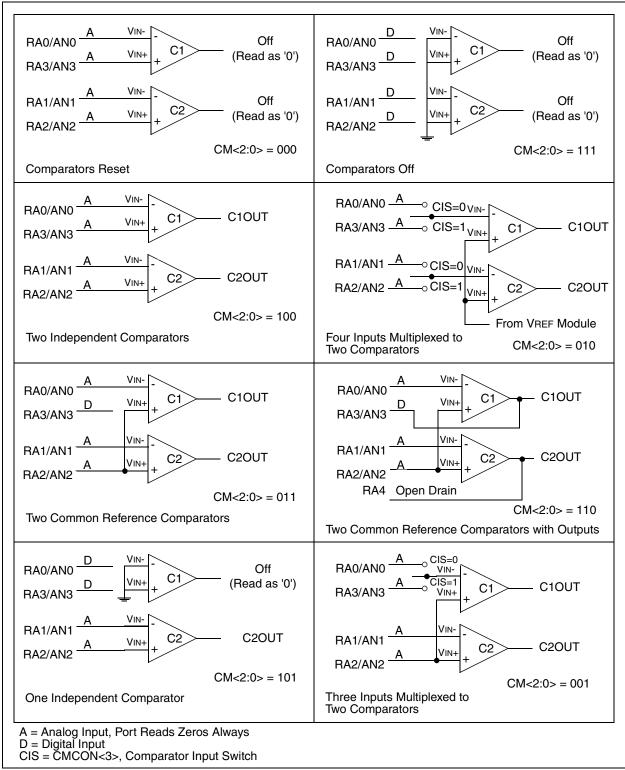

### 8.1 <u>Comparator Configuration</u>

There are eight modes of operation for the comparators. The CMCON register is used to select the mode. Figure 8-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the comparator

mode is changed, the comparator output level may not be valid for the specified mode change delay shown in Table 13-1.

Note: Comparator interrupts should be disabled during a comparator mode change, otherwise a false interrupt may occur.

FIGURE 8-1: COMPARATOR I/O OPERATING MODES

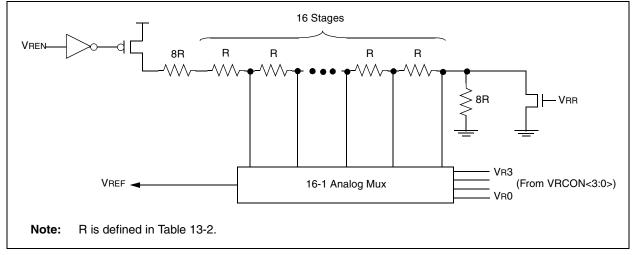

### 9.0 VOLTAGE REFERENCE MODULE

The Voltage Reference is a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of VREF values and has a power-down function to conserve power when the reference is not being used. The VRCON register controls the operation of the reference as shown in Register 9-1. The block diagram is given in Figure 9-1.

### 9.1 Configuring the Voltage Reference

The Voltage Reference can output 16 distinct voltage levels for each range.

The equations used to calculate the output of the Voltage Reference are as follows:

if VRR = 1: VREF = (VR<3:0>/24) x VDD

if VRR = 0: VREF = (VDD x 1/4) + (VR<3:0>/32) x VDD

The setting time of the Voltage Reference must be considered when changing the VREF output (Table 13-1). Example 9-1 shows an example of how to configure the Voltage Reference for an output voltage of 1.25V with VDD = 5.0V.

| R/W-0                                                                                                                                                                | R/W-0                                                                                                                             | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|-------|-------|-------|---------------------------------------------------------------------------------------|

| VREN                                                                                                                                                                 | VROE                                                                                                                              | Vrr   | _   | Vr3   | VR2   | VR1   | VR0   | R = Readable bit                                                                      |

| bit7                                                                                                                                                                 | •                                                                                                                                 |       | •   |       |       |       | bitO  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 7: VREF Enable<br>1 = VREF circuit powered on<br>0 = VREF circuit powered down, no IDD drain                                                                     |                                                                                                                                   |       |     |       |       |       |       |                                                                                       |

| bit 6:                                                                                                                                                               | <ul> <li>t 6: VREF Output Enable</li> <li>1 = VREF is output on RA2 pin</li> <li>0 = VREF is disconnected from RA2 pin</li> </ul> |       |     |       |       |       |       |                                                                                       |

| bit 5:                                                                                                                                                               | <pre>VRR: VREF Range selection 1 = Low Range 0 = High Range</pre>                                                                 |       |     |       |       |       |       |                                                                                       |

| bit 4: Unimplemented: Read as '0'                                                                                                                                    |                                                                                                                                   |       |     |       |       |       |       |                                                                                       |

| bit 3-0: VR<3:0>: VREF value selection $0 \le VR$ [3:0] $\le 15$<br>when VRR = 1: VREF = (VR<3:0>/ 24) * VDD<br>when VRR = 0: VREF = 1/4 * VDD + (VR<3:0>/ 32) * VDD |                                                                                                                                   |       |     |       |       |       |       |                                                                                       |

### REGISTER 9-1: VRCON REGISTER (ADDRESS 9Fh)

FIGURE 9-1: VOLTAGE REFERENCE BLOCK DIAGRAM

### 10.9 <u>Code Protection</u>

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip                    | does | not | recommend | code |  |  |

|-------|------------------------------|------|-----|-----------|------|--|--|

|       | protecting windowed devices. |      |     |           |      |  |  |

### 10.10 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. Only the least significant 4 bits of the ID locations are used.

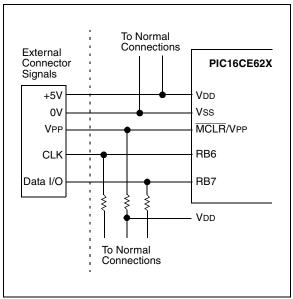

### 10.11 In-Circuit Serial Programming

The PIC16CE62X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a program/verify mode by holding the RB6 and RB7 pins low, while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After reset, to place the device into programming/verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X/9XX Programming Specifications (Literature #DS30228).

A typical in-circuit serial programming connection is shown in Figure 10-20.

### FIGURE 10-20: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

### 11.1 Instruction Descriptions

| ADDLW            | Add Lite                                   | ral and V  | w              |         |

|------------------|--------------------------------------------|------------|----------------|---------|

| Syntax:          | [label] A                                  | ADDLW      | k              |         |

| Operands:        | $0 \le k \le 25$                           | 55         |                |         |

| Operation:       | (W) + k –                                  | → (W)      |                |         |

| Status Affected: | C, DC, Z                                   |            |                |         |

| Encoding:        | 11                                         | 111x       | kkkk           | kkkk    |

| Description:     | The conter<br>added to th<br>result is pla | ne eight b | it literal 'k' | and the |

| Words:           | 1                                          |            |                |         |

| Cycles:          | 1                                          |            |                |         |

| Example          | ADDLW                                      | 0x15       |                |         |

|                  | After Inst                                 | W =        | 0x10<br>0x25   |         |

| ANDLW            | AND Literal with W                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                            |

| Operands:        | $0 \leq k \leq 255$                                                                                                 |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                     |

| Status Affected: | Z                                                                                                                   |

| Encoding:        | 11 1001 kkkk kkkk                                                                                                   |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |

| Words:           | 1                                                                                                                   |

| Cycles:          | 1                                                                                                                   |

| Example          | ANDLW 0x5F                                                                                                          |

|                  | Before Instruction<br>W = 0xA3<br>After Instruction<br>W = 0x03                                                     |

| ADDWF            | Add W and f                                                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |

| Operation:       | $(W) + (f) \to (dest)$                                                                                                                                                      |

| Status Affected: | C, DC, Z                                                                                                                                                                    |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                           |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result is<br>stored in the W register. If 'd' is 1, the<br>result is stored back in register 'f'. |

| Words:           | 1                                                                                                                                                                           |

| Cycles:          | 1                                                                                                                                                                           |

| Example          | ADDWF FSR, 0                                                                                                                                                                |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0xD9<br>FSR = 0xC2                                                                                 |

| ANDWF            | AND W with f                                                                                                                                                |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                           |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                          |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                          |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |  |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                           |  |  |  |  |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is 0, the result is stored in the W<br>register. If 'd' is 1, the result is stored<br>back in register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                           |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                           |  |  |  |  |  |

| Example          | ANDWF FSR, 1                                                                                                                                                |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0x17<br>FSR = 0x02                                                                 |  |  |  |  |  |

| BTFSS            | Bit Test f, Skip if Set                                                  |                                                                                                             |                                           |                           |

|------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------|

| Syntax:          | [ <i>label</i> ] B                                                       | TFSS f,b                                                                                                    | )                                         |                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 12 \\ 0 \leq b < 7 \end{array}$          | 7                                                                                                           |                                           |                           |

| Operation:       | skip if (f<                                                              | b>) = 1                                                                                                     |                                           |                           |

| Status Affected: | None                                                                     |                                                                                                             |                                           |                           |

| Encoding:        | 01                                                                       | 11bb                                                                                                        | bfff                                      | ffff                      |

| Description:     | instruction<br>If bit 'b' is '<br>fetched du<br>execution,<br>executed i | register 'f' is<br>is skipped.<br>1', then the<br>ring the cur<br>is discarde<br>nstead, ma<br>instruction. | next instru<br>rrent instru<br>d and a No | uction<br>Iction<br>DP is |

| Words:           | 1                                                                        |                                                                                                             |                                           |                           |

| Cycles:          | 1(2)                                                                     |                                                                                                             |                                           |                           |

| Example          | HERE<br>FALSE<br>TRUE                                                    |                                                                                                             | FLAG, 1<br>PROCESS_                       | _CODE                     |

|                  | Before In                                                                | struction                                                                                                   |                                           |                           |

|                  | After Inst                                                               | ruction<br>if FLAG<1><br>PC = a<br>if FLAG<1>                                                               | = 0,<br>address F                         |                           |

| CLRF             | Clear f                                                               |                    |       |      |  |

|------------------|-----------------------------------------------------------------------|--------------------|-------|------|--|

| Syntax:          | [label] (                                                             | CLRF f             |       |      |  |

| Operands:        | $0 \le f \le 12$                                                      | 27                 |       |      |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |                    |       |      |  |

| Status Affected: | Z                                                                     |                    |       |      |  |

| Encoding:        | 0 0                                                                   | 0001               | lfff  | ffff |  |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |                    |       |      |  |

| Words:           | 1                                                                     |                    |       |      |  |

| Cycles:          | 1                                                                     |                    |       |      |  |

| Example          | CLRF                                                                  | FLAC               | G_REG |      |  |

|                  | Before In                                                             | struction          |       |      |  |

|                  |                                                                       | FLAG_RE            | EG =  | 0x5A |  |

|                  | After Inst                                                            | ruction<br>Flag Re | EG =  | 0x00 |  |

|                  |                                                                       | Z                  | =     | 1    |  |

| CALL             | Call Subroutine                                                                                                                                                                                                                               |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                       |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                          |  |  |  |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                                                              |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                          |  |  |  |

| Encoding:        | 10 0kkk kkkk kkkk                                                                                                                                                                                                                             |  |  |  |

| Description:     | Call Subroutine. First, return address<br>(PC+1) is pushed onto the stack. The<br>eleven bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a two-cycle instruc-<br>tion. |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                             |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                                             |  |  |  |

| Example          | HERE CALL THERE                                                                                                                                                                                                                               |  |  |  |

|                  | Before Instruction<br>PC = Address HERE<br>After Instruction<br>PC = Address THERE<br>TOS = Address HERE+1                                                                                                                                    |  |  |  |

| Clear W                                                               |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [ label ]                                                             | CLRW                                                                                                          |                                                                                                                                                                  |                                                                                                                                                                                               |  |

| None                                                                  |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |

| $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |

| Z                                                                     |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |

| 00                                                                    | 0001                                                                                                          | 0000                                                                                                                                                             | 0011                                                                                                                                                                                          |  |

| W register is cleared. Zero bit (Z) is set.                           |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |

| 1                                                                     |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |

| 1                                                                     |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |

| CLRW                                                                  |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |

| Before Instruction                                                    |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |

| After Inst                                                            | ruction<br>W =                                                                                                | 0x5A<br>0x00<br>1                                                                                                                                                |                                                                                                                                                                                               |  |

|                                                                       | $[label]$ None $00h \rightarrow (V \\ 1 \rightarrow Z$ $Z$ $00$ W register set. 1 $CLRW$ Before In After Inst | $[label] CLRW$ None $00h \rightarrow (W)$ $1 \rightarrow Z$ $Z$ $00 0001$ W register is cleared set. $1$ $CLRW$ Before Instruction $W =$ After Instruction $W =$ | $[label] CLRW$ None $00h \rightarrow (W)$ $1 \rightarrow Z$ Z $00  0001  0000$ W register is cleared. Zero bit set. $1$ $1$ $CLRW$ Before Instruction $W = 0x5A$ After Instruction $W = 0x00$ |  |

$\odot$  1998-2013 Microchip Technology Inc.

| NOP              | No Operation |      |      |      |  |

|------------------|--------------|------|------|------|--|

| Syntax:          | [ label ]    | NOP  |      |      |  |

| Operands:        | None         |      |      |      |  |

| Operation:       | No operation |      |      |      |  |

| Status Affected: | None         |      |      |      |  |

| Encoding:        | 0 0          | 0000 | 0xx0 | 0000 |  |

| Description:     | No operati   | ion. |      |      |  |

| Words:           | 1            |      |      |      |  |

| Cycles:          | 1            |      |      |      |  |

| Example          | NOP          |      |      |      |  |

| RETFIE           | Return from Interrupt                                                                                                                                                                                             |                        |          |      |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------|------|--|

| Syntax:          | [ label ]                                                                                                                                                                                                         | RETFIE                 |          |      |  |

| Operands:        | None                                                                                                                                                                                                              |                        |          |      |  |

| Operation:       | TOS $\rightarrow$ PC,<br>1 $\rightarrow$ GIE                                                                                                                                                                      |                        |          |      |  |

| Status Affected: | None                                                                                                                                                                                                              |                        |          |      |  |

| Encoding:        | 00                                                                                                                                                                                                                | 0000                   | 0000     | 1001 |  |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top of Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a two-cycle<br>instruction. |                        |          |      |  |

| Words:           | 1                                                                                                                                                                                                                 |                        |          |      |  |

| Cycles:          | 2                                                                                                                                                                                                                 |                        |          |      |  |

| Example          | RETFIE                                                                                                                                                                                                            |                        |          |      |  |

|                  |                                                                                                                                                                                                                   | rrupt<br>PC =<br>GIE = | TOS<br>1 |      |  |

| OPTION                 | Load Op                                                                                                 | tion Reg                                                        | gister                                              |                            |

|------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------|----------------------------|

| Syntax:                | [ label ]                                                                                               | OPTION                                                          | ١                                                   |                            |

| Operands:              | None                                                                                                    |                                                                 |                                                     |                            |

| Operation:             | $(W) \rightarrow O$                                                                                     | PTION                                                           |                                                     |                            |

| Status Affected:       | None                                                                                                    |                                                                 |                                                     |                            |

| Encoding:              | 0 0                                                                                                     | 0000                                                            | 0110                                                | 0010                       |

| Description:<br>Words: | The conter<br>loaded in t<br>instruction<br>compatibil<br>Since OPT<br>register, th<br>address it.<br>1 | he OPTIC<br>is suppor<br>ity with PI<br>TION is a<br>re user ca | DN registe<br>rted for co<br>C16C5X p<br>readable/v | r. This<br>de<br>products. |

| Cycles:                | 1                                                                                                       |                                                                 |                                                     |                            |

| Example                |                                                                                                         |                                                                 |                                                     |                            |

|                        |                                                                                                         | re PIC <sup>®</sup> N                                           | rd compa<br>/ICU prode<br>uction.                   | -                          |

| RETLW            | Return with Literal in W                                                                                                                                                            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                   |

| Description:     | The W register is loaded with the eight<br>bit literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a two-cycle<br>instruction. |

| Words:           | 1                                                                                                                                                                                   |

| Cycles:          | 2                                                                                                                                                                                   |

| Example          | CALL TABLE ;W contains table<br>;offset value<br>• ;W now has table<br>value                                                                                                        |

| TABLE            | ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;<br>•<br>RETLW kn ; End of table                                                                                         |

|                  | Before Instruction                                                                                                                                                                  |

|                  | W = 0x07<br>After Instruction                                                                                                                                                       |

|                  | W = value of k8                                                                                                                                                                     |

| RETURN             | Return from Subroutine                                                                                          | RRF              | Rotate Right f through Carry                                                                                                                                                                                                               |

|--------------------|-----------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:            | [label] RETURN                                                                                                  | Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                                   |

| Operands:          | None                                                                                                            | Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                          |

| Operation:         | $TOS \rightarrow PC$                                                                                            |                  | $d \in [0,1]$                                                                                                                                                                                                                              |

| Status Affected:   | None                                                                                                            | Operation:       | See description below                                                                                                                                                                                                                      |

| Encoding:          | 00 0000 0000 1000                                                                                               | Status Affected: | С                                                                                                                                                                                                                                          |

| Description:       | Return from subroutine. The stack is                                                                            | Encoding:        | 00 1100 dfff ffff                                                                                                                                                                                                                          |

|                    | POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a two cycle instruction. | Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is                                                             |

| Words:             | 1                                                                                                               |                  | placed back in register 'f'.                                                                                                                                                                                                               |

| Cycles:<br>Example | 2<br>RETURN                                                                                                     |                  | C Register f                                                                                                                                                                                                                               |

|                    | After Interrupt                                                                                                 | Words:           | 1                                                                                                                                                                                                                                          |

|                    | PC = TOS                                                                                                        | Cycles:          | 1                                                                                                                                                                                                                                          |

|                    |                                                                                                                 | Example          | RRF REG1,0                                                                                                                                                                                                                                 |

|                    |                                                                                                                 |                  | Before Instruction       REG1       =       1110       0110         C       =       0       0         After Instruction       REG1       =       1110       0110         W       =       0111       0011         C       =       0       0 |

| RLF              | Rotate Left f t                                                                                                                                                                                               | hrough Carry |    |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----|--|--|--|

| Syntax:          | [label] RLF                                                                                                                                                                                                   | f,d          |    |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                             |              |    |  |  |  |

| Operation:       | See description                                                                                                                                                                                               | n below      |    |  |  |  |

| Status Affected: | С                                                                                                                                                                                                             |              |    |  |  |  |

| Encoding:        | 00 110                                                                                                                                                                                                        | 1 dfff ff    | ff |  |  |  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>stored back in register 'f'. |              |    |  |  |  |

| Words:           | 1                                                                                                                                                                                                             |              |    |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                             |              |    |  |  |  |

|                  |                                                                                                                                                                                                               |              |    |  |  |  |

| Example          | RLF                                                                                                                                                                                                           | REG1,0       |    |  |  |  |

# SLEEP

| 02221            |                                                                                                                                                                                                                                                                          |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] SLEEP                                                                                                                                                                                                                                                          |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                                                     |  |  |  |  |

| Operation:       | 00h $\rightarrow$ WDT,<br>0 $\rightarrow$ WDT prescaler,<br>1 $\rightarrow$ TO,<br>0 $\rightarrow$ PD                                                                                                                                                                    |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                                                                   |  |  |  |  |

| Encoding:        | 00 0000 0110 0011                                                                                                                                                                                                                                                        |  |  |  |  |

| Description:     | The power-down status bit, $\overline{PD}$ is<br>cleared. Time-out status bit, $\overline{TO}$ is<br>set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped.<br>See Section 10.8 for more details. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                        |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                        |  |  |  |  |

| Example:         | SLEEP                                                                                                                                                                                                                                                                    |  |  |  |  |

and test the sample code. In addition, PICDEM-17 supports down-loading of programs to and executing out of external FLASH memory on board. The PICDEM-17 is also usable with the MPLAB-ICE or PICMASTER emulator, and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

### 12.17 <u>SEEVAL Evaluation and Programming</u> <u>System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

### 12.18 <u>KEELOQ Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

## 13.1 DC CHARACTERISTICS:

### PIC16CE62X-04 (Commercial, Industrial, Extended) PIC16CE62X-20 (Commercial, Industrial, Extended)

| DC CHARACTERISTICS |                    | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $\leq$ TA $\leq$ +85°C for industrial and $0^{\circ}$ C $\leq$ TA $\leq$ +70°C for commercial an $-40^{\circ}$ C $\leq$ TA $\leq$ +125°C for extended |        |      |           | $\begin{array}{rl} -40^{\circ}C & \leq TA \leq +85^{\circ}C \text{ for industrial and} \\ 0^{\circ}C & \leq TA \leq +70^{\circ}C \text{ for commercial and} \end{array}$ |                                                                   |

|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Param<br>No.       | Sym                | Characteristic                                                                                                                                                                                                                                     | Min    | Тур† | Max       | Units                                                                                                                                                                    | Conditions                                                        |

| D001               | Vdd                | Supply Voltage                                                                                                                                                                                                                                     | 3.0    | -    | 5.5       | V                                                                                                                                                                        | See Figure 13-1 through Figure 13-3                               |