#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Last Time Buy                                                                     |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                           |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40MHz                                                                             |

| Connectivity               | CANbus, EBI/EMI, SPI, UART/USART                                                  |

| Peripherals                | PWM, WDT                                                                          |

| Number of I/O              | 79                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 12K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 2.7V                                                                      |

| Data Converters            | A/D 14x8/10b                                                                      |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-LQFP                                                                          |

| Supplier Device Package    | PG-TQFP-100-5                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc164cs32f40fbbafxqma1 |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Data Sheet, V1.1, Aug. 2006

# XC164CS-32F/32R 16-Bit Single-Chip Microcontroller with C166SV2 Core

## Microcontrollers

Never stop thinking

#### XC164CS Revision History: V1.1, 2006-08

Previous Version(s): V1.0, 2005-06 (XC164-32F)

| Page | Subjects (major changes since last revision)                                                                                                                                                                                                                                         |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6    | New derivatives added.                                                                                                                                                                                                                                                               |

| 51   | Footnote at XTAL1 input pin.                                                                                                                                                                                                                                                         |

| 55   | Footnote on leakage of P3.15 added.                                                                                                                                                                                                                                                  |

| 76   | Green Package added.                                                                                                                                                                                                                                                                 |

| 75   | Thermal Resistance: $R_{\text{THA}}$ replaced by $R_{\Theta \text{JC}}$ and $R_{\Theta \text{JL}}$ because $R_{\text{THA}}$ strongly depends on the external system (PCB, environment). $P_{\text{DISS}}$ removed, because no static parameter, but derived from thermal resistance. |

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: mcdocu.comments@infineon.com

#### Summary of Features

- Up to 12 Mbytes External Address Space for Code and Data

- Programmable External Bus Characteristics for Different Address Ranges

- Multiplexed or Demultiplexed External Address/Data Buses

- Selectable Address Bus Width

- 16-Bit or 8-Bit Data Bus Width

- Four Programmable Chip-Select Signals

- Up to 79 General Purpose I/O Lines, partly with Selectable Input Thresholds and Hysteresis

- On-Chip Bootstrap Loader

- Supported by a Large Range of Development Tools like C-Compilers, Macro-Assembler Packages, Emulators, Evaluation Boards, HLL-Debuggers, Simulators, Logic Analyzer Disassemblers, Programming Boards

- On-Chip Debug Support via JTAG Interface

- 100-Pin Green TQFP Package, 0.5 mm (19.7 mil) pitch (RoHS compliant)

#### **Ordering Information**

The ordering code for Infineon microcontrollers provides an exact reference to the required product. This ordering code identifies:

- the derivative itself, i.e. its function set, the temperature range, and the supply voltage

- the package and the type of delivery.

For the available ordering codes for the XC164CS please refer to your responsible sales representative or your local distributor.

Note: The ordering codes for Mask-ROM versions are defined for each product after verification of the respective ROM code.

This document describes several derivatives of the XC164CS group. **Table 1** enumerates these derivatives and summarizes the differences. As this document refers to all of these derivatives, some descriptions may not apply to a specific product.

For simplicity all versions are referred to by the term **XC164CS** throughout this document.

RH7) so-called General Purpose Registers (GPRs).

The upper 256 bytes of the DPRAM are directly bitaddressable. When used by a GPR, any location in the DPRAM is bitaddressable.

**1024 bytes (2**  $\times$  **512 bytes)** of the address space are reserved for the Special Function Register areas (SFR space and ESFR space). SFRs are wordwide registers which are used for controlling and monitoring functions of the different on-chip units. Unused SFR addresses are reserved for future members of the XC166 Family. Therefore, they should either not be accessed, or written with zeros, to ensure upward compatibility.

In order to meet the needs of designs where more memory is required than is provided on chip, up to 12 Mbytes (approximately, see **Table 3**) of external RAM and/or ROM can be connected to the microcontroller. The External Bus Interface also provides access to external peripherals.

| Address Area                        | Start Loc.           | End Loc.             | Area Size <sup>2)</sup> | Notes                        |

|-------------------------------------|----------------------|----------------------|-------------------------|------------------------------|

| Flash register space                | FF'F000 <sub>H</sub> | FF'FFFF <sub>H</sub> | 4 Kbytes                | 3)                           |

| Reserved (Acc. trap)                | FE'0000 <sub>H</sub> | FF'EFFF <sub>H</sub> | 60 Kbytes               | -                            |

| Reserved for EPSRAM                 | F8'1800 <sub>H</sub> | FD'FFFF <sub>H</sub> | 378 Kbytes              | -                            |

| Emul. Program<br>SRAM <sup>4)</sup> | F8'0000 <sub>H</sub> | F8'17FF <sub>H</sub> | 6 Kbytes                | 2 <sup>nd</sup> way to PSRAM |

| Reserved for PSRAM                  | E0'1800 <sub>H</sub> | F7'FFFF <sub>H</sub> | < 1.5 Mbytes            | Minus PSRAM                  |

| Program SRAM                        | E0'0000 <sub>H</sub> | E0'17FF <sub>H</sub> | 6 Kbytes                | Maximum                      |

| Reserved for program memory         | C4'0000 <sub>H</sub> | DF'FFFF <sub>H</sub> | < 2 Mbytes              | Minus Flash                  |

| Program Flash/ROM                   | C0'0000 <sub>H</sub> | C3'FFFF <sub>H</sub> | 256 Kbytes              | -                            |

| Reserved                            | BF'0000 <sub>H</sub> | BF'FFFF <sub>H</sub> | 64 Kbytes               | -                            |

| External memory area                | 40'0000 <sub>H</sub> | BE'FFFF <sub>H</sub> | < 8 Mbytes              | Minus reserved segment       |

| External IO area <sup>5)</sup>      | 20'0800 <sub>H</sub> | 3F'FFFF <sub>H</sub> | < 2 Mbytes              | Minus TwinCAN                |

| TwinCAN registers                   | 20'0000 <sub>H</sub> | 20'07FF <sub>H</sub> | 2 Kbytes                | -                            |

| External memory area                | 01'0000 <sub>H</sub> | 1F'FFFF <sub>H</sub> | < 2 Mbytes              | Minus segment 0              |

| Data RAMs and SFRs                  | 00'8000 <sub>H</sub> | 00'FFFF <sub>H</sub> | 32 Kbytes               | Partly used                  |

| External memory area                | 00'000 <sub>H</sub>  | 00'7FFF <sub>H</sub> | 32 Kbytes               | -                            |

#### Table 3XC164CS Memory Map1)

1) Accesses to the shaded areas generate external bus accesses.

2) The areas marked with "<" are slightly smaller than indicated, see column "Notes".

3) Not defined register locations return a trap code.

4) The Emulation PSRAM (EPSRAM) realizes a 2<sup>nd</sup> access path to the PSRAM with a different timing.

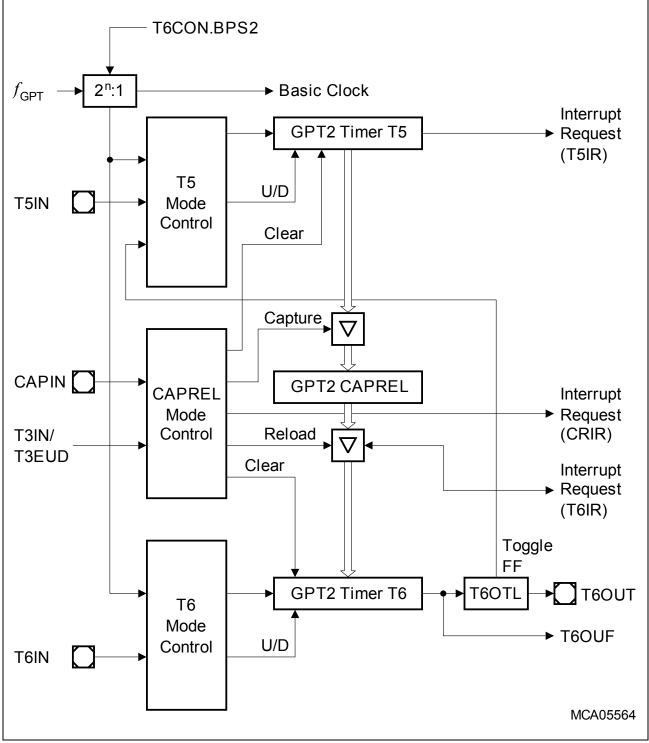

count direction (up/down) for each timer is programmable by software or may additionally be altered dynamically by an external signal on a port pin (TxEUD). Concatenation of the timers is supported via the output toggle latch (T6OTL) of timer T6, which changes its state on each timer overflow/underflow.

The state of this latch may be used to clock timer T5, and/or it may be output on pin T6OUT. The overflows/underflows of timer T6 can additionally be used to clock the CAPCOM1/2 timers, and to cause a reload from the CAPREL register.

The CAPREL register may capture the contents of timer T5 based on an external signal transition on the corresponding port pin (CAPIN), and timer T5 may optionally be cleared after the capture procedure. This allows the XC164CS to measure absolute time differences or to perform pulse multiplication without software overhead.

The capture trigger (timer T5 to CAPREL) may also be generated upon transitions of GPT1 timer T3's inputs T3IN and/or T3EUD. This is especially advantageous when T3 operates in Incremental Interface Mode.

#### 3.10 A/D Converter

For analog signal measurement, a 10-bit A/D converter with 14 multiplexed input channels and a sample and hold circuit has been integrated on-chip. It uses the method of successive approximation. The sample time (for loading the capacitors) and the conversion time is programmable (in two modes) and can thus be adjusted to the external circuitry. The A/D converter can also operate in 8-bit conversion mode, where the conversion time is further reduced.

Overrun error detection/protection is provided for the conversion result register (ADDAT): either an interrupt request will be generated when the result of a previous conversion has not been read from the result register at the time the next conversion is complete, or the next conversion is suspended in such a case until the previous result has been read.

For applications which require less analog input channels, the remaining channel inputs can be used as digital input port pins.

The A/D converter of the XC164CS supports four different conversion modes. In the standard Single Channel conversion mode, the analog level on a specified channel is sampled once and converted to a digital result. In the Single Channel Continuous mode, the analog level on a specified channel is repeatedly sampled and converted without software intervention. In the Auto Scan mode, the analog levels on a prespecified number of channels are sequentially sampled and converted. In the Auto Scan Continuous mode, the prespecified channels are repeatedly sampled and converted. In addition, the conversion of a specific channel can be inserted (injected) into a running sequence without disturbing this sequence. This is called Channel Injection Mode.

The Peripheral Event Controller (PEC) may be used to automatically store the conversion results into a table in memory for later evaluation, without requiring the overhead of entering and exiting interrupt routines for each data transfer.

After each reset and also during normal operation the ADC automatically performs calibration cycles. This automatic self-calibration constantly adjusts the converter to changing operating conditions (e.g. temperature) and compensates process variations.

These calibration cycles are part of the conversion cycle, so they do not affect the normal operation of the A/D converter.

In order to decouple analog inputs from digital noise and to avoid input trigger noise those pins used for analog input can be disconnected from the digital IO or input stages under software control. This can be selected for each pin separately via register P5DIDIS (Port 5 Digital Input Disable).

The Auto-Power-Down feature of the A/D converter minimizes the power consumption when no conversion is in progress.

## 3.12 High Speed Synchronous Serial Channels (SSC0/SSC1)

The High Speed Synchronous Serial Channels SSC0/SSC1 support full-duplex and halfduplex synchronous communication. It may be configured so it interfaces with serially linked peripheral components, full SPI functionality is supported.

A dedicated baud rate generator allows to set up all standard baud rates without oscillator tuning. For transmission, reception and error handling three separate interrupt vectors are provided.

The SSC transmits or receives characters of 2 ... 16 bits length synchronously to a shift clock which can be generated by the SSC (master mode) or by an external master (slave mode). The SSC can start shifting with the LSB or with the MSB and allows the selection of shifting and latching clock edges as well as the clock polarity.

A number of optional hardware error detection capabilities has been included to increase the reliability of data transfers. Transmit error and receive error supervise the correct handling of the data buffer. Phase error and baudrate error detect incorrect serial data.

#### Summary of Features

- Master or Slave mode operation

- Full-duplex or Half-duplex transfers

- Baudrate generation from 20 Mbit/s to 305.18 bit/s (@ 40 MHz)

- Flexible data format

- Programmable number of data bits: 2 to 16 bits

- Programmable shift direction: LSB-first or MSB-first

- Programmable clock polarity: idle low or idle high

- Programmable clock/data phase: data shift with leading or trailing clock edge

- Loop back option available for testing purposes

- Interrupt generation on transmitter buffer empty condition, receive buffer full condition, error condition (receive, phase, baudrate, transmit error)

- Three pin interface with flexible SSC pin configuration

#### 3.15 Clock Generation

The Clock Generation Unit uses a programmable on-chip PLL with multiple prescalers to generate the clock signals for the XC164CS with high flexibility. The master clock  $f_{MC}$  is the reference clock signal, and is used for TwinCAN and is output to the external system. The CPU clock  $f_{CPU}$  and the system clock  $f_{SYS}$  are derived from the master clock either directly (1:1) or via a 2:1 prescaler ( $f_{SYS} = f_{CPU} = f_{MC} / 2$ ). See also Section 4.4.1.

The on-chip oscillator can drive an external crystal or accepts an external clock signal. The oscillator clock frequency can be multiplied by the on-chip PLL (by a programmable factor) or can be divided by a programmable prescaler factor.

If the bypass mode is used (direct drive or prescaler) the PLL can deliver an independent clock to monitor the clock signal generated by the on-chip oscillator. This PLL clock is independent from the XTAL1 clock. When the expected oscillator clock transitions are missing the Oscillator Watchdog (OWD) activates the PLL Unlock/OWD interrupt node and supplies the CPU with an emergency clock, the PLL clock signal. Under these circumstances the PLL will oscillate with its basic frequency.

The oscillator watchdog can be disabled by switching the PLL off. This reduces power consumption, but also no interrupt request will be generated in case of a missing oscillator clock.

Note: At the end of an external reset ( $\overline{EA} = '0'$ ) the oscillator watchdog may be disabled via hardware by (externally) pulling the  $\overline{RD}$  line low upon a reset, similar to the standard reset configuration.

## 3.16 Parallel Ports

The XC164CS provides up to 79 I/O lines which are organized into six input/output ports and one input port. All port lines are bit-addressable, and all input/output lines are individually (bit-wise) programmable as inputs or outputs via direction registers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs. The output drivers of some I/O ports can be configured (pin by pin) for push/pull operation or open-drain operation via control registers. During the internal reset, all port pins are configured as inputs (except for pin RSTOUT).

The edge characteristics (shape) and driver characteristics (output current) of the port drivers can be selected via registers POCONx.

The input threshold of some ports is selectable (TTL or CMOS like), where the special CMOS like input threshold reduces noise sensitivity due to the input hysteresis. The input threshold may be selected individually for each byte of the respective ports.

All port lines have programmable alternate input or output functions associated with them. All port lines that are not used for these alternate functions may be used as general purpose IO lines.

#### 3.18 Instruction Set Summary

Table 8 lists the instructions of the XC164CS in a condensed way.

The various addressing modes that can be used with a specific instruction, the operation of the instructions, parameters for conditional execution of instructions, and the opcodes for each instruction can be found in the "Instruction Set Manual".

This document also provides a detailed description of each instruction.

| Mnemonic      | Description                                                                                       | Bytes |

|---------------|---------------------------------------------------------------------------------------------------|-------|

| ADD(B)        | Add word (byte) operands                                                                          | 2/4   |

| ADDC(B)       | Add word (byte) operands with Carry                                                               | 2/4   |

| SUB(B)        | Subtract word (byte) operands                                                                     | 2/4   |

| SUBC(B)       | Subtract word (byte) operands with Carry                                                          | 2/4   |

| MUL(U)        | (Un)Signed multiply direct GPR by direct GPR (16- $\times$ 16-bit)                                | 2     |

| DIV(U)        | (Un)Signed divide register MDL by direct GPR (16-/16-bit)                                         | 2     |

| DIVL(U)       | (Un)Signed long divide reg. MD by direct GPR (32-/16-bit)                                         | 2     |

| CPL(B)        | Complement direct word (byte) GPR                                                                 | 2     |

| NEG(B)        | Negate direct word (byte) GPR                                                                     | 2     |

| AND(B)        | Bitwise AND, (word/byte operands)                                                                 | 2/4   |

| OR(B)         | Bitwise OR, (word/byte operands)                                                                  | 2/4   |

| XOR(B)        | Bitwise exclusive OR, (word/byte operands)                                                        | 2/4   |

| BCLR/BSET     | Clear/Set direct bit                                                                              | 2     |

| BMOV(N)       | Move (negated) direct bit to direct bit                                                           | 4     |

| BAND/BOR/BXOR | AND/OR/XOR direct bit with direct bit                                                             | 4     |

| BCMP          | Compare direct bit to direct bit                                                                  | 4     |

| BFLDH/BFLDL   | Bitwise modify masked high/low byte of bit-addressable direct word memory with immediate data     | 4     |

| CMP(B)        | Compare word (byte) operands                                                                      | 2/4   |

| CMPD1/2       | Compare word data to GPR and decrement GPR by 1/2                                                 | 2/4   |

| CMPI1/2       | Compare word data to GPR and increment GPR by 1/2                                                 | 2/4   |

| PRIOR         | Determine number of shift cycles to normalize direct word GPR and store result in direct word GPR | 2     |

| SHL/SHR       | Shift left/right direct word GPR                                                                  | 2     |

#### Table 8 Instruction Set Summary

5) Overload conditions occur if the standard operating conditions are exceeded, i.e. the voltage on any pin exceeds the specified range:  $V_{OV} > V_{DDP} + 0.5 \vee (I_{OV} > 0)$  or  $V_{OV} < V_{SS} - 0.5 \vee (I_{OV} < 0)$ . The absolute sum of input overload currents on all pins may not exceed **50 mA**. The supply voltages must remain within the specified limits.

Proper operation is not guaranteed if overload conditions occur on functional pins such as XTAL1,  $\overline{RD}$ ,  $\overline{WR}$ , etc.

- 6) Not subject to production test verified by design/characterization.

- 7) An overload current  $(I_{OV})$  through a pin injects a certain error current  $(I_{INJ})$  into the adjacent pins. This error current adds to the respective pin's leakage current  $(I_{OZ})$ . The amount of error current depends on the overload current and is defined by the overload coupling factor  $K_{OV}$ . The polarity of the injected error current is inverse compared to the polarity of the overload current that produces it.

The total current through a pin is  $|I_{TOT}| = |I_{OZ}| + (|I_{OV}| \times K_{OV})$ . The additional error current may distort the input voltage on analog inputs.

8) The timing is valid for pin drivers operating in default current mode (selected after reset). Reducing the output current may lead to increased delays or reduced driving capability ( $C_L$ ).

#### Parameter Interpretation

The parameters listed in the following partly represent the characteristics of the XC164CS and partly its demands on the system. To aid in interpreting the parameters right, when evaluating them for a design, they are marked in column "Symbol":

**CC** (Controller Characteristics):

The logic of the XC164CS will provide signals with the respective characteristics.

**SR** (System Requirement):

The external system must provide signals with the respective characteristics to the XC164CS.

#### 4.2 DC Parameters

## Table 11DC Characteristics (Operating Conditions apply)<sup>1)</sup>

| Parameter                                                      | Symbol                           |    | Limit                             | Values                          | Unit | <b>Test Condition</b>                                               |  |

|----------------------------------------------------------------|----------------------------------|----|-----------------------------------|---------------------------------|------|---------------------------------------------------------------------|--|

|                                                                |                                  |    | Min.                              | Max.                            |      |                                                                     |  |

| Input low voltage TTL<br>(all except XTAL1)                    | V <sub>IL</sub>                  | SR | -0.5                              | 0.2 × V <sub>DDP</sub><br>- 0.1 | V    | -                                                                   |  |

| Input low voltage<br>XTAL1 <sup>2)</sup>                       | V <sub>ILC</sub>                 | SR | -0.5                              | $0.3 	imes V_{ m DDI}$          | V    | -                                                                   |  |

| Input low voltage<br>(Special Threshold)                       | V <sub>ILS</sub>                 | SR | -0.5                              | $0.45 \times V_{\text{DDP}}$    | V    | 3)                                                                  |  |

| Input high voltage TTL<br>(all except XTAL1)                   | V <sub>IH</sub>                  | SR | $0.2 \times V_{\text{DDP}} + 0.9$ | V <sub>DDP</sub> + 0.5          | V    | -                                                                   |  |

| Input high voltage<br>XTAL1 <sup>2)</sup>                      | V <sub>IHC</sub>                 | SR | $0.7 	imes V_{ m DDI}$            | V <sub>DDI</sub> + 0.5          | V    | -                                                                   |  |

| Input high voltage<br>(Special Threshold)                      | V <sub>IHS</sub>                 | SR | 0.8 × V <sub>DDP</sub><br>- 0.2   | V <sub>DDP</sub> + 0.5          | V    | 3)                                                                  |  |

| Input Hysteresis<br>(Special Threshold)                        | HYS                              |    | $0.04 \times V_{\text{DDP}}$      | -                               | V    | $V_{\text{DDP}}$ in [V],<br>Series resis-<br>tance = 0 $\Omega^{3}$ |  |

| Output low voltage                                             | V <sub>OL</sub>                  | CC | -                                 | 1.0                             | V    | $I_{\rm OL} \leq I_{\rm OLmax}^{4)}$                                |  |

|                                                                |                                  |    | -                                 | 0.45                            | V    | $I_{\rm OL} \leq I_{\rm OLnom}^{4)5)$                               |  |

| Output high voltage <sup>6)</sup>                              | V <sub>OH</sub>                  | СС | V <sub>DDP</sub> - 1.0            | _                               | V    | $I_{\rm OH} \ge I_{\rm OHmax}^{4)}$                                 |  |

|                                                                |                                  |    | V <sub>DDP</sub> - 0.45           | _                               | V    | $I_{\rm OH} \ge I_{\rm OHnom}^{4)5)$                                |  |

| Input leakage current<br>(Port 5) <sup>7)</sup>                | I <sub>OZ1</sub>                 | CC | -                                 | ±300                            | nA   | $0 V < V_{IN} < V_{DDP},$<br>$T_A \le 125 \text{ °C}$               |  |

|                                                                |                                  |    |                                   | ±200                            | nA   | $0 V < V_{IN} < V_{DDP},$<br>$T_A \le 85 \ ^{\circ}C^{14)}$         |  |

| Input leakage current (all other <sup>8)</sup> ) <sup>7)</sup> | I <sub>OZ2</sub>                 | CC | -                                 | ±500                            | nA   | 0.45 V < V <sub>IN</sub> <<br>V <sub>DDP</sub>                      |  |

| Configuration pull-up                                          | $I_{\rm CPUH}^{10)}$             |    | -                                 | -10                             | μA   | $V_{\rm IN} = V_{\rm IHmin}$                                        |  |

| current <sup>9)</sup>                                          | $I_{\rm CPUL}^{11)}$             |    | -100                              | _                               | μA   | $V_{\rm IN} = V_{\rm ILmax}$                                        |  |

| Configuration pull-                                            | $I_{\rm CPDL}^{10)}$             |    | _                                 | 10                              | μA   | $V_{\rm IN}$ = $V_{\rm ILmax}$                                      |  |

| down current <sup>12)</sup>                                    | I <sub>CPDH</sub> <sup>11)</sup> |    | 120                               | -                               | μA   | $V_{\rm IN} = V_{\rm IHmin}$                                        |  |

| Table 11 | DC Characteristics ( | Operating | Conditions | apply)1) ( | (cont'd) |

|----------|----------------------|-----------|------------|------------|----------|

|----------|----------------------|-----------|------------|------------|----------|

| Parameter                                                  | Symbol                                 |    | Limit Values |      | Unit | <b>Test Condition</b>               |  |

|------------------------------------------------------------|----------------------------------------|----|--------------|------|------|-------------------------------------|--|

|                                                            |                                        |    | Min.         | Max. |      |                                     |  |

| Level inactive hold current <sup>13)</sup>                 | <i>I</i> <sub>LHI</sub> <sup>10)</sup> |    | -            | -10  | μA   | $V_{\rm OUT}$ = 0.5 × $V_{\rm DDP}$ |  |

| Level active hold current <sup>13)</sup>                   | $I_{\text{LHA}}^{11)}$                 |    | -100         | -    | μA   | V <sub>OUT</sub> = 0.45 V           |  |

| XTAL1 input current                                        | $I_{\rm IL}$                           | CC | _            | ±20  | μA   | $0 V < V_{IN} < V_{DDI}$            |  |

| Pin capacitance <sup>14)</sup><br>(digital inputs/outputs) | C <sub>IO</sub>                        | CC | -            | 10   | pF   | -                                   |  |

1) Keeping signal levels within the limits specified in this table, ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{OV}$ .

2) If XTAL1 is driven by a crystal, reaching an amplitude (peak to peak) of  $0.4 \times V_{DDI}$  is sufficient.

3) This parameter is tested for P3, P4, P9.

4) The maximum deliverable output current of a port driver depends on the selected output driver mode, see Table 12, Current Limits for Port Output Drivers. The limit for pin groups must be respected.

- 5) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{OL} \rightarrow V_{SS}$ ,  $V_{OH} \rightarrow V_{DDP}$ ). However, only the levels for nominal output currents are guaranteed.

- 6) This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage results from the external circuitry.

- 7) An additional error current ( $I_{INJ}$ ) will flow if an overload current flows through an adjacent pin. Please refer to the definition of the overload coupling factor  $K_{OV}$ .

- 8) The driver of P3.15 is designed for faster switching, because this pin can deliver the reference clock for the bus interface (CLKOUT). The maximum leakage current for P3.15 is, therefore, increased to 1  $\mu$ A.

- 9) This specification is valid during Reset for configuration on RD, WR, EA, PORTO

- 10) The maximum current may be drawn while the respective signal line remains inactive.

- 11) The minimum current must be drawn to drive the respective signal line active.

- 12) This specification is valid during Reset for configuration on ALE.

- 13) This specification is valid during Reset for pins P4.3-0, which can act as  $\overline{CS}$  outputs, and for P3.12.

- 14) Not subject to production test verified by design/characterization.

- 6) All inputs (including pins configured as inputs) at 0 V to 0.1 V or at  $V_{\text{DDP}}$  0.1 V to  $V_{\text{DDP}}$ , all outputs (including pins configured as outputs) disconnected. This parameter is tested at 25 °C and is valid for  $T_{\text{J}} \ge 25$  °C.

- 7) This parameter is determined mainly by the current consumed by the oscillator switched to low gain mode (see Figure 12). This current, however, is influenced by the external oscillator circuitry (crystal, capacitors). The given values refer to a typical circuitry and may change in case of a not optimized external oscillator circuitry.

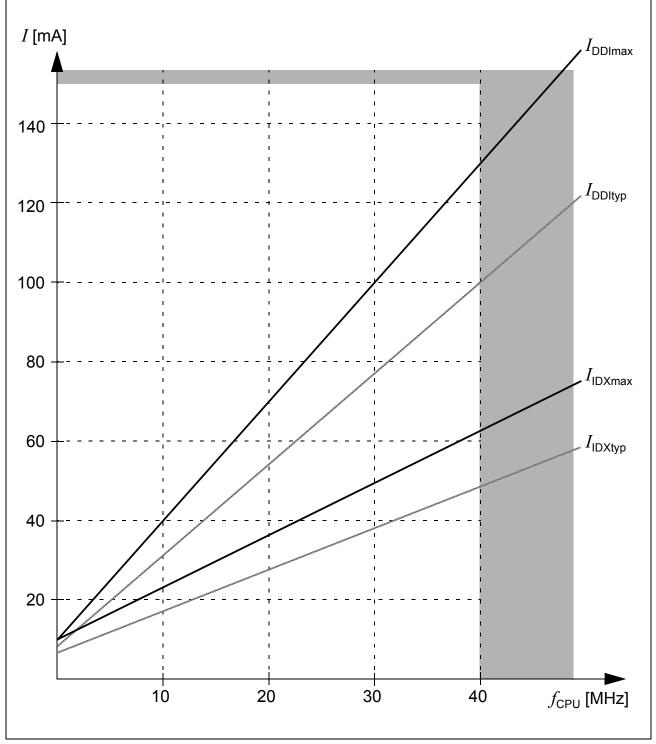

Figure 11 Supply/Idle Current as a Function of Operating Frequency

- 3) The limit values for  $f_{BC}$  must not be exceeded when selecting the peripheral frequency and the ADCTC setting.

- 4) This parameter includes the sample time t<sub>S</sub>, the time for determining the digital result and the time to load the result register with the conversion result (t<sub>SYS</sub> = 1/f<sub>SYS</sub>). Values for the basic clock t<sub>BC</sub> depend on programming and can be taken from Table 15. When the post-calibration is switched off, the conversion time is reduced by 12 x t<sub>BC</sub>.

- 5) The actual duration of the reset calibration depends on the noise on the reference signal. Conversions executed during the reset calibration increase the calibration time. The TUE for those conversions may be increased.

- 6) Not subject to production test verified by design/characterization. The given parameter values cover the complete operating range. Under relaxed operating conditions (temperature, supply voltage) reduced values can be used for calculations. At room temperature and nominal supply voltage the following typical values can be used:

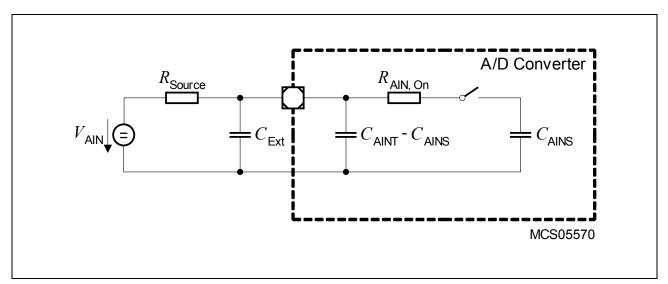

$C_{AINTtyp}$  = 12 pF,  $C_{AINStyp}$  = 7 pF,  $R_{AINtyp}$  = 1.5 k $\Omega$ ,  $C_{AREFTtyp}$  = 15 pF,  $C_{AREFStyp}$  = 13 pF,  $R_{AREFtyp}$  = 0.7 k $\Omega$ .

Figure 14 Equivalent Circuitry for Analog Inputs

## 4.4.2 On-chip Flash Operation

The XC164CS's Flash module delivers data within a fixed access time (see Table 17).

Accesses to the Flash module are controlled by the PMI and take 1 + WS clock cycles, where WS is the number of Flash access waitstates selected via bitfield WSFLASH in register IMBCTRL. The resulting duration of the access phase must cover the access time  $t_{ACC}$  of the Flash array. Therefore, the required Flash waitstates depend on the available speed grade as well as on the actual system frequency.

Note: The Flash access waitstates only affect non-sequential accesses. Due to prefetching mechanisms, the performance for sequential accesses (depending on the software structure) is only partially influenced by waitstates.

In typical applications, eliminating one waitstate increases the average performance by 5% ... 15%.

| Parameter                           | Symb             | Symbol |      | Limit Values      |                  |    |

|-------------------------------------|------------------|--------|------|-------------------|------------------|----|

|                                     |                  |        | Min. | Тур.              | Max.             |    |

| Flash module access time (Standard) | t <sub>ACC</sub> | CC     | -    | _                 | 70 <sup>1)</sup> | ns |

| Flash module access time (Grade A)  | t <sub>ACC</sub> | CC     | -    | _                 | 50 <sup>1)</sup> | ns |

| Programming time per 128-byte block | t <sub>PR</sub>  | CC     | -    | 2 <sup>2)</sup>   | 5                | ms |

| Erase time per sector               | t <sub>ER</sub>  | CC     | -    | 200 <sup>2)</sup> | 500              | ms |

#### Table 17 Flash Characteristics (Operating Conditions apply)

The actual access time is also influenced by the system frequency, so the frequency ranges are not fully linear. See Table 18.

2) Programming and erase time depends on the system frequency. Typical values are valid for 40 MHz.

Example: For an operating frequency of 40 MHz (clock cycle = 25 ns), Standard devices must be operated with 2 waitstates:  $((2 + 1) \times 25 \text{ ns}) \ge 70 \text{ ns}$ .

Grade A devices can be operated with 1 waitstate:  $((1 + 1) \times 25 \text{ ns}) \ge 50 \text{ ns}$ .

Table 18 indicates the interrelation of waitstates, system frequency, and speed grade.

| Table 18 F | Flash Access | Waitstates |

|------------|--------------|------------|

|------------|--------------|------------|

| Required Waitstates               | Frequency Range for<br>Standard Flash Speed | Frequency Range for<br>Flash Speed Grade A |

|-----------------------------------|---------------------------------------------|--------------------------------------------|

| $0$ WS (WSFLASH = $00_B$ )        | $f_{\rm CPU} \le$ 16 MHz                    | $f_{\rm CPU} \le 20 \ { m MHz}$            |

| 1 WS (WSFLASH = $01_B$ )          | $f_{\rm CPU} \le$ 28 MHz                    | $f_{CPU} \le 40 \text{ MHz}$               |

| 2 WS (WSFLASH = 10 <sub>B</sub> ) | $f_{\rm CPU} \le$ 40 MHz                    | $f_{\rm CPU} \le 40 \ { m MHz}$            |

Note: The maximum achievable system frequency is limited by the properties of the respective derivative, i.e. 40 MHz (or 20 MHz for xxx-32F20F devices).

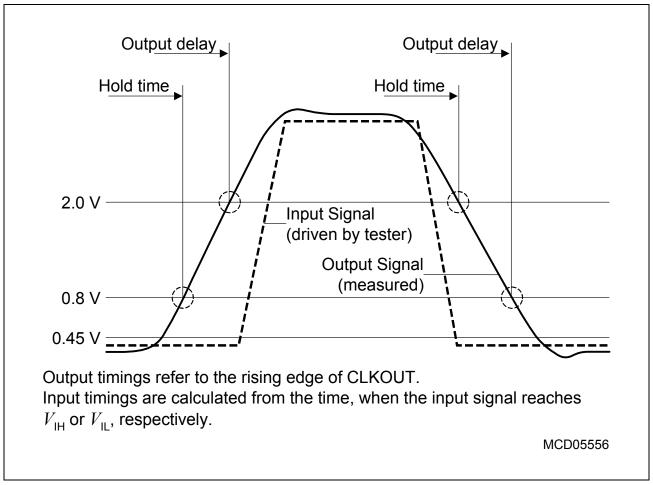

#### 4.4.4 Testing Waveforms

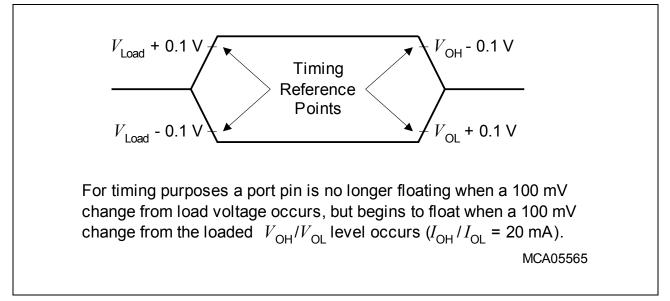

#### Figure 18 Input Output Waveforms

#### Figure 19 Float Waveforms

#### Table 22 External Bus Cycle Timing (Operating Conditions apply)

| Parameter                                                    | Sym                     | ool | Lim  | nit Values | Unit |

|--------------------------------------------------------------|-------------------------|-----|------|------------|------|

|                                                              |                         |     | Min. | Max.       |      |

| Output valid delay for:<br>RD, WR(L/H)                       | <i>tc</i> <sub>10</sub> | CC  | 1    | 15         | ns   |

| Output valid delay for:<br>BHE, ALE                          | <i>tc</i> <sub>11</sub> | СС  | -1   | 8          | ns   |

| Output valid delay for:<br>A23 … A16, A15 … A0 (on PORT1)    | <i>tc</i> <sub>12</sub> | СС  | 3    | 18         | ns   |

| Output valid delay for:<br>A15 … A0 (on PORT0)               | <i>tc</i> <sub>13</sub> | CC  | 3    | 18         | ns   |

| Output valid delay for:<br>CS                                | <i>tc</i> <sub>14</sub> | СС  | 3    | 16         | ns   |

| Output valid delay for:<br>D15 … D0 (write data, MUX-mode)   | <i>tc</i> <sub>15</sub> | СС  | 3    | 19         | ns   |

| Output valid delay for:<br>D15 … D0 (write data, DEMUX-mode) | <i>tc</i> <sub>16</sub> | СС  | 2    | 16         | ns   |

| Output hold time for:<br>RD, WR(L/H)                         | <i>tc</i> <sub>20</sub> | СС  | -3   | 4          | ns   |

| Output hold time for:<br>BHE, ALE                            | <i>tc</i> <sub>21</sub> | СС  | 0    | 11         | ns   |

| Output hold time for:<br>A23 A16, A15 A0 (on PORT0)          | <i>tc</i> <sub>23</sub> | СС  | 1    | 13         | ns   |

| Output hold time for:<br>CS                                  | <i>tc</i> <sub>24</sub> | СС  | -2   | 4          | ns   |

| Output hold time for:<br>D15 … D0 (write data)               | <i>tc</i> <sub>25</sub> | CC  | 1    | 13         | ns   |

| Input setup time for:<br>D15 … D0 (read data)                | <i>tc</i> <sub>30</sub> | SR  | 29   | -          | ns   |

| Input hold time<br>D15 … D0 (read data) <sup>1)</sup>        | <i>tc</i> <sub>31</sub> | SR  | -5   | -          | ns   |

Read data are latched with the same (internal) clock edge that triggers the address change and the rising edge of RD. Therefore address changes before the end of RD have no impact on (demultiplexed) read cycles. Read data can be removed after the rising edge of RD.

Note: The shaded parameters have been verified by characterization. They are not subject to production test.

#### Package and Reliability

#### 5.2 Flash Memory Parameters

The data retention time of the XC164CS's Flash memory (i.e. the time after which stored data can still be retrieved) depends on the number of times the Flash memory has been erased and programmed.

| Table 24 | Flash Parameters    | (XC164CS                     | 256 Kbytes) |

|----------|---------------------|------------------------------|-------------|

|          | i lasti i atameters | $(\Lambda \cup 10 + \cup 0)$ | 230  Ruyles |

| Parameter             | Symbol           | Limit Values         |      | Unit  | Notes                                           |

|-----------------------|------------------|----------------------|------|-------|-------------------------------------------------|

|                       |                  | Min.                 | Max. |       |                                                 |

| Data retention time   | t <sub>RET</sub> | 15                   | -    | years | Max. 10 <sup>3</sup><br>erase/program<br>cycles |

| Flash Erase Endurance | N <sub>ER</sub>  | 20 × 10 <sup>3</sup> | -    | -     | Max. data<br>retention time<br>5 years          |