Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | AVR                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 23                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 512 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                               |

| Data Converters            | A/D 6x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega168p-20pu |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

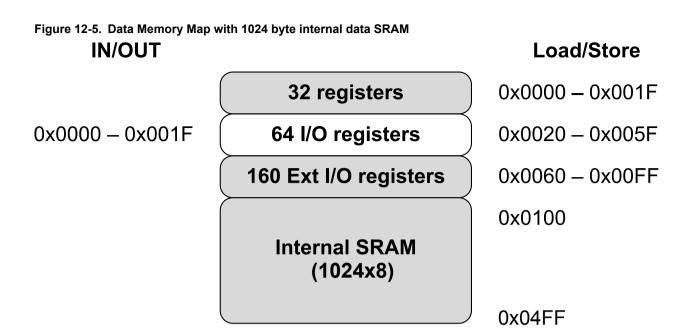

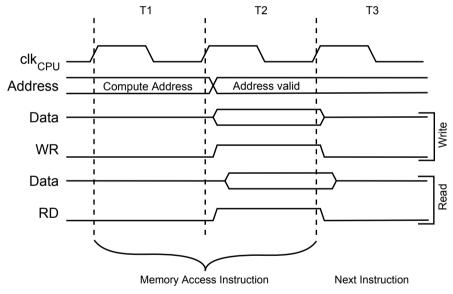

### 12.3.1. Data Memory Access Times

The internal data SRAM access is performed in two clk<sub>CPU</sub> cycles as described in the following Figure.

# 12.4. EEPROM Data Memory

The ATmega48P/PV /88P/PV /168P/PV contains 256/512/512 bytes of data EEPROM memory. It is organized as a separate data space, in which single bytes can be read and written. The EEPROM has an endurance of at least 100,000 write/erase cycles. The access between the EEPROM and the CPU is described in the following, specifying the EEPROM Address Registers, the EEPROM Data Register, and the EEPROM Control Register.

See the related links for a detailed description on EEPROM Programming in SPI or Parallel Programming mode.

### 18.4.3. Port B Data Direction Register

When addressing I/O Registers as data space using LD and ST instructions, the provided offset must be used. When using the I/O specific commands IN and OUT, the offset is reduced by 0x20, resulting in an I/O address offset within 0x00 - 0x3F.

Name:DDRBOffset:0x24Reset:0x00Property:When addressing as I/O Register: address offset is 0x04

| Bit    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| [      | DDRB7 | DDRB6 | DDRB5 | DDRB4 | DDRB3 | DDRB2 | DDRB1 | DDRB0 |

| Access | R/W   |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Bits 7:0 – DDRBn: Port B Data Direction [n = 7:0]

### 18.4.4. Port B Input Pins Address

When addressing I/O Registers as data space using LD and ST instructions, the provided offset must be used. When using the I/O specific commands IN and OUT, the offset is reduced by 0x20, resulting in an I/O address offset within 0x00 - 0x3F.

Name:PINBOffset:0x23Reset:N/AProperty:When addressing as I/O Register: address offset is 0x03

| Bit    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| [      | PINB7 | PINB6 | PINB5 | PINB4 | PINB3 | PINB2 | PINB1 | PINB0 |

| Access | R/W   |

| Reset  | x     | x     | x     | x     | x     | x     | x     | x     |

### Bits 7:0 – PINBn: Port B Input Pins Address [n = 7:0]

Writing to the pin register provides toggle functionality for IO. Refer to Toggling the Pin.

### 19.9.1. TC0 Control Register A

When addressing I/O Registers as data space using LD and ST instructions, the provided offset must be used. When using the I/O specific commands IN and OUT, the offset is reduced by 0x20, resulting in an I/O address offset within 0x00 - 0x3F.

Name:

TCCR0A

Offset:

0x44

Reset:

0x00

Property:

When addressing as I/O Register: address offset is 0x24

| Bit    | 7      | 6      | 5      | 4      | 3 | 2 | 1     | 0     |

|--------|--------|--------|--------|--------|---|---|-------|-------|

|        | COM0A1 | COM0A0 | COM0B1 | COM0B0 |   |   | WGM01 | WGM00 |

| Access | R/W    | R/W    | R/W    | R/W    |   |   | R/W   | R/W   |

| Reset  | 0      | 0      | 0      | 0      |   |   | 0     | 0     |

### Bits 7:6 – COM0An: Compare Output Mode for Channel A [n = 1:0]

These bits control the Output Compare pin (OC0A) behavior. If one or both of the COM0A[1:0] bits are set, the OC0A output overrides the normal port functionality of the I/O pin it is connected to. However, note that the Data Direction Register (DDR) bit corresponding to the OC0A pin must be set in order to enable the output driver.

When OC0A is connected to the pin, the function of the COM0A[1:0] bits depends on the WGM0[2:0] bit setting. The table below shows the COM0A[1:0] bit functionality when the WGM0[2:0] bits are set to a normal or CTC mode (non- PWM).

### Table 19-3. Compare Output Mode, non-PWM

| COM0A1 | COM0A0 | Description                               |

|--------|--------|-------------------------------------------|

| 0      | 0      | Normal port operation, OC0A disconnected. |

| 0      | 1      | Toggle OC0A on Compare Match.             |

| 1      | 0      | Clear OC0A on Compare Match.              |

| 1      | 1      | Set OC0A on Compare Match .               |

The table below shows the COM0A[1:0] bit functionality when the WGM0[1:0] bits are set to fast PWM mode.

Table 19-4. Compare Output Mode, Fast PWM<sup>(1)</sup>

| COM0A1 | COM0A0 | Description                                                                                    |

|--------|--------|------------------------------------------------------------------------------------------------|

| 0      | 0      | Normal port operation, OC0A disconnected.                                                      |

| 0      | 1      | WGM02 = 0: Normal Port Operation, OC0A Disconnected<br>WGM02 = 1: Toggle OC0A on Compare Match |

| 1      | 0      | Clear OC0A on Compare Match, set OC0A at BOTTOM (non-inverting mode)                           |

| 1      | 1      | Set OC0A on Compare Match, clear OC0A at BOTTOM (inverting mode)                               |

Note:

### 19.9.2. TC0 Control Register B

When addressing I/O Registers as data space using LD and ST instructions, the provided offset must be used. When using the I/O specific commands IN and OUT, the offset is reduced by 0x20, resulting in an I/O address offset within 0x00 - 0x3F.

Name: TCCR0B Offset: 0x45 Reset: 0x00 Property: When addressing as I/O Register: address offset is 0x25

| Bit    | 7     | 6     | 5 | 4 | 3     | 2   | 1        | 0   |

|--------|-------|-------|---|---|-------|-----|----------|-----|

| [      | FOC0A | FOC0B |   |   | WGM02 |     | CS0[2:0] |     |

| Access | R/W   | R/W   |   |   | R/W   | R/W | R/W      | R/W |

| Reset  | 0     | 0     |   |   | 0     | 0   | 0        | 0   |

### Bit 7 – FOC0A: Force Output Compare A

The FOC0A bit is only active when the WGM bits specify a non-PWM mode.

To ensure compatibility with future devices, this bit must be set to zero when TCCR0B is written when operating in PWM mode. When writing a logical one to the FOC0A bit, an immediate Compare Match is forced on the Waveform Generation unit. The OC0A output is changed according to its COM0A[1:0] bits setting. The FOC0A bit is implemented as a strobe. Therefore it is the value present in the COM0A[1:0] bits that determines the effect of the forced compare.

A FOC0A strobe will not generate any interrupt, nor will it clear the timer in CTC mode using OCR0A as TOP.

The FOC0A bit is always read as zero.

### Bit 6 – FOC0B: Force Output Compare B

The FOC0B bit is only active when the WGM bits specify a non-PWM mode.

To ensure compatibility with future devices, this bit must be set to zero when TCCR0B is written when operating in PWM mode. When writing a logical one to the FOC0B bit, an immediate Compare Match is forced on the Waveform Generation unit. The OC0B output is changed according to its COM0B[1:0] bits setting. The FOC0B bit is implemented as a strobe. Therefore it is the value present in the COM0B[1:0] bits that determines the effect of the forced compare.

A FOC0B strobe will not generate any interrupt, nor will it clear the timer in CTC mode using OCR0B as TOP.

The FOC0B bit is always read as zero.

### Bit 3 – WGM02: Waveform Generation Mode

Refer to TCCR0A.

### Bits 2:0 - CS0[2:0]: Clock Select 0 [n = 0..2]

The three Clock Select bits select the clock source to be used by the Timer/Counter.

### 19.9.4. General Timer/Counter Control Register

When addressing I/O Registers as data space using LD and ST instructions, the provided offset must be used. When using the I/O specific commands IN and OUT, the offset is reduced by 0x20, resulting in an I/O address offset within 0x00 - 0x3F.

Name: GTCCR Offset: 0x43 Reset: 0x00 Property: When addressing as I/O Register: address offset is 0x23

| Bit    | 7   | 6 | 5 | 4 | 3 | 2 | 1      | 0       |

|--------|-----|---|---|---|---|---|--------|---------|

|        | TSM |   |   |   |   |   | PSRASY | PSRSYNC |

| Access | R/W |   |   |   |   |   | R/W    | R/W     |

| Reset  | 0   |   |   |   |   |   | 0      | 0       |

### Bit 7 – TSM: Timer/Counter Synchronization Mode

Writing the TSM bit to one activates the Timer/Counter Synchronization mode. In this mode, the value that is written to the PSRASY and PSRSYNC bits is kept, hence keeping the corresponding prescaler reset signals asserted. This ensures that the corresponding Timer/Counters are halted and can be configured to the same value without the risk of one of them advancing during configuration. When the TSM bit is written to zero, the PSRASY and PSRSYNC bits are cleared by hardware, and the Timer/ Counters start counting simultaneously.

### Bit 1 – PSRASY: Prescaler Reset Timer/Counter2

When this bit is one, the Timer/Counter2 prescaler will be reset. This bit is normally cleared immediately by hardware. If the bit is written when Timer/Counter2 is operating in asynchronous mode, the bit will remain one until the prescaler has been reset. The bit will not be cleared by hardware if the TSM bit is set.

#### Bit 0 – PSRSYNC: Prescaler Reset

When this bit is one, Timer/Counter1 and Timer/Counter0 prescaler will be Reset. This bit is normally cleared immediately by hardware, except if the TSM bit is set. Note that Timer/Counter1 and Timer/ Counter0 share the same prescaler and a reset of this prescaler will affect both timers.

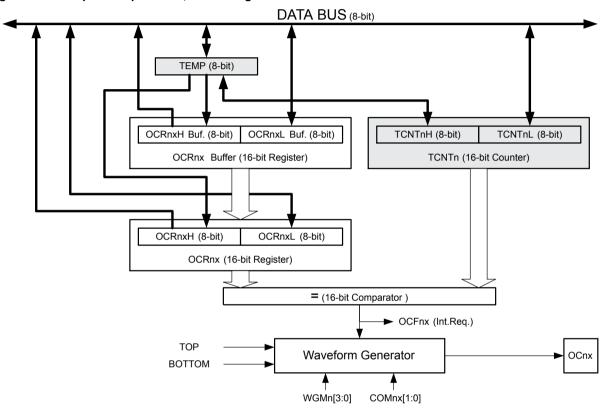

bits. The TOP and BOTTOM signals are used by the Waveform Generator for handling the special cases of the extreme values in some modes of operation, see Modes of Operation.

A special feature of Output Compare unit A allows it to define the Timer/Counter TOP value (i.e., counter resolution). In addition to the counter resolution, the TOP value defines the period time for waveforms generated by the Waveform Generator.

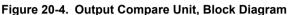

Below is a block diagram of the Output Compare unit. The elements of the block diagram that are not directly a part of the Output Compare unit are gray shaded.

**Note:** The "n" in the register and bit names indicates the device number (n = 1 for Timer/Counter 1), and the "x" indicates Output Compare unit (A/B).

The OCR1x Register is double buffered when using any of the twelve Pulse Width Modulation (PWM) modes. For the Normal and Clear Timer on Compare (CTC) modes of operation, the double buffering is disabled. The double buffering synchronizes the update of the OCR1x Compare Register to either TOP or BOTTOM of the counting sequence. The synchronization prevents the occurrence of odd-length, non-symmetrical PWM pulses, thereby making the output glitch-free.

When double buffering is enabled, the CPU has access to the OCR1x Buffer Register. When double buffering is disabled, the CPU will access the OCR1x directly.

The content of the OCR1x (Buffer or Compare) Register is only changed by a write operation (the Timer/ Counter does not update this register automatically as the TCNT1 and ICR1 Register). Therefore OCR1x is not read via the high byte temporary register (TEMP). However, it is good practice to read the low byte first as when accessing other 16-bit registers. Writing the OCR1x Registers must be done via the TEMP Register since the compare of all 16 bits is done continuously. The high byte (OCR1xH) has to be written first. When the high byte I/O location is written by the CPU, the TEMP Register will be updated by the value written. Then when the low byte (OCR1xL) is written to the lower eight bits, the high byte will be

# 20.14.11. Output Compare Register 1 B High byte

|        | Name:<br>Offset:<br>Reset:<br>Property | OCR1BH<br>0x8B<br>0x00<br>7: - |     |      |         |     |     |     |   |

|--------|----------------------------------------|--------------------------------|-----|------|---------|-----|-----|-----|---|

| Bit    | 7                                      | 6                              | 5   | 4    | 3       | 2   | 1   | 0   |   |

|        |                                        |                                |     | OCR1 | BH[7:0] |     |     |     | ] |

| Access | R/W                                    | R/W                            | R/W | R/W  | R/W     | R/W | R/W | R/W | - |

| Reset  | 0                                      | 0                              | 0   | 0    | 0       | 0   | 0   | 0   |   |

Bits 7:0 – OCR1BH[7:0]: Output Compare 1 B High byte Refer to OCR1AL.

compare match will be missed, resulting in incorrect waveform generation. Similarly, do not write the TCNT2 value equal to BOTTOM when the counter is downcounting.

The setup of the OC2x should be performed before setting the Data Direction Register for the port pin to output. The easiest way of setting the OC2x value is to use the Force Output Compare (FOC2x) strobe bit in Normal mode. The OC2x Register keeps its value even when changing between Waveform Generation modes.

Be aware that the COM2x[1:0] bits are not double buffered together with the compare value. Changing the COM2x[1:0] bits will take effect immediately.

# 22.6. Compare Match Output Unit

The Compare Output mode (COM2x[1:0]) bits have two functions. The Waveform Generator uses the COM2x[1:0] bits for defining the Output Compare (OC2x) state at the next compare match. Also, the COM2x[1:0] bits control the OC2x pin output source. The following figure shows a simplified schematic of the logic affected by the COM2x[1:0] bit setting. The I/O Registers, I/O bits, and I/O pins in the figure are shown in bold. Only the parts of the general I/O Port Control Registers (DDR and PORT) that are affected by the COM2x[1:0] bits are shown. When referring to the OC2x state, the reference is for the internal OC2x Register, not the OC2x pin.

The general I/O port function is overridden by the Output Compare (OC2x) from the Waveform Generator if either of the COM2x1:0 bits are set. However, the OC2x pin direction (input or output) is still controlled by the Data Direction Register (DDR) for the port pin. The Data Direction Register bit for the OC2x pin (DDR\_OC2x) must be set as output before the OC2x value is visible on the pin. The port override function is independent of the Waveform Generation mode.

The design of the Output Compare pin logic allows initialization of the OC2x state before the output is enabled. Note that some COM2x[1:0] bit settings are reserved for certain modes of operation. See Register Description.

### **Related Links**

Modes of Operation on page 137

### 22.11.5. TC2 Output Compare Register B

|        | Name:    | OCR2B |     |      |        |     |     |     |

|--------|----------|-------|-----|------|--------|-----|-----|-----|

|        | Offset:  | 0xB4  |     |      |        |     |     |     |

|        | Reset:   | 0x00  |     |      |        |     |     |     |

|        | Property | :-    |     |      |        |     |     |     |

|        |          |       |     |      |        |     |     |     |

|        |          |       |     |      |        |     |     |     |

| Bit    | 7        | 6     | 5   | 4    | 3      | 2   | 1   | 0   |

|        |          |       |     | OCR2 | B[7:0] |     |     |     |

| Access | R/W      | R/W   | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0        | 0     | 0   | 0    | 0      | 0   | 0   | 0   |

### Bits 7:0 - OCR2B[7:0]: Output Compare 2 B

The Output Compare Register B contains an 8-bit value that is continuously compared with the counter value (TCNT2). A match can be used to generate an Output Compare interrupt, or to generate a waveform output on the OC2B pin.

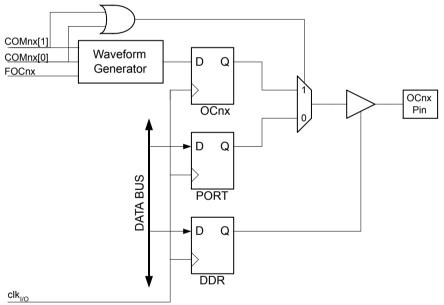

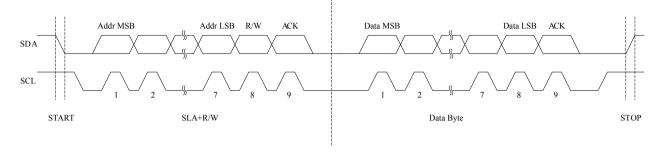

Figure 26-4. Address Packet Format

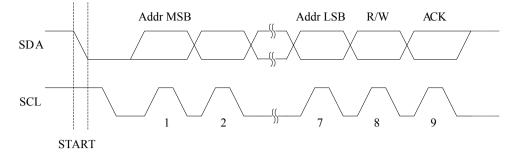

### 26.3.4. Data Packet Format

All data packets transmitted on the TWI bus are nine bits long, consisting of one data byte and an acknowledge bit. During a data transfer, the Master generates the clock and the START and STOP conditions, while the Receiver is responsible for acknowledging the reception. An Acknowledge (ACK) is signalled by the Receiver pulling the SDA line low during the ninth SCL cycle. If the Receiver leaves the SDA line high, a NACK is signalled. When the Receiver has received the last byte, or for some reason cannot receive any more bytes, it should inform the Transmitter by sending a NACK after the final byte. The MSB of the data byte is transmitted first.

#### 26.3.5. Combining Address and Data Packets into a Transmission

A transmission basically consists of a START condition, a SLA+R/W, one or more data packets and a STOP condition. An empty message, consisting of a START followed by a STOP condition, is illegal. Note that the "Wired-ANDing" of the SCL line can be used to implement handshaking between the Master and the Slave. The Slave can extend the SCL low period by pulling the SCL line low. This is useful if the clock speed set up by the Master is too fast for the Slave, or the Slave needs extra time for processing between the data transmissions. The Slave extending the SCL low period will not affect the SCL high period, which is determined by the Master. As a consequence, the Slave can reduce the TWI data transfer speed by prolonging the SCL duty cycle.

The following figure depicts a typical data transmission. Note that several data bytes can be transmitted between the SLA+R/W and the STOP condition, depending on the software protocol implemented by the application software.

Figure 26-6. Typical Data Transmission

## 26.4. Multi-master Bus Systems, Arbitration, and Synchronization

The TWI protocol allows bus systems with several masters. Special concerns have been taken in order to ensure that transmissions will proceed as normal, even if two or more masters initiate a transmission at the same time. Two problems arise in multi-master systems:

- An algorithm must be implemented allowing only one of the masters to complete the transmission. All other masters should cease transmission when they discover that they have lost the selection process. This selection process is called arbitration. When a contending master discovers that it has lost the arbitration process, it should immediately switch to Slave mode to check whether it is being addressed by the winning master. The fact that multiple masters have started transmission at the same time should not be detectable to the slaves, i.e. the data being transferred on the bus must not be corrupted.

- Different masters may use different SCL frequencies. A scheme must be devised to synchronize the serial clocks from all masters, in order to let the transmission proceed in a lockstep fashion. This will facilitate the arbitration process.

The wired-ANDing of the bus lines is used to solve both these problems. The serial clocks from all masters will be wired-ANDed, yielding a combined clock with a high period equal to the one from the Master with the shortest high period. The low period of the combined clock is equal to the low period of the Master with the longest low period. Note that all masters listen to the SCL line, effectively starting to count their SCL high and low time-out periods when the combined SCL line goes high or low, respectively.

|   | Assembly Code Example                                                                                     | C Example                                                                                                                   | Comments                                                                                                         |

|---|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| 7 | in r16,TWSR0<br>andi r16, 0xF8<br>cpi r16, MT_DATA_ACK<br>brne ERROR                                      | <pre>if ((TWSR0 &amp; 0xF8) != MT_DATA_ACK) ERROR();</pre>                                                                  | Check value of TWI Status Register. Mask<br>prescaler bits. If status different from<br>MT_DATA_ACK go to ERROR. |

|   | <pre>ldi r16, (1&lt;<twint)  (1<<twen) ="" (1<<twsto)="" out="" pre="" r16<="" twcr0,=""></twint) ></pre> | TWCR0 = (1< <twint) <br>(1&lt;<twen) (1<<twsto);< td=""><td>Transmit STOP condition.</td></twen) (1<<twsto);<></twint) <br> | Transmit STOP condition.                                                                                         |

# 26.7. Transmission Modes

The TWI can operate in one of four major modes:

- Master Transmitter (MT)

- Master Receiver (MR)

- Slave Transmitter (ST)

- Slave Receiver (SR)

Several of these modes can be used in the same application. As an example, the TWI can use MT mode to write data into a TWI EEPROM, MR mode to read the data back from the EEPROM. If other masters are present in the system, some of these might transmit data to the TWI, and then SR mode would be used. It is the application software that decides which modes are legal.

The following sections describe each of these modes. Possible status codes are described along with figures detailing data transmission in each of the modes. These figures use the following abbreviations:

| _    |                                         |

|------|-----------------------------------------|

| S    | START condition                         |

| Rs   | REPEATED START condition                |

| R    | Read bit (high level at SDA)            |

| W    | Write bit (low level at SDA)            |

| A    | Acknowledge bit (low level at SDA)      |

| Ā    | Not acknowledge bit (high level at SDA) |

| Data | 8-bit data byte                         |

| Р    | STOP condition                          |

| SLA  | Slave Address                           |

**Circles** are used to indicate that the TWINT Flag is set. The numbers in the circles show the status code held in TWSRn, with the prescaler bits masked to zero. At these points, actions must be taken by the application to continue or complete the TWI transfer. The TWI transfer is suspended until the TWINT Flag is cleared by software.

When the TWINT Flag is set, the status code in TWSRn is used to determine the appropriate software action. For each status code, the required software action and details of the following serial transfer are given below in the Status Code table for each mode. Note that the prescaler bits are masked to zero in these tables.

## 27.3.2. Analog Comparator Control and Status Register

When addressing I/O Registers as data space using LD and ST instructions, the provided offset must be used. When using the I/O specific commands IN and OUT, the offset is reduced by 0x20, resulting in an I/O address offset within 0x00 - 0x3F.

Name: ACSR Offset: 0x50 Reset: N/A Property: When addressing as I/O Register: address offset is 0x30

| Bit    | 7   | 6    | 5   | 4   | 3    | 2    | 1     | 0     |

|--------|-----|------|-----|-----|------|------|-------|-------|

|        | ACD | ACBG | ACO | ACI | ACIE | ACIC | ACIS1 | ACIS0 |

| Access | R/W | R/W  | R   | R/W | R/W  | R/W  | R/W   | R/W   |

| Reset  | 0   | 0    | 0   | 0   | 0    | 0    | 0     | 0     |

### Bit 7 – ACD: Analog Comparator Disable

When this bit is written logic one, the power to the Analog Comparator is switched off. This bit can be set at any time to turn off the Analog Comparator. This will reduce power consumption in Active and Idle mode. When changing the ACD bit, the Analog Comparator Interrupt must be disabled by clearing the ACIE bit in ACSR. Otherwise an interrupt can occur when the bit is changed.

### Bit 6 – ACBG: Analog Comparator Bandgap Select

When this bit is set, a fixed bandgap reference voltage replaces the positive input to the Analog Comparator. When this bit is cleared, AINO is applied to the positive input of the Analog Comparator. When the bandgap reference is used as input to the Analog Comparator, it will take a certain time for the voltage to stabilize. If not stabilized, the first conversion may give a wrong value.

### Bit 5 – ACO: Analog Comparator Output

The output of the Analog Comparator is synchronized and then directly connected to ACO. The synchronization introduces a delay of 1 - 2 clock cycles.

### Bit 4 – ACI: Analog Comparator Interrupt Flag

This bit is set by hardware when a comparator output event triggers the interrupt mode defined by ACIS1 and ACIS0. The Analog Comparator interrupt routine is executed if the ACIE bit is set and the I-bit in SREG is set. ACI is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ACI is cleared by writing a logic one to the flag.

### Bit 3 – ACIE: Analog Comparator Interrupt Enable

When the ACIE bit is written logic one and the I-bit in the Status Register is set, the Analog Comparator interrupt is activated. When written logic zero, the interrupt is disabled.

### Bit 2 – ACIC: Analog Comparator Input Capture Enable

When written logic one, this bit enables the input capture function in Timer/Counter1 to be triggered by the Analog Comparator. The comparator output is in this case directly connected to the input capture front-end logic, making the comparator utilize the noise canceler and edge select features of the Timer/Counter1 Input Capture interrupt. When written logic zero, no connection between the Analog Comparator and the input capture function exists. To make the comparator trigger the Timer/Counter1 Input Capture interrupt, the ICIE1 bit in the Timer Interrupt Mask Register (TIMSK1) must be set.

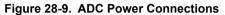

### 28.6.2. Analog Noise Canceling Techniques

Digital circuitry inside and outside the device generates EMI which might affect the accuracy of analog measurements. If conversion accuracy is critical, the noise level can be reduced by applying the following techniques:

Keep analog signal paths as short as possible. Make sure analog tracks run over the analog ground plane, and keep them well away from high-speed switching digital tracks.

1.1. The AV<sub>CC</sub> pin on the device should be connected to the digital V<sub>CC</sub> supply voltage via an LC network as shown in the figure below.

1.2. Use the ADC noise canceler function to reduce induced noise from the CPU.

1.3. If any ADC [3:0] port pins are used as digital outputs, it is essential that these do not switch while a conversion is in progress. However, using the 2-wire Interface (ADC4 and ADC5) will only affect the conversion on ADC4 and ADC5 and not the other ADC channels.

- 1. If there is no need for a Boot Loader update in the system, program the Boot Loader Lock bits to prevent any Boot Loader software updates.

- Keep the AVR RESET active (low) during periods of insufficient power supply voltage. This can be done by enabling the internal Brown-out Detector (BOD) if the operating voltage matches the detection level. If not, an external low V<sub>CC</sub> reset protection circuit can be used. If a reset occurs while a write operation is in progress, the write operation will be completed provided that the power supply voltage is sufficient.

- Keep the AVR core in Power-down sleep mode during periods of low V<sub>CC</sub>. This will prevent the CPU from attempting to decode and execute instructions, effectively protecting the SPMCSR Register and thus the Flash from unintentional writes.

#### 31.8.12. Programming Time for Flash when Using SPM

The calibrated RC Oscillator is used to time Flash accesses. The following table shows the typical programming time for Flash accesses from the CPU.

#### Table 31-6. SPM Programming Time

| Symbol                                                           | Min. Programming Time | Max. Programming Time |

|------------------------------------------------------------------|-----------------------|-----------------------|

| Flash write (Page Erase, Page Write, and write Lock bits by SPM) | 3.2ms                 | 3.4ms                 |

Note: Minimum and maximum programming time is per individual operation.

#### 31.8.13. Simple Assembly Code Example for a Boot Loader

```

;-the routine writes one page of data from RAM to Flash

; the first data location in RAM is pointed to by the Y pointer

; the first data location in Flash is pointed to by the Z-pointer

;-error handling is not included

;-the routine must be placed inside the Boot space

; (at least the Do spm sub routine). Only code inside NRWW section can

; be read during Self-Programming (Page Erase and Page Write).

;-registers used: r0, r1, temp1 (r16), temp2 (r17), looplo (r24),

; loophi (r25), spmcrval (r20)

; storing and restoring of registers is not included in the routine

; register usage can be optimized at the expense of code size

;-It is assumed that either the interrupt table is moved to the Boot

; loader section or that the interrupts are disabled.

.equ PAGESIZEB = PAGESIZE*2 ; PAGESIZEB is page size in BYTES, not words

.org SMALLBOOTSTART

Write page:

; Page Erase

ldi spmcrval, (1<<PGERS) | (1<<SPMEN)</pre>

call Do spm

```

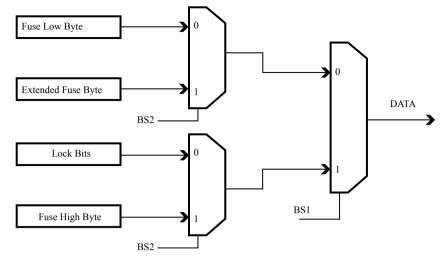

Figure 32-5. Mapping Between BS1, BS2 and the Fuse and Lock Bits During Read

### 32.7.13. Reading the Signature Bytes

The algorithm for reading the Signature bytes is as follows (Please refer to Programming the Flash for details on Command and Address loading):

- 1. Step A: Load Command "0000 1000".

- 2. Step B: Load Address Low Byte (0x00 0x02).

- 3. Set  $\overline{OE}$  to "0", and BS1 to "0". The selected Signature byte can now be read at DATA.

- 4. Set  $\overline{OE}$  to "1".

### 32.7.14. Reading the Calibration Byte

The algorithm for reading the Calibration byte is as follows (Please refer to Programming the Flash for details on Command and Address loading):

- 1. Step A: Load Command "0000 1000".

- 2. Step B: Load Address Low Byte, 0x00.

- 3. Set  $\overline{\text{OE}}$  to "0", and BS1 to "1". The Calibration byte can now be read at DATA.

- 4. Set OE to "1".

### 32.7.15. Parallel Programming Characteristics

For characteristics of the Parallel Programming, please refer to Parallel Programming Characteristics.

## 32.8. Serial Downloading

Both the Flash and EEPROM memory arrays can be programmed using the serial SPI bus while RESET is pulled to GND. The serial interface consists of pins SCK, MOSI (input) and MISO (output). After RESET is set low, the Programming Enable instruction needs to be executed first before program/erase operations can be executed.

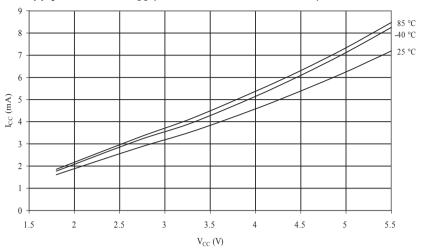

Figure 34-51. Active Supply Current vs. V<sub>CC</sub> (Internal RC Oscillator, 8MHz)

### 34.2.2. Idle Supply Current

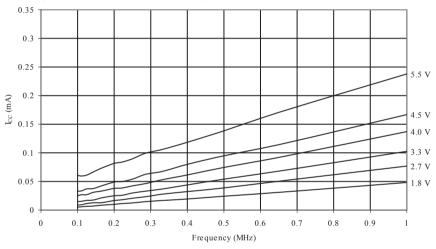

Figure 34-52. Idle Supply Current vs. Low Frequency (0.1MHz - 1.0MHz)

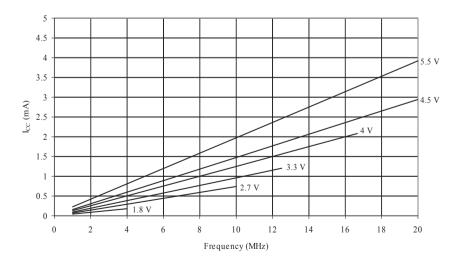

Figure 34-53. Idle Supply Current vs. Frequency (1MHz - 20MHz)

Figure 34-109. ATmega168P/PV: I/O Pin Pull-up Resistor Current vs. Input Voltage (V<sub>CC</sub> = 5V)

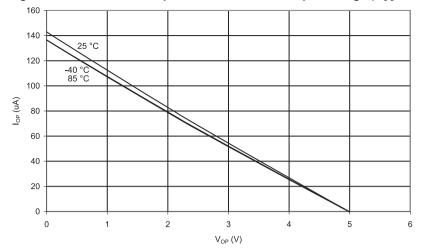

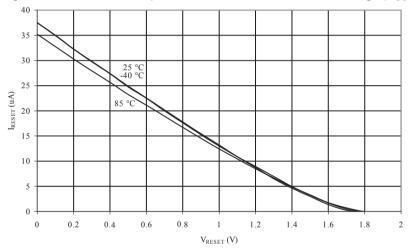

Figure 34-110. ATmega168P/PV: Reset Pull-up Resistor Current vs. Reset Pin Voltage (V<sub>CC</sub> = 1.8V)

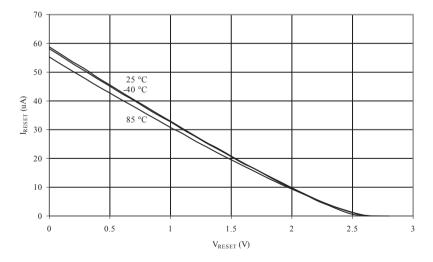

Figure 34-111. ATmega168P/PV: Reset Pull-up Resistor Current vs. Reset Pin Voltage (V<sub>CC</sub> = 2.7V)

## 39.7. Rev. 8025J-05/09

- 1. Removed the "About" section.

- 2. Removed ATmega328P device and its reference from the data sheet.

- 3. Editorial updates.

### 39.8. Rev. 8025I-02/09

Removed "preliminary" from ATmega48P/88P/168P.

### 39.9. Rev. 8025H-02/09

- 1. Added Power-save Maximum values and footnote to ATmega48P DC Characteristics Current Consumption.

- 2. Added Power-save Maximum values and footnote to ATmega88P DC Characteristics Current Consumption.

- Added Power-save Maximum values and footnote to ATmega168P DC Characteristics Current Consumption.

- 4. Added errata for revision A, Rev. A.

## 39.10. Rev. 8025G-01/09

- 1. ATmega48P/88P not recommended for new designs.

- 2. Updated the footnote Note1 of Table 13-3.

- 3. Updated Table 13-5 by removing a footnote Note1.

- 4. Updated Calibrated Internal RC Oscillator by removing a footnote Note1.

- 5. Updated the footnote Note1 of Table 13-13.

- 6. Updated the footnote Note2 of ATmega48P DC Characteristics Current Consumption and removed TBD from the table.

- 7. Updated the footnote Note2 of ATmega88P DC Characteristics Current Consumption and removed TBD from the table.

- 8. Updated the footnote Note2 of ATmega168P DC Characteristics Current Consumption and removed TBD from the table.

- 9. Updated the footnote Note2 of the "" on page 319 and removed TBD from the table.

- 10. Updated the footnote Note1 of Table 33-9.

- 11. Replaced Figure 34-69 by a correct one.

- 12. Replaced Figure 34-137 by a correct one.

- 13. 13. Updated Errata.

- 14. Updated MCUCR.

- 15. Updated TCCR2B.

### 39.11. Rev. 8025F-08/08

- 1. Updated Register Summary with Power-save numbers.

- 2. Added ATmega328P "Standby Supply Current" on page 408.