Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | SmartCard, SPI, UART/USART, USB                                            |

| Peripherals                | LED, POR, WDT                                                              |

| Number of I/O              | 46                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-LQFP                                                                    |

| Supplier Device Package    | 64-VQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c5122d-rdrim |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

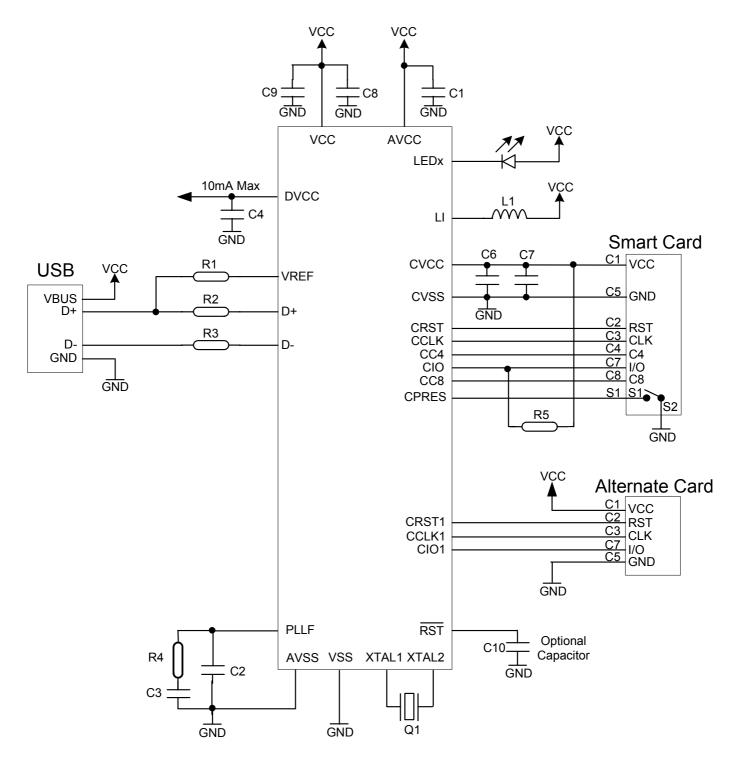

# USB Smart Card Reader Using the AT83C5123 Version

| 7             | 6            | 5               | 4                                                                                                                                                                                | 3                                                                                | 2 | 1 | 0 |  |  |  |

|---------------|--------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---|---|---|--|--|--|

| -             | -            | -               | -                                                                                                                                                                                | RPS                                                                              | - | - | - |  |  |  |

| Bit<br>Number | Bit<br>Mnemo | nic Descr       | Description                                                                                                                                                                      |                                                                                  |   |   |   |  |  |  |

| 7 - 4         | -            |                 | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not change these b                                                                                          |                                                                                  |   |   |   |  |  |  |

| 3             | RPS          | Set to<br>Clear | <b>CRAM Memory Mapping Bit</b><br>Set to map the CRAM memory during MOVX instructions<br>Clear to map the XRAM memory during MOVX.<br>This bit has priority over the EXTRAM bit. |                                                                                  |   |   |   |  |  |  |

| 2-0           | -            |                 |                                                                                                                                                                                  | Reserved<br>The value read from this bit is indeterminate. Do not change these b |   |   |   |  |  |  |

#### Table 8. CRAM Configuration Register - RCON (D1h)

Reset Value = XXXX 0XXXb

#### AT8xC5122's CRAM and E2PROM Versions

The AT8xC5122's CRAM and E2PROM versions implements :

- 32 KB of ROM mapped from 8000 to FFFF in which is embedded a bootloader for In-System Programming feature

- 32 KB of CRAM (Code RAM), a volatile program memory mapped from 0000 to 7FFF

In CRAM versions only :

- 512 bytes of E2PROM can be optionally implemented to store permanent data

In E2PROM version :

- 32KB of E2PROM are implemented to store permanent code

#### Warnings :

- some bytes of user program memory space are reserved for bootloader configuration. Depending on the configuration, up to 256 bytes of code may be not available for the user code from 7F00h location. Refer to bootloader datasheet for further details.

- Port P3.7 may be used by the bootloader as a hardware condition at reset to select the In-System Programming mode. Once the bootloader has started, the P3.7 Port is no more used.

#### Table 18. SCIB SFRs

| Mnemonic | Add | Name                                       | 7                    | 6 | 5 | 4 | 3    | 2     | 1 | 0 |

|----------|-----|--------------------------------------------|----------------------|---|---|---|------|-------|---|---|

| SCICLK   |     | Smart Card Frequency<br>Prescaler Register | XTSCS <sup>(1)</sup> |   |   |   | SCIC | LK5-0 |   |   |

Note: 1. Only for AT8xC5122

#### Table 19. DC/DC SFRs

| Mnemonic | Add | Name                               | 7    | 6      | 5    | 4       | 3 | 2    | 1      | 0 |

|----------|-----|------------------------------------|------|--------|------|---------|---|------|--------|---|

| DCCKPS   | BFh | DC/DC Converter Reload<br>Register | MODE | OVFADJ | BOOS | ST[1-0] |   | DCCk | (PS3-0 |   |

#### Table 20. Keyboard SFRs

| Mnemonic            | Add | Name                                | 7         | 6 | 5 | 4   | 3      | 2 | 1 | 0 |

|---------------------|-----|-------------------------------------|-----------|---|---|-----|--------|---|---|---|

| KBF <sup>(1)</sup>  | 9Eh | Keyboard Flag Register              |           |   |   | KBE | E7 - 0 |   |   |   |

| KBE <sup>(1)</sup>  | 9Dh | Keyboard Input Enable<br>Register   | KBF7 - 0  |   |   |     |        |   |   |   |

| KBLS <sup>(1)</sup> | 9Ch | Keyboard Level Selector<br>Register | KBLS7 - 0 |   |   |     |        |   |   |   |

Note: 1. Only for AT8xC5122

#### Table 21. SPI SFRs

| Mnemonic             | Add | Name                                 | 7    | 6    | 5     | 4    | 3     | 2    | 1    | 0    |

|----------------------|-----|--------------------------------------|------|------|-------|------|-------|------|------|------|

| SPCON <sup>(1)</sup> | C3h | Serial Peripheral Control            | SPR2 | SPEN | SSDIS | MSTR | CPOL  | CPHA | SPR1 | SPR0 |

| SPSTA <sup>(1)</sup> | C4h | Serial Peripheral Status-<br>Control | SPIF | WCOL |       | MODF |       |      |      |      |

| SPDAT <sup>(1)</sup> | C5h | Serial Peripheral Data               |      |      |       | R7   | ′ - 0 |      |      |      |

Notes: 1. Only for AT8xC5122

#### Table 22. USB SFRs

| Mnemonic | Add | Name                           | 7    | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|----------|-----|--------------------------------|------|---------|---------|---------|---------|---------|---------|---------|

| USBCON   | BCh | USB Global Control             | USBE | SUSPCLK | SDRMWUP | DETACH  | UPRSM   | RMWUPE  | CONFG   | FADDEN  |

| USBADDR  | C6h | USB Address                    | FEN  |         |         |         | UADD6-0 |         |         |         |

| USBINT   | BDh | USB Global Interrupt           |      |         | WUPCPU  | EORINT  | SOFINT  |         |         | SPINT   |

| USBIEN   | BEh | USB Global Interrupt<br>Enable |      |         | EWUPCPU | EEORINT | ESOFINT |         |         | ESPINT  |

| UEPNUM   | C7h | USB Endpoint Number            |      |         |         |         |         | EPN     | JM3-0   |         |

| UEPCONX  | D4h | USB Endpoint X Control         | EPEN | NAKIEN  | NAKOUT  | NAKIN   | DTGL    | EPDIR   | EPTYPE1 | EPTYPE0 |

| UEPSTAX  | CEh | USB Endpoint X Status          | DIR  | RXOUTB1 | STALLRQ | TXRDY   | STL/CRC | RXSETUP | RXOUTB0 | TXCMP   |

| UEPRST   | D5h | USB Endpoint Reset             |      | EP6RST  | EP5RST  | EP4RST  | EP3RST  | EP2RST  | EP1RST  | EP0RST  |

| UEPINT   | F8h | USB Endpoint Interrupt         |      | EP6INT  | EP5INT  | EP4INT  | EP3INT  | EP2INT  | EP1INT  | EP0INT  |

# Registers

#### Table 36. Port Mode Register 0 - PMOD0 (91h) for AT8xC5122

| 7          | 6         | 5                           | 4                                                                                                                                                                            | 3                                                      | 2              | 1                | 0        |  |  |  |

|------------|-----------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------|------------------|----------|--|--|--|

| P3C1       | P3C0      | P2C1                        | P2C0                                                                                                                                                                         | CPRESRES                                               | -              | P0C1             | P0C0     |  |  |  |

| Bit Number | Bit Mnemo | onic Descr                  | iption                                                                                                                                                                       |                                                        |                |                  |          |  |  |  |

| 7 - 6      | P3C1-P3   | 00 Qu<br>C0 01 Pus<br>10 Ou | asi bi-direction                                                                                                                                                             | d                                                      | ole to P3.0, F | v3.1, P3.3, P3.  | .4 only) |  |  |  |

| 5-4        | P2C1-P2   | 00 Qu<br>C0 01 Pus<br>10 Ou | Port 2 Configuration bits<br>0 Quasi bi-directional<br>1 Push-pull<br>0 Output Low Speed<br>1 Input with weak pull-down                                                      |                                                        |                |                  |          |  |  |  |

| 3          | CPRESR    | ES Cleare                   |                                                                                                                                                                              | -up resistor<br>ne internal 100K<br>e internal pull-up | • •            |                  |          |  |  |  |

| 2          | -         | <b>Reser</b><br>The va      |                                                                                                                                                                              | this bit is indete                                     | rminate. Do r  | ot set this bit. |          |  |  |  |

| 1-0        | P0C1-P0   | 00 C5<br>C0 01 Re<br>10 Ou  | The value read from this bit is indeterminate. Do not set this bit.<br>Port 0 Configuration bits<br>00 C51 Standard P0<br>01 Reserved<br>10 Output Low Speed<br>11 Push-pull |                                                        |                |                  |          |  |  |  |

Reset Value = 0000 0x00b

### Table 37. Port Mode Register 0 - PMOD0 (91h) for AT83C5123

| 7          | 6         | 5                             | 4                                                                                                                                                                     | 3                 | 2            | 1              | 0        |  |  |

|------------|-----------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------|----------------|----------|--|--|

| P3C1       | P3C0      | -                             | -                                                                                                                                                                     | CPRESRES          | -            | -              | -        |  |  |

| Bit Number | Bit Mnemo | onic Descri                   | Description                                                                                                                                                           |                   |              |                |          |  |  |

| 7 - 6      | P3C1-P3   | 00 Qua<br>C0 01 Pus<br>10 Out | Port 3 Configuration bits (Applicable to P3.0, P3.1, P3.3, P3.4 only)<br>00 Quasi bi-directional<br>01 Push-pull<br>10 Output Low Speed<br>11 Input with weak pull-up |                   |              |                |          |  |  |

| 5-4        |           |                               | Reserved<br>The value read from these bits are indeterminate. Do not set these bit.                                                                                   |                   |              |                |          |  |  |

| 3          | CPRESR    | ES Cleare                     | Card Presence Pull-up resistor<br>Cleared to connect the internal 100K pull-up<br>Set to disconnect the internal pull-up                                              |                   |              |                |          |  |  |

| 2-0        | -         | <b>Reserv</b><br>The va       |                                                                                                                                                                       | these bits are in | determinate. | Do not set the | ese bit. |  |  |

Reset Value = 00xx 0xxxb

# **AMEL**

# Smart Card Interface Block (SCIB)

The SCIB provides all signals to interface directly with a smart card. The compliance with the ISO7816, EMV'2000, GSM and WHQL standards has been certified.

Both synchronous (e.g. memory card) and asynchronous smart cards (e.g. microprocessor card) are supported. The component supplies the different voltages requested by the smart card. The power off sequence is directly managed by the SCIB.

The card presence switch of the smart card connector is used to detect card insertion or card removal. In case of card removal, the SCIB de-activates the smart card using the de-activation sequence. An interrupt can be generated when a card is inserted or removed.

Any malfunction is reported to the microcontroller (interrupt + control register).

The different operating modes are configured by internal registers.

- Support of ISO/IEC 7816

- character mode

- one transmit/receive buffer

- 11 bits ETU counter

- 9 bits guard time counter

- 32 bits waiting time counter

- Auto character repetition on error signal detection in transmit mode

- Auto error signal generation on parity error detection in receive mode

- Power on and power off sequence generation

- Manual mode to drive directly the card I/O

| R     |

|-------|

| · · · |

| ATR                          | Answer To Reset. Response from the ICC to a Reset initiated by the Terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F and D                      | F = Clock Rate Conversion Factor, D = Bit rate adjustment factor. ETU is defined as :<br>ETU = $F/(D^*f)$ with f = Card Clock frequency. If f is in Hertz, ETU is in second. F and D<br>are available in the ATR (byte TA1). The default values are F=372, D=1.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Guard Time                   | The time between 2 leading edges of the start bit of 2 consecutive characters is com-<br>prised of the character duration (10) plus the guard time. Be aware that the Guard Time<br>counter and the Guard Time registers in the AT8xC5122/23 consider the time between 2<br>consecutive characters. So the equation is Guard Time Counter = Guard Time + 10. In<br>other words, the Guard Time is the number of Stop Bits between 2 characters sent in<br>the same direction.                                                                                                                                                                                                                                              |

| Extra Guard Time             | ISO IEC 7816-3 and EMV introduce the Extra Guard time to be added to the minimum Guard Time. Extra Guard Time only apply to consecutive characters sent by the terminal to the ICC. The TC1 byte in the ATR define the number N. For N=0 the character to character duration is 12 ETUs. For N=254 the character to character duration is 266. For N=255 (special case) The minimum character to character duration is to be used : 12 for T=0 protocol and 11 for T=1 protocol.                                                                                                                                                                                                                                           |

| Block Guard Time             | The time between the leading edges of 2 consecutive characters sent in opposit direc-<br>tion. ISO IEC 7816-3 and EMV recommend a fixed Block Guard Time of 22 ETUs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Work Waiting Time (WWT)      | In T=0 protocol WWT is the interval between the leading edge of any character sent by the ICC, and the leading edge of the previous character sent either by the ICC or the Terminal. If no character is received by the terminal after WWTmax time, the Terminal initiates a De-Activation Sequence.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Character Waiting Time (CWT) | In T=1 protocol CWT is the interval between the leading edge of 2 consecutive charac-<br>ters sent by the ICC. If the next character is not received by the Terminal after CWTmax<br>time, the Terminal initiates a De-Activation Sequence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Block Waiting Time (BWT)     | In T=1 protocol BWT is the interval between the leading edge of the start bit of the last character sent by the Terminal that gives the right to sent to the ICC, and the leading edge of the start bit of the first character sent by the ICC. If the first character from the ICC is not received by the Terminal after BWTmax time, the Terminal initiates a De-Activation Sequence.                                                                                                                                                                                                                                                                                                                                    |

| Waiting Time Extention (WTX) | In T=1 protocol the ICC can request a Waiting Time Extension with a S(WTX request) request. The Terminal should acknowlege it. The Waiting time between the leading edge of the start bit of the last character sent by the Terminal that gives the right to sent to the ICC, and the leading edge of the start bit of the start bit of the ICC will be BWT*WTX ETUS.                                                                                                                                                                                                                                                                                                                                                      |

| Parity error in T=0 protocol | In T=0 protocol, a Terminal (respectively an ICC) detecting a parity error while receiving a character shall force the Card IO line at 0 starting at 10.5 ETUs, thus reducing the first Guard bit by half the time. The Terminal (respectively an ICC) shall maintain a 0 for 1 ETU min and 2 ETUs max (according to ISO IEC) or to 2 ETUs (according to EMV). The ICC (respectively a Terminal) shall monitor the Card IO to detect this error signal then attempt to repeat the character. According to EMV, following a parity error the character can be repeated one time, if parity error is detected again this procedure can be repeated 3 more times. The same character can be transmitted 5 times in total. ISO |

64 AT83R5122, AT8xC5122/23

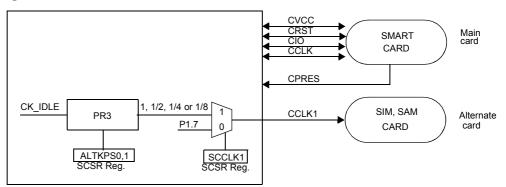

# **Alternate Card**

A second card named 'Alternate Card' can be controlled.

The Clock signal CCLK1 can be adapted to the XTAL frequency. Thanks to the clock prescaler which can divide the frequency by 1, 2, 4 or 8. The bits ALTKPS0 and ALTKPS1 in SCSR Register are used to set this factor.

#### Figure 44. Alternate Card

#### Registers

There are fifteen registers to control the SCIB macro-cell. They are described from Table 58 to Table 45.

Some of the register widths are greater than a byte. Despite the 8 bits access provided by the BIU, the address mapping of this kind of register respects the following rule :

The Low significant byte register is implemented at the higher address.

This implementation makes access to these registers easier when using high level programming languages (C,C++).

# Table 45. Smart Card Contacts Register - SCCON (S:ACh, SCRS=0)

| 7          | 6            | 5                                                                                    | 4                                                                                    | 3                                            | 2                                                                                            | 1                                             | 0                |

|------------|--------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------|------------------|

| CLK        | -            | CARDC8                                                                               | CARDC4                                                                               | CARDIO                                       | CARDCLK                                                                                      | CARDRST                                       | CARDVCC          |

| Bit Number | Bit Mnemonic | Description                                                                          |                                                                                      |                                              |                                                                                              |                                               |                  |

| 7          | CLK          | Set this bit to us                                                                   | use the Card CLK<br>se CK_XTAL1 or Cl                                                | K_PLL signals for (                          | below) to drive Card<br>CK_ISO to drive the<br>CLK pin when switc                            | Card CLK pin (CC                              | EK = P1.4 pin)   |

| 6          | -            | Reserved<br>This bit can be                                                          | changed by softwa                                                                    | re but the read valu                         | ue is indeterminate.                                                                         |                                               |                  |

| 5          | CARDC8       | Set this bit to se<br>The CC8 pin ca                                                 | •                                                                                    | e Card C8 pin (CC<br>eudo bi-directional I   | • •                                                                                          |                                               | in               |

| 4          | CARDC4       | Set this bit to se<br>The CC4 pin ca                                                 | •                                                                                    | e Card C4 pin (CC<br>eudo bi-directional l   |                                                                                              |                                               | 'n               |

| 3          | CARDIO       | pseudo bi-direc<br>To read from Cl<br>value<br>To write in ClO<br>bit to write a 0 i | tional port :<br>O (P1.0) port pin :<br>(P1.0) port pin : set<br>n CIO (P1.0) port p | set CARDIO (P1.0)<br>CARDIO (P1.0) bi<br>in. | les the use of the C<br>) bit then read CARI<br>t to write a 1 in CIO<br>t be true to change | DIO (P1.0) bit to ha<br>(P1.0) port pin , cle | ave the CIO port |

| 2          | CARDCLK      |                                                                                      |                                                                                      | •                                            | value of this bit is d<br>t be true to change                                                |                                               |                  |

| 1          | CARDRST      | Set this bit to se                                                                   | drive a low level or<br>et a high level on th<br>RDOK=1 (SCISR.4                     | e Card RST pin.                              | t be true to change                                                                          | the state of Card R                           | ST pin           |

| 0          | CARDVCC      | effect while this                                                                    | desactivate the Ca<br>bit is cleared.                                                |                                              | t its power-off. The                                                                         |                                               | -                |

Reset Value = 0X00 0000b

#### Table 49. Smart Card Selection Register - SCSR (S:ABh)

| 7          | 6            | 5                                               | 4                                                                                                                          | 3                                                                                   | 2                    | 1                   | 0    |

|------------|--------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------|---------------------|------|

| -          | BGTEN        | -                                               | CREPSEL                                                                                                                    | ALTKPS1                                                                             | ALTKPS0              | SCCLK1              | SCRS |

| Bit Number | Bit Mnemonic | Description                                     |                                                                                                                            |                                                                                     |                      |                     |      |

| 7          | -            | Reserved<br>The value read                      | from this bit is inde                                                                                                      | terminate. Do not ch                                                                | nange this bit.      |                     |      |

| 6          | BGTEN        | received from th counter is done                | elect the minimum in<br>the ICC and the first<br>on the rising edge                                                        | nterval between the<br>character sent by th<br>of the BGTEN.<br>num time between re | ne Terminal. The tra | nsfer of GT[8-0] va |      |

| 5          | -            | Reserved<br>The value read                      | from this bit is inde                                                                                                      | terminate. Do not ch                                                                | nange this bit.      |                     |      |

| 4          | CREPSEL      | Clear this bit to EMV)                          |                                                                                                                            | smission (1 original -<br>nission (1 original + :                                   | . ,                  |                     |      |

| 3-2        | ALTKPS1:0    | 00 ALTKPS = 0<br>01 ALTKPS = 1<br>10 ALTKPS = 2 | Clock prescaler factor<br>prescaler factor<br>prescaler factor<br>prescaler factor<br>prescaler factor<br>prescaler factor | equals 1<br>equals 2<br>equals 4 (reset valu                                        | e)                   |                     |      |

| 1          | SCCLK1       |                                                 | •                                                                                                                          | ock for CCLK1 (P1.7                                                                 | ') pin               |                     |      |

| 0          | SCRS         |                                                 | gister Selection<br>elects which set of                                                                                    | the SCIB registers is                                                               | s accessed.          |                     |      |

Reset Value = X000 1000b

### Table 50. Smart Card Transmit / Receive Buffer - SCIBUF (S:AA)

| 7          | 6            | 5                   | 4                                                                | 3                                                                  | 2                  | 1 | 0 |

|------------|--------------|---------------------|------------------------------------------------------------------|--------------------------------------------------------------------|--------------------|---|---|

| -          | -            | -                   | -                                                                | -                                                                  | -                  | - | - |

| Bit Number | Bit Mnemonic | Description         |                                                                  |                                                                    |                    |   |   |

| -          | -            | The bits are sorted | e written in the buf<br>and copied on the<br>ved from I/O pin is | fer to be transmitted<br>I/O pin versus the<br>ready to be read wh | active convention. |   |   |

Reset Value = 0000 0000b

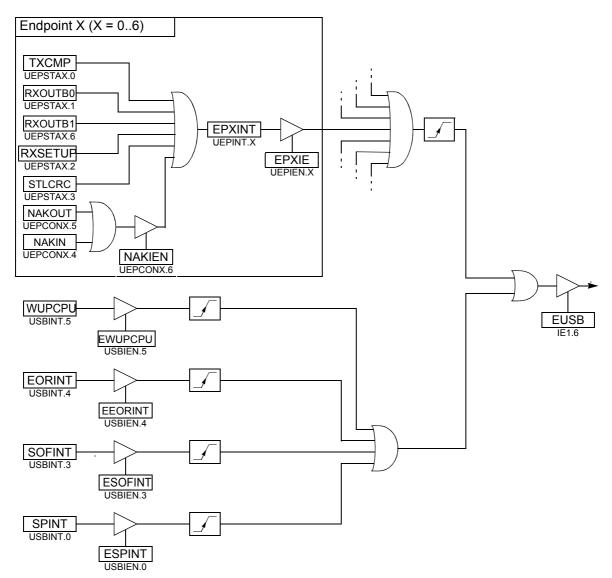

Figure 63. USB Interrupt Control Block Diagram

|                                  | Figure 66. UART Timings in Mode                                                                                                                                                                |                                                                                               |                                                                                |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

|                                  |                                                                                                                                                                                                |                                                                                               |                                                                                |

|                                  | <sup>I</sup> Start <sup>I</sup><br>bit                                                                                                                                                         | Data byte                                                                                     | Ninth <sup>I</sup> Stop <sup>I</sup><br>bit bit                                |

|                                  | RI<br>SMOD0=0                                                                                                                                                                                  |                                                                                               |                                                                                |

|                                  | RI<br>SMOD0=1                                                                                                                                                                                  |                                                                                               |                                                                                |

|                                  | FE<br>SMOD0=1                                                                                                                                                                                  |                                                                                               |                                                                                |

| Automatic Address<br>Recognition | The automatic address recognition nication feature is enabled (SM2 bi                                                                                                                          |                                                                                               | e multiprocessor commu-                                                        |

|                                  | Implemented in hardware, automatic<br>communication feature by allowin<br>incoming command frame. Only w<br>receiver sets RI bit in SCON register<br>is not interrupted by command fram        | ng the serial port to exami<br>when the serial port recognizer<br>to generate an interrupt. T | ne the address of each<br>zes its own address, the<br>his ensures that the CPU |

|                                  | If desired, you may enable the auto<br>configuration, the stop bit takes the<br>received command frame address<br>valid stop bit.<br>To support automatic address reco<br>a broadcast address. | place of the ninth data bit. E matches the device's addres                                    | Bit RI is set only when the<br>ss and is terminated by a                       |

|                                  |                                                                                                                                                                                                | cation and automatic address<br>ting SM2 bit in SCON register i                               |                                                                                |

| Given Address                    | Each device has an individual addured<br>register is a mask byte that conta<br>device's given address. The don't conta<br>slaves at a time. The following examples                             | ains don't care bits (define<br>are bits provide the flexibilit                               | ed by zeros) to form the<br>y to address one or more                           |

|                                  | To address a device by its individ 1111b.                                                                                                                                                      | ual address, the SADEN m                                                                      | nask byte must be 1111                                                         |

|                                  | For example:<br>SADDR0101 0110b<br><u>SADEN1111 1100b</u><br>Given0101 01XXb                                                                                                                   |                                                                                               |                                                                                |

|                                  | The following is an example of how<br>Slave A:SADDR1111 0001b<br><u>SADEN1111 1010b</u><br>Given1111 0X0Xb                                                                                     | v to use given addresses to a                                                                 | address different slaves:                                                      |

|                                  | Slave B:SADDR1111 0011b<br><u>SADEN1111 1001b</u><br>Given1111 0XX1b                                                                                                                           |                                                                                               |                                                                                |

|                                  | Slave C:SADDR1111 0011b<br><u>SADEN1111 1101b</u><br>Given1111 00X1b                                                                                                                           |                                                                                               |                                                                                |

|                                  |                                                                                                                                                                                                |                                                                                               |                                                                                |

| 7                                                      | 6                                                                        | 5                                                   | 4                             | 3                                   | 2                     | 1              | 0          |

|--------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------|-------------------------------------|-----------------------|----------------|------------|

|                                                        |                                                                          |                                                     |                               |                                     |                       |                |            |

| Reset Va                                               | lue = 0000                                                               | 0000b                                               |                               |                                     |                       |                |            |

| Table 79                                               | . Slave Add                                                              | Iress Regist                                        | er for UAR                    | T - SADDR                           | (A9h)                 |                |            |

| 7                                                      | 6                                                                        | 5                                                   | 4                             | 3                                   | 2                     | 1              | 0          |

|                                                        |                                                                          |                                                     |                               |                                     |                       |                |            |

| Reset Va                                               | lue = 0000                                                               | 0000b                                               |                               |                                     |                       |                |            |

| Table 80                                               | . Serial Buf                                                             | fer Register                                        | for UART -                    | - SBUF (991                         | า)                    |                |            |

| 7                                                      | 6                                                                        | 5                                                   | 4                             | 3                                   | 2                     | 1              | 0          |

|                                                        |                                                                          |                                                     |                               |                                     |                       |                |            |

|                                                        | lue = XXXX                                                               |                                                     |                               |                                     |                       |                | 1          |

|                                                        |                                                                          | e Reload Re                                         | gister for th                 | ne internal t                       | baud rate ge          | enerator,      |            |

|                                                        | . Baud Rate                                                              |                                                     | gister for th                 | ne internal b<br>3                  | oaud rate ge<br>2     | enerator,<br>1 | 0          |

| UART - E                                               | . Baud Rate<br>BRL (9Ah)                                                 | e Reload Re                                         | -                             |                                     | -                     |                | 0          |

| UART - E<br>7<br>Reset Va                              | Baud Rate<br>BRL (9Ah)<br>6<br>Iue = 0000                                | e Reload Re<br>5<br>0000b                           | 4                             | 3                                   | 2                     |                | 0          |

| UART - E<br>7<br>Reset Va<br>Table 82                  | Baud Rate<br>BRL (9Ah)<br>6<br>Ilue = 0000                               | e Reload Re<br>5<br>0000b<br>e Control Re           | 4<br>egister - BD             | 3<br>RCON - (91                     | 2<br>                 | 1              |            |

| UART - E<br>7<br>Reset Va                              | Baud Rate<br>BRL (9Ah)<br>6<br>Iue = 0000                                | e Reload Re<br>5<br>0000b                           | 4<br>egister - BD<br>4        | 3<br>                               | 2<br>3h)<br>2         | 1              | 0          |

| UART - E<br>7<br>Reset Va<br>Table 82                  | Baud Rate<br>BRL (9Ah)<br>6<br>Ilue = 0000                               | e Reload Re<br>5<br>0000b<br>e Control Re           | 4<br>egister - BD             | 3<br>RCON - (91                     | 2<br>                 | 1              |            |

| UART - E<br>7<br>Reset Va<br>Table 82                  | Baud Rate<br>BRL (9Ah)<br>6<br>Ilue = 0000                               | e Reload Re<br>5<br>0000b<br>e Control Re           | 4<br>egister - BD<br>4        | 3<br>                               | 2<br>3h)<br>2         | 1              | 0          |

| UART - E<br>7<br>Reset Va<br>Table 82<br>7<br>-<br>Bit | Baud Rate<br>BRL (9Ah)<br>6<br>Ilue = 0000<br>Baud Rate<br>6<br>-<br>Bit | e Reload Re<br>5<br>0000b<br>e Control Re<br>5<br>- | 4<br>egister - BD<br>4<br>BRR | 3<br>RCON - (91<br><u>3</u><br>TBCK | 2<br>Bh)<br>2<br>RBCK | 1<br>1<br>SPD  | 0<br>MOSRC |

| 4 | BRR   | <b>Baud Rate Run Control bit</b><br>Cleared to stop the internal Baud Rate Generator.<br>Set to start the internal Baud Rate Generator.                                                     |

|---|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3 | TBCK  | Transmission Baud rate Generator Selection bit for UART<br>Cleared to select Timer 1 for the Baud Rate Generator.<br>Set to select internal Baud Rate Generator.                            |

| 2 | RBCK  | <b>Reception Baud Rate Generator Selection bit for UART</b><br>Cleared to select Timer 1 for the Baud Rate Generator.<br>Set to select internal Baud Rate Generator.                        |

| 1 | SPD   | Baud Rate Speed Control bit for UART<br>Cleared to select the SLOW Baud Rate Generator.<br>Set to select the FAST Baud Rate Generator.                                                      |

| 0 | M0SRC | Baud Rate Source select bit in Mode 0 for UART<br>Cleared to select F <sub>CK_SI</sub> /6 as the Baud Rate Generator.<br>Set to select the internal Baud Rate Generator for UART in mode 0. |

Reset Value = XXX0 0000b (Not bit addressable)

# 134 AT83R5122, AT8xC5122/23

| 7             | 6               | 5                        | 4                                                        | 3               | 2              | 1              | 0     |

|---------------|-----------------|--------------------------|----------------------------------------------------------|-----------------|----------------|----------------|-------|

| -             | EUSB            | -                        | -                                                        | ESCI            | ESPI           | -              | EKB   |

| Bit<br>Number | Bit<br>Mnemonic | Description              |                                                          |                 |                |                |       |

| 7             | -               | Reserved<br>The value re | ad from this b                                           | it is indetermi | nate. Do not c | hange this bit |       |

| 6             | EUSB            | Cleared to d             | <b>pt Enable bit</b><br>isable USB in<br>e USB interru   | terrupt.        |                |                |       |

| 5 - 4         | -               | Reserved<br>The value re | ad from this b                                           | it is indetermi | nate. Do not c | hange these I  | oits. |

| 3             | ESCI            | Cleared to d             | ot Enable bit<br>isable SClinte<br>e SCI interrup        | •               |                |                |       |

| 2             | ESPI            | Cleared to d             | <b>t Enable bit</b><br>isable SPI inte<br>e SPI interrup | •               |                |                |       |

| 1             | -               | Reserved<br>The value re | ad from this b                                           | it is indetermi | nate. Do not c | hange this bit |       |

| 0             | EKB             | Cleared to d             | iterrupt Enat<br>isable keyboa<br>e keyboard int         | rd interrupt .  |                |                |       |

# Table 99. Interrupt Enable Register 1 - IEN1 (B1h) for AT8xC5122

Reset Value = X0XX 00X0b (Bit addressable)

| 7             | 6               | 5                                                     | 4                          | 3                                                                       | 2             | 1            | 0     |

|---------------|-----------------|-------------------------------------------------------|----------------------------|-------------------------------------------------------------------------|---------------|--------------|-------|

| -             | -               | -                                                     | PSH                        | PT1H                                                                    | PX1H          | PT0H         | PX0H  |

| Bit<br>Number | Bit<br>Mnemonic | Descriptio                                            | on                         |                                                                         |               |              |       |

| 7 - 5         | -               | Reserved<br>The value                                 |                            | s bit is indeterm                                                       | inate. Do not | change these | bits. |

| 4             | PSH             | <b>Serial por</b><br><u>PSH</u><br>0<br>1<br>1        |                            | <b>h bit</b><br><u>Priority Level</u><br>Lowest<br>Highest              |               |              |       |

| 3             | PT1H            | <b>Timer 1 o</b> v<br><u>PT1H</u><br>0<br>0<br>1<br>1 | <u>PT1L</u><br>0<br>1<br>0 | r <b>upt Priority H</b> i<br><u>Priority Level</u><br>Lowest<br>Highest | igh bit       |              |       |

| 2             | PX1H            | External in<br><u>PX1H</u><br>0<br>0<br>1<br>1        | <u>PX1L</u><br>0<br>1<br>0 | <b>iority High bit</b><br><u>Priority Level</u><br>Lowest<br>Highest    |               |              |       |

| 1             | РТОН            | <b>Timer 0 ov</b><br><u>PT0H</u><br>0<br>1<br>1       | <u>PT0L</u><br>0<br>1<br>0 | r <b>upt Priority H</b> i<br><u>Priority Level</u><br>Lowest<br>Highest | igh bit       |              |       |

| 0             | РХОН            | External in<br><u>PX0H</u><br>0<br>1<br>1             | 0<br>1<br>0                | rity High bit<br><u>Priority Level</u><br>Lowest<br>Highest             |               |              |       |

#### Table 102. Interrupt Priority High Register 0 - IPH0 (B7h)

Reset Value = X000 0000b (Not bit addressable)

| 7             | 6               | 5                            | 4                                  | 3                | 2               | 1              | 0     |

|---------------|-----------------|------------------------------|------------------------------------|------------------|-----------------|----------------|-------|

| -             | PUSBL           | -                            | -                                  | PSCIL            | PSPIL           | -              | PKBDL |

| Bit<br>Number | Bit<br>Mnemonic | Description                  |                                    |                  |                 |                |       |

| 7             | _               | Reserved<br>The value rea    | ad from this b                     | it is indetermir | nate. Do not cl | nange this bit |       |

| 6             | PUSBL           |                              | pt Priority bit<br>BH for priority |                  |                 |                |       |

| 5 - 4         | -               | Reserved<br>The value rea    | ad from this b                     | it is indetermir | nate. Do not cl | nange these t  | oits. |

| 3             | PSCIL           | SCI Interrup<br>Refer to PSP | t Priority bit<br>PIH for priority | level.           |                 |                |       |

| 2             | PSPIL           | SPI Interrup<br>Refer to PSP | t Priority bit<br>PIH for priority | level.           |                 |                |       |

| 1             | -               | Reserved<br>The value rea    | ad from this b                     | it is indetermir | nate. Do not cl | nange this bit |       |

| 0             | PKBL            |                              | terrupt Prior                      |                  |                 |                |       |

# Table 103. Interrupt Priority Low Register 1 - IPL1 (B2h) for AT8xC5122

Reset Value = X00X 00X0b (Bit addressable)

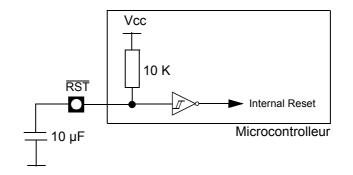

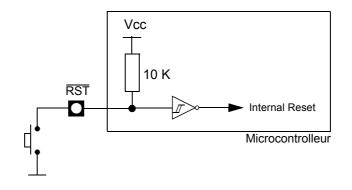

### **Reset pin**

As explained in the POR section there is no need to use the reset pin as the internal reset function at power up is ensured by the POR. Anyway, if some applications requires a long reset, a reset controlled by the user or a reset controlled by external superviser device, the use of the reset pin is necessary.

**Long Reset** As the pad integrates an internal pull-up of 10K, only an external capacitor of at least 10  $\mu$ F is required to have an impact on the reset duration.

Figure 103. Long Reset

**Reset Controlled by the User** The external capacitor is not needed if no long reset is required.

Figure 104. Reset Controlled by the User

| S2 | S1 | S0 | Timeout for $F_{CK_WD}$ = 24 MHz / X2 |

|----|----|----|---------------------------------------|

| 0  | 0  | 0  | 4.10 ms                               |

| 0  | 0  | 1  | 8.19 ms                               |

| 0  | 1  | 0  | 16.38 ms                              |

| 0  | 1  | 1  | 32.77 ms                              |

| 1  | 0  | 0  | 65.54 ms                              |

| 1  | 0  | 1  | 131.07 ms                             |

| 1  | 1  | 0  | 262.14 ms                             |

| 1  | 1  | 1  | 524.29 ms                             |

Table 111. Timeout value for  $F_{CK_{WD}}$  = 24 MHz / X2

| Table 112 | Watchdog | Timer Enable | register (W | /rite Only) | - WDTRST | (A6h) |

|-----------|----------|--------------|-------------|-------------|----------|-------|

|-----------|----------|--------------|-------------|-------------|----------|-------|

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

Reset Value = XXXX XXXXb

The WDTRST register is used to reset / enable the WDT by writing 1EH then E1H in sequence.

| Power Management |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | Before activating the Idle Mode or Power Down Mode, the CPU clock must be switched to on-chip oscillator source if the PLL is used to fed the CPU clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Idle Mode        | An instruction that sets PCON.0 indicates that it is the last instruction to be executed before going into the Idle mode. In the Idle mode, the internal clock signal is gated off to the CPU, but not to the interrupt, Timer, and Serial Port functions. The CPU status is preserved in its entirety: the Stack Pointer, Program Counter, Program Status Word, Accumulator and all other registers maintain their data during Idle. The port pins hold the logical states they had at the time Idle was activated. ALE and PSEN hold at logic high level.                                                                     |

|                  | There are two ways to terminate the Idle mode. Activation of any enabled interrupt will cause PCON.0 to be cleared by hardware, terminating the Idle mode. The interrupt will be serviced, and following RETI the next instruction to be executed will be the one following the instruction that put the device into idle.                                                                                                                                                                                                                                                                                                      |

|                  | The flag bits GF0 and GF1 can be used to give an indication if an interrupt occured dur-<br>ing normal operation or during an Idle. For example, an instruction that activates Idle<br>can also set one or both flag bits. When Idle is terminated by an interrupt, the interrupt<br>service routine can examine the flag bits.                                                                                                                                                                                                                                                                                                 |

|                  | The other way of terminating the Idle mode is with a hardware reset. Since the clock oscillator is still running, the hardware reset needs to be held active for only two machine cycles (24 oscillator periods) to complete the reset.                                                                                                                                                                                                                                                                                                                                                                                         |

| Power Down Mode  | To save maximum power, a power-down mode can be invoked by software (see Table 13, PCON register).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                  | <b>WARNING:</b> To minimize power consumption, all peripherals and I/Os with static current consumption must be set in the proper state. I/Os programmed with low speed output configuration (KB_OUT) must be switch to push-pull or Standard C51 configuration before entering power-down. The CVCC generator must also be switch off.                                                                                                                                                                                                                                                                                         |

|                  | In power-down mode, the oscillator is stopped and the instruction that invoked power-<br>down mode is the last instruction executed. The internal RAM and SFRs retain their<br>value until the power-down mode is terminated. V <sub>CC</sub> can be lowered to save further<br>power. Either a hardware reset or an external interrupt can cause an exit from power-<br>down. To properly terminate power-down, the reset or external interrupt should not be<br>executed before V <sub>CC</sub> is restored to its normal operating level and must be held active<br>long enough for the oscillator to restart and stabilize. |

|                  | Only external interrupts INT0, INT1, Keyboard, Card insertion/removal and USB Inter-<br>rupts are useful to exit from power-down. For that, interrupt must be enabled and<br>configured as level or edge sensitive interrupt input. When Keyboard Interrupt occurs<br>after a power-down mode, 1024 clocks are necessary to exit to power-down mode and<br>enter in operating mode.                                                                                                                                                                                                                                             |

|                  | Holding the pin low restarts the oscillator but bringing the pin high completes the exit as detailed in Figure 108. When both interrupts are enabled, the oscillator restarts as soon as one of the two inputs is held low and power-down exit will be completed when the first input is released. In this case, the higher priority interrupt service routine is executed. Once the interrupt is serviced, the next instruction to be executed after RETI will be the one following the instruction that put AT83R5122, AT8xC5122/23 into power-down mode.                                                                     |

Amer

# 178 AT83R5122, AT8xC5122/23

# **USB** Interface

#### Figure 112. USB Interface

| Symbol           | Parameter                                   | Min | Тур <sup>(5)</sup> | Max | Unit |

|------------------|---------------------------------------------|-----|--------------------|-----|------|

| V <sub>REF</sub> | USB Reference Voltage                       | 3.0 |                    | 3.6 | V    |

| V <sub>IH</sub>  | Input High Voltage for D+ and D- (driven)   | 2.0 |                    | 4.0 | V    |

| V <sub>IHZ</sub> | Input High Voltage for D+ and D- (floating) | 2.7 |                    | 3.6 | V    |

| V <sub>IL</sub>  | Input Low Voltage for D+ and D-             |     |                    | 0.8 | V    |

| V <sub>OH</sub>  | Output High Voltage for D+ and D-           | 2.8 |                    | 3.6 | V    |

| V <sub>OL</sub>  | Output Low Voltage for D+ and D-            | 0.0 |                    | 0.3 | V    |

# **Table of Contents**

| Reference Documents       2         Product Description       3         AT8xC5122/AT83R5122 Block Diagram       4         AT83C5123 Block Diagram       4         Pinout       5         High Pin Count Package Description       5         Low Pin Count Package Description       10         Pin Description       11         Typical Applications       15         Recommended External components       15         USB Keyboard with Smart Card Reader Using AT83R5122, AT8xC5122/AT89C5122DS         16       USB Smart Card Reader Using the AT83C5123 Version         17       Memory Organization         18       Program Memory Managament         19       Dual Data Pointer Register (DDPTR)         20       Registers         21       AT8xC5122's CRAM and E2PROM Versions         22       AT8xC5122's CRAM and E2PROM Version         30       Special Function Registers (SFR's)         31       Introduction         33       SFR's Description         34       AT83C5123 Version         35       Special Function Registers (SFR's)         34       AT83C5123 Version         35       SFR's Description         34       Clock Controller       39                    | Features                                          | 1  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----|--|

| AT8xC5122/AT83R5122 Block Diagram       4         AT83C5123 Block Diagram       4         Pinout       5         High Pin Count Package Description       5         Low Pin Count Package Description       10         Pin Description       11         Typical Applications       15         Recommended External components       15         USB Keyboard with Smart Card Reader Using AT83R5122, AT8xC5122/AT89C5122DS         16       USB Smart Card Reader Using the AT83C5123 Version         17       Memory Organization         18       Program Memory Managament         19       Dual Data Pointer Register (DPTR)         20       Registers         21       AT83C5123 Version         30       Special Function Registers (SFR's)         31       Introduction         33       SFR's Description         34       Clock Controller         39       On-Chip Oscillator         39       On-Chip Oscillator         39       Phase Lock Loop (PLL)         40       Clock Tree Architecture         41       Registers         41       Registers         42       AT83C5123 Version         39       On-Chip Oscillator                                                      | Reference Documents                               | 2  |  |

| AT83C5123 Block Diagram       4         Pinout       5         High Pin Count Package Description       10         Pin Description       11         Typical Applications       15         Recommended External components       15         USB Keyboard with Smart Card Reader Using AT83R5122, AT8xC5122/AT89C5122DS         16       USB Smart Card Reader Using the AT83C5123 Version         17       Memory Organization         18       Program Memory Managament         19       Dual Data Pointer Register (DDPTR)         20       Registers         22       AT8xC5122's CRAM and E2PROM Versions         24       AT83R5122, AT8xC5122's ROM Version         30       Special Function Registers (SFR's)         31       AT83C5122 Version         33       SFR's Description         34       Clock Controller         39       On-Chip Oscillator         39       Phase Lock Loop (PLL)         40       Clock Tree Architecture         41       Registers         48       VO Port Definition         51       Pot Configuration         52       Smart Card Interface Block (SCIB)                                                                                         | Product Description                               | 3  |  |

| Pinout       5         High Pin Count Package Description       5         Low Pin Count Package Description       10         Pin Description       11         Typical Applications       15         Recommended External components       15         USB Keyboard with Smart Card Reader Using AT83R5122, AT8xC5122/AT89C5122DS         16       USB Smart Card Reader Using the AT83C5123 Version         17       Memory Organization         18       Program Memory Managament         19       Dual Data Pointer Register (DDPTR)         20       Registers         21       AT8xC5122's CRAM and E2PROM Versions         22       AT8xC5123 Version         30       Special Function Registers (SFR's)         31       Introduction         31       AT83C5123 Version         32       AT83C5123 Version         33       SFR's Description         34       Clock Controller         39       On-Chip Oscillator         39       Phase Lock Loop (PLL)         48       VO Port Definition         48       VO Port Definition         57       Registers         58       Special Interface Block (SCIB)                                                                          | AT8xC5122/AT83R5122 Block Diagram                 | 4  |  |

| High Pin Count Package Description       5         Low Pin Count Package Description       10         Pin Description       11         Typical Applications       15         Recommended External components       15         USB Keyboard with Smart Card Reader Using AT83R5122, AT8xC5122/AT89C5122DS         16       USB Smart Card Reader Using the AT83C5123 Version         17       Memory Organization         18       Program Memory Managament         19       Dual Data Pointer Register (DDPTR)         20       Registers         21       AT8xC5122's CRAM and E2PROM Versions         24       AT83R5122, AT8xC5122's ROM Version         25       AT83C5123 Version         31       Introduction         31       AT83C5122 Version         32       AT83C5123 Version         33       SFR's Description         34       Clock Controller         39       On-Chip Oscillator         99       Phase Lock Loop (PLL)         40       Clock Tree Architecture         41       Registers         48       VO Port Definition         51       Port Configuration         55       Registers         59       Smart Card In                                              | AT83C5123 Block Diagram                           | 4  |  |

| High Pin Count Package Description       5         Low Pin Count Package Description       10         Pin Description       11         Typical Applications       15         Recommended External components       15         USB Keyboard with Smart Card Reader Using AT83R5122, AT8xC5122/AT89C5122DS         16       USB Smart Card Reader Using the AT83C5123 Version         17       Memory Organization         18       Program Memory Managament         19       Dual Data Pointer Register (DDPTR)         20       Registers         21       AT8xC5122's CRAM and E2PROM Versions         24       AT83R5122, AT8xC5122's ROM Version         25       AT83C5123 Version         31       Introduction         31       AT83C5122 Version         32       AT83C5123 Version         33       SFR's Description         34       Clock Controller         39       On-Chip Oscillator         99       Phase Lock Loop (PLL)         40       Clock Tree Architecture         41       Registers         48       VO Port Definition         51       Port Configuration         55       Registers         59       Smart Card In                                              | Pinout                                            | 5  |  |

| Low Pin Count Package Description         10           Pin Description         11           Typical Applications         15           Recommended External components         15           USB Keyboard with Smart Card Reader Using AT83R5122, AT8xC5122/AT89C5122DS           16         USB Smart Card Reader Using the AT83C5123 Version           17         Memory Organization           18         Program Memory Managament           19         Dual Data Pointer Register (DDPTR)           20         Registers           21         AT8xC5122's CRAM and E2PROM Versions           24         AT83R5122, AT8xC5122's ROM Version           28         AT83C5123 Version           30         Special Function Registers (SFR's)           31         AT8xC5122 Version           32         AT83C5123 Version           33         SFR's Description           34         Clock Controller           39         On-Chip Oscillator           99         Phase Lock Loop (PLL)           40         Clock Tree Architecture           41         Registers           48         VO Port Definition           48         VO Port Definition           51         Port Configuration |                                                   |    |  |