Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | 80C51                                                                       |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | SmartCard, SPI, UART/USART, USB                                             |

| Peripherals                | LED, POR, WDT                                                               |

| Number of I/O              | 46                                                                          |

| Program Memory Size        | 32KB (32K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 768 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-LQFP                                                                     |

| Supplier Device Package    | 64-VQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c5122ds-rdtum |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table 2. Pin Description (Continued)

|      | 964    | °32    | 268    | 228    | 64    | 32    | Internal        |     |     |                |      |                 |           |              |              |      |

|------|--------|--------|--------|--------|-------|-------|-----------------|-----|-----|----------------|------|-----------------|-----------|--------------|--------------|------|

| Port | VQFP64 | VQFP32 | PLCC68 | PLCC28 | QFN64 | QFN32 | Power<br>Supply | ESD | I/O | Reset<br>Level | Alt  | Reset<br>Config | Conf 1    | Conf 2       | Conf 3       | Led  |

| P2.6 | 49     | -      | 62     | -      | 49    | -     | VCC             | 2KV | I/O | 1              | A14  | Port51          | Push-pull | KB_OUT       | Input<br>WPU |      |

| P2.7 | 46     | -      | 57     | -      | 46    | -     | VCC             | 2KV | I/O | 1              | A15  | Port51          | Push-pull | KB_OUT       | Input<br>WPU |      |

| P3.0 | 45     | 22     | 56     | 24     | 45    | 22    | VCC             | 2KV | I/O | 1              | RxD  | Port51          | Push-pull | KB_OUT       | Input<br>WPU |      |

| P3.1 | 48     | 24     | 59     | 25     | 48    | 24    | VCC             | 2KV | I/O | 1              | TxD  | Port51          | Push-pull | KB_OUT       | Input<br>WPU |      |

| P3.2 | 43     | 20     | 54     | 23     | 43    | 20    | VCC             | 2KV | I/O | 1              | INT0 | Port51          |           |              |              | LED0 |

| P3.3 | 41     | 19     | 52     | 22     | 41    | 19    | vcc             | 2KV | I/O | 1              | INT1 | Port51          | Push-pull | KB_OUT       | Input<br>WPU |      |

| P3.4 | 39     | 18     | 50     | 21     | 39    | 18    | VCC             | 2KV | I/O | 1              | TO   | Port51          | Push-pull | KB_OUT       | Input<br>WPU | LED1 |

| P3.5 | 44     | 21     | 55     | -      | 44    | 21    | VCC             | 2KV | I/O | 1              | T1   | Port51          |           |              |              |      |

| P3.6 | 36     | 17     | 47     | 20     | 36    | 17    | VCC             | 2KV | I/O | 1              | WR   | Port51          |           |              |              | LED2 |

| P3.7 | 26     | 13     | 37     | 16     | 26    | 13    | VCC             | 2KV | I/O | 1              | RD   | Port51          |           |              |              | LED3 |

| P4.0 | 42     | -      | 53     | -      | 42    | -     | VCC             | 2KV | I/O | 1              | MISO | Port51          |           |              |              |      |

| P4.1 | 40     | -      | 51     | -      | 40    | -     | VCC             | 2KV | I/O | 1              | MOSI | Port51          |           |              |              |      |

| P4.2 | 38     | -      | 49     | -      | 38    | -     | VCC             | 2KV | I/O | 1              | SCK  | Port51          |           |              |              |      |

| P4.3 | 37     | -      | 48     | -      | 37    | -     | VCC             | 2KV | I/O | 1              |      | Port51          | Push-pull | KB_OUT       | Input<br>MPU | LED4 |

| P4.4 | 35     | -      | 46     | -      | 35    | -     | VCC             | 2KV | I/O | 1              |      | Port51          | Push-pull | KB_OUT       | Input<br>MPU | LED5 |

| P4.5 | 33     | -      | 44     | -      | 33    | -     | VCC             | 2KV | I/O | 1              |      | Port51          | Push-pull | KB_OUT       | Input<br>MPU | LED6 |

| P5.0 | 14     | 7      | 23     | -      | 14    | 7     | VCC             | 2KV | I/O | 1              | KB0  | Port51          | Push-pull | Input<br>MPU | Input<br>WPU |      |

| P5.1 | 13     | -      | 22     | -      | 13    | -     | vcc             | 2KV | I/O | 1              | KB1  | Port51          | Push-pull | Input<br>MPU | Input<br>WPU |      |

| P5.2 | 11     | -      | 20     | -      | 11    | -     | vcc             | 2KV | I/O | 1              | KB2  | Port51          | Push-pull | Input<br>MPU | Input<br>WPU |      |

| P5.3 | 10     | -      | 19     | -      | 10    | -     | VCC             | 2KV | I/O | 1              | KB3  | Port51          | Push-pull | Input<br>WPD | Input<br>WPU |      |

| P5.4 | 8      | -      | 17     | -      | 8     | -     | VCC             | 2KV | I/O | 1              | KB4  | Port51          | Push-pull | Input<br>WPD | Input<br>WPU |      |

<sup>12</sup> AT83R5122, AT8xC5122/23

| 7             | 6               | 5                                                                                                                | 4                                                               | 3                                                              | 2                                                 | 1                  | 0          |  |  |  |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------|--------------------|------------|--|--|--|

| -             | -               | ENBOOT                                                                                                           | ENBOOT - GF3 0 - DF                                             |                                                                |                                                   |                    |            |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                      |                                                                 |                                                                |                                                   |                    |            |  |  |  |

| 7 - 6         | -               | <b>Reserved</b><br>The value read                                                                                | from this bit                                                   | is indetermina                                                 | te. Do not cha                                    | ange these bit     | 6.         |  |  |  |

| 5             | ENBOOT          | Enable Boot F<br>Set this bit to n<br>beyond 7FFFh<br>Clear this bit to<br>the code is feto<br>This bit is force | hap the Boot I<br>address, the<br>disable Boot<br>h from extern | ROM from 800<br>code is fetch<br>ROM. If the F<br>al code memo | 00h to FFFFh.<br>from internal F<br>PC increments | ROM<br>beyond 7FFF | h address, |  |  |  |

| 4             | -               | <b>Reserved</b><br>The value read                                                                                | from this bit                                                   | is indetermina                                                 | te. Do not cha                                    | inge this bit.     |            |  |  |  |

| 3             | GF3             | This bit is a ge                                                                                                 | neral-purpose                                                   | user flag.                                                     |                                                   |                    |            |  |  |  |

| 2             | 0               | Always cleared                                                                                                   | -                                                               |                                                                |                                                   |                    |            |  |  |  |

| 1             | -               | Reserved<br>The value read from this bit is indeterminate. Do not change this bit.                               |                                                                 |                                                                |                                                   |                    |            |  |  |  |

| 0             | DPS             | Data Pointer S<br>Cleared to sele                                                                                |                                                                 | t to select DP                                                 | TR1.                                              |                    |            |  |  |  |

### Table 6. Auxiliary Register 1 AUXR1- (0A2h) for AT8xC5122

Reset Value = XX1X XX0X0b (Not bit addressable)

### Table 7. Auxiliary Register 1 AUXR1- (0A2h) for AT83C5123

| 7             | 6               | 5                                                        | 4               | 3              | 2              | 1               | 0   |

|---------------|-----------------|----------------------------------------------------------|-----------------|----------------|----------------|-----------------|-----|

| -             | -               | -                                                        | -               | GF3            | 0              | -               | DPS |

| Bit<br>Number | Bit<br>Mnemonic | Description                                              |                 |                |                |                 |     |

| 7 - 6         | -               | Reserved<br>The value read                               | I from this bit | is indetermina | te. Do not cha | inge these bits | 6.  |

| 5             |                 | Reserved<br>The value read                               | I from this bit | is indetermina | te. Do not cha | inge these bits | 6.  |

| 4             | -               | Reserved<br>The value read                               | I from this bit | is indetermina | te. Do not cha | inge this bit.  |     |

| 3             | GF3             | This bit is a ge                                         | neral-purpose   | e user flag.   |                |                 |     |

| 2             | 0               | Always cleared                                           | 1.              |                |                |                 |     |

| 1             | -               | Reserved<br>The value read                               | I from this bit | is indetermina | te. Do not cha | ange this bit.  |     |

| 0             | DPS             | Data Pointer S<br>Cleared to select D<br>Set to select D | ect DPTR0.      |                |                |                 |     |

Reset Value = XXXX XX0X0b (Not bit addressable)

| 7             | 6            | 5               | 4                                                                                                                                                                                | 3   | 2 | 1 | 0 |  |  |

|---------------|--------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|---|---|--|--|

| -             | -            | -               | -                                                                                                                                                                                | RPS | - | - | - |  |  |

| Bit<br>Number | Bit<br>Mnemo | nic Descr       | Description                                                                                                                                                                      |     |   |   |   |  |  |

| 7 - 4         | -            |                 | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not change these bits                                                                                       |     |   |   |   |  |  |

| 3             | RPS          | Set to<br>Clear | <b>CRAM Memory Mapping Bit</b><br>Set to map the CRAM memory during MOVX instructions<br>Clear to map the XRAM memory during MOVX.<br>This bit has priority over the EXTRAM bit. |     |   |   |   |  |  |

| 2-0           | -            |                 | Reserved<br>The value read from this bit is indeterminate. Do not change these                                                                                                   |     |   |   |   |  |  |

### Table 8. CRAM Configuration Register - RCON (D1h)

Reset Value = XXXX 0XXXb

## AT8xC5122's CRAM and E2PROM Versions

The AT8xC5122's CRAM and E2PROM versions implements :

- 32 KB of ROM mapped from 8000 to FFFF in which is embedded a bootloader for In-System Programming feature

- 32 KB of CRAM (Code RAM), a volatile program memory mapped from 0000 to 7FFF

In CRAM versions only :

- 512 bytes of E2PROM can be optionally implemented to store permanent data

In E2PROM version :

- 32KB of E2PROM are implemented to store permanent code

#### Warnings :

- some bytes of user program memory space are reserved for bootloader configuration. Depending on the configuration, up to 256 bytes of code may be not available for the user code from 7F00h location. Refer to bootloader datasheet for further details.

- Port P3.7 may be used by the bootloader as a hardware condition at reset to select the In-System Programming mode. Once the bootloader has started, the P3.7 Port is no more used.

### Table 17. Interrupt SFRs

| Mnemonic | Add | Name                                 | 7     | 6     | 5      | 4    | 3     | 2                    | 1      | 0                   |

|----------|-----|--------------------------------------|-------|-------|--------|------|-------|----------------------|--------|---------------------|

| IPH0     | B7h | Interrupt Priority Control<br>High 0 |       |       |        | PSH  | PT1H  | PX1H                 | PT0H   | PX0H                |

| IPL1     | B2h | Interrupt Priority Control<br>Low 1  |       | PUSBL |        |      | PSCIL | PSPIL <sup>(1)</sup> |        | PKBL <sup>(1)</sup> |

| IPH1     | B3h | Interrupt Priority Control<br>High 1 |       | PUSBH |        |      | PSCIH | PSPIH <sup>(1)</sup> |        | PKBH <sup>(1)</sup> |

| ISEL     | A1h | Interrupt Enable Register            | CPLEV |       | PRESIT | RXIT | OELEV | OEEN                 | PRESEN | RXEN                |

Note: 1. Only for AT8xC5122

### Table 18. SCIB SFRs

| Mnemonic | Add | Name                                                                | 7          | 6                              | 5        | 4                              | 3      | 2       | 1       | 0       |  |  |

|----------|-----|---------------------------------------------------------------------|------------|--------------------------------|----------|--------------------------------|--------|---------|---------|---------|--|--|

| SCGT0    | B4h | Smart Card Transmit Guard<br>Time Register 0                        |            |                                |          | GT                             | 7 - 0  |         |         |         |  |  |

| SCGT1    | B5h | Smart Card Transmit Guard<br>Time Register 1                        |            |                                |          |                                |        |         |         | GT8     |  |  |

| SCWT0    | B4h | Smart Card Character/ Block<br>Waiting Time Register 0              | WT7 - 0    |                                |          |                                |        |         |         |         |  |  |

| SCWT1    | B5h | Smart Card Character/ Block<br>Waiting Time Register 1              |            | WT15-8                         |          |                                |        |         |         |         |  |  |

| SCWT2    | B6h | Smart Card Character/ Block<br>Waiting Time Register 2              |            |                                |          | WT2                            | 23-16  |         |         |         |  |  |

| SCWT3    | C1h | Smart Card Character/ Block<br>Waiting Time Register 3              |            |                                |          | WT3                            | 31-24  |         |         |         |  |  |

| SCICR    | B6h | Smart Card Interface Control RESET                                  |            | CARDDET                        | VCARD1-0 |                                | UART   | WTEN    | CREP    | CONV    |  |  |

| SCCON    | ACh | Smart Card Interface<br>Contacts Register                           | CLK        |                                | CARDC8   | CARDC4                         | CARDIO | CARDCLK | CARDRST | CARDVCC |  |  |

| SCETU0   | ACh | Smart Card ETU Register 0                                           | 0 ETU7 - 0 |                                |          |                                |        |         |         |         |  |  |

| SCETU1   | ADh | Smart Card ETU Register 1                                           | COMP       |                                |          |                                |        |         | ETU10-8 |         |  |  |

| SCISR    | ADh | Smart Card UART Interface<br>Status Register (Read only)            | SCTBE      | CARDIN                         | ICARDOVF | VCARDOK                        | SCWTO  | SCTC    | SCRC    | SCPE    |  |  |

| SCIIR    | AEh | Smart Card UART Interrupt<br>Identification Register (Read<br>only) | SCTBI      |                                | ICARDERR | VCARDERR                       | SCWTI  | SCTI    | SCRI    | SCPI    |  |  |

| SCIER    | AEh | Smart Card UART Interrupt<br>Enable Register                        | ESCTBI     |                                | ICARDER  | EVCARDER                       | ESCWTI | ESCTI   | ESCRI   | ESCPI   |  |  |

| SCSR     | ABh | Smart Card Selection<br>Register                                    |            | BGTEN                          |          | CREPSEL                        | ALTK   | PS1-0   | SCCLK1  | SCRS    |  |  |

| SCIBUF   | AAh | Smart Card Buffer Register                                          | depends on | the convention<br>byte receive | on       | d on the I/O p<br>O pin when S |        |         | -       |         |  |  |

# <sup>36</sup> AT83R5122, AT8xC5122/23

| 7          | 6         | 5                                 | 4                                                                                                                                                                                                            | 3                                                                            | 2                               | 1                | 0          |  |  |  |

|------------|-----------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------|------------------|------------|--|--|--|

| -          | WDX2      | -                                 | SIX2                                                                                                                                                                                                         | -                                                                            | T1X2                            | T0X2             | X2         |  |  |  |

| Bit Number | Bit Mnemo | nic Descrip                       | tion                                                                                                                                                                                                         |                                                                              |                                 |                  |            |  |  |  |

| 7          | -         | Reserve<br>The valu               |                                                                                                                                                                                                              | nis bit is indete                                                            | erminate. Do no                 | ot set this bit. |            |  |  |  |

| 6          | WDX2      | This con<br>this bit h<br>Cleared | atchdog clock<br>his control bit is validated when the CPU clock X2 is set; when X2 is lov<br>s bit has no effect.<br>eared to bypass the 1/2 prescaler.<br>et to select the 1/2 output for this peripheral. |                                                                              |                                 |                  |            |  |  |  |

| 5          | -         | <b>Reserve</b><br>The valu        |                                                                                                                                                                                                              | nis bit is indete                                                            | erminate. Do no                 | ot set this bit. |            |  |  |  |

| 4          | SIX2      | This con<br>this bit h<br>Cleared | trol bit is valid<br>as no effect.<br>to bypass the                                                                                                                                                          | <b>ck (Mode 0 ar</b><br>lated when the<br>1/2 prescaler.<br>utput for this p | e CPU clock X2                  | 2 is set; when 2 | X2 is low, |  |  |  |

| 3          | -         | Reserve<br>The valu               |                                                                                                                                                                                                              | nis bit is indete                                                            | erminate. Do no                 | ot set this bit. |            |  |  |  |

| 2          | T1X2      | this bit h<br>Cleared             | trol bit is valid<br>as no effect.<br>to bypass the                                                                                                                                                          | ated when the<br>1/2 prescaler.<br>utput for this p                          |                                 | 2 is set; when 2 | X2 is low, |  |  |  |

| 1          | T0X2      | this bit h<br>Cleared             | trol bit is valid<br>as no effect.<br>to bypass the                                                                                                                                                          | ated when the<br>1/2 prescaler.<br>utput for this p                          |                                 | 2 is set; when 2 | X2 is low, |  |  |  |

| 0          | X2        | Cleared                           |                                                                                                                                                                                                              | PRT output for                                                               | CPU and all ti<br>to enable the |                  |            |  |  |  |

Table 26. Clock Configuration Register 0 - CKCON0 (S:8Fh)

IEC7816-3 says this procedure is mandatory in ATR for card supporting T=0 while EMV says this procedure is mandatory for T=0 but does not apply for ATR.

| Functional Description | The architecture of the Smart Card Interface Block can be detailed as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Barrel Shifter         | The Barrel Shifter performs the translation between 1 bit serial data and 8 bits parallel data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                        | The barrel function is useful for character repetition since the character is still present in the shifter at the end of the character transmission.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        | This shifter is able to shift the data in both directions and to invert the input or output value in order to manage both direct and inverse ISO7816-3 convention.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | Coupled with the barrel shifter is a parity checker and generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | There are 2 registers connected to this barrel shifter, one for the transmission and one for the reception. They act as buffers to relieve the CPU of timing constraints.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SCART FSM              | (Smart Card Asynchronous Receiver Transmitter Finite State Machine)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                        | This is the core of the block. Its purpose is to control the barrel shifter. To sequence correctly the barrel shifter for a reception or a transmission, it uses the signals issued by the different counters. One of the most important counters is the guard time counter that gives time slots corresponding to the character frame.                                                                                                                                                                                                                                                                                                                    |

|                        | The SCART FSM is enabled only in UART mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                        | The transition from the receipt mode to the transmit mode is done automatically. Priority is given to the transmission. Transmission refers to Terminal transmission to the ICC. Reception refers to reception by the Terminal from the ICC.                                                                                                                                                                                                                                                                                                                                                                                                               |

| ETU Counter            | The ETU (Elementary Timing Unit) counter controls the working frequency of the barrel shifter, in fact it generates the enable signal of the barrel shifter. It receives the Card Clock, and generates the ETU clock. The Card Clock frequency is called "f" below. The ETU counter is 11 bit wide.                                                                                                                                                                                                                                                                                                                                                        |

|                        | A special compensation mode can be activated. It accomodates situations where the ETU is not an integer number of Card Clock (CK_ISO). The compensation mode is controlled by the COMP bit in SCETU1 register bit position 7. With COMP=1 the ETU of every character even bits is reduced by 1 Card Clock period. As a result, the average ETU is : ETU_average = (ETU - 0.5). One should bear in mind that the ETU counter should be programmed to deliver a faster ETU which will be reduced by the COMP mechanism, not the other way around. This allows to reach the required precision of the character duration specified by the ISO7816-3 standard. |

|                        | Example1 : F=372, D=32 => ETU= F/D = 11.625 clock cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                        | We select ETU[10-0] = 12 , COMP=1. ETUaverage= 12 - (0.5*COMP) = 11.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                        | The result will be a full character duration (10 bit) = $(10 - 0.107)$ *ETU. The EMV specification is $(10 + - 0.2)$ *ETU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Guard Time Counter     | The minimum time between the leading edge of the start bit of 2 consecutive characters transmitted by the Terminal is controlled by the Guard Time counter, as described in Figure 32.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

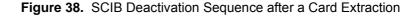

Removal of the smart card will automatically start the power off sequence as described in Figure 38.

The SCIB deactivation sequence after a reset of the CPU or after a lost of power supply is ISO7816-3 compliant. The switching order of the signals is the same as in Figure 38 but the delay between signals is analog and not clock dependent.

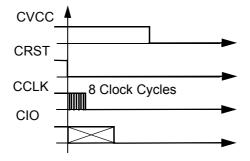

**Interrupt Generator** There are several sources of interruption but the SCIB macro-cell issues only one interrupt signal: SCIBIT.

This signal is high level active. Each of the sources is able to activate the SCIB interruption which is cleared when the Smart Card Interrupt register is read by the microcontroller.

If during the read of the Smart Card Interrupt register another interrupt occurs, the activation of the corresponding bit in the Smart Card Interrupt register and the new SCIB interruption is delayed until the interrupt register is read by the microcontroller.

**Warning** : Each bit of the SCIIR register is irrelevant while the corresponding interruption is disabled in SCIER register. When the interruption mode is not used, the bits of the SCISR register must be used instead of the bits of the SCIIR register.

| Table 44. | Smart Card | Interface | Control | Register | - SCICR | (S:B6h, SCRS = | 1) |

|-----------|------------|-----------|---------|----------|---------|----------------|----|

|-----------|------------|-----------|---------|----------|---------|----------------|----|

| 7          | 6            | 5                                                                                                                                                                                                                                                                                                                                              | 4                                                                                                                                                                                                                                            | 3                                                                                                                                                                                               | 2                                                                                                                                                     | 1                                                                                                                    | 0                                                                                                |

|------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| RESET      | CARDDET      | VCARD1                                                                                                                                                                                                                                                                                                                                         | VCARD0                                                                                                                                                                                                                                       | UART                                                                                                                                                                                            | WTEN                                                                                                                                                  | CREP                                                                                                                 | CONV                                                                                             |

| Bit Number | Bit Mnemonic | Description                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                 |                                                                                                                                                       |                                                                                                                      |                                                                                                  |

| 7          | RESET        | <b>Reset</b><br>Set this bit to reset ar<br>Clear this bit to activa<br>This bit acts as an ac                                                                                                                                                                                                                                                 | te the Smart Card                                                                                                                                                                                                                            | Interface.                                                                                                                                                                                      |                                                                                                                                                       |                                                                                                                      |                                                                                                  |

| 6          | CARDDET      | Card Presence Dete<br>Clear this bit to indica<br>Set this bit to indicate                                                                                                                                                                                                                                                                     | te the card present                                                                                                                                                                                                                          |                                                                                                                                                                                                 |                                                                                                                                                       | ``                                                                                                                   | 0,                                                                                               |

| 5-4        | VCARD[1:0]   | Card Voltage Select           VCARD[1]         VCARD[0]           0         0           0         1           1         0           1         1                                                                                                                                                                                                |                                                                                                                                                                                                                                              |                                                                                                                                                                                                 |                                                                                                                                                       |                                                                                                                      |                                                                                                  |

| 3          | UART         | Card UART Selectio<br>Clear this bit to use th<br>Set this bit to use the<br>Controls also the Wai                                                                                                                                                                                                                                             | ne CARDIO bit (P1.<br>Smart Card UART                                                                                                                                                                                                        | to drive the Card I/                                                                                                                                                                            | O pin (P1.0 pin).                                                                                                                                     | WT) Counter", pag                                                                                                    | je 67                                                                                            |

| 2          | WTEN         | Waiting Time Counter<br>Clear this bit to stop t<br>The hold registers are<br>Set this bit to start the<br>If the UART bit is set,<br>sent or received.                                                                                                                                                                                        | he counter and ena<br>e loaded with SCW<br>e Waiting Time Cou                                                                                                                                                                                | T0, SCWT1, SCWT<br>nter. The counters s                                                                                                                                                         | 2 and SCWT3 value<br>stop when it reaches                                                                                                             | es when SCWT2 is<br>the timeout value                                                                                | e.                                                                                               |

| 1          | CREP         | Character Repetition<br>Clear this bit to disable<br>character repetition in<br>Set this bit to enable<br>repetition when a pari<br>Depending upon CRE<br>up to 5times (4 repetit<br>is enabled, the SCPI<br>Alternately, the transr<br>(depending on CREP<br>register. If parity intern<br><b>Note</b> : Character repe<br>oriented protocol) | le parity error detec<br>n transmit mode.<br>parity error indicatio<br>ity error is indicated<br>EPSET bit is SCSR<br>tions) after which it<br>bit in SCIIR register<br>nitter will detect ICC<br>SEL bit in SCSR re<br>rupt is enabled, the | on on the Card I/O p<br>I in transmit mode.<br>register, the receive<br>will raise the parity of<br>r will be set too.<br>C character repetitio<br>gister), the transmit<br>SCPI bit in SCIIR r | oin in receive mode a<br>er can indicate parity<br>error bit SCPE bit in<br>on request. After 3 o<br>ter will raise the par<br>egister will be set to | and to set automat<br>/ error up to 4time:<br>the SCISR register<br>r 4 unsuccessful re-<br>ity error bit SCPE<br>0. | tic character<br>s (3 repetitions) of<br>r. If parity interrup<br>epetitions<br>bit in the SCISR |

| 0          | CONV         | ISO Convention<br>Clear this bit to use th<br>on the Card I/O pin re<br>Set this bit to use the<br>the Card I/O pin repres                                                                                                                                                                                                                     | presents a'0'.                                                                                                                                                                                                                               | × ,                                                                                                                                                                                             |                                                                                                                                                       |                                                                                                                      |                                                                                                  |

Reset Value = 0000 0000b

# Table 46. Smart Card UART Interface Status Register SCISR (S:ADh, SCRS=0)

| 7          | 6            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4                                                                                                              | 3                                              | 2                    | 1                     | 0                 |  |

|------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------|-----------------------|-------------------|--|

| SCTBE      | CARDIN       | ICARDOVF                                                                                                                                                                                                                                                                                                                                                                                                                             | VCARDOK                                                                                                        | SCWTO                                          | SCTC                 | SCRC                  | SCPE              |  |

| Bit Number | Bit Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                |                                                |                      |                       |                   |  |

| 7          | SCTBE        | This bit is set by ha<br>UART.                                                                                                                                                                                                                                                                                                                                                                                                       | uffer Empty Status<br>ardware when the T<br>dware when SCIBU                                                   | ransmit Buffer is co                           |                      | shift register of the | Smart Card        |  |

| 6          | CARDIN       | -                                                                                                                                                                                                                                                                                                                                                                                                                                    | atus<br>ardware if there is a<br>by hardware if there                                                          |                                                | •                    | o be done by softw    | are).             |  |

| 5          | ICARDOVF     | Card Current Ove<br>This bit is set when<br>on page 92)<br>It is cleared by han                                                                                                                                                                                                                                                                                                                                                      | the current on card                                                                                            | d is above the limit s                         | specified by bit OVF | FADJ in DCCKPS n      | egister (Table 61 |  |

| 4          | VCARDOK      | Card Voltage Corr<br>This bit is set when<br>It is cleared otherw                                                                                                                                                                                                                                                                                                                                                                    | n the output voltage                                                                                           | is within the voltag                           | e range specified by | y VCARD[1:0] in S(    | CICR register.    |  |

| 3          | SCWTO        | This bit is set by ha                                                                                                                                                                                                                                                                                                                                                                                                                | Inter Timeout Statu<br>ardware when the W<br>reload of the counter                                             | aiting Time Counte                             |                      |                       |                   |  |

| 2          | SCTC         | This bit is set by ha<br>selected, this bit wi<br>bit will not be set.                                                                                                                                                                                                                                                                                                                                                               | d Character Status<br>Irdware when the Sr<br>II be set only after a<br>ware when this regi                     | nart Card UART ha<br>successful transmi        |                      |                       |                   |  |

| 1          | SCRC         | It is cleared by hard<br>only after a succes                                                                                                                                                                                                                                                                                                                                                                                         | character Status<br>ardware when the S<br>dware when SCIBUI<br>sful reception. If the<br>s value if necessary. | F register is read. If<br>last allowed repetit | character repetition | mode is selected,     |                   |  |

| 0          | SCPE         | Character Reception Parity Error Status<br>This bit is set when a parity error is detected on the received character.<br>It is cleared by software when this register is read. If character repetition mode is selected, this bit will be set only<br>if the ICC report an error on the last allowed repetition of a TERMINAL transmission, or if a reception parity error<br>is found on the last allowed ICC character repetition. |                                                                                                                |                                                |                      |                       |                   |  |

Reset Value = 1000 0000b

## Table 59. Smart Card Clock Reload Register - SCICLK (S:C1h, SCRS=1)

| 7          | 6            | 5                                                                                                                                                                                                                                                                                                                                      | 4       | 3       | 2       | 1       | 0       |  |

|------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|--|

| XTSCS      | -            | SCICLK5                                                                                                                                                                                                                                                                                                                                | SCICLK4 | SCICLK3 | SCICLK2 | SCICLK1 | SCICLK0 |  |

| Bit Number | Bit Mnemonic | Description                                                                                                                                                                                                                                                                                                                            |         |         |         |         |         |  |

| 7          | XTSCS        | Smart Card Clock Selection Bit<br>If XTSCS bit is set OR EXT48 bit is set (in PLLCON register) , CK_PLL is used to generate CK_ISO.<br>Otherwise, CK_XTAL1 is used to generate CK_ISO.<br>See the Clock Tree diagram figure 17.                                                                                                        |         |         |         |         |         |  |

| 6          | -            | Reserved<br>The value read from this bit is indeterminate. Do not change these bits.                                                                                                                                                                                                                                                   |         |         |         |         |         |  |

| 5 - 0      | SCICLK[5:0]  | SCIB clock reload register         Prescaler 2 reload value is used to defines the card clock frequency.         If SCICLK[5:0] is smaller than 48 :         Fck_iso = Fck_pll or Fck_XTAL1/ (2 * (48 - SCICLK[5:0]))         If SCICLK[5:0] is equal to 48 :         Fck_iso = Fck_XTAL1         SCICLK[5:0] must be smaller than 49. |         |         |         |         |         |  |

Reset Value = 0X10 1111b (default value for a divider by two)

| DC/DC Converter | The Smart Card voltage (CVCC) is supplied by the integrated DC/DC converter which is<br>controlled by several registers:                                                                                                                                                                                                                    |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | • The SCICR register (Table 44 on page 77) controls the CVCC level by means of bits VCARD[1:0].                                                                                                                                                                                                                                             |

|                 | <ul> <li>The SCCON register (Table 45 on page 78) enables to switch the DC/DC converter<br/>on or off by means of bit CARDVCC.</li> </ul>                                                                                                                                                                                                   |

|                 | • The DCCKPS register (Table 61 on page 92) controls the DC/DC clock and current.                                                                                                                                                                                                                                                           |

|                 | The DC/DC converter cannot be switched on while the CPRES pin remains inactive. If CPRES pin becomes inactive while the DC/DC converter is operating an automatic shut down sequence of the DC/DC converter is initiated by the electronics.                                                                                                |

|                 | It is mandatory to switch off the DC/DC Converter before entering in Power-down mode.                                                                                                                                                                                                                                                       |

| Configuration   | The DC/DC Converter can work in two different modes which are selected by bit MODE in DCCKPS register:                                                                                                                                                                                                                                      |

|                 | <ul> <li>Pump Mode: an external inductance of 10 µH must be connected between pins LI<br/>and VCC. VCC can be higher or lower than CVCC.</li> </ul>                                                                                                                                                                                         |

|                 | <ul> <li>Regulator mode : no external inductance is required but VCC must be always higher<br/>than CVCC+0.3V. The Regulation mode will work even if an external inductance of<br/>10 µH is connected between pins LI and VCC</li> </ul>                                                                                                    |

|                 | The DC/DC clock prescaler which is controlled by bits DCCKPS[3:0], in DCCKPS register must be configured to set the DC/DC clock to a working frequency of 4 MHz which depends upon the value of the crystal. There is no need to change the default configuration set by the reset sequence if an 8 MHz crystal is used by the application. |

|                 | The DC/DC Converter implements a current overflow controller which avoids permanent damage of the DC/DC converter in case of short circuit between CVCC and CVSS. The maximum limit is around 100 mA. It is possible to increase this limit in normal operating                                                                             |

### **Miscellaneous**

| USB Reset                | The EORINT bit in the USBINT register is set by hardware when a End of Reset has<br>been detected on the USB bus. This triggers a USB interrupt if enabled. The USB con-<br>troller is still enabled, but all the USB registers are reset by hardware. The firmware<br>should clear the EORINT bit to allow the next USB reset detection.                                       |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STALL Handshake          | This function is only available for Control, Bulk, and Interrupt endpoints.                                                                                                                                                                                                                                                                                                     |

|                          | The firmware has to set the STALLRQ bit in the UEPSTAX register to send a STALL handshake at the next request of the Host on the endpoint selected with the UEPNUM register. The RXSETUP, TXRDY, TXCMPL, RXOUTB0 and RXOUTB1 bits must be first reset to 0. The bit STLCRC is set at 1 by the USB controller when a STALL has been sent. This triggers an interrupt if enabled. |

|                          | The firmware should clear the STALLRQ and STLCRC bits after each STALL sent.<br>The STALLRQ bit is cleared automatically by hardware when a valid SETUP PID is<br>received on a CONTROL type endpoint.                                                                                                                                                                          |

| Start of Frame Detection | The SOFINT bit in the USBINT register is set when the USB controller detects a Start Of Frame PID. This triggers an interrupt if enabled. The firmware should clear the SOFINT bit to allow the next Start of Frame detection.                                                                                                                                                  |

| Frame Number             | When receiving a Start of Frame, the frame number is automatically stored in the UFNUML and UFNUMH registers. The CRCOK and CRCERR bits indicate if the CRC of the last Start Of Frame is valid (CRCOK set at 1) or corrupt (CRCERR set at 1). The UFNUML and UFNUMH registers are automatically updated when receiving a new Start of Frame.                                   |

| Data Toggle Bit          | The Data Toggle bit is set by hardware when a DATA 0 packet is received and accepted<br>by the USB controller and cleared by hardware when a DATA 1 packet is received and<br>accepted by the USB controller. This bit is reset when the firmware resets the endpoint<br>FIFO using the UEPRST register.                                                                        |

|                          | For Control endpoints, each SETUP transaction starts with a DATA 0 and data toggling is then used as for Bulk endpoints until the end of the Data stage (for a control write transfer). The Status stage completes the data transfer with a DATA 1 (for a control read transfer).                                                                                               |

|                          | For Isochronous endpoints, the device firmware should ignore the data-toggle.                                                                                                                                                                                                                                                                                                   |

| NAK Handshakes           | When a NAK handshake is sent by the USB controller to a IN or OUT request from the Host, the NAKIN or NAKOUT bit is set by hardware. This information can be used to determine the direction of the communication during a Control transfer. These bits are cleared by software.                                                                                                |

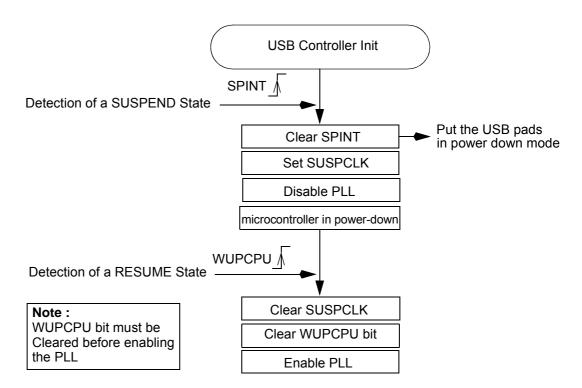

Figure 58. Example of a Suspend/Resume Management

Warning: The core must be switched in external clock mode before disabling the PLL.

Upstream Resume A USB device can be allowed by the Host to send an upstream resume for Remote Wake-up purpose.

When the USB controller receives the SET\_FEATURE request: DEVICE\_REMOTE\_WAKEUP, the firmware should set to 1 the RMWUPE bit in the USBCON register to enable this function. RMWUPE value should be 0 in the other cases.

If the device is in SUSPEND mode, the USB controller can send an upstream resume by clearing first the SPINT bit in the USBINT register and by setting then to 1 the SDRM-WUP bit in the USBCON register. The USB controller sets to 1 the UPRSM bit in the USBCON register. All clocks must be enabled first. The Remote Wake is sent only if the USB bus was in Suspend state for at least 5 ms. When the upstream resume is completed, the UPRSM bit is reset to 0 by hardware. The firmware should then clear the SDRMWUP bit.

# **Serial I/O Port** The serial I/O port in the AT83R5122, AT8xC5122/23 is compatible with the serial I/O port in the 80C52.

The I/O port provides both synchronous and asynchronous communication modes. It operates as an Universal Asynchronous Receiver and Transmitter (UART) in three full-duplex modes (Modes 1, 2 and 3). Asynchronous transmission and reception can occur simultaneously and at different baud rates

Serial I/O port includes the following enhancements:

- Framing error detection

- Automatic address recognition

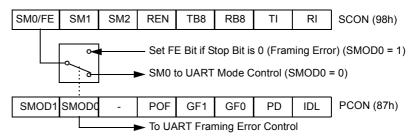

**Framing Error Detection** Framing bit error detection is provided for the three asynchronous modes (Modes 1, 2 and 3). To enable the framing bit error detection feature, set SMOD0 bit in PCON register (See Figure 64).

### Figure 64. Framing Error Block Diagram

When this feature is enabled, the receiver checks each incoming data frame for a valid stop bit. An invalid stop bit may result from noise on the serial lines or from simultaneous transmission by two CPUs. If a valid stop bit is not found, the Framing Error bit (FE) in SCON register (See Figure 69 on page 128) bit is set.

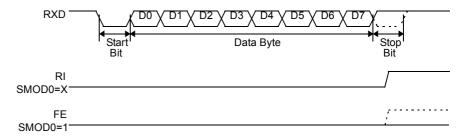

Software may examine FE bit after each reception to check for data errors. Once set, only software or a reset can clear FE bit. Subsequently received frames with valid stop bits cannot clear FE bit. When FE feature is enabled, RI rises on stop bit instead of the last data bit (See Figure 65 and Figure 66).

Figure 65. UART Timings in Mode 1

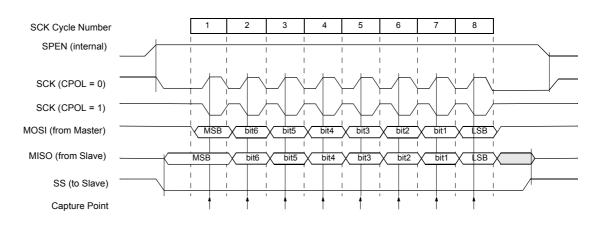

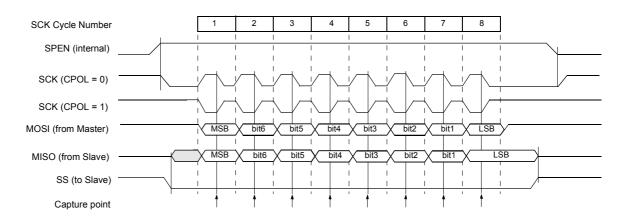

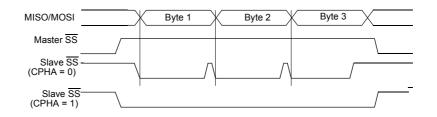

Figure 85. Data Transmission Format (CPHA = 0)

Figure 86. Data Transmission Format (CPHA = 1)

As shown in Figure 85, the first SCK edge is the MSB capture strobe. Therefore the Slave must begin driving its data before the first SCK edge, and a falling edge on the SS pin is used to start the transmission. The SS pin must be toggled high and then low between each byte transmitted (Figure 87).

Figure 87. CPHA/SS Timing

Figure 86 shows an SPI transmission in which CPHA is "1". In this case, the Master begins driving its MOSI pin on the first SCK edge. Therefore, the Slave uses the first SCK edge as a start transmission signal. The SS pin can remain low between transmis-

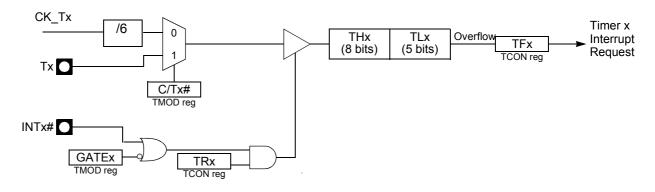

For normal Timer operation (GATE0= 0), setting TR0 allows TL0 to be incremented by the selected input. Setting GATE0 and TR0 allows external pin INT0# to control Timer operation.

Timer 0 overflow (count rolls over from all 1s to all 0s) sets the TF0 flag and generates an interrupt request.

It is important to stop the Timer/Counter before changing modes.

Mode 0 (13-bit Timer)Mode 0 configures Timer 0 as a 13-bit Timer which is set up as an 8-bit Timer (TH0 register) with a modulo-32 prescaler implemented with the lower five bits of the TL0 register (see Figure 89). The upper three bits of the TL0 register are indeterminate and should be ignored. Prescaler overflow increments the TH0 register.

Figure 90 gives the overflow period calculation formula.

Figure 89. Timer/Counter x (x= 0 or 1) in Mode 0

Figure 90. Mode 0 Overflow Period Formula

$$\mathsf{TFx}_{\mathsf{PER}} = \frac{-6 \cdot (\mathsf{16384} - (\mathsf{THx}, \mathsf{TLx}))}{\mathsf{F}_{\mathsf{CK}_{\mathsf{TX}}}}$$

Mode 1 (16-bit Timer)Mode 1 configures Timer 0 as a 16-bit Timer with the TH0 and TL0 registers connected<br/>in a cascade (see Figure 91). The selected input increments the TL0 register.

Figure 92 gives the overflow period calculation formula when in timer mode.

# Interrupt Sources and Vectors

### Table 108. Interrupt Vectors

| Interrupt Source                   | Polling Priority<br>at Same Level | Vector<br>Address |  |

|------------------------------------|-----------------------------------|-------------------|--|

| Reset                              | 0<br>(Highest Priority)           | C:0000h           |  |

| INTO                               | 1                                 | C:0003h           |  |

| Timer 0                            | 2                                 | C:000Bh           |  |

| INT1                               | 3                                 | C:0013h           |  |

| Timer 1                            | 4                                 | C:001Bh           |  |

| UART                               | 6                                 | C:0023h           |  |

| Reserved                           | 7                                 | C:002Bh           |  |

| Reserved                           | 5                                 | C:0033h           |  |

| Keyboard Controller <sup>(1)</sup> | 8                                 | C:003Bh           |  |

| Reserved                           | 9                                 | C:0043h           |  |

| SPI Controller <sup>(1)</sup>      | 10                                | C:004Bh           |  |

| Smart Card Controller              | 11                                | C:0053h           |  |

| Reserved                           | 12                                | C:005Bh           |  |

| Reserved                           | 13                                | C:0063h           |  |

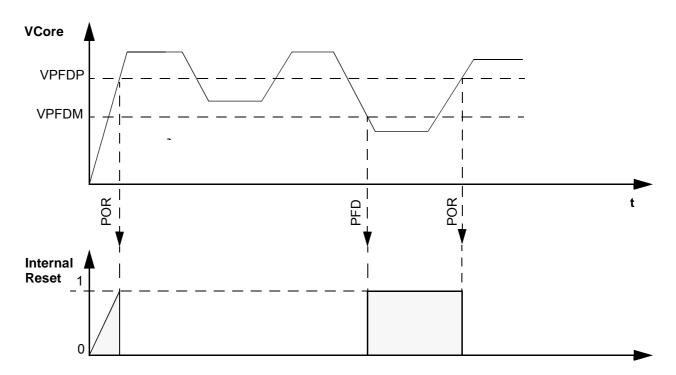

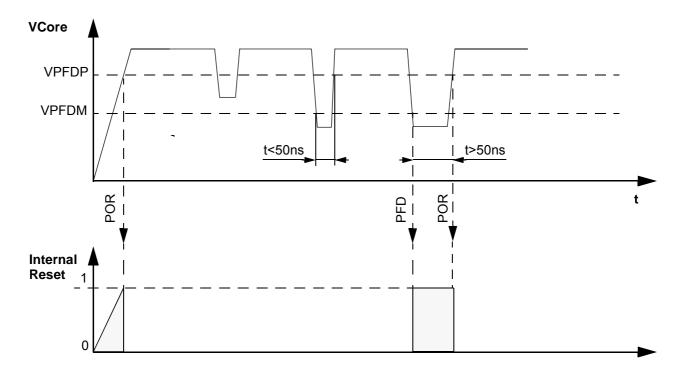

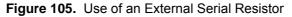

| USB Controller                     | 14                                | C:006Bh           |  |