# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | CIP-51 8051                                                            |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 72MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SMBus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 29                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1.25K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                            |

| Data Converters            | A/D 20x14b; D/A 2x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-UFQFN Exposed Pad                                                   |

| Supplier Device Package    | 32-QFN (4x4)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm8lb11f16e-b-qfn32 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Low Pin Count Package Description

AT83C5123 version

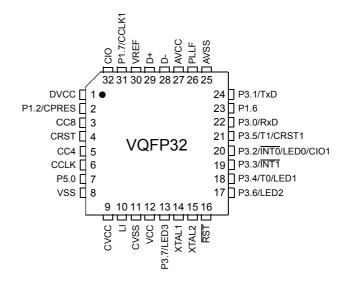

Figure 6. VQFP32 Package Pinout

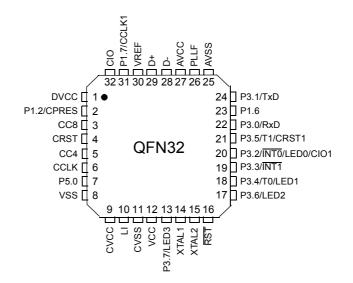

Figure 7. QFN32 Package Pinout

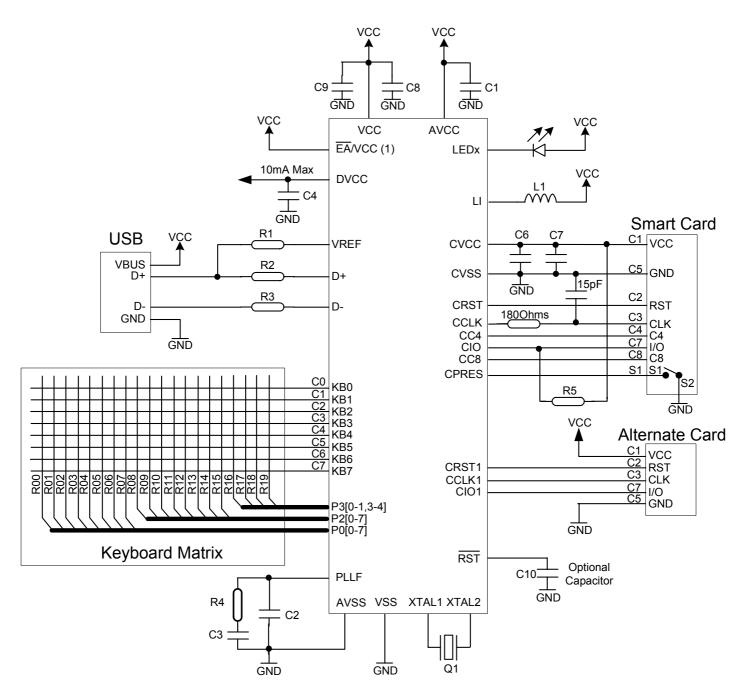

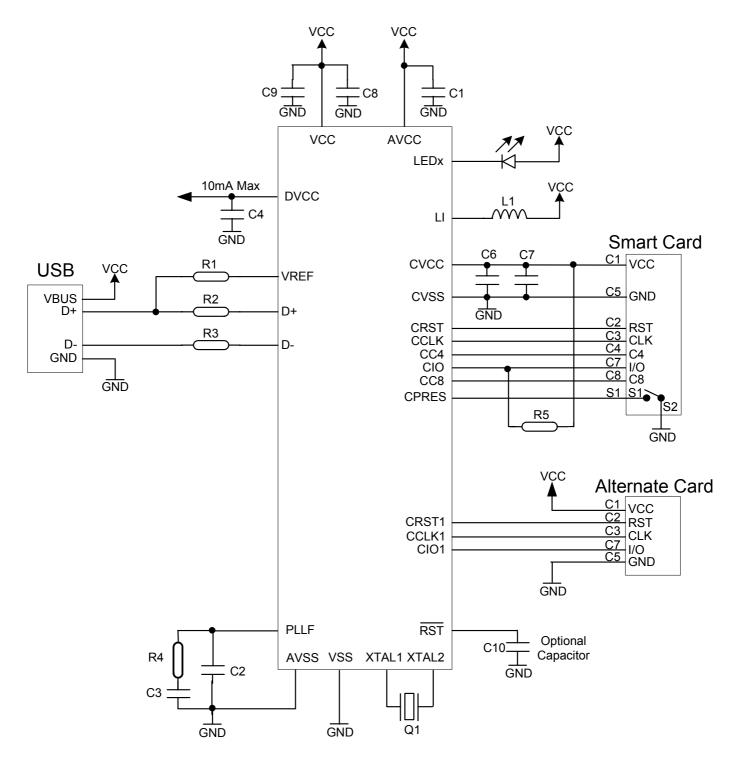

USB Keyboard with Smart Card Reader Using AT83R5122, AT8xC5122/AT89C5122DS

Notes : 1 - Pin configuration depends on product versions

<sup>16</sup> AT83R5122, AT8xC5122/23

## USB Smart Card Reader Using the AT83C5123 Version

## Registers

| 7             | 6               | 5                                                                                    | 4                                                                                                                                                                                                                                                            | 3 | 2    | 1      | 0  |  |  |  |  |

|---------------|-----------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|--------|----|--|--|--|--|

| DPU           | -               | -                                                                                    | -                                                                                                                                                                                                                                                            |   | XRS0 | EXTRAM | AO |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                          | Description                                                                                                                                                                                                                                                  |   |      |        |    |  |  |  |  |

| 7             | DPU             | <b>Disable weak</b><br>0<br>1                                                        |                                                                                                                                                                                                                                                              |   |      |        |    |  |  |  |  |

| 6-3           | -               | Reserved<br>The value read from this bit is indeterminate. Do not change these bits. |                                                                                                                                                                                                                                                              |   |      |        |    |  |  |  |  |

| 2             | XRS0            | <b>XRAM Size</b><br>0<br>1                                                           | 0 256 bytes (default)                                                                                                                                                                                                                                        |   |      |        |    |  |  |  |  |

| 1             | EXTRAM          | Set to access<br>Programmed b                                                        | EXTRAM bit<br>Cleared to access internal XRAM using MOVX @ Ri/ @ DPTR.<br>Set to access external memory.<br>Programmed by hardware after Power-up regarding Hardware Security Byte<br>(HSB), default setting , XRAM selected.                                |   |      |        |    |  |  |  |  |

| 0             | AO              | Cleared , ALE<br>X2 mode is us                                                       | (HSB), default setting , XRAM selected.<br><b>ALE Output bit</b><br>Cleared , ALE is emitted at a constant rate of 1/6 the oscillator frequency (or 1/3 i<br>X2 mode is used)(default).<br>Set , ALE is active only when a MOVX or MOVC instruction is used. |   |      |        |    |  |  |  |  |

#### Table 5. Auxiliary Register - AUXR (8Eh)

Reset Value = 0XXX X000b

| 7             | 6               | 5                                                                                  | 4                                                                                                                                                                                                                                                                                                                                                                                              | 3              | 2              | 1              | 0   |  |  |  |

|---------------|-----------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|----------------|-----|--|--|--|

| -             | -               | ENBOOT                                                                             | -                                                                                                                                                                                                                                                                                                                                                                                              | GF3            | 0              | -              | DPS |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                    |                |                |                |     |  |  |  |

| 7 - 6         | -               | <b>Reserved</b><br>The value read                                                  | eserved<br>he value read from this bit is indeterminate. Do not change these bits.                                                                                                                                                                                                                                                                                                             |                |                |                |     |  |  |  |

| 5             | ENBOOT          | Set this bit to n<br>beyond 7FFFh<br>Clear this bit to<br>the code is feto         | Enable Boot ROM (CRAM / E2PROM version only)<br>Set this bit to map the Boot ROM from 8000h to FFFFh. If the PC increments<br>beyond 7FFFh address, the code is fetch from internal ROM<br>Clear this bit to disable Boot ROM. If the PC increments beyond 7FFFh address,<br>the code is fetch from external code memory (C51 standard roll over function)<br>This bit is forced to 1 at reset |                |                |                |     |  |  |  |

| 4             | -               | <b>Reserved</b><br>The value read                                                  | from this bit                                                                                                                                                                                                                                                                                                                                                                                  | is indetermina | te. Do not cha | inge this bit. |     |  |  |  |

| 3             | GF3             | This bit is a ge                                                                   | neral-purpose                                                                                                                                                                                                                                                                                                                                                                                  | user flag.     |                |                |     |  |  |  |

| 2             | 0               | Always cleared                                                                     | -                                                                                                                                                                                                                                                                                                                                                                                              |                |                |                |     |  |  |  |

| 1             | -               | Reserved<br>The value read from this bit is indeterminate. Do not change this bit. |                                                                                                                                                                                                                                                                                                                                                                                                |                |                |                |     |  |  |  |

| 0             | DPS             | Data Pointer S<br>Cleared to sele                                                  |                                                                                                                                                                                                                                                                                                                                                                                                | t to select DP | TR1.           |                |     |  |  |  |

#### Table 6. Auxiliary Register 1 AUXR1- (0A2h) for AT8xC5122

Reset Value = XX1X XX0X0b (Not bit addressable)

#### Table 7. Auxiliary Register 1 AUXR1- (0A2h) for AT83C5123

| 7             | 6               | 5                                                        | 4                                                                                    | 3              | 2              | 1               | 0   |  |  |  |

|---------------|-----------------|----------------------------------------------------------|--------------------------------------------------------------------------------------|----------------|----------------|-----------------|-----|--|--|--|

| -             | -               | -                                                        | -                                                                                    | GF3            | 0              | -               | DPS |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                              |                                                                                      |                |                |                 |     |  |  |  |

| 7 - 6         | -               | Reserved<br>The value read                               | I from this bit                                                                      | is indetermina | te. Do not cha | inge these bits | 6.  |  |  |  |

| 5             |                 | Reserved<br>The value read                               | teserved<br>The value read from this bit is indeterminate. Do not change these bits. |                |                |                 |     |  |  |  |

| 4             | -               | Reserved<br>The value read                               | I from this bit                                                                      | is indetermina | te. Do not cha | inge this bit.  |     |  |  |  |

| 3             | GF3             | This bit is a ge                                         | neral-purpose                                                                        | e user flag.   |                |                 |     |  |  |  |

| 2             | 0               | Always cleared                                           | 1.                                                                                   |                |                |                 |     |  |  |  |

| 1             | -               | Reserved<br>The value read                               | Reserved<br>The value read from this bit is indeterminate. Do not change this bit.   |                |                |                 |     |  |  |  |

| 0             | DPS             | Data Pointer S<br>Cleared to select D<br>Set to select D | ect DPTR0.                                                                           |                |                |                 |     |  |  |  |

Reset Value = XXXX XX0X0b (Not bit addressable)

## <sup>32</sup> AT83R5122, AT8xC5122/23

2. Grey areas : do not write in.

|                     | 0/8                 | 1/9                                                                     | 2/A                 | 3/B                 | 4/C                                | 5/D                                | 6/E                               | 7/F                  |

|---------------------|---------------------|-------------------------------------------------------------------------|---------------------|---------------------|------------------------------------|------------------------------------|-----------------------------------|----------------------|

| F8h                 | UEPINT<br>0000 0000 |                                                                         |                     |                     |                                    |                                    |                                   |                      |

| F0h                 | B<br>0000 0000      | LEDCON0<br>0000 0000                                                    |                     |                     |                                    |                                    |                                   |                      |

| E8h                 | P5<br>1111 1111     |                                                                         |                     |                     |                                    |                                    |                                   |                      |

| E0h                 | ACC<br>0000 0000    | LEDCON1<br>XX00 0000                                                    | UBYCTX<br>0000 0000 |                     |                                    |                                    |                                   |                      |

| D8h                 |                     |                                                                         |                     |                     |                                    |                                    |                                   |                      |

| D0h                 | PSW<br>0000 0000    | RCON<br>XXXX 0XXX                                                       |                     |                     | UEPCONX<br>1000 0000               | UEPRST<br>0000 0000                |                                   |                      |

| C8h                 |                     |                                                                         |                     |                     |                                    |                                    | UEPSTAX<br>0000 0000              | UEPDATX<br>0000 0000 |

| S 1<br>C COh<br>R 0 | P4<br>1111 1111     | SCICLK <sup>(1)</sup><br>0X10 1111<br>SCWT3 <sup>(1)</sup><br>0000 0000 | UEPIEN<br>0000 0000 | SPCON<br>0001 0100  | SPSTA<br>0000 0000                 | SPDAT<br>1111 1111                 | USBADDR<br>1000 0000              | UEPNUM<br>0000 0000  |

| B8h                 | IPL0<br>X000 000    | SADEN<br>0000 0000                                                      | UFNUML<br>0000 0000 | UFNUMH<br>0000 0000 | USBCON<br>0000 0000                | USBINT<br>0000 0000                | USBIEN<br>0000 0000               | DCCKPS<br>0000 0000  |

| 6 1<br>C Bob        | P3                  | IEN1                                                                    | IPL1                | IPH1                | SCGT0 <sup>(1)</sup><br>0000 1100  | SCGT1 <sup>(1)</sup><br>XXXX XXX0  | SCICR <sup>(1)</sup><br>0000 0000 | IPH0                 |

| BOh<br>S 0          | 1111 1111           | XXXX X000                                                               | 00XX 00X0           | 00XX 00X0           | SCWT0 <sup>(1)</sup><br>1000 0000  | SCWT1 <sup>(1)</sup><br>0010 0101  | SCWT2 <sup>(1)</sup><br>0000 0000 | X000 0000            |

| 6 1<br>C Ash        | IEN0                | SADDR                                                                   | SCIBUF              | SCSR                | SCETU0 <sup>(1)</sup><br>0111 0100 | SCETU1 <sup>(1)</sup><br>XXXX X001 | SCIER <sup>(1)</sup><br>0X00 0000 |                      |

| A8h<br>S 0          | 0000 0000           | 0000 0000                                                               | XXXX XXXX           | X000 1000           | SCCON <sup>(1)</sup><br>0000 0000  | SCISR <sup>(1)</sup><br>10X0 0000  | SCIIR <sup>(1)</sup><br>0X00 0000 |                      |

| A0h                 | P2<br>1111 1111     | ISEL<br>0000 0100                                                       | AUXR1<br>XX1X 0XX0  | PLLCON<br>XXXX X000 | PLLDIV<br>0000 0000                |                                    | WDTRST<br>XXXX XXXX               | WDTPRG<br>XXXX X000  |

| 98h                 | SCON<br>0000 0000   | SBUF<br>XXXX XXXX                                                       | BRL<br>0000 0000    | BDRCON<br>XXX0 0000 | KBLS<br>0000 0000                  | KBE<br>0000 0000                   | KBF<br>0000 0000                  |                      |

| 90h                 | P1<br>1111 1111     | PMOD0 <sup>(2)</sup><br>0000 0000                                       |                     |                     |                                    |                                    |                                   | CKRL<br>XXXX 1111    |

| 88h                 | TCON<br>0000 0000   | TMOD<br>0000 0000                                                       | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000                   | TH1<br>0000 0000                   | AUXR<br>0XXX X000                 | CKCON0<br>X0X0 X000  |

| 80h                 | P0<br>1111 1111     | SP<br>0000 0111                                                         | DPL<br>0000 0000    | DPH<br>0000 0000    | PMOD1<br>0000 0000                 | CKSEL<br>XXXX XXX0                 |                                   | PCON<br>00X1 0000    |

## AT8xC5122 Version

Bit addressable

Not bit addressable

## SFR's Description

Table 10. C51 Core SFRs

| Mnemonic | Add | Name                                    | 7   | 6   | 5  | 4   | 3   | 2  | 1  | 0 |

|----------|-----|-----------------------------------------|-----|-----|----|-----|-----|----|----|---|

| ACC      | E0h | Accumulator                             | ACC |     |    |     |     |    |    |   |

| В        | F0h | B Register                              |     | В   |    |     |     |    |    |   |

| PSW      | D0h | Program Status Word                     | CY  | AC  | F0 | RS1 | RS0 | OV | F1 | Р |

| SP       | 81h | Stack Pointer                           |     |     |    | S   | P   |    |    |   |

| DPL      | 82h | Data Pointer Low byte (LSB of DPTR)     |     | DPL |    |     |     |    |    |   |

| DPH      | 83h | Data Pointer High byte<br>(MSB of DPTR) |     | DPH |    |     |     |    |    |   |

#### Table 11. Clock SFRs

| Mnemonic            | Add | Name                         | 7     | 6     | 5                     | 4    | 3         | 2     | 1      | 0     |

|---------------------|-----|------------------------------|-------|-------|-----------------------|------|-----------|-------|--------|-------|

| PCON                | 87h | Power Controller             | SMOD1 | SMOD0 |                       | POF  | GF1       | GF0   | PD     | IDL   |

| CKCON0              | 8Fh | Clock Controller 0           |       | WDX2  |                       | SIX2 |           | T1X2  | T0X2   | X2    |

| CKCON1              | AFh | Clock Controller 1           |       |       |                       |      |           |       |        | SPIX2 |

| CKSEL               | 85h | Clock Selection              |       |       |                       |      |           |       |        | CKS   |

| CKRL                | 97h | Clock Reload Register        |       |       |                       |      | CKREL 3-0 |       |        |       |

| PLLCON              | A3h | PLL Controller Register      |       |       |                       |      |           | EXT48 | PLLEN  | PLOCK |

| PLLDIV              | A4h | PLL Divider register         |       | F     | 3-0                   |      |           | N     | 3-0    |       |

| AUXR                | 8Eh | Auxiliary Register 0         | DPU   |       |                       |      |           | XRS0  | EXTRAM | A0    |

| AUXR1               | A2h | Auxiliary Register 1         |       |       | ENBOOT <sup>(1)</sup> |      | GF3       |       |        | DPS   |

| RCON <sup>(1)</sup> | D1h | CRAM memory<br>Configuration |       |       |                       |      | RPS       |       |        |       |

Note: 1. Only for AT8xC5122

### Table 12. I/O Port SFRs

| Mnemonic          | Add | Name                 | 7                    | 6                    | 5                    | 4                    | 3               | 2     | 1                   | 0                   |

|-------------------|-----|----------------------|----------------------|----------------------|----------------------|----------------------|-----------------|-------|---------------------|---------------------|

| P0 <sup>(1)</sup> | 80h | Port 0               |                      | P0                   |                      |                      |                 |       |                     |                     |

| P1                | 90h | Port 1               |                      | P1                   |                      |                      |                 |       |                     |                     |

| P2 <sup>(1)</sup> | A0h | Port 2               |                      | P2                   |                      |                      |                 |       |                     |                     |

| P3                | B0h | Port 3               |                      |                      |                      |                      | P3              |       |                     |                     |

| P4 <sup>(1)</sup> | C0h | Port 4               |                      |                      |                      |                      | P4              |       |                     |                     |

| P5                | E8h | Port 5               |                      |                      |                      | P5 (only P5.0        | ) for AT8xC5122 | 2)    |                     |                     |

| PMOD0             | 91h | Port Mode Register 0 | P3C1                 | P3C0                 | P2C1 <sup>(1)</sup>  | P2C0 <sup>(1)</sup>  | CPRESRES        | -     | P0C1 <sup>(1)</sup> | P0C0 <sup>(1)</sup> |

| PMOD1             | 84h | Port Mode Register 1 | P5HC1 <sup>(1)</sup> | P5HC0 <sup>(1)</sup> | P5MC1 <sup>(1)</sup> | P5MC0 <sup>(1)</sup> | P5LC1           | P5LC0 | P4C1 <sup>(1)</sup> | P4C0 <sup>(1)</sup> |

Note: 1. Only for AT8xC5122

## <sup>34</sup> AT83R5122, AT8xC5122/23

### **Port Configuration**

Standard I/O P0

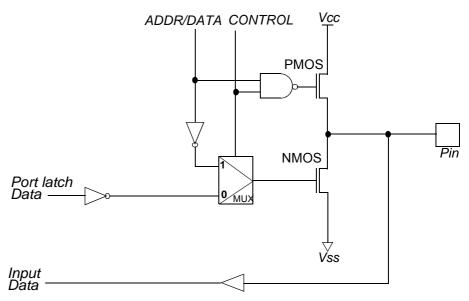

The P0 port is described in Figure 22.

Figure 22. Standard Input/Output Port

Quasi Bi-directional Port The default port output configuration for standard I/O ports is the quasi-bi-directional output that is common on the 80C51 and most of its derivatives. The "Port51" output type can be used as both an input and output without the need to reconfigure the port. This is possible because when the port outputs a logic high, it is weakly driven, allowing an external device to pull the pin low.

When the port outputs a logic low state, it is driven strongly and is able to sink a fairly large current.

These features are somewhat similar to an open-drain output except that there are three pull-up transistors in the quasi-bi-directional output that serve different purposes.

One of these pull-ups, called the weak pull-up, is turned on whenever the port latch for the pin contains a logic 1. The weak pull-up sources a very small current that will pull the pin high if it is left floating. The weak pull-up can be turned off by the DPU bit in AUXR register.

A second pull-up, called the medium pull-up, is turned on when the port latch for the pin contains a logic 1 and the pin itself is also at a logic 1 level. This pull-up provides the primary source current for a quasi-bi-directional pin that is outputting a 1. If a pin that has a logic 1 on it is pulled low by an external device, the medium pull-up turns off, and only the weak pull-up remains on. In order to pull the pin low under these conditions, the external device has to sink enough current to overpower the medium pull-up and take the voltage on the port pin below its input threshold.

Note: for CIO, CC4, CC8 ports of SCIB interface , in input mode when the ICC (smart card) is driving the port pin :

- if 0 < Vin < CVCC/2 : weak pull-up is active (~100KOhm)</li>

- if CVCC/2 < Vin < CVCC : weak (~100KOhm) and medium (~12KOhm) pullup's are active

| Table 44. | Smart Card | Interface | Control | Register | - SCICR | (S:B6h, SCRS = | 1) |

|-----------|------------|-----------|---------|----------|---------|----------------|----|

|-----------|------------|-----------|---------|----------|---------|----------------|----|

| 7          | 6            | 5                                                                                                                                                                                                                                                                                                                                              | 4                                                                                                                                                                                                                                            | 3                                                                                                                                                                                               | 2                                                                                                                                                     | 1                                                                                                                    | 0                                                                                                |

|------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| RESET      | CARDDET      | VCARD1                                                                                                                                                                                                                                                                                                                                         | VCARD0                                                                                                                                                                                                                                       | UART                                                                                                                                                                                            | WTEN                                                                                                                                                  | CREP                                                                                                                 | CONV                                                                                             |

| Bit Number | Bit Mnemonic | Description                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                 |                                                                                                                                                       |                                                                                                                      |                                                                                                  |

| 7          | RESET        | <b>Reset</b><br>Set this bit to reset ar<br>Clear this bit to activa<br>This bit acts as an ac                                                                                                                                                                                                                                                 | te the Smart Card                                                                                                                                                                                                                            | Interface.                                                                                                                                                                                      |                                                                                                                                                       |                                                                                                                      |                                                                                                  |

| 6          | CARDDET      | Card Presence Dete<br>Clear this bit to indica<br>Set this bit to indicate                                                                                                                                                                                                                                                                     | te the card present                                                                                                                                                                                                                          |                                                                                                                                                                                                 |                                                                                                                                                       | ``                                                                                                                   | 0,                                                                                               |

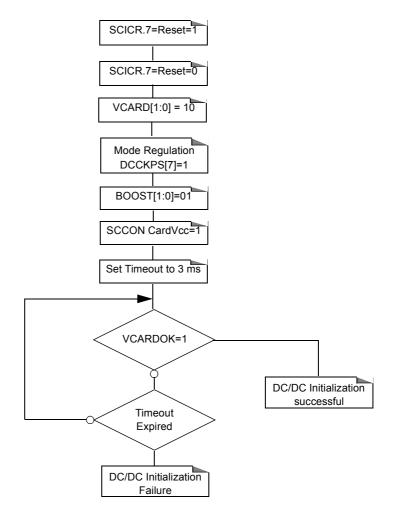

| 5-4        | VCARD[1:0]   | Card Voltage Select           VCARD[1]         VCARD[0]           0         0           0         1           1         0           1         1                                                                                                                                                                                                |                                                                                                                                                                                                                                              |                                                                                                                                                                                                 |                                                                                                                                                       |                                                                                                                      |                                                                                                  |

| 3          | UART         | Card UART Selectio<br>Clear this bit to use th<br>Set this bit to use the<br>Controls also the Wai                                                                                                                                                                                                                                             | ne CARDIO bit (P1.<br>Smart Card UART                                                                                                                                                                                                        | to drive the Card I/                                                                                                                                                                            | O pin (P1.0 pin).                                                                                                                                     | WT) Counter", pag                                                                                                    | je 67                                                                                            |

| 2          | WTEN         | Waiting Time Counter<br>Clear this bit to stop t<br>The hold registers are<br>Set this bit to start the<br>If the UART bit is set,<br>sent or received.                                                                                                                                                                                        | he counter and ena<br>e loaded with SCW<br>e Waiting Time Cou                                                                                                                                                                                | T0, SCWT1, SCWT<br>nter. The counters s                                                                                                                                                         | 2 and SCWT3 value<br>stop when it reaches                                                                                                             | es when SCWT2 is<br>the timeout value                                                                                | e.                                                                                               |

| 1          | CREP         | Character Repetition<br>Clear this bit to disable<br>character repetition in<br>Set this bit to enable<br>repetition when a pari<br>Depending upon CRE<br>up to 5times (4 repetit<br>is enabled, the SCPI<br>Alternately, the transr<br>(depending on CREP<br>register. If parity intern<br><b>Note</b> : Character repe<br>oriented protocol) | le parity error detec<br>n transmit mode.<br>parity error indicatio<br>ity error is indicated<br>EPSET bit is SCSR<br>tions) after which it<br>bit in SCIIR register<br>nitter will detect ICC<br>SEL bit in SCSR re<br>rupt is enabled, the | on on the Card I/O p<br>I in transmit mode.<br>register, the receive<br>will raise the parity of<br>r will be set too.<br>C character repetitio<br>gister), the transmit<br>SCPI bit in SCIIR r | oin in receive mode a<br>er can indicate parity<br>error bit SCPE bit in<br>on request. After 3 o<br>ter will raise the par<br>egister will be set to | and to set automat<br>/ error up to 4time:<br>the SCISR register<br>r 4 unsuccessful re-<br>ity error bit SCPE<br>0. | tic character<br>s (3 repetitions) of<br>r. If parity interrup<br>epetitions<br>bit in the SCISR |

| 0          | CONV         | ISO Convention<br>Clear this bit to use th<br>on the Card I/O pin re<br>Set this bit to use the<br>the Card I/O pin repres                                                                                                                                                                                                                     | presents a'0'.                                                                                                                                                                                                                               | × ,                                                                                                                                                                                             |                                                                                                                                                       |                                                                                                                      |                                                                                                  |

Reset Value = 0000 0000b

Figure 46. Card Vcc = 3V Initialization Procedure

advised to decrement the BOOST[1:0] bits to restore the overflow current to its normal or desired value.

## Monitoring ProcedureOnce the DC/DC has been successfuly initialized, it is necessary to monitor the DC/DC<br/>converter by means of bits VCARDOK and ICARDOVF in the SCISR register.

| VCARDOK | ICARDOVF | DC/DC Status                                                                                                                                                                                                                                                                                                   |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | 0        | - Not Started or switched off by application.<br>The current overflow sensor is disabled during the DC/DC converter startup. Then if a current<br>overflow condition is applied during the DC/DC converter startup, the DC/DC converter is unable<br>to start and both bits VCARDOK and ICARDOVF remains at 0. |

|         |          | DC/DC converter correctly started then the output voltage is out of ISO/IEC 7816-3 specifications. In this case the firmware must take appropriate actions like deactivating the DC/DC converter in compliance with ISO/IEC 7816.                                                                              |

| 0       | 1        | Started and automatically switched off by a current overflow condition                                                                                                                                                                                                                                         |

| 1       | 0        | Operating properly according to ISO/IEC 7816-3 and EMV recommendations                                                                                                                                                                                                                                         |

| 1       | 1        | Not applicable                                                                                                                                                                                                                                                                                                 |

#### Table 60. DC/DC converter status

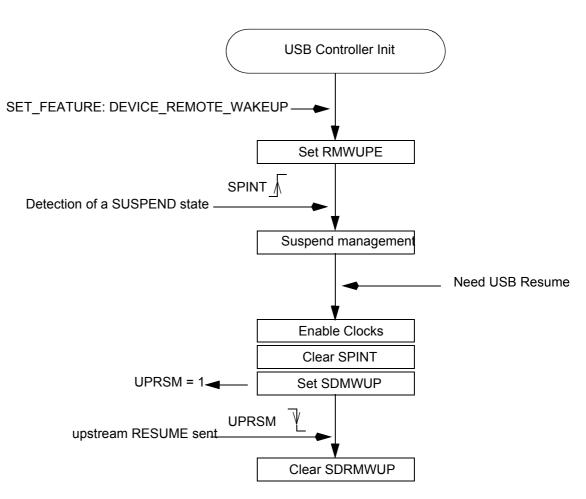

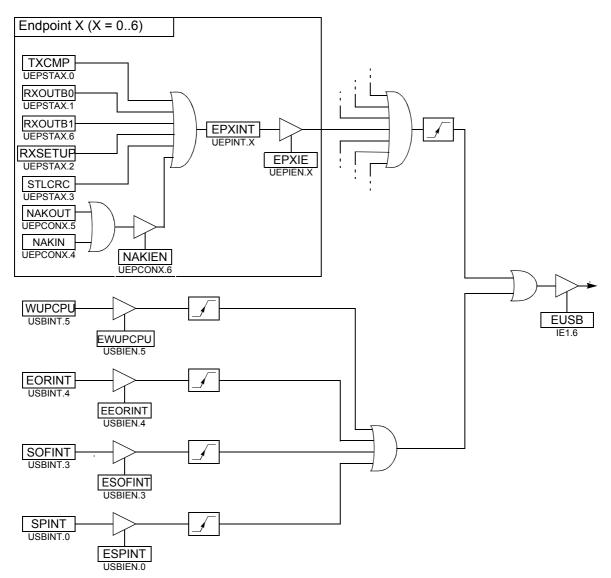

Figure 59. Example of REMOTE WAKEUP Management

Figure 63. USB Interrupt Control Block Diagram

| 7          | 6               | 5                         | 4                                                                                                                                 | 3                                           | 2 | 1               | 0   |  |  |  |  |

|------------|-----------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---|-----------------|-----|--|--|--|--|

| -          | -               | EWUPCPU                   | WUPCPU EEORINT ESOFINT ESPIN                                                                                                      |                                             |   |                 |     |  |  |  |  |

| Bit Number | Bit<br>Mnemonic | Description               | Description                                                                                                                       |                                             |   |                 |     |  |  |  |  |

| 7 - 6      | -               | Reserved<br>The value rea | eserved<br>he value read from these bits is always 0. Do not change these bits.                                                   |                                             |   |                 |     |  |  |  |  |

| 5          | EWUPCPU         | Set this bit to           | Enable Wake-up CPU Interrupt<br>Set this bit to enable Wake-up CPU Interrupt.<br>Clear this bit to disable Wake-up CPU Interrupt. |                                             |   |                 |     |  |  |  |  |

| 4          | EEORINT         | Set this bit to           |                                                                                                                                   | errupt<br>of Reset Intern<br>d of Reset Int |   | s set after res | et. |  |  |  |  |

| 3          | ESOFINT         |                           | Interrupt<br>enable SOF<br>to disable SC                                                                                          | •                                           |   |                 |     |  |  |  |  |

| 2-1        | -               | Reserved<br>The value rea | Reserved<br>The value read from these bits is always 0. Do not change these bits.                                                 |                                             |   |                 |     |  |  |  |  |

| 0          | ESPINT          | Set this bit to           | •                                                                                                                                 | ot<br>end Interrupts<br>spend Interru       | • | 5 on page 11    | 6). |  |  |  |  |

#### Table 66. USB Global Interrupt Enable Register - USBIEN (S:BEh)

Reset Value = 0001 0000b

#### Table 67. USB Address Register - USBADDR (S:C6h)

| 7             | 6               | 5                                                                                                                                                                                                          | 4                                                                                                                        | 3     | 2     | 1     | 0     |  |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|--|

| FEN           | UADD6           | UADD5                                                                                                                                                                                                      | UADD4                                                                                                                    | UADD3 | UADD2 | UADD1 | UADD0 |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                | Description                                                                                                              |       |       |       |       |  |

| 7             | FEN             | Set this bit to                                                                                                                                                                                            | Function Enable<br>Set this bit to enable the function. FADD is reset to 1.<br>Cleared this bit to disable the function. |       |       |       |       |  |

| 6-0           | UADD[6:0]       | <b>USB Address</b><br>This field contains the default address (0) after power-up or USB bus reset.<br>It should be written with the value set by a SET_ADDRESS request received by<br>the device firmware. |                                                                                                                          |       |       |       |       |  |

Reset Value = 1000 0000b

#### Table 68. USB Endpoint Number - UEPNUM (S:C7h)

| 7          | 6            | 5                                         | 4                                                                                                                                                                                                                                                                                                     | 3      | 2      | 1      | 0      |  |

|------------|--------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|--|

|            |              | -                                         | -                                                                                                                                                                                                                                                                                                     | EPNUM3 | EPNUM2 | EPNUM1 | EPNUM0 |  |

| Bit Number | Bit Mnemonic | Description                               |                                                                                                                                                                                                                                                                                                       |        |        |        |        |  |

| 7 - 4      | -            | Reserved<br>The value read fro            | Reserved<br>The value read from these bits is always 0. Do not change these bits.                                                                                                                                                                                                                     |        |        |        |        |  |

| 3 - 0      | EPNUM[3:0]   | Set this field with t<br>Count Register X | Endpoint Number<br>Set this field with the number of the endpoint which should be accessed when reading or writing to, USB Byte<br>Count Register X (X=EPNUM set in UEPNUM Register) - UBYCTX (S:E2h) or USB Endpoint X Control Register<br>UEPCONX (S:D4h). This value can be 0, 1, 2, 3, 4, 5 or 6. |        |        |        |        |  |

Reset Value = 0000 0000b

#### Table 69. USB Endpoint X Control Register - UEPCONX (S:D4h)

| 7          | 6            | 5                                                                                                          | 4                                                                                                                                                                                                                                                        | 3                                                                     | 2                    | 1                     | 0                  |

|------------|--------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------|-----------------------|--------------------|

| EPEN       | NAKIEN       | NAKOUT                                                                                                     | NAKIN                                                                                                                                                                                                                                                    | DTGL                                                                  | EPDIR                | EPTYPE1               | EPTYPE0            |

| Bit Number | Bit Mnemonic | Description                                                                                                |                                                                                                                                                                                                                                                          |                                                                       |                      |                       |                    |

| 7          | EPEN         | a hardware or l                                                                                            | able the endpoint JSB bus reset and                                                                                                                                                                                                                      | according to the dev<br>participate in the de<br>int according to the | evice configuration. |                       | s be enabled after |

| 6          | NAKIEN       |                                                                                                            | hable NAKIN and I                                                                                                                                                                                                                                        | NAKOUT Interrupt.<br>d NAKOUT Interrup                                | t.                   |                       |                    |

| 5          | NAKOUT       | the Host. This g                                                                                           | y hardware when t                                                                                                                                                                                                                                        | he a NAK handshak<br>upt if the NAKIEN b<br>are.                      |                      | B controller to an C  | OUT request from   |

| 4          | NAKIN        | Host. This gene                                                                                            | •                                                                                                                                                                                                                                                        | he a NAK handshak<br>if the NAKIEN bit is<br>are.                     |                      | B controller to an IN | I request from the |

| 3          | DTGL         |                                                                                                            | y hardware when a                                                                                                                                                                                                                                        | a valid DATA0 packe<br>nen a valid DATA1 p                            |                      | •                     |                    |

| 2          | EPDIR        | Set this bit to co<br>Clear this bit to                                                                    | Endpoint Direction<br>Set this bit to configure IN direction for Bulk, Interrupt and Isochronous endpoints.<br>Clear this bit to configure OUT direction for Bulk, Interrupt and Isochronous endpoints.<br>This bit has no effect for Control endpoints. |                                                                       |                      |                       |                    |

| 1-0        | EPTYPE[1:0]  | Endpoint Type<br>Set this field ac<br>00Control endp<br>01Isochronous<br>10Bulk endpoin<br>11Interrupt end | cording to the end<br>oint<br>endpoint<br>t                                                                                                                                                                                                              | point configuration (                                                 | Endpoint 0 will alwa | ays be configured a   | s control):        |

Reset Value = 1000 0000b when UEPNUM = 0 Reset Value = 0000 0000b otherwise

|                                  | Figure 66. UART Timings in Mode                                                                                                                                                                | ·                                                                                             |                                                                                |  |  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|

|                                  |                                                                                                                                                                                                |                                                                                               |                                                                                |  |  |

|                                  | <sup>I</sup> Start <sup>I</sup><br>bit                                                                                                                                                         | Data byte                                                                                     | Ninth <sup>I</sup> Stop <sup>I</sup><br>bit bit                                |  |  |

|                                  | RI<br>SMOD0=0                                                                                                                                                                                  |                                                                                               |                                                                                |  |  |

|                                  | RI<br>SMOD0=1                                                                                                                                                                                  |                                                                                               |                                                                                |  |  |

|                                  | FE<br>SMOD0=1                                                                                                                                                                                  |                                                                                               |                                                                                |  |  |

| Automatic Address<br>Recognition | The automatic address recognition nication feature is enabled (SM2 bi                                                                                                                          |                                                                                               | e multiprocessor commu-                                                        |  |  |

|                                  | Implemented in hardware, automatic<br>communication feature by allowin<br>incoming command frame. Only w<br>receiver sets RI bit in SCON register<br>is not interrupted by command fram        | ng the serial port to exami<br>when the serial port recognizer<br>to generate an interrupt. T | ne the address of each<br>zes its own address, the<br>his ensures that the CPU |  |  |

|                                  | If desired, you may enable the auto<br>configuration, the stop bit takes the<br>received command frame address<br>valid stop bit.<br>To support automatic address reco<br>a broadcast address. | place of the ninth data bit. E matches the device's addres                                    | Bit RI is set only when the<br>ss and is terminated by a                       |  |  |

|                                  |                                                                                                                                                                                                | cation and automatic address<br>ting SM2 bit in SCON register i                               |                                                                                |  |  |

| Given Address                    | Each device has an individual addured<br>register is a mask byte that conta<br>device's given address. The don't conta<br>slaves at a time. The following examples                             | ains don't care bits (define<br>are bits provide the flexibilit                               | ed by zeros) to form the<br>y to address one or more                           |  |  |

|                                  | To address a device by its individ 1111b.                                                                                                                                                      | ual address, the SADEN m                                                                      | nask byte must be 1111                                                         |  |  |

|                                  | For example:<br>SADDR0101 0110b<br><u>SADEN1111 1100b</u><br>Given0101 01XXb                                                                                                                   |                                                                                               |                                                                                |  |  |

|                                  | The following is an example of how<br>Slave A:SADDR1111 0001b<br><u>SADEN1111 1010b</u><br>Given1111 0X0Xb                                                                                     | v to use given addresses to a                                                                 | address different slaves:                                                      |  |  |

|                                  | Slave B:SADDR1111 0011b<br><u>SADEN1111 1001b</u><br>Given1111 0XX1b                                                                                                                           |                                                                                               |                                                                                |  |  |

|                                  | Slave C:SADDR1111 0011b<br><u>SADEN1111 1101b</u><br>Given1111 00X1b                                                                                                                           |                                                                                               |                                                                                |  |  |

|                                  |                                                                                                                                                                                                |                                                                                               |                                                                                |  |  |

| Slave Select (SS) | Each Slave peripheral is selected by one Slave Select pin ( $\overline{SS}$ ). This signal must stay<br>low for any message for a Slave. Only one Master ( $\overline{SS}$ high level) can drive the network.<br>The Master may select each Slave device by software through port pins (Figure 82). To<br>prevent bus conflicts on the MISO line, only one slave should be selected at a time by<br>the Master for a transmission. |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | In a Master configuration, the $\overline{\text{SS}}$ line can be used in conjunction with the MODF flag in the SPI Status register (SPSTA) to prevent multiple masters from driving MOSI and SCK (see Section "Error Conditions", page 140).                                                                                                                                                                                      |

|                   | A high level on the $\overline{\text{SS}}$ pin puts the MISO line of a Slave SPI in a high-impedance state.                                                                                                                                                                                                                                                                                                                        |

|                   | The $\overline{SS}$ pin could be used as a general-purpose if the following conditions are met:                                                                                                                                                                                                                                                                                                                                    |

|                   | <ul> <li>The device is configured as a Master and the SSDIS control bit in SPCON is set.<br/>This kind of configuration can be found when only one Master is driving the network<br/>and there is no way that the SS pin will be pulled low. Therefore, the MODF flag in<br/>the SPSTA will never be set<sup>(1)</sup>.</li> </ul>                                                                                                 |

|                   | <ul> <li>The Device is configured as a Slave with CPHA and SSDIS control bits set <sup>(2)</sup>. This kind of configuration can happen when the system comprises one Master and one Slave only. Therefore, the device should always be selected and there is no reason that the Master uses the SS pin to select the communicating Slave device.</li> </ul>                                                                       |

| Baud Rate         | In Master mode, the baud rate can be selected from a baud rate generator which is con-<br>troled by three bits in the SPCON register: SPR2, SPR1 and SPR0. The Master clock is                                                                                                                                                                                                                                                     |

troled by three bits in the SPCON register: SPR2, SPR1 and SPR0. The Master clock is chosen from one of six clock rates resulting from the division of the internal clock by 4, 8, 16, 32, 64 or 128.

Table 83 gives the different clock rates selected by SPR2:SPR1:SPR0

| SPR2:SPR1:SPR0 | Clock Rate               | Baud Rate Divisor (BD) |

|----------------|--------------------------|------------------------|

| 000            | Reserved                 | N/A                    |

| 001            | F <sub>CK_SPI</sub> /4   | 4                      |

| 010            | F <sub>CK_SPI</sub> / 8  | 8                      |

| 011            | F <sub>CK_SPI</sub> /16  | 16                     |

| 100            | F <sub>CK_SPI</sub> /32  | 32                     |

| 101            | F <sub>CK_SPI</sub> /64  | 64                     |

| 110            | F <sub>CK_SPI</sub> /128 | 128                    |

| 111            | Reserved                 | N/A                    |

#### Table 83. SPI Master Baud Rate Selection

- 1. Clearing SSDIS control bit does not clear MODF.

- 2. Special care should be taken not to set SSDIS control bit when CPHA = '0' because in this mode, the  $\overline{SS}$  is used to start the transmission.

## Interrupt Sources and Vectors

#### Table 108. Interrupt Vectors

| Interrupt Source                   | Polling Priority<br>at Same Level | Vector<br>Address |  |

|------------------------------------|-----------------------------------|-------------------|--|

| Reset                              | 0<br>(Highest Priority)           | C:0000h           |  |

| INTO                               | 1                                 | C:0003h           |  |

| Timer 0                            | 2                                 | C:000Bh           |  |

| INT1                               | 3                                 | C:0013h           |  |

| Timer 1                            | 4                                 | C:001Bh           |  |

| UART                               | 6                                 | C:0023h           |  |

| Reserved                           | 7                                 | C:002Bh           |  |

| Reserved                           | 5                                 | C:0033h           |  |

| Keyboard Controller <sup>(1)</sup> | 8                                 | C:003Bh           |  |

| Reserved                           | 9                                 | C:0043h           |  |

| SPI Controller <sup>(1)</sup>      | 10                                | C:004Bh           |  |

| Smart Card Controller              | 11                                | C:0053h           |  |

| Reserved                           | 12                                | C:005Bh           |  |

| Reserved                           | 13                                | C:0063h           |  |

| USB Controller                     | 14                                | C:006Bh           |  |

| Reserved                           | 15<br>(Lowest Priority)           | C:0073h           |  |

Note: 1. Only fot AT8xC5122

### **Reset pin**

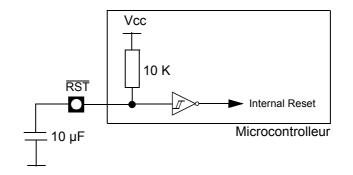

As explained in the POR section there is no need to use the reset pin as the internal reset function at power up is ensured by the POR. Anyway, if some applications requires a long reset, a reset controlled by the user or a reset controlled by external superviser device, the use of the reset pin is necessary.

**Long Reset** As the pad integrates an internal pull-up of 10K, only an external capacitor of at least 10  $\mu$ F is required to have an impact on the reset duration.

Figure 103. Long Reset

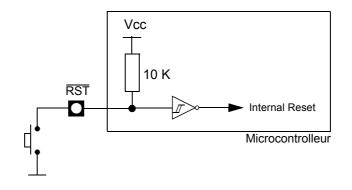

**Reset Controlled by the User** The external capacitor is not needed if no long reset is required.

Figure 104. Reset Controlled by the User

## **Electrical Characteristics**

## **Absolute Maximum Ratings**

| Ambiant Temperature Under Bias25°C to 85°C                        |

|-------------------------------------------------------------------|

| Storage Temperature65°C to + 150°C                                |

| Voltage on V <sub>CC</sub> to V <sub>SS</sub> 0.5 V to + 6.0V     |

| Voltage on Any Pin to $V_{\rm SS}$ -0.5 V to $V_{\rm CC}$ + 0.5 V |

| Power Dissipation 1 W                                             |

Note: Stresses at or above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

Power Dissipation value is based on the maximum allowable die temperature and the thermal resistance of the package.

## **DC Parameters**

| Symbol                               | Parameter                                                                          | Min                       | Тур | Max                       | Unit   | Test Conditions                                         |

|--------------------------------------|------------------------------------------------------------------------------------|---------------------------|-----|---------------------------|--------|---------------------------------------------------------|

| V <sub>IL</sub>                      | Input Low Voltage                                                                  | -0.5                      |     | 0.2 V <sub>CC</sub> - 0.1 | V      |                                                         |

| V <sub>IH</sub>                      | Input High Voltage except XTAL1, RST                                               | 0.2 V <sub>CC</sub> + 0.9 |     | V <sub>CC</sub> + 0.5     | V      |                                                         |

| V <sub>IH1</sub>                     | Input High Voltage, XTAL1, RST                                                     | 0.7 V <sub>CC</sub>       |     | V <sub>CC</sub> + 0.5     | V      |                                                         |

| V <sub>OL</sub>                      | Output Low Voltage: P0, ALE, PSEN                                                  |                           |     | 0.45                      | V      | I <sub>OL</sub> = 1.6 mA                                |

| V <sub>OH</sub>                      | Output High Voltage: P0, ALE, PSEN                                                 | 0.9 V <sub>CC</sub>       |     |                           | V      | I <sub>OH</sub> = 10 μA                                 |

| V <sub>OL1</sub>                     | Output Low Voltage: P2, P3, P4, P5, P1.2, P1.6, P1.7                               |                           |     | 0.45                      | V      | I <sub>OL</sub> = 0.8 mA                                |

| V <sub>OH1</sub>                     | Output High Voltage: P2, P3, P4, P5, P1.2, P1.6, P1.7                              | 0.9 V <sub>CC</sub>       |     |                           | V      | Ι <sub>ΟΗ</sub> = -10 μΑ                                |

| l <sub>IL</sub>                      | Logical 0 Input Current ports 2 to 5 and P1.2, P1.6, P1.7, if Weak pull-up enabled |                           |     | -50                       | μA     | Vin = 0.45 V                                            |

| LI                                   | Input Leakage Current                                                              |                           |     | ±10                       | μA     | 0.45 V < V <sub>IN</sub> < V <sub>CC</sub>              |

| I <sub>TL</sub>                      | Logical 1 to O transistion Current, Port 51 configuration                          |                           |     | -650                      | μA     | V <sub>IN</sub> = 2 V                                   |

| R <sub>MEDIUM</sub>                  | Medium Pullup Resistor                                                             |                           | 10  |                           | kΩ     |                                                         |