Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                       |

|--------------------------------|------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 3000                                                                         |

| Number of Logic Elements/Cells | 12000                                                                        |

| Total RAM Bits                 | 589824                                                                       |

| Number of I/O                  | 197                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.045V ~ 1.155V                                                              |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                              |

| Package / Case                 | 256-LFBGA                                                                    |

| Supplier Device Package        | 256-CABGA (14x14)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe5u-12f-6bg256c |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Tables

| Table 1.1. ECP5 and ECP5-5G Family Selection Guide                                                                        | 11 |

|---------------------------------------------------------------------------------------------------------------------------|----|

| Table 2.1. Resources and Modes Available per Slice                                                                        | 14 |

| Table 2.2. Slice Signal Descriptions                                                                                      |    |

| Table 2.3. Number of Slices Required to Implement Distributed RAM                                                         |    |

| Table 2.4. PLL Blocks Signal Descriptions                                                                                 |    |

| Table 2.5. DDRDLL Ports List                                                                                              |    |

| Table 2.6. sysMEM Block Configurations                                                                                    |    |

| Table 2.7. Maximum Number of Elements in a Slice                                                                          |    |

| Table 2.8. Input Block Port Description                                                                                   |    |

| Table 2.9. Output Block Port Description                                                                                  |    |

| Table 2.10. Tristate Block Port Description                                                                               |    |

| Table 2.11. DQSBUF Port List Description                                                                                  |    |

| Table 2.12. On-Chip Termination Options for Input Modes                                                                   |    |

| Table 2.13. LFE5UM/LFE5UM5G SERDES Standard Support                                                                       |    |

| Table 2.14. Available SERDES Duals per LFE5UM/LFE5UM5G Devices                                                            |    |

| Table 2.15. LFE5UM/LFE5UM5G Mixed Protocol Support                                                                        |    |

| Table 2.16. Selectable Master Clock (MCLK) Frequencies during Configuration (Nominal)                                     |    |

| Table 3.1. Absolute Maximum Ratings                                                                                       |    |

| Table 3.2. Recommended Operating Conditions                                                                               |    |

| Table 3.3. Power Supply Ramp Rates                                                                                        |    |

| Table 3.4. Power-On-Reset Voltage Levels                                                                                  |    |

| Table 3.5. Hot Socketing Specifications                                                                                   |    |

| Table 3.6. Hot Socketing Requirements                                                                                     |    |

| Table 3.7. DC Electrical Characteristics                                                                                  |    |

| Table 3.8. ECP5/ECP5-5G Supply Current (Standby)                                                                          |    |

| Table 3.9. ECP5UM                                                                                                         |    |

| Table 3.10. ECP5-5G                                                                                                       |    |

| Table 3.11. sysI/O Recommended Operating Conditions                                                                       |    |

| Table 3.12. Single-Ended DC Characteristics                                                                               |    |

| Table 3.13. LVDS                                                                                                          |    |

| Table 3.14. LVDS25E DC Conditions                                                                                         |    |

| Table 3.15. BLVDS25 DC Conditions                                                                                         |    |

| Table 3.16. LVPECL33 DC Conditions                                                                                        |    |

| Table 3.17. MLVDS25 DC Conditions                                                                                         |    |

| Table 3.18. Input to SLVS                                                                                                 |    |

| Table 3.19. Pin-to-Pin Performance                                                                                        |    |

| Table 3.20. Register-to-Register Performance                                                                              |    |

| Table 3.21. ECP5/ECP5-5G Maximum I/O Buffer Speed                                                                         |    |

| Table 3.22. ECP5/ECP5-5G External Switching Characteristics                                                               |    |

| Table 3.23. sysCLOCK PLL Timing                                                                                           |    |

| Table 3.24. Serial Output Timing and Levels                                                                               |    |

| Table 3.25. Channel Output Jitter                                                                                         |    |

| Table 3.26. SERDES/PCS Latency Breakdown                                                                                  |    |

| Table 3.27. Serial Input Data Specifications   Table 3.28. Passiver Table littler Talerance Specification                 |    |

| Table 3.28. Receiver Total Jitter Tolerance Specification   Table 3.20. External Reference Clock Specification (refeller) |    |

| Table 3.29. External Reference Clock Specification (refclkp/refclkn)   Table 3.20. PCIe (2.5. Ch/c)                       |    |

| Table 3.30. PCIe (2.5 Gb/s)                                                                                               |    |

| Table 3.31. PCIe (5 Gb/s)<br>Table 3.32. CPRI LV2 E.48 Electrical and Timing Characteristics                              |    |

| Table 3.32. CPRI LV2 E.48 Electrical and Timing Characteristics                                                           |    |

| Table 3.33. Transmit                                                                                                      |    |

| Table 3.35. Transmit                                                                                                      |    |

|                                                                                                                           | 80 |

# 1. General Description

The ECP5/ECP5-5G family of FPGA devices is optimized to deliver high performance features such as an enhanced DSP architecture, high speed SERDES (Serializer/Deserializer), and high speed source synchronous interfaces, in an economical FPGA fabric. This combination is achieved through advances in device architecture and the use of 40 nm technology making the devices suitable for high-volume, highspeed, and low-cost applications.

The ECP5/ECP5-5G device family covers look-up-table (LUT) capacity to 84K logic elements and supports up to 365 user I/Os. The ECP5/ECP5-5G device family also offers up to 156 18 x 18 multipliers and a wide range of parallel I/O standards.

The ECP5/ECP5-5G FPGA fabric is optimized high performance with low power and low cost in mind. The ECP5/ ECP5-5G devices utilize reconfigurable SRAM logic technology and provide popular building blocks such as LUT-based logic, distributed and embedded memory, Phase-Locked Loops (PLLs), Delay-Locked Loops (DLLs), pre-engineered source synchronous I/O support, enhanced sysDSP slices and advanced configuration support, including encryption and dual-boot capabilities.

The pre-engineered source synchronous logic implemented in the ECP5/ECP5-5G device family supports a broad range of interface standards including DDR2/3, LPDDR2/3, XGMII, and 7:1 LVDS.

The ECP5/ECP5-5G device family also features high speed SERDES with dedicated Physical Coding Sublayer (PCS) functions. High jitter tolerance and low transmit jitter allow the SERDES plus PCS blocks to be configured to support an array of popular data protocols including PCI Express, Ethernet (XAUI, GbE, and SGMII) and CPRI. Transmit De-emphasis with pre- and post-cursors, and Receive Equalization settings make the SERDES suitable for transmission and reception over various forms of media.

The ECP5/ECP5-5G devices also provide flexible, reliable and secure configuration options, such as dual-boot capability, bit-stream encryption, and TransFR field upgrade features.

ECP5-5G family devices have made some enhancement in the SERDES compared to ECP5UM devices. These enhancements increase the performance of the SERDES to up to 5 Gb/s data rate.

The ECP5-5G family devices are pin-to-pin compatible with the ECP5UM devices. These allows a migration path for users to port designs from ECP5UM to ECP5-5G devices to get higher performance. The Lattice Diamond<sup>™</sup> design software allows large complex designs to be efficiently implemented using the ECP5/ECP5-5G FPGA family. Synthesis library support for ECP5/ECP5-5G devices is available for popular logic synthesis tools. The Diamond tools use the synthesis tool output along with the constraints from its floor planning tools to place and route the design in the ECP5/ECP5-5G device. The tools extract the timing from the routing and back-annotate it into the design for timing verification.

Lattice provides many pre-engineered IP (Intellectual Property) modules for the ECP5/ECP5-5G family. By using these configurable soft core IPs as standardized blocks, designers are free to concentrate on the unique aspects of their design, increasing their productivity.

# 1.1. Features

- Higher Logic Density for Increased System Integration

- 12K to 84K LUTs

- 197 to 365 user programmable I/Os

- Embedded SERDES

- 270 Mb/s, up to 3.2 Gb/s, SERDES interface (ECP5)

- 270 Mb/s, up to 5.0 Gb/s, SERDES interface (ECP5-5G)

- Supports eDP in RDR (1.62 Gb/s) and HDR (2.7 Gb/s)

- Up to four channels per device: PCI Express, Ethernet (1GbE, SGMII, XAUI), and CPRI

- sysDSP™

- Fully cascadable slice architecture

- 12 to 160 slices for high performance multiply and accumulate

- Powerful 54-bit ALU operations

- Time Division Multiplexing MAC Sharing

- Rounding and truncation

- Each slice supports

- Half 36 x 36, two 18 x 18 or four 9 x 9 multipliers

- Advanced 18 x 36 MAC and 18 x 18 Multiply-Multiply-Accumulate (MMAC) operations

- Flexible Memory Resources

- Up to 3.744 Mb sysMEM<sup>™</sup> Embedded Block RAM (EBR)

- 194K to 669K bits distributed RAM

- sysCLOCK Analog PLLs and DLLs

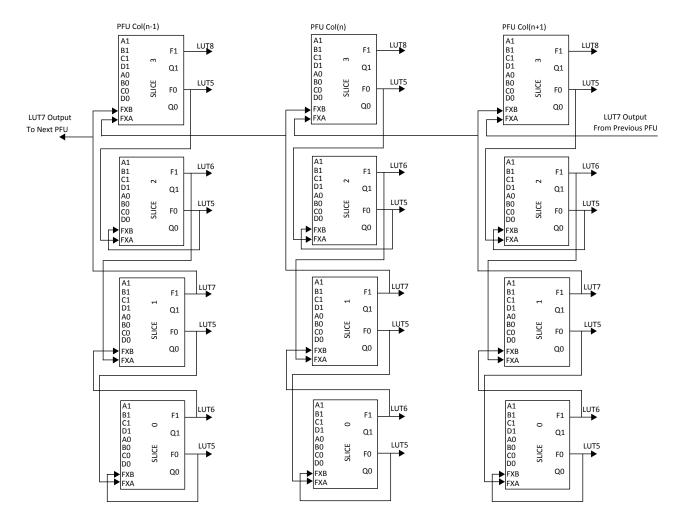

| Figure 2.4. Connectivity Supporting LUT5, LUT6, LUT | 7, and LUT8 |

|-----------------------------------------------------|-------------|

|-----------------------------------------------------|-------------|

| Table | 2.2. | Slice | Signal | Descriptions |

|-------|------|-------|--------|--------------|

|-------|------|-------|--------|--------------|

| Function | Туре               | Signal Names   | Description                                                      |

|----------|--------------------|----------------|------------------------------------------------------------------|

| Input    | Data signal        | A0, B0, C0, D0 | Inputs to LUT4                                                   |

| Input    | Data signal        | A1, B1, C1, D1 | Inputs to LUT4                                                   |

| Input    | Multi-purpose      | M0             | Multipurpose Input                                               |

| Input    | Multi-purpose      | M1             | Multipurpose Input                                               |

| Input    | Control signal     | CE             | Clock Enable                                                     |

| Input    | Control signal     | LSR            | Local Set/Reset                                                  |

| Input    | Control signal     | CLK            | System Clock                                                     |

| Input    | Inter-PFU signal   | FCI            | Fast Carry-in <sup>1</sup>                                       |

| Input    | Inter-slice signal | FXA            | Intermediate signal to generate LUT6, LUT7 and LUT8 <sup>2</sup> |

| Input    | Inter-slice signal | FXB            | Intermediate signal to generate LUT6, LUT7 and LUT8 <sup>2</sup> |

| Output   | Data signals       | F0, F1         | LUT4 output register bypass signals                              |

| Output   | Data signals       | Q0, Q1         | Register outputs                                                 |

| Output   | Inter-PFU signal   | FCO            | Fast carry chain output <sup>1</sup>                             |

Notes:

2. Requires two adjacent PFUs.

<sup>1.</sup> See Figure 2.3 on page 15 for connection details.

## Table 2.6. sysMEM Block Configurations

| Memory Mode      | Configurations     16,384 x 1     8,192 x 2     4,096 x 4     2,048 x 9     1,024 x 18     512 x 36     16,384 x 1     8,192 x 2     4,096 x 4     2,048 x 9     16,384 x 1     8,192 x 2     4,096 x 4     2,048 x 9     1,024 x 18     16,384 x 1     8,192 x 2     4,096 x 4     2,048 x 9     16,384 x 1     8,192 x 2     4,096 x 4     2,048 x 9 |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                  | 16,384 x 1                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                  | 8,192 x 2                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Single Port      | 4,096 x 4                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Single Port      | 2,048 x 9                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                  | 1,024 x 18                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                  | 512 x 36                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|                  | 16,384 x 1                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                  | 8,192 x 2                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| True Dual Port   | 4,096 x 4                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                  | 2,048 x 9                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                  | 1,024 x 18                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                  | 16,384 x 1                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                  | 8,192 x 2                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Decude Duel Dert | 4,096 x 4                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Pseudo Dual Port | 2,048 x 9                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                  | 1,024 x 18                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                  | 512 x 36                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

## 2.8.2. Bus Size Matching

All of the multi-port memory modes support different widths on each of the ports. The RAM bits are mapped LSB word 0 to MSB word 0, LSB word 1 to MSB word 1, and so on. Although the word size and number of words for each port varies, this mapping scheme applies to each port.

## 2.8.3. RAM Initialization and ROM Operation

If desired, the contents of the RAM can be pre-loaded during device configuration. By preloading the RAM block during the chip configuration cycle and disabling the write controls, the sysMEM block can also be utilized as a ROM.

## 2.8.4. Memory Cascading

Larger and deeper blocks of RAM can be created using EBR sysMEM Blocks. Typically, the Lattice design tools cascade memory transparently, based on specific design inputs.

# 2.8.5. Single, Dual and Pseudo-Dual Port Modes

In all the sysMEM RAM modes the input data and address for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the output.

EBR memory supports the following forms of write behavior for single port or dual port operation:

- **Normal** Data on the output appears only during a read cycle. During a write cycle, the data (at the current address) does not appear on the output. This mode is supported for all data widths.

- Write Through A copy of the input data appears at the output of the same port during a write cycle. This mode is supported for all data widths.

- **Read-Before-Write** When new data is written, the old content of the address appears at the output. This mode is supported for x9, x18, and x36 data widths.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

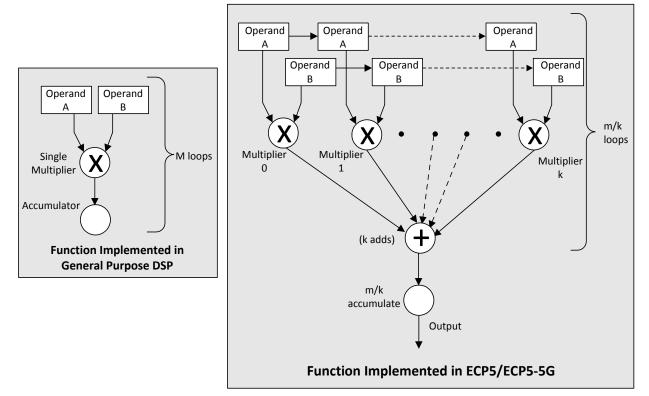

Figure 2.13. Comparison of General DSP and ECP5/ECP5-5G Approaches

# 2.9.2. sysDSP Slice Architecture Features

The ECP5/ECP5-5G sysDSP Slice has been significantly enhanced to provide functions needed for advanced processing applications. These enhancements provide improved flexibility and resource utilization.

The ECP5/ECP5-5G sysDSP Slice supports many functions that include the following:

- Symmetry support. The primary target application is wireless. 1D Symmetry is useful for many applications that use FIR filters when their coefficients have symmetry or asymmetry characteristics. The main motivation for using 1D symmetry is cost/size optimization. The expected size reduction is up to 2x.

- Odd mode Filter with Odd number of taps

- Even mode Filter with Even number of taps

- Two dimensional (2D) symmetry mode supports 2D filters for mainly video applications

- Dual-multiplier architecture. Lower accumulator overhead to half and the latency to half compared to single multiplier architecture

- Fully cascadable DSP across slices. Support for symmetric, asymmetric and non-symmetric filters.

- Multiply (one 18x36, two 18x18 or four 9x9 Multiplies per Slice)

- Multiply (36x36 by cascading across two sysDSP slices)

- Multiply Accumulate (supports one 18x36 multiplier result accumulation or two 18x18 multiplier result accumulation)

- Two Multiplies feeding one Accumulate per cycle for increased processing with lower latency (two 18x18 Multiplies feed into an accumulator that can accumulate up to 52 bits)

- Pipeline registers

- 1D Symmetry support. The coefficients of FIR filters have symmetry or negative symmetry characteristics.

- Odd mode Filter with Odd number of taps

- Even mode Filter with Even number of taps

- 2D Symmetry support. The coefficients of 2D FIR filters have symmetry or negative symmetry characteristics.

- 3\*3 and 3\*5 Internal DSP Slice support

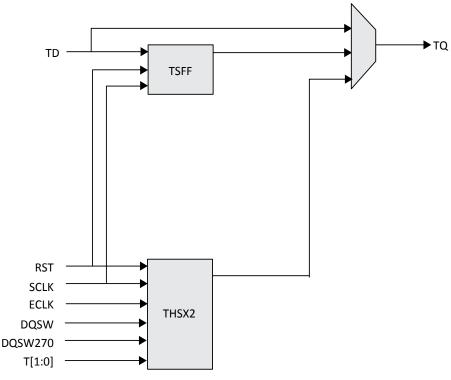

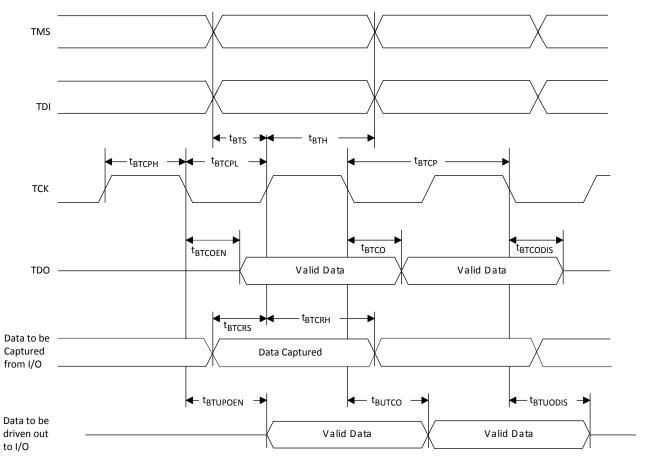

| Name    | Туре   | Description                                                         |

|---------|--------|---------------------------------------------------------------------|

| TD      | Input  | Tristate Input to Tristate SDR Register                             |

| RST     | Input  | Reset to the Tristate Block                                         |

| TD[1:0] | Input  | Tristate input to TSHX2 function                                    |

| SCLK    | Input  | Slow Speed System Clock                                             |

| ECLK    | Input  | High Speed Edge Clock                                               |

| DQSW    | Input  | Clock from DQS control Block used to generate DDR memory DQS output |

| DQSW270 | Input  | Clock from DQS control Block used to generate DDR memory DQ output  |

| TQ      | Output | Output of the Tristate block                                        |

# 2.13. DDR Memory Support

# 2.13.1. DQS Grouping for DDR Memory

Certain PICs have additional circuitry to allow the implementation of high-speed source synchronous and DDR2, DDR3, LPDDR2 or LPDDR3 memory interfaces. The support varies by the edge of the device as detailed below.

The left and right sides of the PIC have fully functional elements supporting DDR2, DDR3, LPDDR2 or LPDDR3 memory interfaces. Every 16 PIOs on the left and right sides are grouped into one DQS group, as shown in Figure 2.23 on page 36. Within each DQS group, there are two pre-placed pins for DQS and DQS# signals. The rest of the pins in the DQS group can be used as DQ signals and DM signal. The number of pins in each DQS group bonded out is package dependent. DQS groups with less than 11 pins bonded out can only be used for LPDDR2/3 Command/ Address busses. In DQS groups with more than 11 pins bonded out, up to two pre-defined pins are assigned to be used as "virtual" VCCIO, by driving these pins to HIGH, with the user connecting these pins to VCCIO power supply. These connections create "soft" connections to V<sub>CCIO</sub> thru these output pins, and make better connections on VCCIO to help to reduce SSO noise. For details, refer to ECP5 and ECP5-5G High-Speed I/O Interface (TN1265).

|            | PIO A          | sysIO Buffer | Pad A (T)      |

|------------|----------------|--------------|----------------|

| •          | PIO B          | sysIO Buffer | Pad B (C)      |

| <b>↓</b>   | PIO C          | sysIO Buffer | Pad C          |

| <b>↓</b>   | PIO D          | sysIO Buffer | Pad D          |

| <b>↓</b>   | PIO A          | sysIO Buffer | Pad A (T)      |

| <b>↓</b>   | PIO B          | sysIO Buffer | Pad B (C)      |

| <b>↓</b>   | PIO C          | sysIO Buffer | Pad C          |

| <b>↓</b>   | PIO D          | sysIO Buffer | Pad D          |

|            | DQSBUF         | <br>Delay    |                |

| <b>↓</b>   | PIO A          | sysIO Buffer | Pad A (T)      |

| <b>↓</b>   | PIO B          | sysIO Buffer | Pad B (C)      |

| <b>↓</b>   | PIO C          | sysIO Buffer | Pad C          |

| <b>↓</b>   | PIO D          | sysIO Buffer | Pad D          |

| <b>↓</b>   | PIO A          | syslO Buffer | Pad A (T)      |

| <b>↓</b>   | PIO B          | sysIO Buffer | Pad B (C)      |

|            |                |              |                |

| <b>♦</b> → | PIO C          | sysIO Buffer | Pad C          |

| •          | PIO C<br>PIO D | sysIO Buffer | Pad C<br>Pad D |

Figure 2.23. DQS Grouping on the Left and Right Edges

# 2.13.2. DLL Calibrated DQS Delay and Control Block (DQSBUF)

To support DDR memory interfaces (DDR2/3, LPDDR2/3), the DQS strobe signal from the memory must be used to capture the data (DQ) in the PIC registers during memory reads. This signal is output from the DDR memory device aligned to data transitions and must be time shifted before it can be used to capture data in the PIC. This time shifted is achieved by using DQSDEL programmable delay line in the DQS Delay Block (DQS read circuit). The DQSDEL is implemented as a slave delay line and works in conjunction with a master DDRDLL.

This block also includes slave delay line to generate delayed clocks used in the write side to generate DQ and DQS with correct phases within one DQS group. There is a third delay line inside this block used to provide write leveling feature for DDR write if needed.

Each of the read and write side delays can be dynamically shifted using margin control signals that can be controlled by the core logic.

FIFO Control Block shown in Figure 2.24 generates the Read and Write Pointers for the FIFO block inside the Input Register Block. These pointers are generated to control the DQS to ECLK domain crossing using the FIFO module.

| Package    | LFE5UM/LFE5UM5G-25 | LFE5UM/LFE5UM5G-45 | LFE5UM/LFE5UM5G-85 |  |  |

|------------|--------------------|--------------------|--------------------|--|--|

| 285 csfBGA | 1                  | 1                  | 1                  |  |  |

| 381 caBGA  | 1                  | 2                  | 2                  |  |  |

| 554 caBGA  | -                  | 2                  | 2                  |  |  |

| 756 caBGA  | -                  | -                  | 2                  |  |  |

## Table 2.14. Available SERDES Duals per LFE5UM/LFE5UM5G Devices

# 2.15.1. SERDES Block

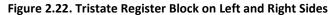

A SERDES receiver channel may receive the serial differential data stream, equalize the signal, perform Clock and Data Recovery (CDR) and de-serialize the data stream before passing the 8- or 10-bit data to the PCS logic. The SERDES transmitter channel may receive the parallel 8- or 10-bit data, serialize the data and transmit the serial bit stream through the differential drivers. Figure 2.28 shows a single-channel SERDES/PCS block. Each SERDES channel provides a recovered clock and a SERDES transmit clock to the PCS block and to the FPGA core logic.

Each transmit channel, receiver channel, and SERDES PLL shares the same power supply (VCCA). The output and input buffers of each channel have their own independent power supplies (VCCHTX and VCCHRX).

Figure 2.28. Simplified Channel Block Diagram for SERDES/PCS Block

# 2.15.2. PCS

As shown in Figure 2.28, the PCS receives the parallel digital data from the deserializer and selects the polarity, performs word alignment, decodes (8b/10b), provides Clock Tolerance Compensation and transfers the clock domain from the recovered clock to the FPGA clock via the Down Sample FIFO.

For the transmit channel, the PCS block receives the parallel data from the FPGA core, encodes it with 8b/10b, selects the polarity and passes the 8/10 bit data to the transmit SERDES channel.

The PCS also provides bypass modes that allow a direct 8-bit or 10-bit interface from the SERDES to the FPGA logic. The PCS interface to the FPGA can also be programmed to run at 1/2 speed for a 16-bit or 20-bit interface to the FPGA logic. Some of the enhancements in LFE5UM/LFE5UM5G SERDES/PCS include:

- Higher clock/channel granularity: Dual channel architecture provides more clock resource per channel.

- Enhanced Tx de-emphasis: Programmable pre- and post-cursors improves Tx output signaling

- Bit-slip function in PCS: Improves logic needed to perform Word Alignment function

Refer to ECP5 and ECP5-5G SERDES/PCS Usage Guide (TN1261) for more information.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

| Demonstern                                                                                                                              | Description                            | Device        | -8        |            | -7   |       | -6   |       | 11   |

|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------|-----------|------------|------|-------|------|-------|------|

| Parameter                                                                                                                               | rameter Description                    |               | Min       | Max        | Min  | Max   | Min  | Max   | Unit |

| f <sub>data_ddr2</sub><br>f <sub>data_ddr3</sub><br>f <sub>data_ddr3</sub><br>f <sub>data_lpddr2</sub><br>f <sub>data_lpddr3</sub>      | DDR Memory Data Rate                   | All Devices   | Ι         | 800        | _    | 700   | _    | 624   | Mb/s |

| fmax_ddr2<br>fmax_ddr3<br>fmax_ddr3l<br>fmax_lpddr2<br>fmax_lpddr3                                                                      | DDR Memory CLK<br>Frequency (ECLK)     | All Devices   | Ι         | 400        | _    | 350   | _    | 312   | MHz  |

| DDR2/DDR3/DDR                                                                                                                           | 3L/LPDDR2/LPDDR3 WRITE (DO             | Q Output Data | are Cente | ered to DC | QS)  |       |      |       |      |

| t <sub>dqvbs_ddr2</sub><br>t <sub>dqvbs_ddr3</sub><br>t <sub>dqvbs_ddr3</sub><br>t <sub>dqvbs_lpddr2</sub><br>t <sub>dqvbs_lpddr3</sub> | Data Output Valid before<br>DQS Output | All Devices   | _         | -0.25      | _    | -0.25 | _    | -0.25 | UI   |

| tdqvas_ddr2<br>tdqvas_ddr3<br>tdqvas_ddr3l<br>tdqvas_lpddr2<br>tdqvas_lpddr2<br>tdqvas_lpddr3                                           | Data Output Valid after DQS<br>Output  | All Devices   | 0.25      | _          | 0.25 | _     | 0.25 | _     | UI   |

| fdata_ddr2<br>fdata_ddr3<br>fdata_ddr3l<br>fdata_lpddr2<br>fdata_lpddr3                                                                 | DDR Memory Data Rate                   | All Devices   | _         | 800        | _    | 700   | _    | 624   | Mb/s |

| f <sub>MAX_DDR2</sub><br>f <sub>MAX_DDR3</sub><br>f <sub>MAX_DDR3L</sub><br>f <sub>MAX_LPDDR2</sub><br>f <sub>MAX_LPDDR3</sub>          | DDR Memory CLK<br>Frequency (ECLK)     | All Devices   | _         | 400        | _    | 350   | _    | 312   | MHz  |

Notes:

1. Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from the Diamond software.

General I/O timing numbers are based on LVCMOS 2.5, 12 mA, Fast Slew Rate, 0pf load. Generic DDR timing are numbers based on LVDS I/O. DDR2 timing numbers are based on SSTL18. DDR3 timing numbers are based on SSTL15. LPDDR2 and LPDDR3 timing numbers are based on HSUL12.

- 3. Uses LVDS I/O standard for measurements.

- 4. Maximum clock frequencies are tested under best case conditions. System performance may vary upon the user environment.

- 5. All numbers are generated with the Diamond software.

FPGA-DS-02012-1.9

# 3.19. sysCLOCK PLL Timing

Over recommended operating conditions.

| Parameter                      | Descriptions                                                         | Conditions                 | Min   | Max   | Units      |

|--------------------------------|----------------------------------------------------------------------|----------------------------|-------|-------|------------|

| f <sub>IN</sub>                | Input Clock Frequency (CLKI, CLKFB)                                  | _                          | 8     | 400   | MHz        |

| f <sub>out</sub>               | Output Clock Frequency (CLKOP, CLKOS)                                | _                          | 3.125 | 400   | MHz        |

| f <sub>vco</sub>               | PLL VCO Frequency                                                    | _                          | 400   | 800   | MHz        |

| $f_{\text{PFD}}{}^3$           | Phase Detector Input Frequency                                       | _                          | 10    | 400   | MHz        |

| AC Characteris                 | tics                                                                 |                            |       |       |            |

| t <sub>DT</sub>                | Output Clock Duty Cycle                                              | _                          | 45    | 55    | %          |

| t <sub>PH4</sub>               | Output Phase Accuracy                                                | _                          | -5    | 5     | %          |

|                                |                                                                      | f <sub>o∪τ</sub> ≥ 100 MHz | _     | 100   | ps p-p     |

|                                | Output Clock Period Jitter                                           | f <sub>оυт</sub> < 100 MHz | _     | 0.025 | UIPP       |

|                                |                                                                      | f <sub>o∪τ</sub> ≥ 100 MHz | _     | 200   | ps p-p     |

| t <sub>opjit</sub> 1           | Output Clock Cycle-to-Cycle Jitter                                   | f <sub>оυт</sub> < 100 MHz | _     | 0.050 | UIPP       |

|                                |                                                                      | f <sub>PFD</sub> ≥ 100 MHz | _     | 200   | ps p-p     |

|                                | Output Clock Phase Jitter                                            | f <sub>PFD</sub> < 100 MHz | _     | 0.011 | UIPP       |

| t <sub>spo</sub>               | Static Phase Offset                                                  | Divider ratio =<br>integer | _     | 400   | ps p-p     |

| t <sub>w</sub>                 | Output Clock Pulse Width                                             | At 90% or 10%              | 0.9   | _     | ns         |

| t <sub>LOCK</sub> <sup>2</sup> | PLL Lock-in Time                                                     | _                          | _     | 15    | ms         |

| t <sub>UNLOCK</sub>            | PLL Unlock Time                                                      | _                          | _     | 50    | ns         |

|                                |                                                                      | f <sub>PFD</sub> ≥ 20 MHz  | _     | 1,000 | ps p-p     |

| t <sub>IPJIT</sub>             | Input Clock Period Jitter                                            | f <sub>PFD</sub> < 20 MHz  | _     | 0.02  | UIPP       |

| t <sub>HI</sub>                | Input Clock High Time                                                | 90% to 90%                 | 0.5   | _     | ns         |

| t <sub>LO</sub>                | Input Clock Low Time                                                 | 10% to 10%                 | 0.5   | _     | ns         |

| t <sub>RST</sub>               | RST/ Pulse Width                                                     | _                          | 1     | _     | ms         |

| t <sub>rstrec</sub>            | RST Recovery Time                                                    | _                          | 1     | -     | ns         |

| t <sub>load_reg</sub>          | Min Pulse for CIB_LOAD_REG                                           | _                          | 10    | _     | ns         |

| t <sub>rotate-setup</sub>      | Min time for CIB dynamic phase controls to be stable fore CIB_ROTATE | _                          | 5     | -     | ns         |

| t <sub>rotate-wd</sub>         | Min pulse width for CIB_ROTATE to maintain "0" or                    | _                          | 4     | -     | VCO cycles |

Notes:

1. Jitter sample is taken over 10,000 samples for Periodic jitter, and 2,000 samples for Cycle-to-Cycle jitter of the primary PLL output with clean reference clock with no additional I/O toggling.

2. Output clock is valid after  $t_{LOCK}$  for PLL reset and dynamic delay adjustment.

3. Period jitter and cycle-to-cycle jitter numbers are guaranteed for  $f_{PFD} > 10$  MHz. For  $f_{PFD} < 10$  MHz, the jitter numbers may not be met in certain conditions.

## Table 3.31. PCIe (5 Gb/s) (Continued)

| Symbol                           | Description                                            | Test Conditions                      | Min               | Тур | Max              | Unit        |

|----------------------------------|--------------------------------------------------------|--------------------------------------|-------------------|-----|------------------|-------------|

| Receive <sup>1, 2</sup>          |                                                        | '                                    |                   | '   | '                |             |

| UI                               | Unit Interval                                          | -                                    | 199.94            | 200 | 200.06           | ps          |

| V <sub>RX-DIFF-PP</sub>          | Differential Rx peak-peak voltage                      | -                                    | 0.34 <sup>3</sup> | —   | 1.2              | V, p-p      |

| T <sub>RX-RJ-RMS</sub>           | Receiver random jitter tolerance<br>(RMS)              | 1.5 MHz – 100<br>MHz Random<br>noise | _                 | _   | 4.2              | ps,<br>RMS  |

| T <sub>RX-DJ</sub>               | Receiver deterministic jitter tolerance                | —                                    | —                 | —   | 88               | ps          |

| V <sub>RX-CM-AC</sub>            | Common mode noise from Rx                              | -                                    | _                 | _   |                  | mV,<br>p-p  |

| D                                | Receiver differential Return Loss,                     | 50 MHz < freq <<br>1.25 GHz          | 10                | _   | -                | dB          |

| R <sub>LRX-DIFF</sub>            | package plus silicon                                   | 1.25 GHz < freq<br>< 2.5 GHz         | 8                 | _   | -                | dB          |

| R <sub>LRX-CM</sub>              | Receiver common mode Return Loss, package plus silicon | -                                    | 6                 | _   | -                | dB          |

| Z <sub>RX-DC</sub>               | Receiver DC single ended impedance                     | _                                    | 40                | _   | 60               | Ω           |

| Z <sub>RX-HIGH-IMP-DC</sub>      | Receiver DC single ended impedance when powered down   | -                                    | 200K              | _   | -                | Ω           |

| V <sub>RX-CM-AC-P</sub>          | Rx AC peak common mode voltage                         | _                                    | _                 | _   |                  | mV,<br>peak |

| V <sub>RX-IDLE-DET-DIFF-PP</sub> | Electrical Idle Detect Threshold                       | -                                    | 65                | _   | 340 <sup>3</sup> | mv,         |

| L <sub>RX-SKEW</sub>             | Receiver lane-lane skew                                | -                                    | —                 | —   | 8                | ns          |

Notes:

1. Values are measured at 5 Gb/s.

2. Measured with external AC-coupling on the receiver.

3. Not in compliance with PCI Express standard.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

# 3.26. CPRI LV2 E.48 Electrical and Timing Characteristics – Preliminary

| Symbol                                     | Description                                                | Test Conditions                   | Min    | Тур    | Max                             | Unit        |

|--------------------------------------------|------------------------------------------------------------|-----------------------------------|--------|--------|---------------------------------|-------------|

| Transmit                                   | -                                                          |                                   |        |        |                                 |             |

| UI                                         | Unit Interval                                              | -                                 | 203.43 | 203.45 | 203.47                          | ps          |

| T <sub>DCD</sub>                           | Duty Cycle Distortion                                      | -                                 | -      | —      | 0.05                            | UI          |

| J <sub>UBHPJ</sub>                         | Uncorrelated Bounded High<br>Probability Jitter            | _                                 | _      | _      | 0.15                            | UI          |

| J <sub>TOTAL</sub>                         | Total Jitter                                               | -                                 | -      | _      | 0.3                             | UI          |

| Z <sub>RX-DIFF-DC</sub>                    | DC differential Impedance                                  | -                                 | 80     | -      | 120                             | Ω           |

| T <sub>SKEW</sub>                          | Skew between differential signals                          | _                                 | _      | —      | 9                               | ps          |

| D                                          | Tx Differential Return Loss (S22),                         | 100 MHz < freq<br>< 3.6864 GHz    | _      | -      | -8                              | dB          |

| R <sub>LTX-DIFF</sub>                      | including package and silicon                              | 3.6864 GHz < freq<br>< 4.9152 GHz | Ι      | _      | -8 + 16.6 *log<br>(freq/3.6864) | dB          |

| R <sub>LTX-CM</sub>                        | Tx Common Mode Return Loss, including package and silicon  | 100 MHz < freq<br>< 3.6864 GHz    | 6      | -      | -                               | dB          |

| I <sub>TX-SHORT</sub>                      | Transmitter short-circuit current                          | -                                 | _      | _      | 100                             | mA          |

| T <sub>RISE_FALL-DIFF</sub>                | Differential Rise and Fall Time                            | -                                 |        | —      | _                               | ps          |

| L <sub>TX-SKEW</sub>                       | Lane-to-lane output skew                                   | -                                 | _      | —      |                                 | ps          |

| Receive                                    |                                                            | ·                                 |        |        |                                 |             |

| UI                                         | Unit Interval                                              | —                                 | 203.43 | 203.45 | 203.47                          | ps          |

| V <sub>RX-DIFF-PP</sub>                    | Differential Rx peak-peak voltage                          | -                                 | _      | —      | 1.2                             | V, p-p      |

| V <sub>RX-EYE_Y1_Y2</sub>                  | Receiver eye opening mask, Y1 and Y2                       | _                                 | 62.5   | -      | 375                             | mV,<br>diff |

| V <sub>RX-EYE_X1</sub>                     | Receiver eye opening mask, X1                              | -                                 | -      | _      | 0.3                             | UI          |

| T <sub>RX-TJ</sub>                         | Receiver total jitter tolerance (not including sinusoidal) | _                                 | _      | _      | 0.6                             | UI          |

| P                                          | Receiver differential Return Loss,                         | 100 MHz < freq<br>< 3.6864 GHz    | _      | -      | -8                              | dB          |

| R <sub>LRX-DIFF</sub> package plus silicon |                                                            | 3.6864 GHz < freq<br>< 4.9152 GHz | _      | -      | -8 + 16.6 *log<br>(freq/3.6864) | dB          |

| R <sub>LRX-CM</sub>                        | Receiver common mode Return<br>Loss, package plus silicon  | _                                 | 6      | _      | _                               | dB          |

| Z <sub>RX-DIFF-DC</sub>                    | Receiver DC differential impedance                         | _                                 | 80     | 100    | 120                             | Ω           |

## Table 3.32. CPRI LV2 E.48 Electrical and Timing Characteristics

**Note**: Data is measured with PRBS7 data pattern, not with PRBS-31 pattern.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

#### Table 3.36. Receive and Jitter Tolerance

| Symbol                                       | Description                                   | Test Conditions         | Min  | Тур | Max  | Unit |

|----------------------------------------------|-----------------------------------------------|-------------------------|------|-----|------|------|

| RL <sub>RX_DIFF</sub>                        | Differential return loss                      | From 100 MHz to 2.5 GHz | 10   | —   | —    | dB   |

| RL <sub>RX_CM</sub>                          | Common mode return loss                       | From 100 MHz to 2.5 GHz | 6    | —   | —    | dB   |

| Z <sub>RX_DIFF</sub>                         | Differential termination resistance           | —                       | 80   | 100 | 120  | Ω    |

| J <sub>RX_DJ</sub> <sup>2, 3, 4</sup>        | Deterministic jitter tolerance (peak-to-peak) | _                       | —    | _   | 0.37 | UI   |

| J <sub>RX_RJ</sub> <sup>2, 3, 4</sup>        | Random jitter tolerance (peak-to-peak)        | -                       | —    | _   | 0.18 | UI   |

| <b>J</b> <sub>RX_SJ</sub> <sup>2, 3, 4</sup> | Sinusoidal jitter tolerance (peak-to-peak)    | _                       | —    | _   | 0.10 | UI   |

| J <sub>RX_TJ</sub> <sup>1, 2, 3, 4</sup>     | Total jitter tolerance (peak-to-peak)         | -                       | —    | _   | 0.65 | UI   |

| T <sub>RX_EYE</sub>                          | Receiver eye opening                          | _                       | 0.35 | _   | —    | UI   |

Notes:

- 1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter.

- 2. Jitter values are measured with each high-speed input AC coupled into a 50  $\Omega$  impedance.

- 3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 4. Jitter tolerance, Differential Input Sensitivity and Receiver Eye Opening parameters are characterized when Full Rx Equalization is enabled.

# 3.29. Gigabit Ethernet/SGMII(1.25Gbps)/CPRI LV E.12 Electrical and Timing Characteristics

## 3.29.1. AC and DC Characteristics

#### Table 3.37. Transmit

| Symbol                                | Description                      | Test Conditions | Min | Тур | Max  | Unit |

|---------------------------------------|----------------------------------|-----------------|-----|-----|------|------|

| T <sub>RF</sub>                       | Differential rise/fall time      | 20% to 80%      | _   | 80  | _    | ps   |

| Z <sub>TX_DIFF_DC</sub>               | Differential impedance           | -               | 80  | 100 | 120  | Ω    |

| J <sub>TX_DDJ</sub> <sup>2, 3</sup>   | Output data deterministic jitter | -               | _   | —   | 0.10 | UI   |

| J <sub>TX_TJ</sub> <sup>1, 2, 3</sup> | Total output data jitter         | _               | —   | —   | 0.24 | UI   |

Notes:

1. Total jitter includes both deterministic jitter and random jitter. The random jitter is the total jitter minus the actual deterministic jitter.

2. Jitter values are measured with each CML output AC coupled into a 50  $\Omega$  impedance (100  $\Omega$  differential impedance).

3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

#### Table 3.38. Receive and Jitter Tolerance

| Symbol                                   | Description                                   | Test Conditions          | Min  | Тур | Max  | Unit |

|------------------------------------------|-----------------------------------------------|--------------------------|------|-----|------|------|

| RL <sub>RX_DIFF</sub>                    | Differential return loss                      | From 100 MHz to 1.25 GHz | 10   | -   | —    | dB   |

| RL <sub>RX_CM</sub>                      | Common mode return loss                       | From 100 MHz to 1.25 GHz | 6    | -   | —    | dB   |

| Z <sub>RX_DIFF</sub>                     | Differential termination resistance           | -                        | 80   | 100 | 120  | Ω    |

| J <sub>RX_DJ</sub> <sup>1, 2, 3, 4</sup> | Deterministic jitter tolerance (peak-to-peak) | -                        | -    | _   | 0.34 | UI   |

| J <sub>RX_RJ</sub> <sup>1, 2, 3, 4</sup> | Random jitter tolerance (peak-to-peak)        | -                        | -    | -   | 0.26 | UI   |

| J <sub>RX_SJ</sub> <sup>1, 2, 3, 4</sup> | Sinusoidal jitter tolerance (peak-to-peak)    | -                        | -    | _   | 0.11 | UI   |

| J <sub>RX_TJ</sub> <sup>1, 2, 3, 4</sup> | Total jitter tolerance (peak-to-peak)         | —                        | _    | _   | 0.71 | UI   |

| T <sub>RX_EYE</sub>                      | Receiver eye opening                          | —                        | 0.29 | -   | _    | UI   |

Notes:

1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter.

- 2. Jitter values are measured with each high-speed input AC coupled into a 50  $\Omega$  impedance.

- 3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 4. Jitter tolerance, Differential Input Sensitivity and Receiver Eye Opening parameters are characterized when Full Rx Equalization is enabled.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

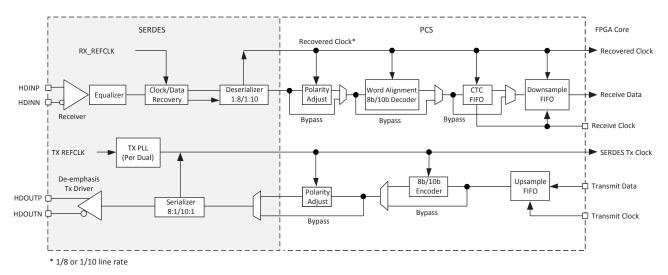

Figure 3.23. JTAG Port Timing Waveforms

# 3.33. Switching Test Conditions

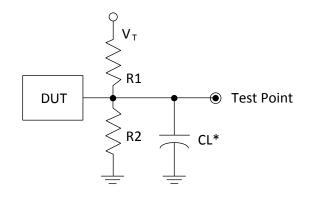

Figure 3.24 shows the output test load that is used for AC testing. The specific values for resistance, capacitance, voltage, and other test conditions are listed in Table 3.44.

\*CL Includes Test Fixture and Probe Capacitance

### Figure 3.24. Output Test Load, LVTTL and LVCMOS Standards

| Signal Name                          | I/O      | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL, DLL and Clock Functions (Contin | nued)    |                                                                                                                                                                                                                                                                                                                                                                                             |

| [L/R]DQS[group_num]                  | I/O      | DQS input/output pads: T (top), R (right), group_num = ball number associated with DQS[T] pin.                                                                                                                                                                                                                                                                                              |

| [T/R]]DQ[group_num]                  | I/O      | DQ input/output pads: T (top), R (right), group_ num = ball number associated with DQS[T] pin.                                                                                                                                                                                                                                                                                              |

| Test and Programming (Dedicated F    | Pins)    |                                                                                                                                                                                                                                                                                                                                                                                             |

| TMS                                  | I        | Test Mode Select input, used to control the 1149.1 state machine. Pull-up is enabled during configuration. This is a dedicated input pin.                                                                                                                                                                                                                                                   |

| тск                                  | I        | Test Clock input pin, used to clock the 1149.1 state machine. No pull-up enabled.<br>This is a dedicated input pin.                                                                                                                                                                                                                                                                         |

| TDI                                  | I        | Test Data in pin. Used to load data into device using 1149.1 state machine. After power-up, this TAP port can be activated for configuration by sending appropriate command. (Note: once a configuration port is selected it is locked. Another configuration port cannot be selected until the power-up sequence). Pull-up is enabled during configuration. This is a dedicated input pin. |

| TDO                                  | 0        | Output pin. Test Data Out pin used to shift data out of a device using 1149.1.<br>This is a dedicated output pin.                                                                                                                                                                                                                                                                           |

| Configuration Pads (Used during sys  | sCONFIG) |                                                                                                                                                                                                                                                                                                                                                                                             |

| CFG[2:0]                             | I        | Mode pins used to specify configuration mode values latched on rising edge of INITN. During configuration, a pull-up is enabled.<br>These are dedicated pins.                                                                                                                                                                                                                               |

| INITN                                | I/O      | Open Drain pin. Indicates the FPGA is ready to be configured. During configuration, a pull-up is enabled.<br>This is a dedicated pin.                                                                                                                                                                                                                                                       |

| PROGRAMN                             | 1        | Initiates configuration sequence when asserted low. This pin always has an active pull-up.<br>This is a dedicated pin.                                                                                                                                                                                                                                                                      |

| DONE                                 | I/O      | Open Drain pin. Indicates that the configuration sequence is complete, and the startup sequence is in progress.<br>This is a dedicated pin.                                                                                                                                                                                                                                                 |

| ССГК                                 | I/O      | Input Configuration Clock for configuring an FPGA in Slave SPI, Serial, and CPU modes. Output Configuration Clock for configuring an FPGA in Master configuration modes (Master SPI, Master Serial).<br>This is a dedicated pin.                                                                                                                                                            |

| HOLDN/DI/BUSY/CSSPIN/CEN             | I/O      | Parallel configuration mode busy indicator. SPI/SPIm mode data output.<br>This is a shared I/O pin. This is a shared I/O pin. When not in configuration, it can<br>be used as general purpose I/O pin.                                                                                                                                                                                      |

| CSN/SN                               | ı/o      | Parallel configuration mode active-low chip select. Slave SPI chip select. This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O pin.                                                                                                                                                                                                                  |

| CS1N                                 | I        | Parallel configuration mode active-low chip select.<br>This is a shared I/O pin. When not in configuration, it can be used as general<br>purpose I/O pin.                                                                                                                                                                                                                                   |

| WRITEN                               | I        | Write enable for parallel configuration modes.<br>This is a shared I/O pin. When not in configuration, it can be used as general<br>purpose I/O pin.                                                                                                                                                                                                                                        |

| DOUT/CSON                            | о        | Serial data output. Chip select output. SPI/SPIm mode chip select. This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O                                                                                                                                                                                                                               |

| D0/MOSI/IO0                          | I/O      | Parallel configuration I/O. Open drain during configuration. When in SPI modes,<br>it is an output in Master mode, and input in Slave mode.<br>This is a shared I/O pin. When not in configuration, it can be used as general<br>purpose I/O pin.                                                                                                                                           |

<sup>© 2014-2018</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Part number          | Grade | Package          | Pins | Temp.      | LUTs (K) | SERDES |

|----------------------|-------|------------------|------|------------|----------|--------|

| LFE5U-45F-8BG554C    | -8    | Lead free caBGA  | 554  | Commercial | 44       | No     |

| LFE5U-85F-6MG285C    | -6    | Lead free csfBGA | 285  | Commercial | 84       | No     |

| LFE5U-85F-7MG285C    | -7    | Lead free csfBGA | 285  | Commercial | 84       | No     |

| LFE5U-85F-8MG285C    | -8    | Lead free csfBGA | 285  | Commercial | 84       | No     |

| LFE5U-85F-6BG381C    | -6    | Lead free caBGA  | 381  | Commercial | 84       | No     |

| LFE5U-85F-7BG381C    | -7    | Lead free caBGA  | 381  | Commercial | 84       | No     |

| LFE5U-85F-8BG381C    | -8    | Lead free caBGA  | 381  | Commercial | 84       | No     |

| LFE5U-85F-6BG554C    | -6    | Lead free caBGA  | 554  | Commercial | 84       | No     |

| LFE5U-85F-7BG554C    | -7    | Lead free caBGA  | 554  | Commercial | 84       | No     |

| LFE5U-85F-8BG554C    | -8    | Lead free caBGA  | 554  | Commercial | 84       | No     |

| LFE5U-85F-6BG756C    | -6    | Lead free caBGA  | 756  | Commercial | 84       | No     |

| LFE5U-85F-7BG756C    | -7    | Lead free caBGA  | 756  | Commercial | 84       | No     |

| LFE5U-85F-8BG756C    | -8    | Lead free caBGA  | 756  | Commercial | 84       | No     |

| LFE5UM-25F-6MG285C   | -6    | Lead free csfBGA | 285  | Commercial | 24       | Yes    |

| LFE5UM-25F-7MG285C   | -7    | Lead free csfBGA | 285  | Commercial | 24       | Yes    |

| LFE5UM-25F-8MG285C   | -8    | Lead free csfBGA | 285  | Commercial | 24       | Yes    |

| LFE5UM-25F-6BG381C   | -6    | Lead free caBGA  | 381  | Commercial | 24       | Yes    |

| LFE5UM-25F-7BG381C   | -7    | Lead free caBGA  | 381  | Commercial | 24       | Yes    |

| LFE5UM-25F-8BG381C   | -8    | Lead free caBGA  | 381  | Commercial | 24       | Yes    |

| LFE5UM-45F-6MG285C   | -6    | Lead free csfBGA | 285  | Commercial | 44       | Yes    |

| LFE5UM-45F-7MG285C   | -7    | Lead free csfBGA | 285  | Commercial | 44       | Yes    |

| LFE5UM-45F-8MG285C   | -8    | Lead free csfBGA | 285  | Commercial | 44       | Yes    |

| LFE5UM-45F-6BG381C   | -6    | Lead free caBGA  | 381  | Commercial | 44       | Yes    |

| LFE5UM-45F-7BG381C   | -7    | Lead free caBGA  | 381  | Commercial | 44       | Yes    |

| LFE5UM-45F-8BG381C   | -8    | Lead free caBGA  | 381  | Commercial | 44       | Yes    |

| LFE5UM-45F-6BG554C   | -6    | Lead free caBGA  | 554  | Commercial | 44       | Yes    |

| LFE5UM-45F-7BG554C   | -7    | Lead free caBGA  | 554  | Commercial | 44       | Yes    |

| LFE5UM-45F-8BG554C   | -8    | Lead free caBGA  | 554  | Commercial | 44       | Yes    |

| LFE5UM-85F-6MG285C   | -6    | Lead free csfBGA | 285  | Commercial | 84       | Yes    |

| LFE5UM-85F-7MG285C   | -7    | Lead free csfBGA | 285  | Commercial | 84       | Yes    |

| LFE5UM-85F-8MG285C   | -8    | Lead free csfBGA | 285  | Commercial | 84       | Yes    |

| LFE5UM-85F-6BG381C   | -6    | Lead free caBGA  | 381  | Commercial | 84       | Yes    |

| LFE5UM-85F-7BG381C   | -7    | Lead free caBGA  | 381  | Commercial | 84       | Yes    |

| LFE5UM-85F-8BG381C   | -8    | Lead free caBGA  | 381  | Commercial | 84       | Yes    |

| LFE5UM-85F-6BG554C   | -6    | Lead free caBGA  | 554  | Commercial | 84       | Yes    |

| LFE5UM-85F-7BG554C   | -7    | Lead free caBGA  | 554  | Commercial | 84       | Yes    |

| LFE5UM-85F-8BG554C   | -8    | Lead free caBGA  | 554  | Commercial | 84       | Yes    |

| LFE5UM-85F-6BG756C   | -6    | Lead free caBGA  | 756  | Commercial | 84       | Yes    |

| LFE5UM-85F-7BG756C   | -7    | Lead free caBGA  | 756  | Commercial | 84       | Yes    |

| LFE5UM-85F-8BG756C   | -8    | Lead free caBGA  | 756  | Commercial | 84       | Yes    |

| LFE5UM5G-25F-8MG285C | -8    | Lead free csfBGA | 285  | Commercial | 24       | Yes    |

| LFE5UM5G-25F-8BG381C | -8    | Lead free caBGA  | 381  | Commercial | 24       | Yes    |

| LFE5UM5G-45F-8MG285C | -8    | Lead free csfBGA | 285  | Commercial | 44       | Yes    |

| LFE5UM5G-45F-8BG381C | -8    | Lead free caBGA  | 381  | Commercial | 44       | Yes    |

| LFE5UM5G-45F-8BG554C | -8    | Lead free caBGA  | 554  | Commercial | 44       | Yes    |

| LFE5UM5G-85F-8MG285C | -8    | Lead free csfBGA | 285  | Commercial | 84       | Yes    |

| Part number          | Grade | Package          | Pins | Temp.      | LUTs (K) | SERDES |

|----------------------|-------|------------------|------|------------|----------|--------|

| LFE5U-85F-6BG756I    | -6    | Lead free caBGA  | 756  | Industrial | 84       | No     |

| LFE5U-85F-7BG756I    | -7    | Lead free caBGA  | 756  | Industrial | 84       | No     |

| LFE5U-85F-8BG756I    | -8    | Lead free caBGA  | 756  | Industrial | 84       | No     |

| LFE5UM-25F-6MG285I   | -6    | Lead free csfBGA | 285  | Industrial | 24       | Yes    |

| LFE5UM-25F-7MG285I   | -7    | Lead free csfBGA | 285  | Industrial | 24       | Yes    |

| LFE5UM-25F-8MG285I   | -8    | Lead free csfBGA | 285  | Industrial | 24       | Yes    |

| LFE5UM-25F-6BG381I   | -6    | Lead free caBGA  | 381  | Industrial | 24       | Yes    |

| LFE5UM-25F-7BG381I   | -7    | Lead free caBGA  | 381  | Industrial | 24       | Yes    |

| LFE5UM-25F-8BG381I   | -8    | Lead free caBGA  | 381  | Industrial | 24       | Yes    |

| LFE5UM-45F-6MG285I   | -6    | Lead free csfBGA | 285  | Industrial | 44       | Yes    |

| LFE5UM-45F-7MG285I   | -7    | Lead free csfBGA | 285  | Industrial | 44       | Yes    |

| LFE5UM-45F-8MG285I   | -8    | Lead free csfBGA | 285  | Industrial | 44       | Yes    |

| LFE5UM-45F-6BG381I   | -6    | Lead free caBGA  | 381  | Industrial | 44       | Yes    |

| LFE5UM-45F-7BG381I   | -7    | Lead free caBGA  | 381  | Industrial | 44       | Yes    |

| LFE5UM-45F-8BG381I   | -8    | Lead free caBGA  | 381  | Industrial | 44       | Yes    |

| LFE5UM-45F-6BG554I   | -6    | Lead free caBGA  | 554  | Industrial | 44       | Yes    |

| LFE5UM-45F-7BG554I   | -7    | Lead free caBGA  | 554  | Industrial | 44       | Yes    |

| LFE5UM-45F-8BG554I   | -8    | Lead free caBGA  | 554  | Industrial | 44       | Yes    |

| LFE5UM-85F-6MG285I   | -6    | Lead free csfBGA | 285  | Industrial | 84       | Yes    |

| LFE5UM-85F-7MG285I   | -7    | Lead free csfBGA | 285  | Industrial | 84       | Yes    |

| LFE5UM-85F-8MG285I   | -8    | Lead free csfBGA | 285  | Industrial | 84       | Yes    |

| LFE5UM-85F-6BG381I   | -6    | Lead free caBGA  | 381  | Industrial | 84       | Yes    |

| LFE5UM-85F-7BG381I   | -7    | Lead free caBGA  | 381  | Industrial | 84       | Yes    |

| LFE5UM-85F-8BG381I   | -8    | Lead free caBGA  | 381  | Industrial | 84       | Yes    |

| LFE5UM-85F-6BG554I   | -6    | Lead free caBGA  | 554  | Industrial | 84       | Yes    |

| LFE5UM-85F-7BG554I   | -7    | Lead free caBGA  | 554  | Industrial | 84       | Yes    |

| LFE5UM-85F-8BG554I   | -8    | Lead free caBGA  | 554  | Industrial | 84       | Yes    |

| LFE5UM-85F-6BG756I   | -6    | Lead free caBGA  | 756  | Industrial | 84       | Yes    |

| LFE5UM-85F-7BG756I   | -7    | Lead free caBGA  | 756  | Industrial | 84       | Yes    |

| LFE5UM-85F-8BG756I   | -8    | Lead free caBGA  | 756  | Industrial | 84       | Yes    |

| LFE5UM5G-25F-8MG285I | -8    | Lead free csfBGA | 285  | Industrial | 24       | Yes    |

| LFE5UM5G-25F-8BG381I | -8    | Lead free caBGA  | 381  | Industrial | 24       | Yes    |

| LFE5UM5G-45F-8MG285I | -8    | Lead free csfBGA | 285  | Industrial | 44       | Yes    |

| LFE5UM5G-45F-8BG381I | -8    | Lead free caBGA  | 381  | Industrial | 44       | Yes    |

| LFE5UM5G-45F-8BG554I | -8    | Lead free caBGA  | 554  | Industrial | 44       | Yes    |

| LFE5UM5G-85F-8MG285I | -8    | Lead free csfBGA | 285  | Industrial | 84       | Yes    |

| LFE5UM5G-85F-8BG381I | -8    | Lead free caBGA  | 381  | Industrial | 84       | Yes    |

| LFE5UM5G-85F-8BG554I | -8    | Lead free caBGA  | 554  | Industrial | 84       | Yes    |

| LFE5UM5G-85F-8BG756I | -8    | Lead free caBGA  | 756  | Industrial | 84       | Yes    |

# **Supplemental Information**

# **For Further Information**

A variety of technical notes for the ECP5/ECP5-5G family are available.

- High-Speed PCB Design Considerations (TN1033)

- Transmission of High-Speed Serial Signals Over Common Cable Media (TN1066)

- PCB Layout Recommendations for BGA Packages (TN1074)

- Minimizing System Interruption During Configuration Using TransFR Technology (TN1087)

- Electrical Recommendations for Lattice SERDES (FPGA-TN-02077)

- LatticeECP3, ECP-5 and ECP5-5G Soft Error Detection (SED)/Correction (SEC) Usage Guide (TN1184)

- Using TraceID (TN1207)

- Sub-LVDS Signaling Using Lattice Devices (TN1210)

- Advanced Security Encryption Key Programming Guide for ECP5, ECP5-5G, LatticeECP3, and LatticeECP2/MS Devices (TN1215)

- LatticeECP3, LatticeECP2/M, ECP5 and ECP5-5G Dual Boot and Multiple Boot Feature (TN1216)

- ECP5 and ECP5-5G sysCONFIG Usage Guide (TN1260)

- ECP5 and ECP5-5G SERDES/PCS Usage Guide (TN1261)

- ECP5 and ECP5-5G sysIO Usage Guide (TN1262)

- ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263)

- ECP5 and ECP5-5G Memory Usage Guide (TN1264)

- ECP5 and ECP5-5G High-Speed I/O Interface (TN1265)

- Power Consumption and Management for ECP5 and ECP5-5G Devices (TN1266)

- ECP5 and ECP5-5G sysDSP Usage Guide (TN1267)

- ECP5 and ECP5-5G Hardware Checklist (FPGA-TN-02038)

- Solder Reflow Guide for Surface Mount Devices (FPGA-TN-02041)

- ECP5 and ECP5-5G PCI Express Soft IP Ease of Use Guidelines (FPGA-TN-02045)

- Programming External SPI Flash through JTAG for ECP5/ECP5-5G (FPGA-TN-02050)