Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                       |

|--------------------------------|------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 3000                                                                         |

| Number of Logic Elements/Cells | 12000                                                                        |

| Total RAM Bits                 | 589824                                                                       |

| Number of I/O                  | 197                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.045V ~ 1.155V                                                              |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                           |

| Package / Case                 | 256-LFBGA                                                                    |

| Supplier Device Package        | 256-CABGA (14x14)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe5u-12f-8bg256i |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Contents

| Acronyms in This Document                                   |    |

|-------------------------------------------------------------|----|

| 1. General Description                                      | 10 |

| 1.1. Features                                               | 10 |

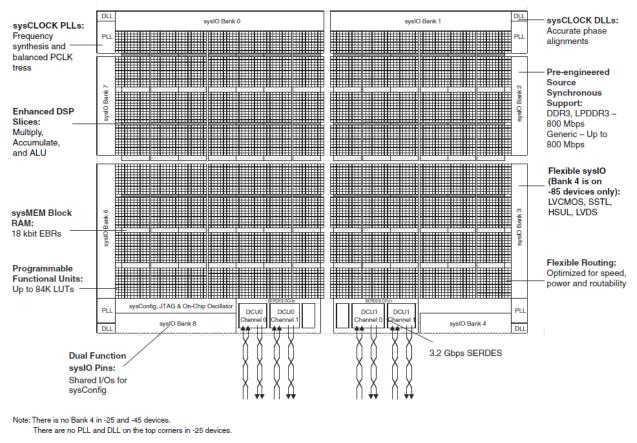

| 2. Architecture                                             | 12 |

| 2.1. Overview                                               | 12 |

| 2.2. PFU Blocks                                             | 13 |

| 2.2.1. Slice                                                | 14 |

| 2.2.2. Modes of Operation                                   | 17 |

| 2.3. Routing                                                |    |

| 2.4. Clocking Structure                                     |    |

| 2.4.1. sysCLOCK PLL                                         |    |

| 2.5. Clock Distribution Network                             | 19 |

| 2.5.1. Primary Clocks                                       | 20 |

| 2.5.2. Edge Clock                                           | 21 |

| 2.6. Clock Dividers                                         |    |

| 2.7. DDRDLL                                                 |    |

| 2.8. sysMEM Memory                                          |    |

| 2.8.1. sysMEM Memory Block                                  |    |

| 2.8.2. Bus Size Matching                                    |    |

| 2.8.3. RAM Initialization and ROM Operation                 |    |

| 2.8.4. Memory Cascading                                     |    |

| 2.8.5. Single, Dual and Pseudo-Dual Port Modes              |    |

| 2.8.6. Memory Core Reset                                    |    |

| 2.9. sysDSP <sup>™</sup> Slice                              |    |

| 2.9.1. sysDSP Slice Approach Compared to General DSP        |    |

| 2.9.2. sysDSP Slice Architecture Features                   |    |

| 2.10. Programmable I/O Cells                                |    |

| 2.11. PIO                                                   |    |

| 2.11. Input Register Block                                  |    |

| 2.11.2. Output Register Block                               |    |

| 2.12. Tristate Register Block                               |    |

| 2.12. DDR Memory Support                                    |    |

| 2.13. DQS Grouping for DDR Memory                           |    |

| 2.13.2. DLL Calibrated DQS Delay and Control Block (DQSBUF) |    |

| 2.14. sysl/O Buffer                                         |    |

| 2.14. sysi/O Buffer Banks                                   |    |

| 2.14.1. Syst/O Burlet Balliss                               |    |

| 2.14.2. Typical syst/O f/O Benavior during Power-up         |    |

| 2.14.3. Supported syst/O Standards                          |    |

| 2.14.4. On-Chip Programmable Termination                    |    |

| 2.14.5. For socketing                                       |    |

| 2.15. SERDES and Physical County Sublayer                   |    |

|                                                             |    |

|                                                             |    |

| 2.15.3. SERDES Client Interface Bus                         |    |

| 2.16. Flexible Dual SERDES Architecture                     |    |

| 2.17. IEEE 1149.1-Compliant Boundary Scan Testability       |    |

| 2.18. Device Configuration                                  |    |

| 2.18.1. Enhanced Configuration Options                      |    |

| 2.18.2. Single Event Upset (SEU) Support                    |    |

| 2.18.3. On-Chip Oscillator                                  |    |

| 2.19. Density Shifting                                      |    |

| 3. DC and Switching Characteristics                         | 47 |

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

### 2.2. **PFU Blocks**

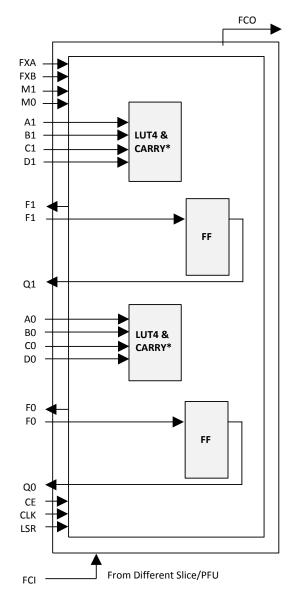

The core of the ECP5/ECP5-5G device consists of PFU blocks. Each PFU block consists of four interconnected slices numbered 0-3, as shown in Figure 2.2. Each slice contains two LUTs. All the interconnections to and from PFU blocks are from routing. There are 50 inputs and 23 outputs associated with each PFU block.

The PFU block can be used in Distributed RAM or ROM function, or used to perform Logic, Arithmetic, or ROM functions. Table 2.1 shows the functions each slice can perform in either mode.

Notes: For Slices 0 and 1, memory control signals are generated from Slice 2 as follows: WCK is CLK

WRE is from LSR

DI[3:2] for Slice 1 and DI[1:0] for Slice 0 data from Slice 2 WAD [A:D] is a 4-bit address from slice 2 LUT input

Figure 2.3. Slice Diagram

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

### 2.2.2. Modes of Operation

Slices 0-2 have up to four potential modes of operation: Logic, Ripple, RAM and ROM. Slice 3 is not needed for RAM mode, it can be used in Logic, Ripple, or ROM modes.

### Logic Mode

In this mode, the LUTs in each slice are configured as 4-input combinatorial lookup tables. A LUT4 can have 16 possible input combinations. Any four input logic functions can be generated by programming this lookup table. Since there are two LUT4s per slice, a LUT5 can be constructed within one slice. Larger look-up tables such as LUT6, LUT7 and LUT8 can be constructed by concatenating other slices. Note that LUT8 requires more than four slices.

### **Ripple Mode**

Ripple mode supports the efficient implementation of small arithmetic functions. In ripple mode, the following functions can be implemented by each slice:

- Addition 2-bit

- Subtraction 2-bit

- Add/Subtract 2-bit using dynamic control

- Up counter 2-bit

- Down counter 2-bit

- Up/Down counter with asynchronous clear

- Up/Down counter with preload (sync)

- Ripple mode multiplier building block

- Multiplier support

- Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Ripple Mode includes an optional configuration that performs arithmetic using fast carry chain methods. In this configuration (also referred to as CCU2 mode) two additional signals, Carry Generate and Carry Propagate, are generated on a per slice basis to allow fast arithmetic functions to be constructed by concatenating Slices.

#### **RAM Mode**

In this mode, a 16x4-bit distributed single port RAM (SPR) can be constructed in one PFU using each LUT block in Slice 0 and Slice 1 as a 16 x 2-bit memory in each slice. Slice 2 is used to provide memory address and control signals. A 16 x 2-bit pseudo dual port RAM (PDPR) memory is created in one PFU by using one Slice as the read-write port and the other companion slice as the read-only port. The slice with the read-write port updates the SRAM data contents in both slices at the same write cycle.

ECP5/ECP5-5G devices support distributed memory initialization.

The Lattice design tools support the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2.3 lists the number of slices required to implement different distributed RAM primitives. For more information about using RAM in ECP5/ECP5-5G devices, refer to ECP5 and ECP5-5G Memory Usage Guide (TN1264).

#### Table 2.3. Number of Slices Required to Implement Distributed RAM

|                  | SPR 16 X 4 | PDPR 16 X 4 |

|------------------|------------|-------------|

| Number of slices | 3          | 6           |

|                  |            |             |

Note: SPR = Single Port RAM, PDPR = Pseudo Dual Port RAM

### ROM Mode

ROM mode uses the LUT logic; hence, Slices 0 through 3 can be used in ROM mode. Preloading is accomplished through the programming interface during PFU configuration.

For more information, refer to ECP5 and ECP5-5G Memory Usage Guide (TN1264).

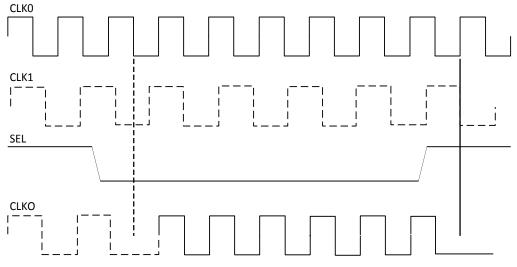

### 2.5.1.2. Dynamic Clock Select

The Dynamic Clock Select (DCS) is a smart multiplexer function available in the primary clock routing. It switches between two independent input clock sources. Depending on the operation modes, it switches between two (2) independent input clock sources either with or without any glitches. This is achieved regardless of when the select signal is toggled. Both input clocks must be running to achieve functioning glitch-less DCS output clock, but it is not required running clocks when used as non-glitch-less normal clock multiplexer.

There are two DCS blocks per device that are fed to all quadrants. The inputs to the DCS block come from all the output of MIDMUXs and Clock from CIB located at the center of the PLC array core. The output of the DCS is connected to one of the inputs of Primary Clock Center MUX.

Figure 2.7 shows the timing waveforms of the default DCS operating mode. The DCS block can be programmed to other modes. For more information about the DCS, refer to ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263).

Figure 2.7. DCS Waveforms

### 2.5.2. Edge Clock

ECP5/ECP5-5G devices have a number of high-speed edge clocks that are intended for use with the PIOs in the implementation of high-speed interfaces. There are two ECLK networks per bank IO on the Left and Right sides of the devices.

Each Edge Clock can be sourced from the following:

- Dedicated Clock input pins (PCLK)

- DLLDEL output (Clock delayed by 90o)

- PLL outputs (CLKOP and CLKOS)

- ECLKBRIDGE

- Internal Nodes

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

\*For 7:1 LVDS interface only. It is required to use PIO pair pins PIOA/B.

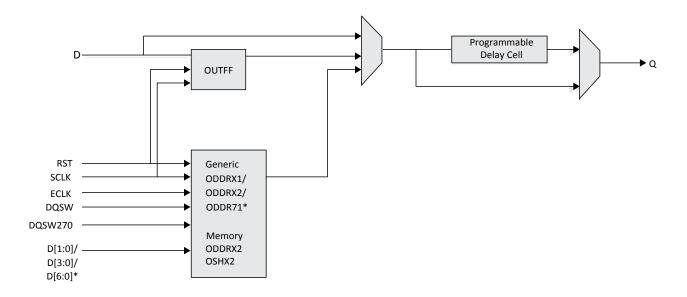

#### Figure 2.20. Output Register Block on Left and Right Sides

| Name                  | Туре   | Description                                                         |

|-----------------------|--------|---------------------------------------------------------------------|

| Q                     | Output | High Speed Data Output                                              |

| D                     | Input  | Data from core to output SDR register                               |

| D[1:0]/D[3:0]/ D[6:0] | Input  | Low Speed Data from device core to output DDR register              |

| RST                   | Input  | Reset to the Output Block                                           |

| SCLK                  | Input  | Slow Speed System Clock                                             |

| ECLK                  | Input  | High Speed Edge Clock                                               |

| DQSW                  | Input  | Clock from DQS control Block used to generate DDR memory DQS output |

| DQSW270               | Input  | Clock from DQS control Block used to generate DDR memory DQ output  |

#### Table 2.9. Output Block Port Description

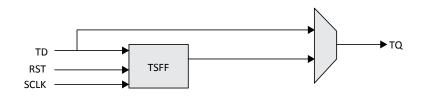

### 2.12. Tristate Register Block

The tristate register block registers tristate control signals from the core of the device before they are passed to the sysIO buffers. The block contains a register for SDR operation. In SDR, TD input feeds one of the flip-flops that then feeds the output. In DDR operation used mainly for DDR memory interface can be implemented on the left and right sides of the device. Here two inputs feed the tristate registers clocked by both ECLK and SCLK.

Figure 2.21 and Figure 2.22 show the Tristate Register Block functions on the device. For detailed description of the tristate register block modes and usage, refer to ECP5 and ECP5-5G High-Speed I/O Interface (TN1265).

Figure 2.21. Tristate Register Block on Top Side

| Package    | LFE5UM/LFE5UM5G-25 | LFE5UM/LFE5UM5G-45 | LFE5UM/LFE5UM5G-85 |

|------------|--------------------|--------------------|--------------------|

| 285 csfBGA | 1                  | 1                  | 1                  |

| 381 caBGA  | 1                  | 2                  | 2                  |

| 554 caBGA  | -                  | 2                  | 2                  |

| 756 caBGA  | -                  | -                  | 2                  |

### Table 2.14. Available SERDES Duals per LFE5UM/LFE5UM5G Devices

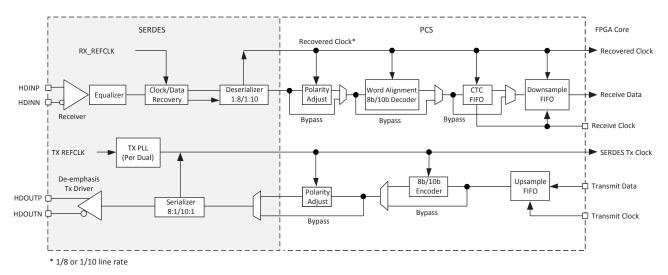

### 2.15.1. SERDES Block

A SERDES receiver channel may receive the serial differential data stream, equalize the signal, perform Clock and Data Recovery (CDR) and de-serialize the data stream before passing the 8- or 10-bit data to the PCS logic. The SERDES transmitter channel may receive the parallel 8- or 10-bit data, serialize the data and transmit the serial bit stream through the differential drivers. Figure 2.28 shows a single-channel SERDES/PCS block. Each SERDES channel provides a recovered clock and a SERDES transmit clock to the PCS block and to the FPGA core logic.

Each transmit channel, receiver channel, and SERDES PLL shares the same power supply (VCCA). The output and input buffers of each channel have their own independent power supplies (VCCHTX and VCCHRX).

Figure 2.28. Simplified Channel Block Diagram for SERDES/PCS Block

### 2.15.2. PCS

As shown in Figure 2.28, the PCS receives the parallel digital data from the deserializer and selects the polarity, performs word alignment, decodes (8b/10b), provides Clock Tolerance Compensation and transfers the clock domain from the recovered clock to the FPGA clock via the Down Sample FIFO.

For the transmit channel, the PCS block receives the parallel data from the FPGA core, encodes it with 8b/10b, selects the polarity and passes the 8/10 bit data to the transmit SERDES channel.

The PCS also provides bypass modes that allow a direct 8-bit or 10-bit interface from the SERDES to the FPGA logic. The PCS interface to the FPGA can also be programmed to run at 1/2 speed for a 16-bit or 20-bit interface to the FPGA logic. Some of the enhancements in LFE5UM/LFE5UM5G SERDES/PCS include:

- Higher clock/channel granularity: Dual channel architecture provides more clock resource per channel.

- Enhanced Tx de-emphasis: Programmable pre- and post-cursors improves Tx output signaling

- Bit-slip function in PCS: Improves logic needed to perform Word Alignment function

Refer to ECP5 and ECP5-5G SERDES/PCS Usage Guide (TN1261) for more information.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

## 2.18. Device Configuration

All ECP5/ECP5-5G devices contain two ports that can be used for device configuration. The Test Access Port (TAP), which supports bit-wide configuration, and the sysCONFIG port, support dual-byte, byte and serial configuration. The TAP supports both the IEEE Standard 1149.1 Boundary Scan specification and the IEEE Standard 1532 In-System Configuration specification. There are 11 dedicated pins for TAP and sysConfig supports (TDI, TDO, TCK, TMS, CFG[2:0], PROGRAMN, DONE, INITN and CCLK). The remaining sysCONFIG pins are used as dual function pins. Refer to ECP5 and ECP5-5G sysCONFIG Usage Guide (TN1260) for more information about using the dual-use pins as general purpose I/Os.

There are various ways to configure an ECP5/ECP5-5G device:

- JTAG

- Standard Serial Peripheral Interface (SPI) Interface to boot PROM Support x1, x2, x4 wide SPI memory interfaces.

- System microprocessor to drive a x8 CPU port SPCM mode

- System microprocessor to drive a serial slave SPI port (SSPI mode)

- Slave Serial model (SCM)

On power-up, the FPGA SRAM is ready to be configured using the selected sysCONFIG port. Once a configuration port is selected, it will remain active throughout that configuration cycle. The IEEE 1149.1 port can be activated any time after power-up by sending the appropriate command through the TAP port.

ECP5/ECP5-5G devices also support the Slave SPI Interface. In this mode, the FPGA behaves like a SPI Flash device (slave mode) with the SPI port of the FPGA to perform read-write operations.

### 2.18.1. Enhanced Configuration Options

ECP5/ECP5-5G devices have enhanced configuration features such as: decryption support, decompression support, TransFR™ I/O and dual-boot and multi-boot image support.

### TransFR (Transparent Field Reconfiguration)

TransFR I/O (TFR) is a unique Lattice technology that allows users to update their logic in the field without interrupting system operation using a single ispVM command. TransFR I/O allows I/O states to be frozen during device configuration. This allows the device to be field updated with a minimum of system disruption and downtime. Refer to Minimizing System Interruption During Configuration Using TransFR Technology (TN1087) for details.

### **Dual-Boot and Multi-Boot Image Support**

Dual-boot and multi-boot images are supported for applications requiring reliable remote updates of configuration data for the system FPGA. After the system is running with a basic configuration, a new boot image can be downloaded remotely and stored in a separate location in the configuration storage device. Any time after the update the ECP5/ECP5-5G devices can be re-booted from this new configuration file. If there is a problem, such as corrupt data during download or incorrect version number with this new boot image, the ECP5/ECP5-5G device can revert back to the original backup golden configuration and try again. This all can be done without power cycling the system. For more information, refer to ECP5 and ECP5-5G sysCONFIG Usage Guide (TN1260).

### 2.18.2. Single Event Upset (SEU) Support

ECP5/ECP5-5G devices support SEU mitigation with three supporting functions:

- SED Soft Error Detect

- SEC Soft Error Correction

- SEI Soft Error Injection

ECP5/ECP5-5G devices have dedicated logic to perform Cycle Redundancy Code (CRC) checks. During configuration, the configuration data bitstream can be checked with the CRC logic block. In addition, the ECP5/ECP5-5G device can also be programmed to utilize a Soft Error Detect (SED) mode that checks for soft errors in configuration SRAM. The SED operation can be run in the background during user mode. If a soft error occurs, during user mode (normal operation) the device can be programmed to generate an error signal.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

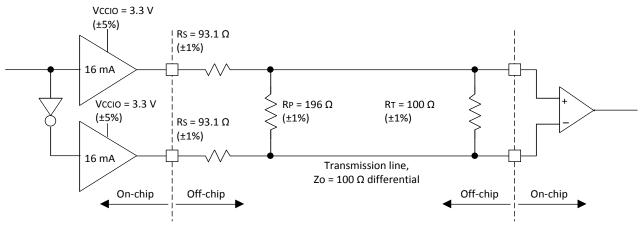

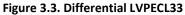

### 3.14.6. LVPECL33

The ECP5/ECP5-5G devices support the differential LVPECL standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The LVPECL input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3.3 is one possible solution for point-to-point signals.

Over recommended operating conditions.

| Parameter         | Description                    | Typical | Unit |

|-------------------|--------------------------------|---------|------|

| V <sub>CCIO</sub> | Output Driver Supply (±5%)     | 3.30    | V    |

| Z <sub>OUT</sub>  | Driver Impedance               | 10      | Ω    |

| Rs                | Driver Series Resistor (±1%)   | 93      | Ω    |

| R <sub>P</sub>    | Driver Parallel Resistor (±1%) | 196     | Ω    |

| R <sub>T</sub>    | Receiver Termination (±1%)     | 100     | Ω    |

| V <sub>OH</sub>   | Output High Voltage            | 2.05    | V    |

| V <sub>OL</sub>   | Output Low Voltage             | 1.25    | V    |

| V <sub>OD</sub>   | Output Differential Voltage    | 0.80    | V    |

| V <sub>CM</sub>   | Output Common Mode Voltage     | 1.65    | V    |

| ZBACK             | Back Impedance                 | 100.5   | Ω    |

| I <sub>DC</sub>   | DC Output Current              | 12.11   | mA   |

#### Table 3.16. LVPECL33 DC Conditions

Note: For input buffer, see LVDS Table 3.13 on page 55.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

| Demonstern                                                                                                                              | Description                            | Davies        | -         | -8         | -7   |       | -6   |       | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------|-----------|------------|------|-------|------|-------|------|

| Parameter                                                                                                                               | Description                            | Device        | Min       | Max        | Min  | Max   | Min  | Max   | Unit |

| f <sub>data_ddr2</sub><br>f <sub>data_ddr3</sub><br>f <sub>data_ddr3</sub><br>f <sub>data_lpddr2</sub><br>f <sub>data_lpddr3</sub>      | DDR Memory Data Rate                   | All Devices   | Ι         | 800        | _    | 700   | _    | 624   | Mb/s |

| fmax_ddr2<br>fmax_ddr3<br>fmax_ddr3l<br>fmax_lpddr2<br>fmax_lpddr3                                                                      | DDR Memory CLK<br>Frequency (ECLK)     | All Devices   | Ι         | 400        | _    | 350   | _    | 312   | MHz  |

| DDR2/DDR3/DDR                                                                                                                           | 3L/LPDDR2/LPDDR3 WRITE (DO             | Q Output Data | are Cente | ered to DC | QS)  |       |      |       |      |

| t <sub>dqvbs_ddr2</sub><br>t <sub>dqvbs_ddr3</sub><br>t <sub>dqvbs_ddr3</sub><br>t <sub>dqvbs_lpddr2</sub><br>t <sub>dqvbs_lpddr3</sub> | Data Output Valid before<br>DQS Output | All Devices   | _         | -0.25      | _    | -0.25 | _    | -0.25 | UI   |

| tdqvas_ddr2<br>tdqvas_ddr3<br>tdqvas_ddr3l<br>tdqvas_lpddr2<br>tdqvas_lpddr2<br>tdqvas_lpddr3                                           | Data Output Valid after DQS<br>Output  | All Devices   | 0.25      | _          | 0.25 | _     | 0.25 | _     | UI   |

| fdata_ddr2<br>fdata_ddr3<br>fdata_ddr3l<br>fdata_lpddr2<br>fdata_lpddr3                                                                 | DDR Memory Data Rate                   | All Devices   | _         | 800        | _    | 700   | _    | 624   | Mb/s |

| f <sub>MAX_DDR2</sub><br>f <sub>MAX_DDR3</sub><br>f <sub>MAX_DDR3L</sub><br>f <sub>MAX_LPDDR2</sub><br>f <sub>MAX_LPDDR3</sub>          | DDR Memory CLK<br>Frequency (ECLK)     | All Devices   | _         | 400        | _    | 350   | _    | 312   | MHz  |

Notes:

1. Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from the Diamond software.

General I/O timing numbers are based on LVCMOS 2.5, 12 mA, Fast Slew Rate, 0pf load. Generic DDR timing are numbers based on LVDS I/O. DDR2 timing numbers are based on SSTL18. DDR3 timing numbers are based on SSTL15. LPDDR2 and LPDDR3 timing numbers are based on HSUL12.

- 3. Uses LVDS I/O standard for measurements.

- 4. Maximum clock frequencies are tested under best case conditions. System performance may vary upon the user environment.

- 5. All numbers are generated with the Diamond software.

FPGA-DS-02012-1.9

## 3.19. sysCLOCK PLL Timing

Over recommended operating conditions.

| Parameter                      | Descriptions                                                         | Conditions                 | Min   | Max   | Units      |

|--------------------------------|----------------------------------------------------------------------|----------------------------|-------|-------|------------|

| f <sub>IN</sub>                | Input Clock Frequency (CLKI, CLKFB)                                  | _                          | 8     | 400   | MHz        |

| f <sub>out</sub>               | Output Clock Frequency (CLKOP, CLKOS)                                | _                          | 3.125 | 400   | MHz        |

| f <sub>vco</sub>               | PLL VCO Frequency                                                    | _                          | 400   | 800   | MHz        |

| $f_{\text{PFD}}{}^3$           | Phase Detector Input Frequency                                       | —                          | 10    | 400   | MHz        |

| AC Characteris                 | tics                                                                 |                            |       |       |            |

| t <sub>DT</sub>                | Output Clock Duty Cycle                                              | _                          | 45    | 55    | %          |

| t <sub>PH4</sub>               | Output Phase Accuracy                                                | _                          | -5    | 5     | %          |

|                                |                                                                      | f <sub>o∪T</sub> ≥ 100 MHz | _     | 100   | ps p-p     |

|                                | Output Clock Period Jitter                                           | f <sub>оυт</sub> < 100 MHz | _     | 0.025 | UIPP       |

|                                |                                                                      | f <sub>o∪τ</sub> ≥ 100 MHz | _     | 200   | ps p-p     |

| t <sub>opjit</sub> 1           | Output Clock Cycle-to-Cycle Jitter                                   | f <sub>оυт</sub> < 100 MHz | _     | 0.050 | UIPP       |

|                                | Output Clock Phase Jitter                                            | f <sub>PFD</sub> ≥ 100 MHz | _     | 200   | ps p-p     |

|                                |                                                                      | f <sub>PFD</sub> < 100 MHz | _     | 0.011 | UIPP       |

| t <sub>spo</sub>               | Static Phase Offset                                                  | Divider ratio =<br>integer | _     | 400   | ps p-p     |

| t <sub>w</sub>                 | Output Clock Pulse Width                                             | At 90% or 10%              | 0.9   | _     | ns         |

| t <sub>LOCK</sub> <sup>2</sup> | PLL Lock-in Time                                                     | _                          | _     | 15    | ms         |

| t <sub>UNLOCK</sub>            | PLL Unlock Time                                                      | _                          | _     | 50    | ns         |

|                                |                                                                      | f <sub>PFD</sub> ≥ 20 MHz  | _     | 1,000 | ps p-p     |

| t <sub>IPJIT</sub>             | Input Clock Period Jitter                                            | f <sub>PFD</sub> < 20 MHz  | _     | 0.02  | UIPP       |

| t <sub>HI</sub>                | Input Clock High Time                                                | 90% to 90%                 | 0.5   | _     | ns         |

| t <sub>LO</sub>                | Input Clock Low Time                                                 | 10% to 10%                 | 0.5   | _     | ns         |

| t <sub>rst</sub>               | RST/ Pulse Width                                                     | —                          | 1     | _     | ms         |

| t <sub>rstrec</sub>            | RST Recovery Time                                                    | _                          | 1     | -     | ns         |

| t <sub>load_reg</sub>          | Min Pulse for CIB_LOAD_REG                                           | _                          | 10    | _     | ns         |

| t <sub>rotate-setup</sub>      | Min time for CIB dynamic phase controls to be stable fore CIB_ROTATE | _                          | 5     | -     | ns         |

| t <sub>rotate-wd</sub>         | Min pulse width for CIB_ROTATE to maintain "0" or                    | _                          | 4     | -     | VCO cycles |

Notes:

1. Jitter sample is taken over 10,000 samples for Periodic jitter, and 2,000 samples for Cycle-to-Cycle jitter of the primary PLL output with clean reference clock with no additional I/O toggling.

2. Output clock is valid after  $t_{LOCK}$  for PLL reset and dynamic delay adjustment.

3. Period jitter and cycle-to-cycle jitter numbers are guaranteed for  $f_{PFD} > 10$  MHz. For  $f_{PFD} < 10$  MHz, the jitter numbers may not be met in certain conditions.

## 3.22. SERDES High-Speed Data Receiver

### Table 3.27. Serial Input Data Specifications

| Symbol                  | Description                                                     | Min  | Тур       | Max                                | Unit    |

|-------------------------|-----------------------------------------------------------------|------|-----------|------------------------------------|---------|

| V <sub>RX-DIFF-S</sub>  | Differential input sensitivity                                  | 150  | -         | 1760                               | mV, p-p |

| V <sub>RX-IN</sub>      | Input levels                                                    | 0    | -         | V <sub>CCA</sub> +0.5 <sup>2</sup> | V       |

| V <sub>RX-CM-DCCM</sub> | Input common mode range (internal DC coupled mode)              | 0.6  | _         | V <sub>CCA</sub>                   | V       |

| V <sub>RX-CM-ACCM</sub> | Input common mode range (internal AC coupled mode) <sup>2</sup> | 0.1  | _         | V <sub>CCA</sub> +0.2              | V       |

| T <sub>RX-RELOCK</sub>  | SCDR re-lock time <sup>1</sup>                                  | _    | 1000      | _                                  | Bits    |

| Z <sub>RX-TERM</sub>    | Input termination 50/75 $\Omega$ /High Z                        | -20% | 50/75/5 K | +20%                               | Ω       |

| RL <sub>RX-RL</sub>     | Return loss (without package)                                   | —    | _         | -10                                | dB      |

Notes:

1. This is the typical number of bit times to re-lock to a new phase or frequency within ±300 ppm, assuming 8b10b encoded data.

2. Up to 1.655 for ECP5, and 1.76 for ECP5-5G.

## 3.23. Input Data Jitter Tolerance

A receiver's ability to tolerate incoming signal jitter is very dependent on jitter type. High speed serial interface standards have recognized the dependency on jitter type and have specifications to indicate tolerance levels for different jitter types as they relate to specific protocols. Sinusoidal jitter is considered to be a worst case jitter type.

| Description   | Frequency  | Condition               | Min | Тур | Max  | Unit            |

|---------------|------------|-------------------------|-----|-----|------|-----------------|

| Deterministic |            | 400 mV differential eye | —   | —   | TBD  | UI, p-p         |

| Random        | 5 Gb/s     | 400 mV differential eye | —   | _   | TBD  | UI <i>,</i> p-p |

| Total         |            | 400 mV differential eye | —   | —   | TBD  | UI, p-p         |

| Deterministic |            | 400 mV differential eye | —   | —   | 0.37 | UI, p-p         |

| Random        | 3.125 Gb/s | 400 mV differential eye | —   | _   | 0.18 | UI <i>,</i> p-p |

| Total         |            | 400 mV differential eye | —   | —   | 0.65 | UI, p-p         |

| Deterministic |            | 400 mV differential eye | —   | —   | 0.37 | UI <i>,</i> p-p |

| Random        | 2.5 Gb/s   | 400 mV differential eye | —   | —   | 0.18 | UI, p-p         |

| Total         |            | 400 mV differential eye | —   | _   | 0.65 | UI <i>,</i> p-p |

| Deterministic |            | 400 mV differential eye | —   | —   | 0.37 | UI <i>,</i> p-p |

| Random        | 1.25 Gb/s  | 400 mV differential eye | —   | _   | 0.18 | UI <i>,</i> p-p |

| Total         |            | 400 mV differential eye | _   | _   | 0.65 | UI, p-p         |

#### Table 3.28. Receiver Total Jitter Tolerance Specification

Notes:

1. Jitter tolerance measurements are done with protocol compliance tests: 3.125 Gb/s - XAUI Standard, 2.5 Gb/s - PCIe Standard, 1.25 Gb/s - SGMII Standard.

2. For ECP5-5G family devices only.

## 3.27. XAUI/CPRI LV E.30 Electrical and Timing Characteristics

### 3.27.1. AC and DC Characteristics

Over recommended operating conditions.

### Table 3.33. Transmit

| Symbol                                | Description                      | Test Conditions | Min | Тур | Max  | Unit |

|---------------------------------------|----------------------------------|-----------------|-----|-----|------|------|

| T <sub>RF</sub>                       | Differential rise/fall time      | 20% to 80%      | —   | 80  | -    | ps   |

| Z <sub>TX_DIFF_DC</sub>               | Differential impedance           | —               | 80  | 100 | 120  | Ω    |

| J <sub>TX_DDJ</sub> <sup>2, 3</sup>   | Output data deterministic jitter | —               | —   | —   | 0.17 | UI   |

| J <sub>TX_TJ</sub> <sup>1, 2, 3</sup> | Total output data jitter         | —               | _   | —   | 0.35 | UI   |

Notes:

- 1. Total jitter includes both deterministic jitter and random jitter.

- 2. Jitter values are measured with each CML output AC coupled into a 50  $\Omega$  impedance (100  $\Omega$  differential impedance).

- 3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

Over recommended operating conditions.

#### Table 3.34. Receive and Jitter Tolerance

| Symbol                                | Description                                   | Test Conditions | Min  | Тур | Max  | Unit |  |

|---------------------------------------|-----------------------------------------------|-----------------|------|-----|------|------|--|

| Ы                                     | Differential return loss                      | From 100 MHz    | 10   | _   | _    | dB   |  |

| RL <sub>RX_DIFF</sub>                 | Differential return loss                      | to 3.125 GHz    | 10   |     |      | ив   |  |

| Ы                                     | Common mode return loss                       | From 100 MHz    | 6    |     |      | dB   |  |

| RL <sub>RX_CM</sub>                   | Common mode return loss                       | to 3.125 GHz    | 0    | _   | _    | uв   |  |

| Z <sub>RX_DIFF</sub>                  | Differential termination resistance           | -               | 80   | 100 | 120  | Ω    |  |

| J <sub>RX_DJ</sub> <sup>1, 2, 3</sup> | Deterministic jitter tolerance (peak-to-peak) | -               | _    | —   | 0.37 | UI   |  |

| J <sub>RX_RJ</sub> <sup>1, 2, 3</sup> | Random jitter tolerance (peak-to-peak)        | —               | _    | _   | 0.18 | UI   |  |

| J <sub>RX_SJ</sub> <sup>1, 2, 3</sup> | Sinusoidal jitter tolerance (peak-to-peak)    | _               | _    | _   | 0.10 | UI   |  |

| J <sub>RX_TJ</sub> <sup>1, 2, 3</sup> | Total jitter tolerance (peak-to-peak)         | _               | —    | _   | 0.65 | UI   |  |

| T <sub>RX_EYE</sub>                   | Receiver eye opening                          | _               | 0.35 | _   | _    | UI   |  |

Notes:

1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter.

2. Jitter values are measured with each high-speed input AC coupled into a 50  $\Omega$  impedance.

3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

## 3.28. CPRI LV E.24/SGMII(2.5Gbps) Electrical and Timing Characteristics

### 3.28.1. AC and DC Characteristics

#### Table 3.35. Transmit

| Symbol                                | Description                      | Test Conditions | Min | Тур | Max  | Unit |

|---------------------------------------|----------------------------------|-----------------|-----|-----|------|------|

| T <sub>RF</sub> <sup>1</sup>          | Differential rise/fall time      | 20% to 80%      | _   | 80  | —    | ps   |

| Z <sub>TX_DIFF_DC</sub>               | Differential impedance           | _               | 80  | 100 | 120  | Ω    |

| J <sub>TX_DDJ</sub> <sup>3, 4</sup>   | Output data deterministic jitter | —               | -   | _   | 0.17 | UI   |

| J <sub>TX_TJ</sub> <sup>2, 3, 4</sup> | Total output data jitter         | _               | _   | —   | 0.35 | UI   |

Notes:

1. Rise and Fall times measured with board trace, connector and approximately 2.5 pf load.

- 2. Total jitter includes both deterministic jitter and random jitter. The random jitter is the total jitter minus the actual deterministic jitter.

- 3. Jitter values are measured with each CML output AC coupled into a 50  $\Omega$  impedance (100  $\Omega$  differential impedance).

- 4. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

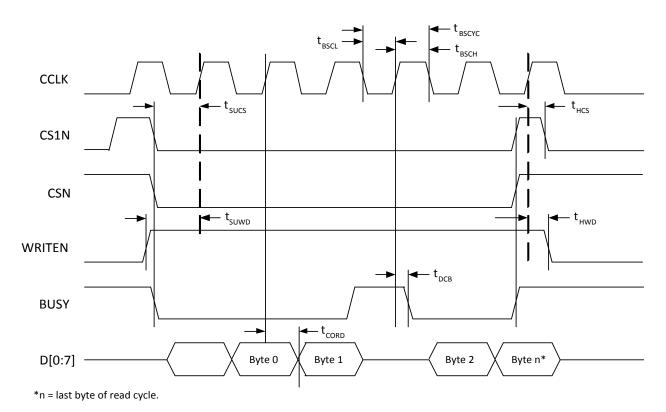

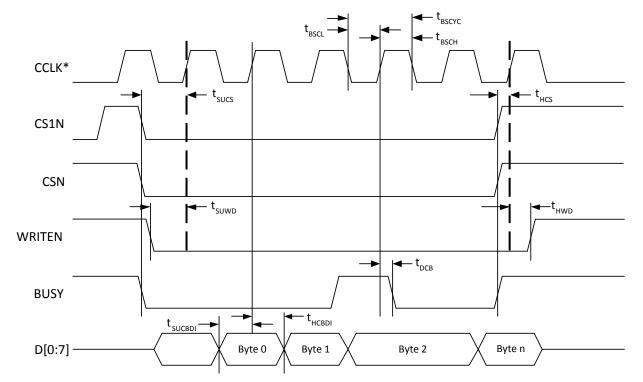

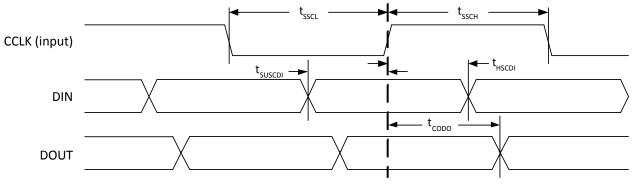

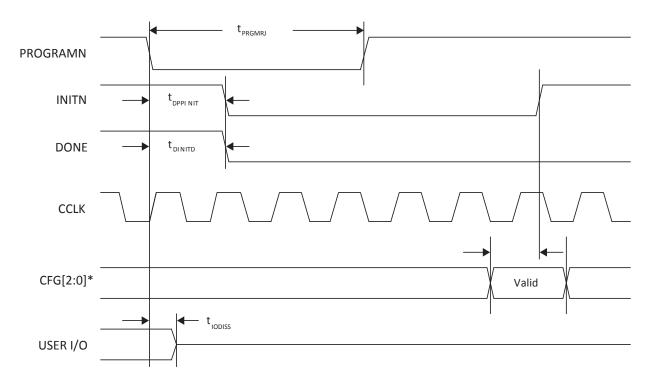

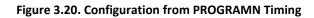

### Table 3.42. ECP5/ECP5-5G sysCONFIG Port Timing Specifications (Continued)

| Symbol              | Parameter                        |   | Min | Max | Unit |  |  |

|---------------------|----------------------------------|---|-----|-----|------|--|--|

| Slave Para          | Slave Parallel                   |   |     |     |      |  |  |

| f <sub>cclк</sub>   | CCLK input clock frequency       | — | —   | 50  | MHz  |  |  |

| t <sub>BSCH</sub>   | CCLK input clock pulsewidth HIGH | — | 6   | _   | ns   |  |  |

| t <sub>BSCL</sub>   | CCLK input clock pulsewidth LOW  | — | 6   | _   | ns   |  |  |

| t <sub>CORD</sub>   | CCLK to DOUT for Read Data       | — | —   | 12  | ns   |  |  |

| t <sub>sucbdi</sub> | Data Setup Time to CCLK          | — | 1.5 | _   | ns   |  |  |

| t <sub>HCBDI</sub>  | Data Hold Time to CCLK           | — | 1.5 | _   | ns   |  |  |

| t <sub>sucs</sub>   | CSN, CSN1 Setup Time to CCLK     | — | 2.5 | _   | ns   |  |  |

| t <sub>HCS</sub>    | CSN, CSN1 Hold Time to CCLK      | — | 1.5 | _   | ns   |  |  |

| t <sub>suwd</sub>   | WRITEN Setup Time to CCLK        | — | 45  | _   | ns   |  |  |

| t <sub>HCWD</sub>   | WRITEN Hold Time to CCLK         | — | 2   | _   | ns   |  |  |

| t <sub>DCB</sub>    | CCLK to BUSY Delay Time          | — | _   | 12  | ns   |  |  |

Figure 3.15. sysCONFIG Parallel Port Read Cycle

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

\*In Master Parallel Mode the FPGA provides CCLK (MCLK). In Slave Parallel Mode the external device provides CCLK.

Figure 3.16. sysCONFIG Parallel Port Write Cycle

Figure 3.17. sysCONFIG Slave Serial Port Timing

\*The CFG pins are normally static (hardwired).

# 4. Pinout Information

## 4.1. Signal Descriptions

| Signal Name                     | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Purpose                 |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| P[L/R] [Group Number]_[A/B/C/D] | ı/o | [L/R] indicates the L (Left), or R (Right) edge of the device. [Group Number]<br>indicates the PIO [A/B/C/D] group.<br>[A/B/C/D] indicates the PIO within the PIC to which the pad is connected.<br>Some of these user-programmable pins are shared with special function pins.<br>These pins, when not used as special purpose pins, can be programmed as I/Os<br>for user logic. During configuration the user-programmable I/Os are tristated<br>with an internal pull-down resistor enabled. If any pin is not used (or not bonded<br>to a package pin), it is tristated and default to have pull-down enabled after<br>configuration.<br>PIO A and B are grouped as a pair, and PIO C and D are group as a pair. Each pair<br>supports true LVDS differential input buffer. Only PIO A and B pair supports true<br>LVDS differential output buffer.<br>Each A/B and C/D pair supports programmable on/off differential input<br>termination of 100 Ω. |

| P[T/B][Group Number]_[A/B]      | 1/0 | [T/B] indicates the T (top) or B (bottom) edge of the device. [Group Number]<br>indicates the PIO [A/B] group.<br>[A/B] indicates the PIO within the PIC to which the pad is connected. Some of<br>these user-programmable pins are shared with sysConfig pins. These pins, when<br>not used as configuration pins, can be programmed as I/Os for user logic. During<br>configuration, the pins not used in configuration are tristated with an internal<br>pull-down resistor enabled. If any pin is not used (or not bonded to a package<br>pin), it is tristated and default to have pull-down enabled after configuration.<br>PIOs on top and bottom do not support differential input signaling or true LVDS<br>output signaling, but it can support emulated differential output buffer.<br>PIO A/B forms a pair of emulated differential output buffer.                                                                                             |

| GSRN                            | 1   | Global RESET signal (active low). Any I/O pin can be GSRN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| NC                              | _   | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RESERVED                        | _   | This pin is reserved and should not be connected to anything on the board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| GND                             | _   | Ground. Dedicated pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| V <sub>cc</sub>                 | -   | Power supply pins for core logic. Dedicated pins. V <sub>CC</sub> = 1.1 V (ECP5), 1.2 V (ECP5UM5G)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>CCAUX</sub>              | _   | Auxiliary power supply pin. This dedicated pin powers all the differential and referenced input buffers. $V_{CCAUX} = 2.5 V$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>CCIOx</sub>              | _   | Dedicated power supply pins for I/O bank x. $V_{\text{CCIO8}}$ is used for configuration and JTAG.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VREF1_x                         | _   | Reference supply pins for I/O bank x. Pre-determined shared pin in each bank are assigned as VREF1 input. When not used, they may be used as I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PLL, DLL and Clock Functions    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| [LOC][_GPLL[T, C]_IN            | I   | General Purpose PLL (GPLL) input pads: [LOC] = ULC, LLC, URC and LRC, T = true and C = complement. These pins are shared I/O pins. When not configured as GPLL input pads, they can be used as general purpose I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| GR_PCLK[Bank][num]              | I   | General Routing Signals in Banks 0, 1, 2, 3, 4, 6 and 7. There are two in each bank ([num] = 0, 1). Refer to ECP5 sysClock PLL/DLL Design and Usage Guide (TN1263). These pins are shared I/O pins. When not configured as GR pins, they can be used as general purpose I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PCLK[T/C][Bank]_[num]           | I/O | General Purpose Primary CLK pads: [T/C] = True/Complement, [Bank] = (0, 1, 2, 3, 6 and 7). There are two in each bank ([num] = 0, 1). These are shared I/ O pins. When not configured as PCLK pins, they can be used as general purpose I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

### 4.3.2. LFE5U

| Pin Information<br>Summary             |        | L            | .FE5U-1       | 2            | L            | .FE5U-2       | 5            |              | LFE5          | U-45         |              |              | LFE5U-85     |              |             |  |

|----------------------------------------|--------|--------------|---------------|--------------|--------------|---------------|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|-------------|--|

| Pin Type                               |        | 256<br>caBGA | 285<br>csfBGA | 381<br>caBGA | 256<br>caBGA | 285<br>csfBGA | 381<br>caBGA | 256<br>caBGA | 285<br>csfBGA | 381<br>caBGA | 554<br>caBGA | 285<br>csfBG | 381<br>caBGA | 554<br>caBGA | 756<br>caBG |  |

|                                        | Bank 0 | 24           | 6             | 24           | 24           | 6             | 24           | 24           | 6             | 27           | 32           | 6            | 27           | 32           | 56          |  |

|                                        | Bank 1 | 32           | 6             | 32           | 32           | 6             | 32           | 32           | 6             | 33           | 40           | 6            | 33           | 40           | 48          |  |

| General                                | Bank 2 | 32           | 21            | 32           | 32           | 21            | 32           | 32           | 21            | 32           | 32           | 21           | 34           | 32           | 48          |  |

| Purpose                                | Bank 3 | 32           | 28            | 32           | 32           | 28            | 32           | 32           | 28            | 33           | 48           | 28           | 33           | 48           | 64          |  |

| Inputs/Outputs                         | Bank 4 | 0            | 0             | 0            | 0            | 0             | 0            | 0            | 0             | 0            | 0            | 0            | 0            | 14           | 24          |  |

| per Bank                               | Bank 6 | 32           | 26            | 32           | 32           | 26            | 32           | 32           | 26            | 33           | 48           | 26           | 33           | 48           | 64          |  |

|                                        | Bank 7 | 32           | 18            | 32           | 32           | 18            | 32           | 32           | 18            | 32           | 32           | 18           | 32           | 32           | 48          |  |

|                                        | Bank 8 | 13           | 13            | 13           | 13           | 13            | 13           | 13           | 13            | 13           | 13           | 13           | 13           | 13           | 13          |  |

| Total Single-Ende                      | d User | 197          | 118           | 197          | 197          | 118           | 197          | 197          | 118           | 203          | 245          | 118          | 205          | 259          | 365         |  |

| VCC                                    |        | 6            | 13            | 20           | 6            | 13            | 20           | 6            | 13            | 20           | 24           | 13           | 20           | 24           | 36          |  |

| VCCAUX (Core)                          |        | 2            | 3             | 4            | 2            | 3             | 4            | 2            | 3             | 4            | 9            | 3            | 4            | 9            | 8           |  |

|                                        | Bank 0 | 2            | 1             | 2            | 2            | 1             | 2            | 2            | 1             | 2            | 3            | 1            | 2            | 3            | 4           |  |

|                                        | Bank 1 | 2            | 1             | 2            | 2            | 1             | 2            | 2            | 1             | 2            | 3            | 1            | 2            | 3            | 4           |  |

|                                        | Bank 2 | 2            | 2             | 3            | 2            | 2             | 3            | 2            | 2             | 3            | 4            | 2            | 3            | 4            | 4           |  |

| VCCIO                                  | Bank 3 | 2            | 2             | 3            | 2            | 2             | 3            | 2            | 2             | 3            | 3            | 2            | 3            | 3            | 4           |  |

|                                        | Bank 4 | 0            | 0             | 0            | 0            | 0             | 0            | 0            | 0             | 0            | 0            | 0            | 0            | 2            | 2           |  |

|                                        | Bank 6 | 2            | 2             | 3            | 2            | 2             | 3            | 2            | 2             | 3            | 4            | 2            | 3            | 4            | 4           |  |

|                                        | Bank 7 | 2            | 2             | 3            | 2            | 2             | 3            | 2            | 2             | 3            | 3            | 2            | 3            | 3            | 4           |  |

|                                        | Bank 8 | 1            | 2             | 2            | 1            | 2             | 2            | 1            | 2             | 2            | 2            | 2            | 2            | 2            | 2           |  |

| ТАР                                    |        | 4            | 4             | 4            | 4            | 4             | 4            | 4            | 4             | 4            | 4            | 4            | 4            | 4            | 4           |  |

| Miscellaneous Dedicated                |        | 7            | 7             | 7            | 7            | 7             | 7            | 7            | 7             | 7            | 7            | 7            | 7            | 7            | 7           |  |

| GND                                    |        | 27           | 123           | 99           | 27           | 123           | 99           | 27           | 123           | 99           | 198          | 123          | 99           | 198          | 267         |  |

| NC                                     |        | 0            | 1             | 26           | 0            | 1             | 26           | 0            | 1             | 26           | 33           | 1            | 26           | 33           | 29          |  |

| Reserved                               |        | 0            | 4             | 6            | 0            | 4             | 6            | 0            | 4             | 6            | 12           | 4            | 6            | 12           | 12          |  |

| Total Balls                            |        | 256          | 285           | 381          | 256          | 285           | 381          | 256          | 285           | 381          | 554          | 285          | 381          | 554          | 756         |  |

|                                        |        | Bank         | 0             | 0            | 0            | 0             | 0            | 0            | 0             | 0            | 0            | 0            | 0            | 0            | 0           |  |

|                                        |        | Bank         | 0             | 0            | 0            | 0             | 0            | 0            | 0             | 0            | 0            | 0            | 0            | 0            | 0           |  |

|                                        |        | Bank         | 16/8          | 10/8         | 16/8         | 16/8          | 10/8         | 16/8         | 16/8          | 10/8         | 16/8         | 16/8         | 10/8         | 17/9         | 16/8        |  |

| High Speed Differ<br>Input / Output Pa |        | Bank<br>Bank | 16/8<br>0     | 14/7<br>0    | 16/8<br>0    | 16/8<br>0     | 14/7<br>0    | 16/8<br>0    | 16/8<br>0     | 14/7<br>0    | 16/8<br>0    | 24/12<br>0   | 14/7<br>0    | 16/8<br>0    | 24/1<br>0   |  |

|                                        | 111 3  | Bank         |               |              | -            | -             | -            | -            | -             | -            | -            | 24/12        | -            |              |             |  |

|                                        |        | Bank         | 16/8<br>16/8  | 13/6<br>8/6  | 16/8<br>16/8 | 16/8<br>16/8  | 13/6<br>8/6  | 16/8<br>16/8 | 16/8<br>16/8  | 13/6<br>8/6  | 16/8<br>16/8 | 16/8         | 13/6<br>8/6  | 16/8<br>16/8 | 24/1        |  |

|                                        |        | Bank         | 0             | 0            | 0            | 0             | 0            | 0            | 0             | 0            | 0            | 0            | 0            | 0            | 16/8<br>0   |  |

| Total High Speed                       |        | 64/32        | 45/27         | 64/32        | 64/32        | -             | 64/32        | 64/32        | -             | 64/32        | 80/40        | 45/27        | 65/33        | 80/40        | 112/        |  |

| Total High Speed                       |        | Bank         | 43/27         | 04/32        | 04/32        | 43/27         | 04/32        | 04/32        | 43/27         | 04/32        | 0            | 43/27        | 03/33        | 0            | 0           |  |

|                                        |        | Bank         | 0             | 0            | 0            | 0             | 0            | 0            | 0             | 0            | 0            | 0            | 0            | 0            | 0           |  |

|                                        |        | Bank         | 2             | 1            | 2            | 2             | 1            | 2            | 2             | 1            | 2            | 2            | 1            | 2            | 2           |  |

|                                        |        | Bank         | 2             | 2            | 2            | 2             | 2            | 2            | 2             | 2            | 2            | 3            | 2            | 2            | 3           |  |

| DQS Groups<br>(> 11 pins in grou       | (a     | Bank         | 0             | 0            | 0            | 0             | 0            | 0            | 0             | 0            | 0            | 0            | 0            | 0            | 0           |  |

| /. TT huis in Broahl                   |        | Bank         | 2             | 2            | 2            | 2             | 2            | 2            | 2             | 2            | 2            | 3            | 2            | 2            | 3           |  |

|                                        |        | Bank         | 2             | 1            | 2            | 2             | 1            | 2            | 2             | 1            | 2            | 2            | 1            | 2            | 2           |  |

|                                        |        | Bank         | 0             | 0            | 0            | 0             | 0            | 0            | 0             | 0            | 0            | 0            | 0            | 0            | 0           |  |

| Total DQS Groups                       |        | 8            | 6             | 8            | 8            | 6             | 8            | 8            | 6             | 8            | 10           | 6            | 8            | 10           | 14          |  |

### (Continued)

| Date        | Version | Section             | Change Summary                                                                                                                                                                                                                                                                                                     |

|-------------|---------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| August 2014 | 1.2     | All                 | Changed document status from Advance to Preliminary.                                                                                                                                                                                                                                                               |

|             |         | General Description | Updated Features section.                                                                                                                                                                                                                                                                                          |

|             |         |                     | Deleted Serial RapidIO protocol under Embedded SERDES.                                                                                                                                                                                                                                                             |

|             |         |                     | Corrected data rate under Pre-Engineered Source Synchronous                                                                                                                                                                                                                                                        |

|             |         |                     | Changed DD3. LPDDR3 to DDR2/3, LPDDR2/3.                                                                                                                                                                                                                                                                           |

|             |         |                     | Mentioned transmit de-emphasis "pre- and post-cursors".                                                                                                                                                                                                                                                            |

|             |         | Architecture        | Updated Overview section.                                                                                                                                                                                                                                                                                          |

|             |         |                     | Revised description of PFU blocks.                                                                                                                                                                                                                                                                                 |

|             |         |                     | <ul> <li>Specified SRAM cell settings in describing the control of<br/>SERDES/PCS duals.</li> </ul>                                                                                                                                                                                                                |

|             |         |                     | Updated SERDES and Physical Coding Sublayer section.                                                                                                                                                                                                                                                               |

|             |         |                     | Changed PCI Express 2.0 to PCI Express Gen1 and Gen2.                                                                                                                                                                                                                                                              |

|             |         |                     | Deleted Serial RapidIO protocol.                                                                                                                                                                                                                                                                                   |

|             |         |                     | <ul> <li>Updated Table 2.13. LFE5UM/LFE5UM5G SERDES Standard<br/>Support.</li> </ul>                                                                                                                                                                                                                               |

|             |         |                     | Updated On-Chip Oscillator section.                                                                                                                                                                                                                                                                                |

|             |         |                     | • Deleted "130 MHz ±15% CMOS" oscillator.                                                                                                                                                                                                                                                                          |

|             |         |                     | Updated Table 2.16. Selectable Master Clock (MCLK) Frequencies<br>during Configuration (Nominal)                                                                                                                                                                                                                   |

|             |         | DC and Switching    | Updated Absolute Maximum Ratings section. Added supply voltages                                                                                                                                                                                                                                                    |

|             |         | Characteristics     | V <sub>CCA</sub> and V <sub>CCAUXA</sub> .                                                                                                                                                                                                                                                                         |

|             |         |                     | Updated sysI/O Recommended Operating Conditions section. Revised<br>HSULD12D VCCIO values and removed table note.                                                                                                                                                                                                  |