Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                              |

|--------------------------------|------------------------------------------------------------------------------|

| Product Status                 | Active                                                                       |

| Number of LABs/CLBs            | 3000                                                                         |

| Number of Logic Elements/Cells | 12000                                                                        |

| Total RAM Bits                 | 589824                                                                       |

| Number of I/O                  | 197                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.045V ~ 1.155V                                                              |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                           |

| Package / Case                 | 381-FBGA                                                                     |

| Supplier Device Package        | 381-CABGA (17x17)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe5u-12f-8bg381i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Copyright Notice**

Copyright © 2014-2018 Lattice Semiconductor Corporation. All rights reserved. The contents of these materials contain proprietary and confidential information (including trade secrets, copyright, and other Intellectual Property interests) of Lattice Semiconductor Corporation and/or its affiliates. All rights are reserved. You are permitted to use this document and any information contained therein expressly and only for bona fide non-commercial evaluation of products and/or services from Lattice Semiconductor Corporation or its affiliates; and only in connection with your bona fide consideration of purchase or license of products or services from Lattice Semiconductor Corporation or its affiliates, and only in accordance with the terms and conditions stipulated. Contents, (in whole or in part) may not be reproduced, downloaded, disseminated, published, or transferred in any form or by any means, except with the prior written permission of Lattice Semiconductor Corporation and/or its affiliates. Copyright infringement is a violation of federal law subject to criminal and civil penalties. You have no right to copy, modify, create derivative works of, transfer, sublicense, publicly display, distribute or otherwise make these materials available, in whole or in part, to any third party. You are not permitted to reverse engineer, disassemble, or decompile any device or object code provided herewith. Lattice Semiconductor Corporation proprietary materials and/or data.

#### Patents

The subject matter described herein may contain one or more inventions claimed in patents or patents pending owned by Lattice Semiconductor Corporation and/or its affiliates.

### **Trademark Acknowledgment**

Lattice Semiconductor Corporation®, the Lattice Semiconductor logo, Silicon Image®, the Silicon Image logo, Instaport®, the Instaport logo, InstaPrevue®, Simplay®, Simplay HD®, the Simplay HD logo, Simplay Labs™, the Simplay Labs logo, the SiBEAM Snap™, the SiBEAM Snap logo, UltraGig™, the UltraGig logo are trademarks or registered trademarks of Lattice Semiconductor Corporation in the United States and/or other countries. HDMI® and the HDMI logo with High-Definition Multimedia Interface are trademarks or registered trademarks of, and are used under license from, HDMI Licensing, LLC. in the United States or other countries. MHL® and the MHL logo with Mobile High-Definition Link are trademarks or registered trademarks of, and are used under license from, MHL, LLC. in the United States and/or other countries. WirelessHD logo, WiHD® and the WiHD logo are trademarks, registered trademarks or service marks of SiBeam, Inc. in the United States or other countries. HDMI Licensing, LLC; Simplay Labs, LLC; and SiBeam, Inc. are wholly owned subsidiaries of Lattice Semiconductor Corporation.

All other trademarks and registered trademarks are the property of their respective owners in the United States or other countries. The absence of a trademark symbol does not constitute a waiver of Lattice Semiconductor's trademarks or other intellectual property rights with regard to a product name, logo or slogan.

#### **Export Controlled Document**

This document contains materials that are subject to the U.S. Export Administration Regulations and may also be subject to additional export control laws and regulations (collectively "Export Laws") and may be used only in compliance with such Export Laws. Unless otherwise authorized by an officer of Lattice Semiconductor Corporation in writing, this document and the information contained herein (a) may not be used in relation to nuclear, biological or chemical weapons, or missiles capable of delivering these weapons, and (b) may not be re-exported or otherwise transferred to a third party who is known or suspected to be involved in relation to nuclear, biological or chemical weapons, or missiles capable of delivering these weapons, or to any sanctioned persons or entities.

## **Further Information**

To request other materials, documentation, and information, contact your local Lattice Semiconductor sales office or visit the Lattice Semiconductor web site at <a href="https://www.latticesemi.com">www.latticesemi.com</a>.

### **Disclaimers**

These materials are provided on an "AS IS" basis. Lattice Semiconductor Corporation and its affiliates disclaim all representations and warranties (express, implied, statutory or otherwise), including but not limited to: (i) all implied warranties of merchantability, fitness for a particular purpose, and/or non-infringement of third party rights; (ii) all warranties arising out of course-of-dealing, usage, and/or trade; and (iii) all warranties that the information or results provided in, or that may be obtained from use of, the materials are accurate, reliable, complete, up-to-date, or produce specific outcomes. Lattice Semiconductor Corporation and its affiliates assume no liability or responsibility for any errors or omissions in these materials, makes no commitment or warranty to correct any such errors or omissions or update or keep current the information contained in these materials, and expressly disclaims all direct, indirect, special, incidental, consequential, reliance and punitive damages, including WITHOUT LIMITATION any loss of profits arising out of your access to, use or interpretation of, or actions taken or not taken based on the content of these materials. Lattice Semiconductor Corporation and its affiliates reserve the right, without notice, to periodically modify the information in these materials, and to add to, delete, and/or change any of this information.

### **Products and Services**

The products and services described in these materials, and any other information, services, designs, know-how and/or products provided by Lattice Semiconductor Corporation and/or its affiliates are provided on "AS IS" basis, except to the extent that Lattice Semiconductor Corporation and/or its affiliates provides an applicable written limited warranty in its standard form license agreements, standard Terms and Conditions of Sale and Service or its other applicable standard form agreements, in which case such limited warranty shall apply and shall govern in lieu of all other warranties (express, statutory, or implied). EXCEPT FOR SUCH LIMITED WARRANTY, LATTICE SEMICONDUCTOR CORPORATION AND ITS AFFILIATES DISCLAIM ALL REPRESENTATIONS AND WARRANTIES (EXPRESS, IMPLIED, STATUTORY OR OTHERWISE), REGARDING THE INFORMATION, SERVICES, DESIGNS, KNOW-HOW AND PRODUCTS PROVIDED BY LATTICE SEMICONDUCTOR CORPORATION AND/OR ITS AFFILIATES, INCLUDING BUT NOT LIMITED TO, ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND/OR NON-INFRINGEMENT OF THIRD PARTY RIGHTS. YOU ACKNOWLEDGE AND AGREE THAT SUCH INFORMATION, SERVICES, DESIGNS, KNOW-HOW AND PRODUCTS HAVE NOT BEEN DESIGNED, TESTED, OR MANUFACTURED FOR USE OR RESALE IN SYSTEMS WHERE THE FAILURE, MALFUNCTION, OR ANY INACCURACY OF THESE ITEMS CARRIES A RISK OF DEATH OR SERIOUS BODILY INJURY, INCLUDING, BUT NOT LIMITED TO, USE IN NUCLEAR FACILITIES, AIRCRAFT NAVIGATION OR COMMUNICATION, EMERGENCY SYSTEMS, OR OTHER SYSTEMS WITH A SIMILAR DEGREE OF POTENTIAL HAZARD. NO PERSON IS AUTHORIZED TO MAKE ANY OTHER WARRANTY OR REPRESENTATION CONCERNING THE PERFORMANCE OF THE INFORMATION, PRODUCTS, KNOW-HOW, DESIGNS OR SERVICES OTHER THAN AS PROVIDED IN THESE TERMS AND CONDITIONS.

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym | Definition                                          |  |  |  |

|---------|-----------------------------------------------------|--|--|--|

| ALU     | Arithmetic Logic Unit                               |  |  |  |

| BGA     | Ball Grid Array                                     |  |  |  |

| CDR     | Clock and Data Recovery                             |  |  |  |

| CRC     | Cycle Redundancy Code                               |  |  |  |

| DCC     | Dynamic Clock Control                               |  |  |  |

| DCS     | Dynamic Clock Select                                |  |  |  |

| DDR     | Double Data Rate                                    |  |  |  |

| DLL     | Delay-Locked Loops                                  |  |  |  |

| DSP     | Digital Signal Processing                           |  |  |  |

| EBR     | Embedded Block RAM                                  |  |  |  |

| ECLK    | Edge Clock                                          |  |  |  |

| FFT     | Fast Fourier Transforms                             |  |  |  |

| FIFO    | First In First Out                                  |  |  |  |

| FIR     | Finite Impulse Response                             |  |  |  |

| LVCMOS  | Low-Voltage Complementary Metal Oxide Semiconductor |  |  |  |

| LVDS    | Low-Voltage Differential Signaling                  |  |  |  |

| LVPECL  | Low Voltage Positive Emitter Coupled Logic          |  |  |  |

| LVTTL   | Low Voltage Transistor-Transistor Logic             |  |  |  |

| LUT     | Look Up Table                                       |  |  |  |

| MLVDS   | Multipoint Low-Voltage Differential Signaling       |  |  |  |

| PCI     | Peripheral Component Interconnect                   |  |  |  |

| PCS     | Physical Coding Sublayer                            |  |  |  |

| PCLK    | Primary Clock                                       |  |  |  |

| PDPR    | Pseudo Dual Port RAM                                |  |  |  |

| PFU     | Programmable Functional Unit                        |  |  |  |

| PIC     | Programmable I/O Cells                              |  |  |  |

| PLL     | Phase-Locked Loops                                  |  |  |  |

| POR     | Power On Reset                                      |  |  |  |

| SCI     | SERDES Client Interface                             |  |  |  |

| SERDES  | Serializer/Deserializer                             |  |  |  |

| SEU     | Single Event Upset                                  |  |  |  |

| SLVS    | Scalable Low-Voltage Signaling                      |  |  |  |

| SPI     | Serial Peripheral Interface                         |  |  |  |

| SPR     | Single Port RAM                                     |  |  |  |

| SRAM    | Static Random-Access Memory                         |  |  |  |

|         |                                                     |  |  |  |

| TAP     | Test Access Port                                    |  |  |  |

## 2.5.1.2. Dynamic Clock Select

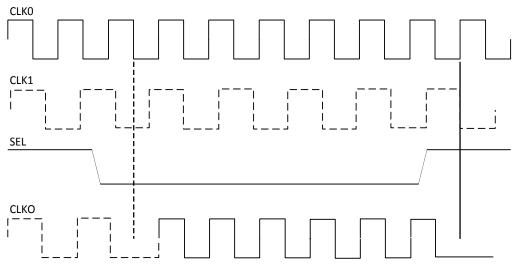

The Dynamic Clock Select (DCS) is a smart multiplexer function available in the primary clock routing. It switches between two independent input clock sources. Depending on the operation modes, it switches between two (2) independent input clock sources either with or without any glitches. This is achieved regardless of when the select signal is toggled. Both input clocks must be running to achieve functioning glitch-less DCS output clock, but it is not required running clocks when used as non-glitch-less normal clock multiplexer.

There are two DCS blocks per device that are fed to all quadrants. The inputs to the DCS block come from all the output of MIDMUXs and Clock from CIB located at the center of the PLC array core. The output of the DCS is connected to one of the inputs of Primary Clock Center MUX.

Figure 2.7 shows the timing waveforms of the default DCS operating mode. The DCS block can be programmed to other modes. For more information about the DCS, refer to ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263).

Figure 2.7. DCS Waveforms

# 2.5.2. Edge Clock

ECP5/ECP5-5G devices have a number of high-speed edge clocks that are intended for use with the PIOs in the implementation of high-speed interfaces. There are two ECLK networks per bank IO on the Left and Right sides of the devices.

Each Edge Clock can be sourced from the following:

- Dedicated Clock input pins (PCLK)

- DLLDEL output (Clock delayed by 90o)

- PLL outputs (CLKOP and CLKOS)

- ECLKBRIDGE

- Internal Nodes

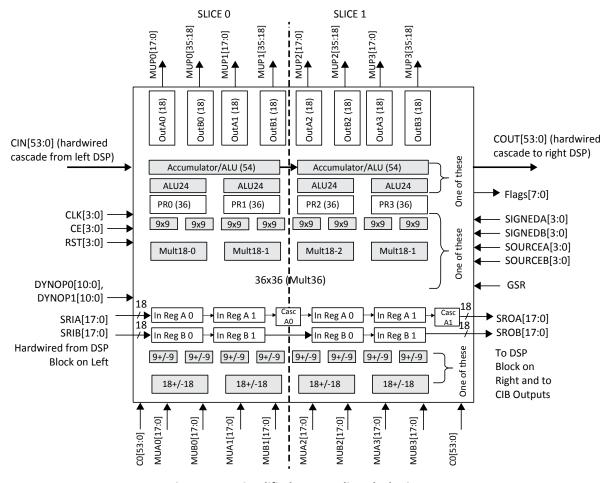

- 5\*5 and larger size 2D blocks Semi internal DSP Slice support

- Flexible saturation and rounding options to satisfy a diverse set of applications situations

- Flexible cascading across DSP slices

- Minimizes fabric use for common DSP and ALU functions

- Enables implementation of FIR Filter or similar structures using dedicated sysDSP slice resources only

- Provides matching pipeline registers

- Can be configured to continue cascading from one row of sysDSP slices to another for longer cascade chains

- Flexible and Powerful Arithmetic Logic Unit (ALU) Supports:

- Dynamically selectable ALU OPCODE

- Ternary arithmetic (addition/subtraction of three inputs)

- Bit-wise two-input logic operations (AND, OR, NAND, NOR, XOR and XNOR)

- Eight flexible and programmable ALU flags that can be used for multiple pattern detection scenarios, such as, overflow, underflow and convergent rounding.

- Flexible cascading across slices to get larger functions

- RTL Synthesis friendly synchronous reset on all registers, while still supporting asynchronous reset for legacy users

- Dynamic MUX selection to allow Time Division Multiplexing (TDM) of resources for applications that require processor-like flexibility that enables different functions for each clock cycle

For most cases, as shown in Figure 2.14, the ECP5/ECP5-5G sysDSP slice is backwards-compatible with the LatticeECP2™ and LatticeECP3™ sysDSP block, such that, legacy applications can be targeted to the ECP5/ ECP5-5G sysDSP slice. Figure 2.14 shows the diagram of sysDSP, and Figure 2.15 shows the detailed diagram.

Figure 2.14. Simplified sysDSP Slice Block Diagram

# 3.10. Supply Current (Standby)

Over recommended operating conditions.

Table 3.8. ECP5/ECP5-5G Supply Current (Standby)

| Symbol                         | Parameter                            | Device                                            | Typical | Unit |

|--------------------------------|--------------------------------------|---------------------------------------------------|---------|------|

|                                |                                      | LFE5U-12F/ LFE5U-25F/ LFE5UM-25F                  | 77      | mA   |

|                                |                                      | LFE5UM5G-25F                                      | 77      | mA   |

|                                | Cons Bourse Consult Consult          | LFE5U-45F/ LFE5UM-45F                             | 116     | mA   |

| I <sub>CC</sub>                | Core Power Supply Current            | LFE5UM5G-45F                                      | 116     | mA   |

|                                |                                      | LFE5U-85F/ LFE5UM-85F                             | 212     | mA   |

|                                |                                      | LFE5UM5G-85F                                      | 212     | mA   |

| I <sub>CCAUX</sub> Auxiliary P |                                      | LFE5U-12F/ LFE5U-25F/ LFE5UM-25F/<br>LFE5UM5G-25F | 16      | mA   |

|                                | Auxiliary Power Supply Current       | LFE5U-45F/ LFE5UM-45F/ LFE5UM5G-45F               | 17      | mA   |

|                                |                                      | LFE5U-85F/ LFE5UM-85F/ LFE5UM5G-85F               | 26      | mA   |

|                                |                                      | LFE5U-12F/ LFE5U-25F/ LFE5UM-25F/<br>LFE5UM5G-25F | 0.5     | mA   |

| I <sub>CCIO</sub>              | Bank Power Supply Current (Per Bank) | LFE5U-45F/ LFE5UM-45F/ LFE5UM5G-45F               | 0.5     | mA   |

|                                |                                      | LFE5U-85F/ LFE5UM-85F/ LFE5UM5G-85F               | 0.5     | mA   |

|                                |                                      | LFE5UM-25F                                        | 11      | mA   |

|                                |                                      | LFE5UM5G-25F                                      | 12      | mA   |

|                                | SERDES Power Supply Current (Per     | LFE5UM-45F                                        | 9.5     | mA   |

| I <sub>CCA</sub>               | Dual)                                | LFE5UM5G-45F                                      | 11      | mA   |

|                                |                                      | LFE5UM-85F                                        | 9.5     | mA   |

|                                |                                      | LFE5UM5G-85F                                      | 11      | mA   |

## Notes:

- For further information on supply current, see the list of technical documentation in Supplemental Information section on page 102.

- Assumes all outputs are tristated, all inputs are configured as LVCMOS and held at the V<sub>CCIO</sub> or GND.

- Frequency 0 Hz.

- Pattern represents a "blank" configuration data file.

- T<sub>J</sub> = 85 °C, power supplies at nominal voltage.

- To determine the ECP5/ECP5-5G peak start-up current, use the Power Calculator tool in the Lattice Diamond Design Software.

# 3.11. SERDES Power Supply Requirements<sup>1,2,3</sup>

Over recommended operating conditions.

Table 3.9. ECP5UM

| Symbol                             | Description                                              | Тур     | Max | Unit |

|------------------------------------|----------------------------------------------------------|---------|-----|------|

| Standby (Pov                       | ver Down)                                                | '       |     | ı.   |

| I <sub>CCA-SB</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 4       | 9.5 | mA   |

| I <sub>CCHRX-SB</sub> <sup>4</sup> | V <sub>CCHRX</sub> , Input Buffer Current (Per Channel)  | _       | 0.1 | mA   |

| I <sub>CCHTX-SB</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | _       | 0.9 | mA   |

| Operating (Da                      | ata Rate = 3.125 Gb/s)                                   |         |     |      |

| I <sub>CCA-OP</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 43      | 54  | mA   |

| I <sub>CCHRX-OP</sub> <sup>5</sup> | V <sub>CCHRX</sub> , Input Buffer Current (Per Channel)  | 0.4     | 0.5 | mA   |

| I <sub>CCHTX-OP</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | 10      | 13  | mA   |

| Operating (Da                      | ata Rate = 2.5 Gb/s)                                     |         |     |      |

| I <sub>CCA-OP</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 40      | 50  | mA   |

| I <sub>CCHRX-OP</sub> <sup>5</sup> | V <sub>CCHRX</sub> , Input Buffer Current (Per Channel)  | 0.4     | 0.5 | mA   |

| I <sub>CCHTX-OP</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | 10 13   |     | mA   |

| Operating (Da                      | ata Rate = 1.25 Gb/s)                                    |         |     |      |

| I <sub>CCA-OP</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 34      | 43  | mA   |

| I <sub>CCHRX-OP</sub> <sup>5</sup> | V <sub>CCHRX</sub> , Input Buffer Current (Per Channel)  | 0.4     | 0.5 | mA   |

| I <sub>CCHTX-OP</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | 10      | 13  | mA   |

| Operating (Da                      | ata Rate = 270 Mb/s)                                     | •       | •   | ,    |

| I <sub>CCA-OP</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 28      | 38  | mA   |

| I <sub>CCHRX-OP</sub> <sup>5</sup> | V <sub>CCHRX</sub> , Input Buffer Current (Per Channel)  | 0.4 0.5 |     | mA   |

| I <sub>CCHTX-OP</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | 8 10 mA |     |      |

## Notes:

- 1. Rx Equalization enabled, Tx De-emphasis (pre-cursor and post-cursor) disabled

- 2. Per Channel current is calculated with both channels on in a Dual, and divide current by two. If only one channel is on, current will be higher.

- 3. To calculate with Tx De-emphasis enabled, use the Diamond Power Calculator tool.

- 4. For Icchrx-sb, during Standby, input termination on Rx are disabled.

- 5. For Icchrx-op, during operational, the max specified when external AC coupling is used. If externally DC coupled, the power is based on current pulled down by external driver when the input is driven to LOW.

# 3.12. sysI/O Recommended Operating Conditions

Table 3.11. sysI/O Recommended Operating Conditions

| Standard                                             |       | V <sub>CCIO</sub> |       |       | V <sub>REF</sub> (V) |       |

|------------------------------------------------------|-------|-------------------|-------|-------|----------------------|-------|

| Standard                                             | Min   | Тур               | Max   | Min   | Тур                  | Max   |

| LVCMOS33 <sup>1</sup>                                | 3.135 | 3.3               | 3.465 | _     | _                    | _     |

| LVCMOS33D <sup>3</sup> Output                        | 3.135 | 3.3               | 3.465 | _     | _                    | _     |

| LVCMOS25 <sup>1</sup>                                | 2.375 | 2.5               | 2.625 | _     | _                    | _     |

| LVCMOS18                                             | 1.71  | 1.8               | 1.89  | _     | _                    | _     |

| LVCMOS15                                             | 1.425 | 1.5               | 1.575 | _     | _                    | _     |

| LVCMOS12 <sup>1</sup>                                | 1.14  | 1.2               | 1.26  | _     | _                    | _     |

| LVTTL33 <sup>1</sup>                                 | 3.135 | 3.3               | 3.465 | _     | _                    | _     |

| SSTL15_I, _II <sup>2</sup>                           | 1.43  | 1.5               | 1.57  | 0.68  | 0.75                 | 0.9   |

| SSTL18_I, _II <sup>2</sup>                           | 1.71  | 1.8               | 1.89  | 0.833 | 0.9                  | 0.969 |

| SSTL135_I, _II <sup>2</sup>                          | 1.28  | 1.35              | 1.42  | 0.6   | 0.675                | 0.75  |

| HSUL12 <sup>2</sup>                                  | 1.14  | 1.2               | 1.26  | 0.588 | 0.6                  | 0.612 |

| MIPI D-PHY LP Input <sup>3, 5</sup>                  | 1.425 | 1.5               | 1.575 | _     | _                    | _     |

| LVDS25 <sup>1, 3</sup> Output                        | 2.375 | 2.5               | 2.625 | _     | _                    | _     |

| subLVS <sup>3</sup> (Input only)                     | _     | _                 | _     | _     | _                    | _     |

| SLVS <sup>3</sup> (Input only)                       | _     | _                 | _     | _     | _                    | _     |

| LVDS25E <sup>3</sup> Output                          | 2.375 | 2.5               | 2.625 | _     | _                    | _     |

| MLVDS <sup>3</sup> Output                            | 2.375 | 2.5               | 2.625 | _     | _                    | _     |

| LVPECL33 <sup>1, 3</sup> Output                      | 3.135 | 3.3               | 3.465 | _     | _                    | _     |

| BLVDS25 <sup>1, 3</sup> Output                       | 2.375 | 2.5               | 2.625 | _     | _                    | _     |

| HSULD12D <sup>2, 3</sup>                             | 1.14  | 1.2               | 1.26  | _     | _                    |       |

| SSTL135D_I, II <sup>2,3</sup>                        | 1.28  | 1.35              | 1.42  | _     | _                    | _     |

| SSTL15D_I, II <sup>2, 3</sup>                        | 1.43  | 1.5               | 1.57  | _     | _                    | _     |

| SSTL18D_I <sup>1, 2, 3</sup> , II <sup>1, 2, 3</sup> | 1.71  | 1.8               | 1.89  | _     | _                    | _     |

# Notes:

- 1. For input voltage compatibility, refer to ECP5 and ECP5-5G sysIO Usage Guide (TN1262).

- 2.  $V_{REF}$  is required when using Differential SSTL and HSUL to interface to DDR/LPDDR memories.

- 3. These differential inputs use LVDS input comparator, which uses V<sub>CCAUX</sub> power

- 4. All differential inputs and LVDS25 output are supported in the Left and Right banks only. Refer to ECP5 and ECP5-5G sysIO Usage Guide (TN1262) for details.

- 5. MIPI D-PHY LP input can be implemented by powering VCCIO to 1.5V, and select MIPI LP primitive to meet MIPI Alliance spec on  $V_{IH}$  and  $V_{IL}$ . It can also be implemented as LVCMOS12 with VCCIO at 1.2V, which would meet  $V_{IH}/V_{IL}$  spec on LVCOM12.

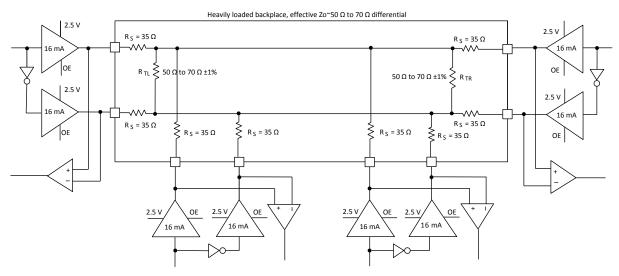

# 3.14.7. MLVDS25

The ECP5/ECP5-5G devices support the differential MLVDS standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The MLVDS input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3.4 is one possible solution for MLVDS standard implementation. Resistor values in the figure are industry standard values for 1% resistors.

Figure 3.4. MLVDS25 (Multipoint Low Voltage Differential Signaling)

Table 3.17. MLVDS25 DC Conditions

| Parameter         | Description                    | Тур     | Unit    |      |

|-------------------|--------------------------------|---------|---------|------|

| Parameter         | Description                    | Zo=50 Ω | Ζο=70 Ω | Onit |

| V <sub>CCIO</sub> | Output Driver Supply (±5%)     | 2.50    | 2.50    | V    |

| Z <sub>OUT</sub>  | Driver Impedance               | 10.00   | 10.00   | Ω    |

| R <sub>S</sub>    | Driver Series Resistor (±1%)   | 35.00   | 35.00   | Ω    |

| R <sub>TL</sub>   | Driver Parallel Resistor (±1%) | 50.00   | 70.00   | Ω    |

| R <sub>TR</sub>   | Receiver Termination (±1%)     | 50.00   | 70.00   | Ω    |

| V <sub>OH</sub>   | Output High Voltage            | 1.52    | 1.60    | V    |

| V <sub>OL</sub>   | Output Low Voltage             | 0.98    | 0.90    | V    |

| V <sub>OD</sub>   | Output Differential Voltage    |         | 0.70    | V    |

| V <sub>CM</sub>   | Output Common Mode Voltage     | 1.25    | 1.25    | V    |

| I <sub>DC</sub>   | DC Output Current              | 21.74   | 20.00   | mA   |

Note: For input buffer, see LVDS Table 3.13 on page 55.

**Table 3.22. ECP5/ECP5-5G External Switching Characteristics** (Continued)

| Table 3.22. ECP5/                                               | able 3.22. ECP5/ECP5-5G External Switching Characteristics (Continued) |                |            |           |            |           |            |            |                  |

|-----------------------------------------------------------------|------------------------------------------------------------------------|----------------|------------|-----------|------------|-----------|------------|------------|------------------|

| Parameter                                                       | Description                                                            | Device         | -8 -       |           | -7         |           | -6         | Unit       |                  |

| raiametei                                                       | Description                                                            | Device         | Min        | Max       | Min        | Max       | Min        | Max        | Oilit            |

| Generic DDR Outp                                                | ut                                                                     |                |            |           |            |           |            |            |                  |

| Generic DDRX1 Ou                                                | tputs With Clock and Data Cente                                        | red at Pin (GD | DRX1_TX    | .SCLK.Ce  | ntered) l  | Jsing PCL | K Clock Ir | put - Fig  | ure 3.6          |

| $t_{\text{DVB\_GDDRX1\_centered}}$                              | Data Output Valid before CLK<br>Output                                 | All Devices    | -0.67      | _         | -0.67      | _         | -0.67      | _          | ns +<br>1/2 UI   |

| t <sub>DVA_GDDRX1_centered</sub>                                | Data Output Valid after CLK Output                                     | All Devices    | -0.67      | _         | -0.67      | _         | -0.67      | _          | ns +<br>1/2 UI   |

| $f_{DATA\_GDDRX1\_centered}$                                    | GDDRX1 Data Rate                                                       | All Devices    | _          | 500       | _          | 500       | _          | 500        | Mb/s             |

| f <sub>MAX_GDDRX1_centered</sub>                                | GDDRX1 CLK Frequency (SCLK)                                            | All Devices    | _          | 250       | _          | 250       | _          | 250        | MHz              |

| Generic DDRX1 Ou                                                | tputs With Clock and Data Aligne                                       | ed at Pin (GDD | RX1_TX.    | CLK.Alig  | ned) Usin  | g PCLK C  | lock Inpu  | t - Figure | 3.9              |

| t <sub>DIB_GDDRX1_aligned</sub>                                 | Data Output Invalid before<br>CLK Output                               | All Devices    | -0.3       | _         | -0.3       | _         | -0.3       | _          | ns               |

| t <sub>DIA_GDDRX1_aligned</sub>                                 | Data Output Invalid after CLK Output                                   | All Devices    | 1          | 0.3       | _          | 0.3       | _          | 0.3        | ns               |

| $f_{DATA\_GDDRX1\_aligned}$                                     | GDDRX1 Data Rate                                                       | All Devices    | _          | 500       | _          | 500       | _          | 500        | Mb/s             |

| $f_{\text{MAX\_GDDRX1\_aligned}}$                               | GDDRX1 CLK Frequency (SCLK)                                            | All Devices    | _          | 250       | _          | 250       | _          | 250        | MHz              |

| Generic DDRX2 Ou                                                | tputs With Clock and Data Cente                                        | red at Pin (GD | DRX2_TX    | .ECLK.Ce  | ntered) l  | Jsing PCL | K Clock II | nput, Left | and              |

| Right sides Only -                                              | Figure 3.8                                                             |                |            |           |            |           |            |            |                  |

| $t_{\text{DVB\_GDDRX2\_centered}}$                              | Data Output Valid Before CLK<br>Output                                 | All Devices    | -<br>0.442 | _         | -0.56      | _         | -<br>0.676 | _          | ns +<br>1/2 UI   |

| $t_{DVA\_GDDRX2\_centered}$                                     | Data Output Valid After CLK<br>Output                                  | All Devices    | _          | 0.442     | _          | 0.56      | _          | 0.676      | ns +<br>1/2 UI   |

| $f_{DATA\_GDDRX2\_centered}$                                    | GDDRX2 Data Rate                                                       | All Devices    | _          | 800       | _          | 700       | _          | 624        | Mb/s             |

| f <sub>MAX_GDDRX2_centered</sub>                                | GDDRX2 CLK Frequency (ECLK)                                            | All Devices    | _          | 400       | _          | 350       | _          | 312        | MHz              |

|                                                                 | tputs With Clock and Data Aligne                                       | ed at Pin (GDD | RX2_TX.I   | CLK.Alig  | ned) Usin  | g PCLK C  | lock Inpu  | t, Left an | d Right          |

| sides Only - Figure                                             |                                                                        |                |            | 1         | I          | ı         | 1          | ı          | 1                |

| t <sub>DIB_GDDRX2_aligned</sub>                                 | Data Output Invalid before<br>CLK Output                               | All Devices    | -0.16      | _         | -0.18      | _         | -0.2       | _          | ns               |

| $t_{DIA\_GDDRX2\_aligned}$                                      | Data Output Invalid after CLK Output                                   | All Devices    | _          | 0.16      | _          | 0.18      | _          | 0.2        | ns               |

| $f_{DATA\_GDDRX2\_aligned}$                                     | GDDRX2 Data Rate                                                       | All Devices    | _          | 800       | _          | 700       | _          | 624        | Mb/s             |

| f <sub>MAX_GDDRX2_aligned</sub>                                 | GDDRX2 CLK Frequency (ECLK)                                            | All Devices    | _          | 400       | _          | 350       | _          | 312        | MHz              |

| Video DDRX71 Out                                                | tputs With Clock and Data Aligne                                       | d at Pin (GDDF | RX71_TX.   | ECLK) Usi | ing PLL Cl | ock Input | t, Left an | d Right si | des Only         |

| - Figure 3.12                                                   |                                                                        |                |            |           |            |           | ı          | ı          |                  |

| $t_{\text{DIB\_LVDS71\_i}}$                                     | Data Output Invalid before<br>CLK Output                               | All Devices    | -0.16      | _         | -0.18      | _         | -0.2       | _          | ns +<br>(i) * UI |

| $t_{DIA\_LVDS71\_i}$                                            | Data Output Invalid after CLK Output                                   | All Devices    | _          | 0.16      | _          | 0.18      | _          | 0.2        | ns +<br>(i) * UI |

| f <sub>DATA_LVDS71</sub>                                        | DDR71 Data Rate                                                        | All Devices    | _          | 756       | _          | 620       | _          | 525        | Mb/s             |

| f <sub>MAX LVDS71</sub>                                         | DDR71 CLK Frequency (ECLK)                                             | All Devices    | _          | 378       | _          | 310       | _          | 262.5      | MHz              |

| Memory Interface                                                |                                                                        |                |            |           |            |           |            |            |                  |

| DDR2/DDR3/LPDDR2/LPDDR3 READ (DQ Input Data are Aligned to DQS) |                                                                        |                |            |           |            |           |            |            |                  |

| t <sub>DVBDQ DDR2</sub>                                         |                                                                        |                | <u> </u>   | .,        |            |           |            |            |                  |

| t <sub>DVBDQ_DDR3</sub> t <sub>DVBDQ_DDR3L</sub>                | Data Output Valid before DQS                                           | All Devices    | _          | -0.26     | _          | _         | _          | _          | ns + 1/2         |

| t <sub>DVBDQ_LPDDR2</sub>                                       | Input                                                                  | 3003           |            |           |            | 0.317     |            | 0.374      | UI               |

| t <sub>DVADQ DDR2</sub>                                         |                                                                        |                |            |           |            |           |            |            |                  |

| t <sub>DVADQ_DDR3</sub>                                         | Data Output Valid after DOS                                            |                |            |           |            |           |            |            | nc   1/2         |

| t <sub>DVADQ_DDR3L</sub>                                        | Data Output Valid after DQS Input                                      | All Devices    | 0.26       | _         | 0.317      | _         | 0.374      | _          | ns + 1/2<br>UI   |

| t <sub>DVADQ_LPDDR2</sub>                                       | put                                                                    |                |            |           |            |           |            |            | 51               |

| t <sub>DVADQ_LPDDR3</sub>                                       |                                                                        | 1              |            |           |            |           |            |            |                  |

**Table 3.22. ECP5/ECP5-5G External Switching Characteristics** (Continued)

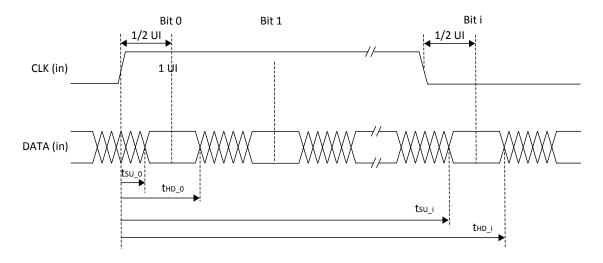

Figure 3.11. Receiver DDRX71\_RX Waveforms

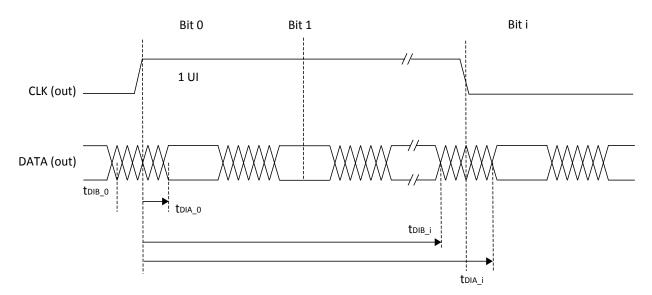

Figure 3.12. Transmitter DDRX71\_TX Waveforms

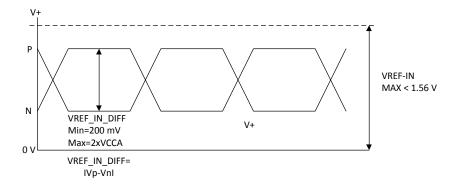

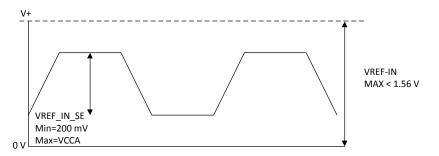

# 3.24. SERDES External Reference Clock

The external reference clock selection and its interface are a critical part of system applications for this product. Table 3.29 specifies reference clock requirements, over the full range of operating conditions.

Table 3.29. External Reference Clock Specification (refclkp/refclkn)

| Symbol                        | Description                                     | Min   | Тур            | Max                       | Unit                    |

|-------------------------------|-------------------------------------------------|-------|----------------|---------------------------|-------------------------|

| F <sub>REF</sub>              | Frequency range                                 | 50    | _              | 320                       | MHz                     |

| F <sub>REF-PPM</sub>          | Frequency tolerance <sup>1</sup>                | -1000 | _              | 1000                      | ppm                     |

| V <sub>REF-IN-SE</sub>        | Input swing, single-ended clock <sup>2, 4</sup> | 200   | _              | V <sub>CCAUXA</sub>       | mV, p-p                 |

| V <sub>REF-IN-DIFF</sub>      | Input swing, differential clock                 | 200   | 00 — 2*Vccauya |                           | mV, p-p<br>differential |

| $V_{REF-IN}$                  | Input levels                                    | 0     | _              | V <sub>CCAUXA</sub> + 0.4 | V                       |

| D <sub>REF</sub>              | Duty cycle <sup>3</sup>                         | 40    | _              | 60                        | %                       |

| T <sub>REF-R</sub>            | Rise time (20% to 80%)                          | 200   | 500            | 1000                      | ps                      |

| T <sub>REF-F</sub>            | Fall time (80% to 20%)                          | 200   | 500            | 1000                      | ps                      |

| Z <sub>REF-IN-TERM-DIFF</sub> | Differential input termination                  | -30%  | 100/HiZ        | +30%                      | Ω                       |

| C <sub>REF-IN-CAP</sub>       | Input capacitance                               | _     | _              | 7                         | pF                      |

#### Notes:

- Depending on the application, the PLL\_LOL\_SET and CDR\_LOL\_SET control registers may be adjusted for other tolerance values as described in ECP5 and ECP5-5G SERDES/PCS Usage Guide (TN1261).

- 2. The signal swing for a single-ended input clock must be as large as the p-p differential swing of a differential input clock to get the same gain at the input receiver. With single-ended clock, a reference voltage needs to be externally connected to CLKREFN pin, and the input voltage needs to be swung around this reference voltage.

- 3. Measured at 50% amplitude.

- Single-ended clocking is achieved by applying a reference voltage V<sub>REF</sub> on REFCLKN input, with the clock applied to REFCLKP input pin. V<sub>REF</sub> should be set to mid-point of the REFCLKP voltage swing.

Figure 3.14. SERDES External Reference Clock Waveforms

FPGA-DS-02012-1.9 75

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

# 3.27. XAUI/CPRI LV E.30 Electrical and Timing Characteristics

### 3.27.1. AC and DC Characteristics

Over recommended operating conditions.

### Table 3.33. Transmit

| Symbol                              | Description                      | Test Conditions | Min | Тур  | Max  | Unit |

|-------------------------------------|----------------------------------|-----------------|-----|------|------|------|

| $T_{RF}$                            | Differential rise/fall time      | 20% to 80%      | _   | 80   | 1    | ps   |

| Z <sub>TX_DIFF_DC</sub>             | Differential impedance           | _               | 80  | 100  | 120  | Ω    |

| J <sub>TX_DDJ</sub> <sup>2, 3</sup> | Output data deterministic jitter | 0.17            |     | 0.17 | UI   |      |

| J <sub>TX_TJ</sub> 1, 2, 3          | Total output data jitter         | _               | _   | -    | 0.35 | UI   |

### Notes:

- 1. Total jitter includes both deterministic jitter and random jitter.

- 2. Jitter values are measured with each CML output AC coupled into a 50  $\Omega$  impedance (100  $\Omega$  differential impedance).

- 3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

Over recommended operating conditions.

Table 3.34. Receive and Jitter Tolerance

| Symbol                     | Description                                   | Test Conditions              | Min  | Тур | Max  | Unit |

|----------------------------|-----------------------------------------------|------------------------------|------|-----|------|------|

| RL <sub>RX_DIFF</sub>      | Differential return loss                      | From 100 MHz<br>to 3.125 GHz | 10   | _   | _    | dB   |

| RL <sub>RX_CM</sub>        | Common mode return loss                       | From 100 MHz<br>to 3.125 GHz | 6    | _   | _    | dB   |

| Z <sub>RX_DIFF</sub>       | Differential termination resistance           | _                            | 80   | 100 | 120  | Ω    |

| J <sub>RX_DJ</sub> 1, 2, 3 | Deterministic jitter tolerance (peak-to-peak) | _                            | _    | _   | 0.37 | UI   |

| J <sub>RX_RJ</sub> 1, 2, 3 | Random jitter tolerance (peak-to-peak)        | _                            | _    | _   | 0.18 | UI   |

| J <sub>RX_SJ</sub> 1, 2, 3 | Sinusoidal jitter tolerance (peak-to-peak)    | _                            | _    | _   | 0.10 | UI   |

| J <sub>RX_TJ</sub> 1, 2, 3 | Total jitter tolerance (peak-to-peak)         | _                            | _    | _   | 0.65 | UI   |

| T <sub>RX_EYE</sub>        | Receiver eye opening                          | _                            | 0.35 | _   | _    | UI   |

### Notes:

- 1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter.

- 2. Jitter values are measured with each high-speed input AC coupled into a 50  $\Omega$  impedance.

- 3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

# 3.28. CPRI LV E.24/SGMII(2.5Gbps) Electrical and Timing Characteristics

# 3.28.1. AC and DC Characteristics

Table 3.35. Transmit

| Symbol                                | Description                      | Test Conditions | Min | Тур | Max  | Unit |

|---------------------------------------|----------------------------------|-----------------|-----|-----|------|------|

| T <sub>RF</sub> <sup>1</sup>          | Differential rise/fall time      | 20% to 80%      | 1   | 80  | -    | ps   |

| Z <sub>TX_DIFF_DC</sub>               | Differential impedance           | _               | 80  | 100 | 120  | Ω    |

| J <sub>TX_DDJ</sub> 3, 4              | Output data deterministic jitter | _               | -   | _   | 0.17 | UI   |

| J <sub>TX_TJ</sub> <sup>2, 3, 4</sup> | Total output data jitter         | _               | _   | _   | 0.35 | UI   |

### Notes:

- Rise and Fall times measured with board trace, connector and approximately 2.5 pf load.

- Total jitter includes both deterministic jitter and random jitter. The random jitter is the total jitter minus the actual deterministic jitter.

- 3. Jitter values are measured with each CML output AC coupled into a 50  $\Omega$  impedance (100  $\Omega$  differential impedance).

- 4. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

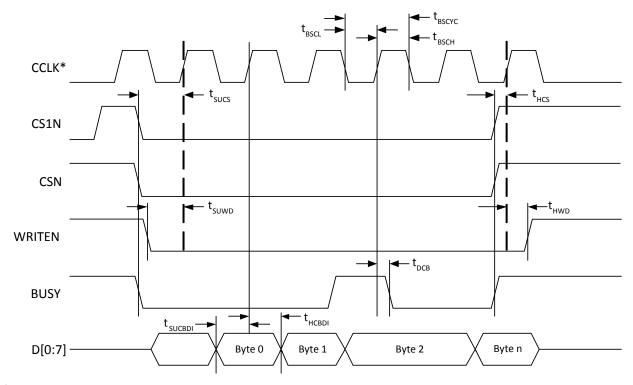

<sup>\*</sup>In Master Parallel Mode the FPGA provides CCLK (MCLK). In Slave Parallel Mode the external device provides CCLK.

Figure 3.16. sysCONFIG Parallel Port Write Cycle

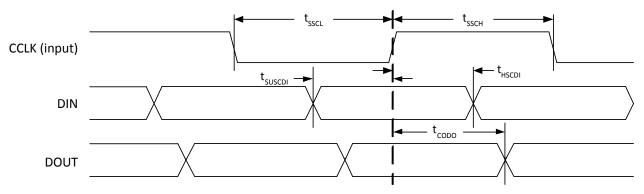

Figure 3.17. sysCONFIG Slave Serial Port Timing

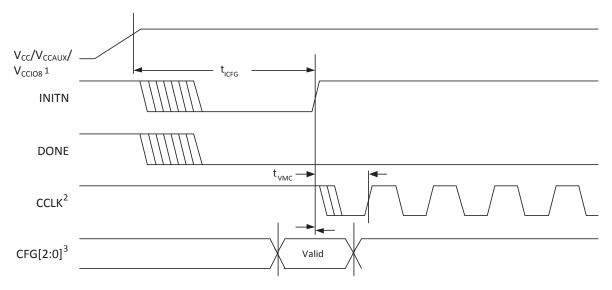

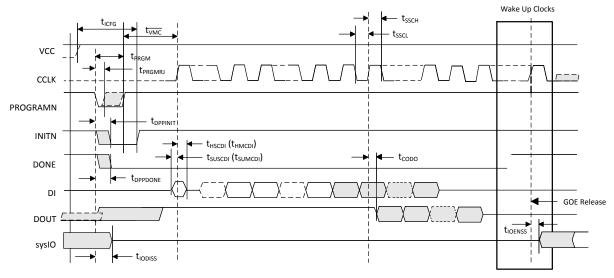

- 1. Time taken from  $V_{CC}$ ,  $V_{CCAUX}$  or  $V_{CCIO8}$ , whichever is the last to cross the POR trip point.

- 2. Device is in a Master Mode (SPI, SPIm).

- 3. The CFG pins are normally static (hardwired).

Figure 3.18. Power-On-Reset (POR) Timing

Figure 3.19. sysCONFIG Port Timing

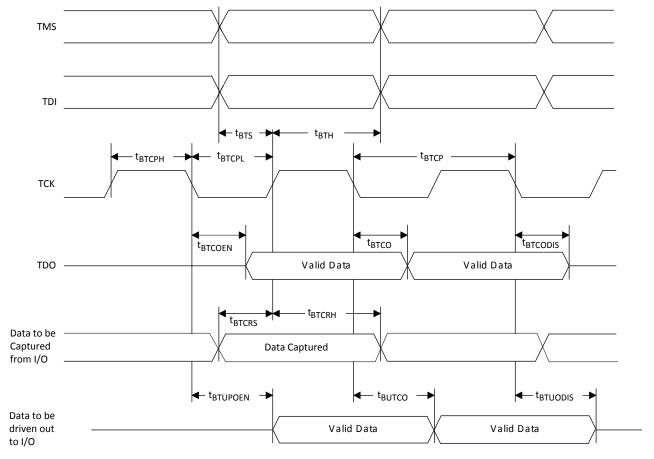

Figure 3.23. JTAG Port Timing Waveforms

# 3.33. Switching Test Conditions

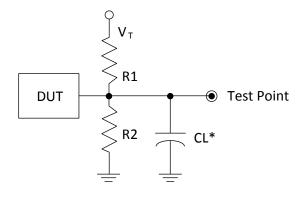

Figure 3.24 shows the output test load that is used for AC testing. The specific values for resistance, capacitance, voltage, and other test conditions are listed in Table 3.44.

\*CL Includes Test Fixture and Probe Capacitance

Figure 3.24. Output Test Load, LVTTL and LVCMOS Standards

| Signal Name                         | 1/0      | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL, DLL and Clock Functions (Conti | nued)    |                                                                                                                                                                                                                                                                                                                                                                                             |

| [L/R]DQS[group_num]                 | 1/0      | DQS input/output pads: T (top), R (right), group_ num = ball number associated with DQS[T] pin.                                                                                                                                                                                                                                                                                             |

| [T/R]]DQ[group_num]                 | 1/0      | DQ input/output pads: T (top), R (right), group_ num = ball number associated with DQS[T] pin.                                                                                                                                                                                                                                                                                              |

| Test and Programming (Dedicated     | Pins)    |                                                                                                                                                                                                                                                                                                                                                                                             |

| TMS                                 | I        | Test Mode Select input, used to control the 1149.1 state machine. Pull-up is enabled during configuration. This is a dedicated input pin.                                                                                                                                                                                                                                                   |

| тск                                 | I        | Test Clock input pin, used to clock the 1149.1 state machine. No pull-up enabled. This is a dedicated input pin.                                                                                                                                                                                                                                                                            |

| TDI                                 | I        | Test Data in pin. Used to load data into device using 1149.1 state machine. After power-up, this TAP port can be activated for configuration by sending appropriate command. (Note: once a configuration port is selected it is locked. Another configuration port cannot be selected until the power-up sequence). Pull-up is enabled during configuration. This is a dedicated input pin. |

| TDO                                 | 0        | Output pin. Test Data Out pin used to shift data out of a device using 1149.1. This is a dedicated output pin.                                                                                                                                                                                                                                                                              |

| Configuration Pads (Used during sy  | sCONFIG) |                                                                                                                                                                                                                                                                                                                                                                                             |

| CFG[2:0]                            | ı        | Mode pins used to specify configuration mode values latched on rising edge of INITN. During configuration, a pull-up is enabled. These are dedicated pins.                                                                                                                                                                                                                                  |

| INITN                               | I/O      | Open Drain pin. Indicates the FPGA is ready to be configured. During configuration, a pull-up is enabled.  This is a dedicated pin.                                                                                                                                                                                                                                                         |

| PROGRAMN                            | ı        | Initiates configuration sequence when asserted low. This pin always has an active pull-up. This is a dedicated pin.                                                                                                                                                                                                                                                                         |

| DONE                                | 1/0      | Open Drain pin. Indicates that the configuration sequence is complete, and the startup sequence is in progress.  This is a dedicated pin.                                                                                                                                                                                                                                                   |

| CCLK                                | 1/0      | Input Configuration Clock for configuring an FPGA in Slave SPI, Serial, and CPU modes. Output Configuration Clock for configuring an FPGA in Master configuration modes (Master SPI, Master Serial).  This is a dedicated pin.                                                                                                                                                              |

| HOLDN/DI/BUSY/CSSPIN/CEN            | I/O      | Parallel configuration mode busy indicator. SPI/SPIm mode data output.  This is a shared I/O pin. This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O pin.                                                                                                                                                                                           |

| CSN/SN                              | 1/0      | Parallel configuration mode active-low chip select. Slave SPI chip select. This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O pin.                                                                                                                                                                                                                  |

| CS1N                                | I        | Parallel configuration mode active-low chip select. This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O pin.                                                                                                                                                                                                                                         |

| WRITEN                              | ı        | Write enable for parallel configuration modes.  This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O pin.                                                                                                                                                                                                                                             |

| DOUT/CSON                           | 0        | Serial data output. Chip select output. SPI/SPIm mode chip select. This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O                                                                                                                                                                                                                               |

| D0/MOSI/IO0                         | 1/0      | Parallel configuration I/O. Open drain during configuration. When in SPI modes, it is an output in Master mode, and input in Slave mode.  This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O pin.                                                                                                                                                   |

| Pin Information Summary Pin Type        |          | LFE5UM/<br>LFE5UM5G-25 |              | LFE5UM/LFE5UM5G-45 |             |              | LFE5UM/LFE5UM5G-85 |             |              |              |

|-----------------------------------------|----------|------------------------|--------------|--------------------|-------------|--------------|--------------------|-------------|--------------|--------------|

|                                         |          | 285<br>csfBG           | 381<br>caBGA | 285<br>csfBGA      | 381<br>caBG | 554<br>caBGA | 285<br>csfBGA      | 381<br>caBG | 554<br>caBGA | 756<br>caBGA |

| TAP                                     |          | 4                      | 4            | 4                  | 4           | 4            | 4                  | 4           | 4            | 4            |

| Miscellaneous Dedicated Pins            |          | 7                      | 7            | 7                  | 7           | 7            | 7                  | 7           | 7            | 7            |

| GND                                     |          | 83                     | 59           | 83                 | 59          | 113          | 83                 | 59          | 113          | 166          |

| NC                                      |          | 1                      | 8            | 1                  | 2           | 33           | 1                  | 0           | 17           | 29           |

| Reserved                                |          | 0                      | 2            | 0                  | 2           | 4            | 0                  | 2           | 4            | 4            |

| SERDES                                  |          | 14                     | 28           | 14                 | 28          | 28           | 14                 | 28          | 28           | 28           |

| VCCV (CEDDEC)                           | VCCA0    | 2                      | 2            | 2                  | 2           | 6            | 2                  | 2           | 6            | 8            |

| VCCA (SERDES)                           | VCCA1    | 0                      | 2            | 0                  | 2           | 6            | 0                  | 2           | 6            | 9            |

| VCCALIV (CERDEC)                        | VCCAUXA0 | 2                      | 2            | 2                  | 2           | 2            | 2                  | 2           | 2            | 2            |

| VCCAUX (SERDES)                         | VCCAUXA1 | 0                      | 2            | 0                  | 2           | 2            | 0                  | 2           | 2            | 2            |

| GNDA (SERDES)                           |          | 26                     | 26           | 26                 | 26          | 49           | 26                 | 26          | 49           | 60           |

| Total Balls                             |          | 285                    | 381          | 285                | 381         | 554          | 285                | 381         | 554          | 756          |

|                                         | Bank 0   | 0                      | 0            | 0                  | 0           | 0            | 0                  | 0           | 0            | 0            |

|                                         | Bank 1   | 0                      | 0            | 0                  | 0           | 0            | 0                  | 0           | 0            | 0            |

|                                         | Bank 2   | 10/8                   | 16/8         | 10/8               | 16/8        | 16/8         | 10/8               | 17/9        | 16/8         | 24/12        |

| High Speed Differential Input           | Bank 3   | 14/7                   | 16/8         | 14/7               | 16/8        | 24/12        | 14/7               | 16/8        | 24/12        | 32/16        |

| / Output Pairs                          | Bank 4   | 0                      | 0            | 0                  | 0           | 0            | 0                  | 0           | 0            | 0            |

|                                         | Bank 6   | 13/6                   | 16/8         | 13/6               | 16/8        | 24/12        | 13/6               | 16/8        | 24/12        | 32/16        |

|                                         | Bank 7   | 8/6                    | 16/8         | 8/6                | 16/8        | 16/8         | 8/6                | 16/8        | 16/8         | 24/12        |

|                                         | Bank 8   | 0                      | 0            | 0                  | 0           | 0            | 0                  | 0           | 0            | 0            |

| Total High Speed Differential I/O Pairs |          | 45/2                   | 64/32        | 45/27              | 64/3        | 80/40        | 45/27              | 65/3        | 80/40        | 112/5        |

|                                         | Bank 0   | 0                      | 0            | 0                  | 0           | 0            | 0                  | 0           | 0            | 0            |

|                                         | Bank 1   | 0                      | 0            | 0                  | 0           | 0            | 0                  | 0           | 0            | 0            |

| DQS Groups                              | Bank 2   | 1                      | 2            | 1                  | 2           | 2            | 1                  | 2           | 2            | 3            |

| (> 11 pins in group)                    | Bank 3   | 2                      | 2            | 2                  | 2           | 3            | 2                  | 2           | 3            | 4            |

|                                         | Bank 4   | 0                      | 0            | 0                  | 0           | 0            | 0                  | 0           | 0            | 0            |

|                                         | Bank 6   | 2                      | 2            | 2                  | 2           | 3            | 2                  | 2           | 3            | 4            |

|                                         | Bank 7   | 1                      | 2            | 1                  | 2           | 2            | 1                  | 2           | 2            | 3            |

|                                         | Bank 8   | 0                      | 0            | 0                  | 0           | 0            | 0                  | 0           | 0            | 0            |

| Total DQS Groups                        |          | 6                      | 8            | 6                  | 8           | 10           | 6                  | 8           | 10           | 14           |

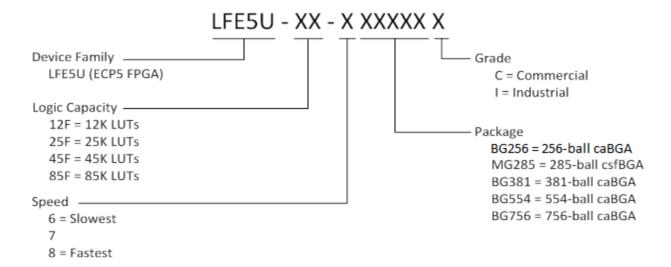

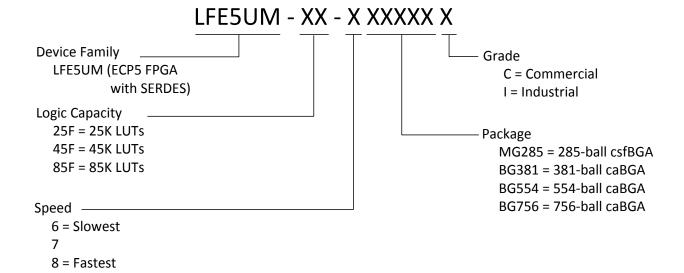

# 5. Ordering Information

# 5.1. ECP5/ECP5-5G Part Number Description

| Part number          | Grade      | Package          | Pins | Temp.          | LUTs (K) | SERDES |

|----------------------|------------|------------------|------|----------------|----------|--------|

| LFE5U-85F-6BG756I    | -6         | Lead free caBGA  | 756  | Industrial     | 84       | No     |

| LFE5U-85F-7BG756I    | -7         | Lead free caBGA  | 756  | 756 Industrial |          | No     |

| LFE5U-85F-8BG756I    | -8         | Lead free caBGA  | 756  | Industrial     | 84       | No     |

| LFE5UM-25F-6MG285I   | -6         | Lead free csfBGA | 285  | Industrial     | 24       | Yes    |

| LFE5UM-25F-7MG285I   | <b>-</b> 7 | Lead free csfBGA | 285  | Industrial     | 24       | Yes    |

| LFE5UM-25F-8MG285I   | -8         | Lead free csfBGA | 285  | Industrial     | 24       | Yes    |

| LFE5UM-25F-6BG381I   | -6         | Lead free caBGA  | 381  | Industrial     | 24       | Yes    |

| LFE5UM-25F-7BG381I   | <b>-</b> 7 | Lead free caBGA  | 381  | Industrial     | 24       | Yes    |

| LFE5UM-25F-8BG381I   | -8         | Lead free caBGA  | 381  | Industrial     | 24       | Yes    |

| LFE5UM-45F-6MG285I   | -6         | Lead free csfBGA | 285  | Industrial     | 44       | Yes    |

| LFE5UM-45F-7MG285I   | <b>-</b> 7 | Lead free csfBGA | 285  | Industrial     | 44       | Yes    |

| LFE5UM-45F-8MG285I   | -8         | Lead free csfBGA | 285  | Industrial     | 44       | Yes    |

| LFE5UM-45F-6BG381I   | -6         | Lead free caBGA  | 381  | Industrial     | 44       | Yes    |

| LFE5UM-45F-7BG381I   | -7         | Lead free caBGA  | 381  | Industrial     | 44       | Yes    |

| LFE5UM-45F-8BG381I   | -8         | Lead free caBGA  | 381  | Industrial     | 44       | Yes    |

| LFE5UM-45F-6BG554I   | -6         | Lead free caBGA  | 554  | Industrial     | 44       | Yes    |

| LFE5UM-45F-7BG554I   | -7         | Lead free caBGA  | 554  | Industrial     | 44       | Yes    |

| LFE5UM-45F-8BG554I   | -8         | Lead free caBGA  | 554  | Industrial     | 44       | Yes    |

| LFE5UM-85F-6MG285I   | -6         | Lead free csfBGA | 285  | Industrial     | 84       | Yes    |

| LFE5UM-85F-7MG285I   | -7         | Lead free csfBGA | 285  | Industrial     | 84       | Yes    |

| LFE5UM-85F-8MG285I   | -8         | Lead free csfBGA | 285  | Industrial     | 84       | Yes    |

| LFE5UM-85F-6BG381I   | -6         | Lead free caBGA  | 381  | Industrial     | 84       | Yes    |

| LFE5UM-85F-7BG381I   | <b>-</b> 7 | Lead free caBGA  | 381  | Industrial     | 84       | Yes    |

| LFE5UM-85F-8BG381I   | -8         | Lead free caBGA  | 381  | Industrial     | 84       | Yes    |

| LFE5UM-85F-6BG554I   | -6         | Lead free caBGA  | 554  | Industrial     | 84       | Yes    |

| LFE5UM-85F-7BG554I   | <b>-</b> 7 | Lead free caBGA  | 554  | Industrial     | 84       | Yes    |

| LFE5UM-85F-8BG554I   | -8         | Lead free caBGA  | 554  | Industrial     | 84       | Yes    |

| LFE5UM-85F-6BG756I   | -6         | Lead free caBGA  | 756  | Industrial     | 84       | Yes    |

| LFE5UM-85F-7BG756I   | <b>-</b> 7 | Lead free caBGA  | 756  | Industrial     | 84       | Yes    |

| LFE5UM-85F-8BG756I   | -8         | Lead free caBGA  | 756  | Industrial     | 84       | Yes    |

| LFE5UM5G-25F-8MG285I | -8         | Lead free csfBGA | 285  | Industrial     | 24       | Yes    |

| LFE5UM5G-25F-8BG381I | -8         | Lead free caBGA  | 381  | Industrial     | 24       | Yes    |

| LFE5UM5G-45F-8MG285I | -8         | Lead free csfBGA | 285  | Industrial     | 44       | Yes    |

| LFE5UM5G-45F-8BG381I | -8         | Lead free caBGA  | 381  | Industrial     | 44       | Yes    |

| LFE5UM5G-45F-8BG554I | -8         | Lead free caBGA  | 554  | Industrial     | 44       | Yes    |

| LFE5UM5G-85F-8MG285I | -8         | Lead free csfBGA | 285  | Industrial     | 84       | Yes    |

| LFE5UM5G-85F-8BG381I | -8         | Lead free caBGA  | 381  | Industrial     | 84       | Yes    |

| LFE5UM5G-85F-8BG554I | -8         | Lead free caBGA  | 554  | Industrial     | 84       | Yes    |

| LFE5UM5G-85F-8BG756I | -8         | Lead free caBGA  | 756  | Industrial     | 84       | Yes    |

# (Continued)

| Date          | Version | Section                             | Change Summary                                                                                                                     |  |  |  |  |

|---------------|---------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| November 2015 | 1.5     | All                                 | Added ECP5-5G device family.                                                                                                       |  |  |  |  |

|               |         |                                     | Changed document title to ECP5 and ECP5-5G Family Data Sheet.                                                                      |  |  |  |  |

|               | 1.4     | General Description                 | Updated Features section. Added support for eDP in RDR and HDR.                                                                    |  |  |  |  |

|               |         | Architecture                        | Updated Overview section.                                                                                                          |  |  |  |  |

|               |         |                                     | Revised Figure 2.1. Simplified Block Diagram, LFE5UM/LFE5UM5G-85 Device (Top Level). Modified Flexible sysIO description and Note. |  |  |  |  |

|               |         |                                     | Updated SERDES and Physical Coding Sublayer section.                                                                               |  |  |  |  |

|               |         |                                     | Changed E.24.V in CPRI protocol to E.24.LV.                                                                                        |  |  |  |  |

|               |         |                                     | Removed "1.1 V" from paragraph on unused Dual.                                                                                     |  |  |  |  |

|               |         | DC and Switching                    | Updated Hot Socketing Requirements section. Revised V <sub>CCHTX</sub> in table                                                    |  |  |  |  |

|               |         | Characteristics                     | notes 1 and 3. Indicated V <sub>CCHTX</sub> in table note 4.                                                                       |  |  |  |  |

|               |         |                                     | Updated SERDES High-Speed Data Transmitter section. Revised V <sub>CCHTX</sub>                                                     |  |  |  |  |

|               | ļ       |                                     | in table note 1.                                                                                                                   |  |  |  |  |

|               |         | Ordering Information                | Updated ECP5/ECP5-5G Part Number Description section. Changed "LFE5 FPGA" under Device Family to "ECP5 FPGA".                      |  |  |  |  |

| August 2015   | 1.3     | General Description                 | Updated Features section.                                                                                                          |  |  |  |  |

|               |         |                                     | Removed SMPTE3G under Embedded SERDES.                                                                                             |  |  |  |  |

|               |         |                                     | Added Single Event Upset (SEU) Mitigation Support.                                                                                 |  |  |  |  |

|               |         |                                     | Removed SMPTE protocol in fifth paragraph.                                                                                         |  |  |  |  |

|               |         | Architecture                        | General update.                                                                                                                    |  |  |  |  |

|               |         | DC and Switching<br>Characteristics | General update.                                                                                                                    |  |  |  |  |

|               |         | Pinout Information                  | Updated Signal Descriptions section. Revised the descriptions of the following signals:                                            |  |  |  |  |

|               |         |                                     | P[L/R] [Group Number]_[A/B/C/D]                                                                                                    |  |  |  |  |

|               |         |                                     | P[T/B][Group Number]_[A/B]                                                                                                         |  |  |  |  |

|               |         |                                     | D4/IO4 (Previously named D4/MOSI2/IO4)                                                                                             |  |  |  |  |

|               |         |                                     | D5/IO5 (Previously named D5/MISO/IO5)                                                                                              |  |  |  |  |

|               |         |                                     | VCCHRX_D[dual_num]CH[chan_num]                                                                                                     |  |  |  |  |

|               |         |                                     | VCCHTX_D[dual_num]CH[chan_num]                                                                                                     |  |  |  |  |

|               |         | Supplemental<br>Information         | Added TN1184 reference.                                                                                                            |  |  |  |  |