Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                       |

|--------------------------------|------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 11000                                                                        |

| Number of Logic Elements/Cells | 44000                                                                        |

| Total RAM Bits                 | 1990656                                                                      |

| Number of I/O                  | 197                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.045V ~ 1.155V                                                              |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                           |

| Package / Case                 | 256-LFBGA                                                                    |

| Supplier Device Package        | 256-CABGA (14x14)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe5u-45f-6bg256i |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 5.1. ECP5/ECP5-5G Part Number Description | 97 |

|-------------------------------------------|----|

| 5.2. Ordering Part Numbers                |    |

| 5.2.1. Commercial                         |    |

| 5.2.2. Industrial                         |    |

| Supplemental Information                  |    |

| For Further Information                   |    |

| Revision History                          |    |

# Tables

| Table 1.1. ECP5 and ECP5-5G Family Selection Guide                                                                              | 11 |

|---------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2.1. Resources and Modes Available per Slice                                                                              | 14 |

| Table 2.2. Slice Signal Descriptions                                                                                            |    |

| Table 2.3. Number of Slices Required to Implement Distributed RAM                                                               |    |

| Table 2.4. PLL Blocks Signal Descriptions                                                                                       |    |

| Table 2.5. DDRDLL Ports List                                                                                                    |    |

| Table 2.6. sysMEM Block Configurations                                                                                          |    |

| Table 2.7. Maximum Number of Elements in a Slice                                                                                |    |

| Table 2.8. Input Block Port Description                                                                                         |    |

| Table 2.9. Output Block Port Description                                                                                        |    |

| Table 2.10. Tristate Block Port Description                                                                                     |    |

| Table 2.11. DQSBUF Port List Description                                                                                        |    |

| Table 2.12. On-Chip Termination Options for Input Modes                                                                         |    |

| Table 2.13. LFE5UM/LFE5UM5G SERDES Standard Support                                                                             |    |

| Table 2.14. Available SERDES Duals per LFE5UM/LFE5UM5G Devices                                                                  |    |

| Table 2.15. LFE5UM/LFE5UM5G Mixed Protocol Support                                                                              |    |

| Table 2.16. Selectable Master Clock (MCLK) Frequencies during Configuration (Nominal)                                           |    |

| Table 3.1. Absolute Maximum Ratings                                                                                             |    |

| Table 3.2. Recommended Operating Conditions                                                                                     |    |

| Table 3.3. Power Supply Ramp Rates                                                                                              |    |

| Table 3.4. Power-On-Reset Voltage Levels                                                                                        |    |

| Table 3.5. Hot Socketing Specifications                                                                                         |    |

| Table 3.6. Hot Socketing Requirements                                                                                           |    |

| Table 3.7. DC Electrical Characteristics                                                                                        |    |

| Table 3.8. ECP5/ECP5-5G Supply Current (Standby)                                                                                |    |

| Table 3.9. ECP5UM                                                                                                               |    |

| Table 3.10. ECP5-5G                                                                                                             |    |

| Table 3.11. sysI/O Recommended Operating Conditions                                                                             |    |

| Table 3.12. Single-Ended DC Characteristics                                                                                     |    |

| Table 3.13. LVDS                                                                                                                |    |

| Table 3.14. LVDS25E DC Conditions                                                                                               |    |

| Table 3.15. BLVDS25 DC Conditions                                                                                               |    |

| Table 3.16. LVPECL33 DC Conditions                                                                                              |    |

| Table 3.17. MLVDS25 DC Conditions                                                                                               |    |

| Table 3.18. Input to SLVS                                                                                                       |    |

| Table 3.19. Pin-to-Pin Performance                                                                                              |    |

| Table 3.20. Register-to-Register Performance                                                                                    |    |

| Table 3.21. ECP5/ECP5-5G Maximum I/O Buffer Speed                                                                               |    |

| Table 3.22. ECP5/ECP5-5G External Switching Characteristics                                                                     |    |

| Table 3.23. sysCLOCK PLL Timing                                                                                                 |    |

| Table 3.24. Serial Output Timing and Levels                                                                                     |    |

| Table 3.25. Channel Output Jitter                                                                                               |    |

| Table 3.26. SERDES/PCS Latency Breakdown                                                                                        |    |

| Table 3.27. Serial Input Data Specifications         Table 3.28. Passiver Table littler Talerance Specification                 |    |

| Table 3.28. Receiver Total Jitter Tolerance Specification         Table 3.20. External Reference Clock Specification (refeller) |    |

| Table 3.29. External Reference Clock Specification (refclkp/refclkn)         Table 3.20. PCIe (2.5. Ch/c)                       |    |

| Table 3.30. PCIe (2.5 Gb/s)                                                                                                     |    |

| Table 3.31. PCIe (5 Gb/s)<br>Table 3.32. CPRI LV2 E.48 Electrical and Timing Characteristics                                    |    |

| Table 3.32. CPRI LV2 E.48 Electrical and Timing Characteristics                                                                 |    |

| Table 3.33. Transmit                                                                                                            |    |

| Table 3.35. Transmit                                                                                                            |    |

|                                                                                                                                 | 80 |

| Table 3.36. Receive and Jitter Tolerance                                |    |

|-------------------------------------------------------------------------|----|

| Table 3.37. Transmit                                                    |    |

| Table 3.38. Receive and Jitter Tolerance                                |    |

| Table 3.39. Transmit                                                    | 82 |

| Table 3.40. Receive                                                     | 82 |

| Table 3.41. Reference Clock                                             | 82 |

| Table 3.42. ECP5/ECP5-5G sysCONFIG Port Timing Specifications           | 83 |

| Table 3.43. JTAG Port Timing Specifications                             |    |

| Table 3.44. Test Fixture Required Components, Non-Terminated Interfaces |    |

|                                                                         |    |

# 1. General Description

The ECP5/ECP5-5G family of FPGA devices is optimized to deliver high performance features such as an enhanced DSP architecture, high speed SERDES (Serializer/Deserializer), and high speed source synchronous interfaces, in an economical FPGA fabric. This combination is achieved through advances in device architecture and the use of 40 nm technology making the devices suitable for high-volume, highspeed, and low-cost applications.

The ECP5/ECP5-5G device family covers look-up-table (LUT) capacity to 84K logic elements and supports up to 365 user I/Os. The ECP5/ECP5-5G device family also offers up to 156 18 x 18 multipliers and a wide range of parallel I/O standards.

The ECP5/ECP5-5G FPGA fabric is optimized high performance with low power and low cost in mind. The ECP5/ ECP5-5G devices utilize reconfigurable SRAM logic technology and provide popular building blocks such as LUT-based logic, distributed and embedded memory, Phase-Locked Loops (PLLs), Delay-Locked Loops (DLLs), pre-engineered source synchronous I/O support, enhanced sysDSP slices and advanced configuration support, including encryption and dual-boot capabilities.

The pre-engineered source synchronous logic implemented in the ECP5/ECP5-5G device family supports a broad range of interface standards including DDR2/3, LPDDR2/3, XGMII, and 7:1 LVDS.

The ECP5/ECP5-5G device family also features high speed SERDES with dedicated Physical Coding Sublayer (PCS) functions. High jitter tolerance and low transmit jitter allow the SERDES plus PCS blocks to be configured to support an array of popular data protocols including PCI Express, Ethernet (XAUI, GbE, and SGMII) and CPRI. Transmit De-emphasis with pre- and post-cursors, and Receive Equalization settings make the SERDES suitable for transmission and reception over various forms of media.

The ECP5/ECP5-5G devices also provide flexible, reliable and secure configuration options, such as dual-boot capability, bit-stream encryption, and TransFR field upgrade features.

ECP5-5G family devices have made some enhancement in the SERDES compared to ECP5UM devices. These enhancements increase the performance of the SERDES to up to 5 Gb/s data rate.

The ECP5-5G family devices are pin-to-pin compatible with the ECP5UM devices. These allows a migration path for users to port designs from ECP5UM to ECP5-5G devices to get higher performance. The Lattice Diamond<sup>™</sup> design software allows large complex designs to be efficiently implemented using the ECP5/ECP5-5G FPGA family. Synthesis library support for ECP5/ECP5-5G devices is available for popular logic synthesis tools. The Diamond tools use the synthesis tool output along with the constraints from its floor planning tools to place and route the design in the ECP5/ECP5-5G device. The tools extract the timing from the routing and back-annotate it into the design for timing verification.

Lattice provides many pre-engineered IP (Intellectual Property) modules for the ECP5/ECP5-5G family. By using these configurable soft core IPs as standardized blocks, designers are free to concentrate on the unique aspects of their design, increasing their productivity.

## 1.1. Features

- Higher Logic Density for Increased System Integration

- 12K to 84K LUTs

- 197 to 365 user programmable I/Os

- Embedded SERDES

- 270 Mb/s, up to 3.2 Gb/s, SERDES interface (ECP5)

- 270 Mb/s, up to 5.0 Gb/s, SERDES interface (ECP5-5G)

- Supports eDP in RDR (1.62 Gb/s) and HDR (2.7 Gb/s)

- Up to four channels per device: PCI Express, Ethernet (1GbE, SGMII, XAUI), and CPRI

- sysDSP™

- Fully cascadable slice architecture

- 12 to 160 slices for high performance multiply and accumulate

- Powerful 54-bit ALU operations

- Time Division Multiplexing MAC Sharing

- Rounding and truncation

- Each slice supports

- Half 36 x 36, two 18 x 18 or four 9 x 9 multipliers

- Advanced 18 x 36 MAC and 18 x 18 Multiply-Multiply-Accumulate (MMAC) operations

- Flexible Memory Resources

- Up to 3.744 Mb sysMEM<sup>™</sup> Embedded Block RAM (EBR)

- 194K to 669K bits distributed RAM

- sysCLOCK Analog PLLs and DLLs

- Four DLLs and four PLLs in LFE5-45 and LFE5-85; two DLLs and two PLLs in LFE5-25 and LFE5-12

- Pre-Engineered Source Synchronous I/O

- DDR registers in I/O cells

- Dedicated read/write levelling functionality

- Dedicated gearing logic

- Source synchronous standards support

- ADC/DAC, 7:1 LVDS, XGMII

- High Speed ADC/DAC devices

- Dedicated DDR2/DDR3 and LPDDR2/LPDDR3 memory support with DQS logic, up to 800 Mb/s data-rate

- Programmable sysI/O<sup>™</sup> Buffer Supports Wide Range of Interfaces

- On-chip termination

- LVTTL and LVCMOS 33/25/18/15/12

- SSTL 18/15 I, II

- HSUL12

- LVDS, Bus-LVDS, LVPECL, RSDS, MLVDS

- subLVDS and SLVS, MIPI D-PHY input interfaces

- Flexible Device Configuration

- Shared bank for configuration I/Os

- SPI boot flash interface

- Dual-boot images supported

- Slave SPI

- TransFR<sup>™</sup> I/O for simple field updates

- Single Event Upset (SEU) Mitigation Support

- Soft Error Detect Embedded hard macro

- Soft Error Correction Without stopping user operation

- Soft Error Injection Emulate SEU event to debug system error handling

- System Level Support

- IEEE 1149.1 and IEEE 1532 compliant

- Reveal Logic Analyzer

- On-chip oscillator for initialization and general use

- 1.1 V core power supply for ECP5, 1.2 V core power supply for ECP5UM5G

| Device                              | LFE5UM-25<br>LFE5UM5G-25 | LFE5UM-45<br>LFE5UM5G-45 | LFE5UM-85<br>LFE5UM5G-85 | LFE5U-<br>12 | LFE5U-<br>25 | LFE5U-<br>45 | LFE5U-<br>85 |

|-------------------------------------|--------------------------|--------------------------|--------------------------|--------------|--------------|--------------|--------------|

| LUTs (K)                            | 24                       | 44                       | 84                       | 12           | 24           | 44           | 84           |

| sysMEM Blocks (18 Kb)               | 56                       | 108                      | 208                      | 32           | 56           | 108          | 208          |

| Embedded Memory (Kb)                | 1,008                    | 1944                     | 3744                     | 576          | 1,008        | 1944         | 3744         |

| Distributed RAM Bits (Kb)           | 194                      | 351                      | 669                      | 97           | 194          | 351          | 669          |

| 18 X 18 Multipliers                 | 28                       | 72                       | 156                      | 28           | 28           | 72           | 156          |

| SERDES (Dual/Channels)              | 1/2                      | 2/4                      | 2/4                      | 0            | 0            | 0            | 0            |

| PLLs/DLLs                           | 2/2                      | 4/4                      | 4/4                      | 2/2          | 2/2          | 4/4          | 4/4          |

| Packages (SERDES Channels /         | IO Count)                |                          |                          |              |              |              |              |

| 256 caBGA<br>(14 x 14 mm², 0.8 mm)  | _                        | _                        | -                        | 0/197        | 0/197        | 0/197        | _            |

| 285 csfBGA<br>(10 x 10 mm², 0.5 mm) | 2/118                    | 2/118                    | 2/118                    | 0/118        | 0/118        | 0/118        | 0/118        |

| 381 caBGA<br>(17 x 17 mm², 0.8 mm)  | 2/197                    | 4/203                    | 4/205                    | 0/197        | 0/197        | 0/203        | 0/205        |

| 554 caBGA<br>(23 x 23 mm², 0.8 mm)  | _                        | 4/245                    | 4/259                    | _            | _            | 0/245        | 0/259        |

| 756 caBGA<br>(27 x 27 mm², 0.8 mm)  | _                        | _                        | 4/365                    | _            | _            | _            | 0/365        |

### Table 1.1. ECP5 and ECP5-5G Family Selection Guide

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

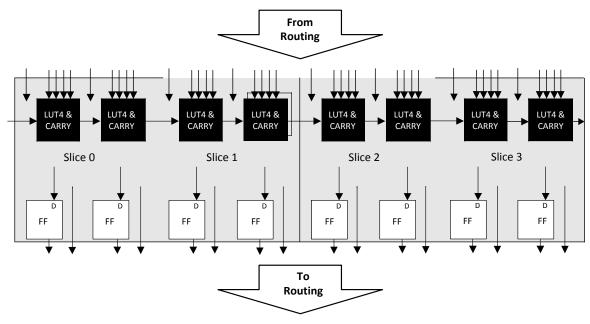

Figure 2.2. PFU Diagram

### 2.2.1. Slice

Each slice contains two LUT4s feeding two registers. In Distributed SRAM mode, Slice 0 through Slice 2 are configured as distributed memory, and Slice 3 is used as Logic or ROM. Table 2.1 shows the capability of the slices along with the operation modes they enable. In addition, each PFU contains logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7 and LUT8. There is control logic to perform set/reset functions (programmable as synchronous/ asynchronous), clock select, chip-select and wider RAM/ROM functions.

| Slice   | PFU (Used in Dis        | tributed SRAM)     | PFU (Not used as I      | Distributed SRAM)  |

|---------|-------------------------|--------------------|-------------------------|--------------------|

| Silce   | Resources Modes         |                    | Resources               | Modes              |

| Slice 0 | 2 LUT4s and 2 Registers | RAM                | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |

| Slice 1 | 2 LUT4s and 2 Registers | RAM                | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |

| Slice 2 | 2 LUT4s and 2 Registers | RAM                | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |

| Slice 3 | 2 LUT4s and 2 Registers | Logic, Ripple, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |

Table 2.1. Resources and Modes Available per Slice

Figure 2.3 shows an overview of the internal logic of the slice. The registers in the slice can be configured for positive/negative and edge triggered or level sensitive clocks.

Each slice has 14 input signals, 13 signals from routing and one from the carry-chain (from the adjacent slice or PFU). There are five outputs, four to routing and one to carry-chain (to the adjacent PFU). There are two inter slice/ PFU output signals that are used to support wider LUT functions, such as LUT6, LUT7 and LUT8. Table 2.2 and Figure 2.3 list the signals associated with all the slices. Figure 2.4 on page 16 shows the connectivity of the inter-slice/PFU signals that support LUT5, LUT6, LUT7 and LUT8.

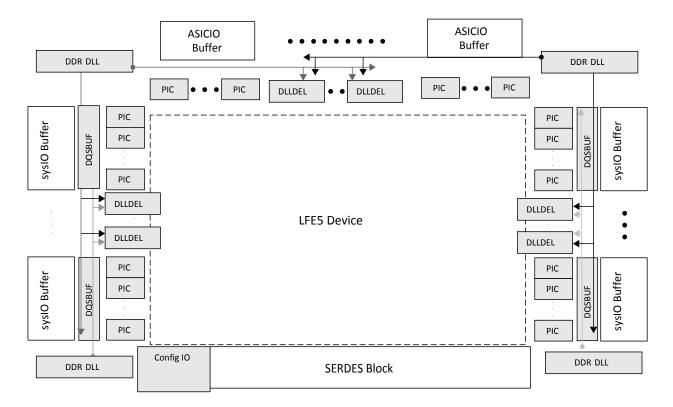

Figure 2.11. ECP5/ECP5-5G DLL Top Level View (For LFE-45 and LFE-85)

# 2.8. sysMEM Memory

ECP5/ECP5-5G devices contain a number of sysMEM Embedded Block RAM (EBR). The EBR consists of an 18 Kb RAM with memory core, dedicated input registers and output registers with separate clock and clock enable. Each EBR includes functionality to support true dual-port, pseudo dual-port, single-port RAM, ROM and FIFO buffers (via external PFUs).

### 2.8.1. sysMEM Memory Block

The sysMEM block can implement single port, dual port or pseudo dual port memories. Each block can be used in a variety of depths and widths as listed in Table 2.6 on page 25. FIFOs can be implemented in sysMEM EBR blocks by implementing support logic with PFUs. The EBR block facilitates parity checking by supporting an optional parity bit for each data byte. EBR blocks provide byte-enable support for configurations with 18-bit and 36-bit data widths. For more information, refer to ECP5 and ECP5-5G Memory Usage Guide (TN1264).

# 2.11. **PIO**

The PIO contains three blocks: an input register block, output register block, and tristate register block. These blocks contain registers for operating in a variety of modes along with the necessary clock and selection logic.

### 2.11.1. Input Register Block

The input register blocks for the PIOs on all edges contain delay elements and registers that can be used to condition high-speed interface signals before they are passed to the device core. In addition, the input register blocks for the PIOs on the left and right edges include built-in FIFO logic to interface to DDR and LPDDR memory.

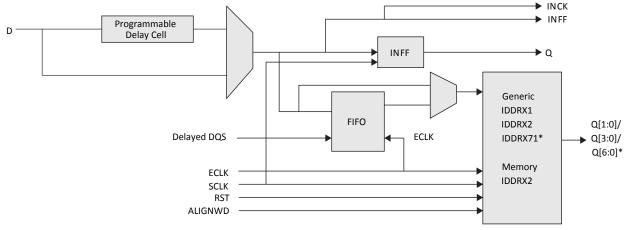

The Input register block on the right and left sides includes gearing logic and registers to implement IDDRX1 and IDDRX2 functions. With two PICs sharing the DDR register path, it can also implement IDDRX71 function used for 7:1 LVDS interfaces. It uses three sets of registers to shift, update, and transfer to implement gearing and the clock domain transfer. The first stage registers samples the high-speed input data by the high-speed edge clock on its rising and falling edges. The second stage registers perform data alignment based on the control signals. The third stage pipeline registers pass the data to the device core synchronized to the low-speed system clock. The top side of the device supports IDDRX1 gearing function. For more information on gearing function, refer to ECP5 and ECP5-5G High-Speed I/O Interface (TN1265).

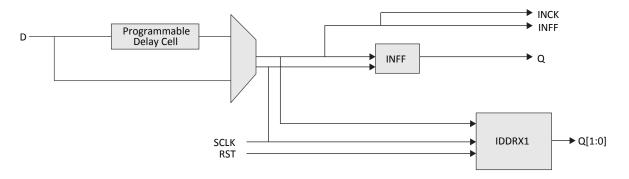

Figure 2.17 shows the input register block for the PIOs on the top edge.

Figure 2.17. Input Register Block for PIO on Top Side of the Device

Figure 2.18 shows the input register block for the PIOs located on the left and right edges.

\*For 7:1 LVDS interface only. It is required to use PIO pair pins (PIOA/B or PIOC/D).

#### Figure 2.18. Input Register Block for PIO on Left and Right Side of the Device

# 2.15. SERDES and Physical Coding Sublayer

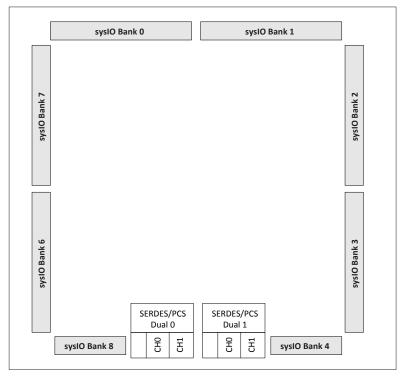

LFE5UM/LFE5UM5G devices feature up to 4 channels of embedded SERDES/PCS arranged in dual-channel blocks at the bottom of the devices. Each channel supports up to 3.2 Gb/s (ECP5), or up to 5 Gb/s (ECP5-5G) data rate. Figure 2.27 shows the position of the dual blocks for the LFE5-85. Table 2.13 shows the location of available SERDES Duals for all devices. The LFE5UM/LFE5UM5G SERDES/PCS supports a range of popular serial protocols, including:

- PCI Express Gen1 and Gen2 (2.5 Gb/s) on ECP5UM; Gen 1, Gen2 (2.5 Gb/s and 5 Gb/s) on ECP5-5G

- Ethernet (XAUI, GbE 1000 Base CS/SX/LX and SGMII)

- SMPTE SDI (3G-SDI, HD-SDI, SD-SDI)

- CPRI (E.6.LV: 614.4 Mb/s, E.12.LV: 1228.8 Mb/s, E.24.LV: 2457.6 Mb/s, E.30.LV: 3072 Mb/s), also E.48.LV2:4915 Mb/s in ECP5-5G

- JESD204A/B ADC and DAC converter interface: 312.5 Mb/s to 3.125 Gb/s (ECP5) / 5 Gb/s (ECP5-5G)

Each dual contains two dedicated SERDES for high speed, full duplex serial data transfer. Each dual also has a PCS block that interfaces to the SERDES channels and contains protocol specific digital logic to support the standards listed above. The PCS block also contains interface logic to the FPGA fabric. All PCS logic for dedicated protocol support can also be bypassed to allow raw 8-bit or 10-bit interfaces to the FPGA fabric.

Even though the SERDES/PCS blocks are arranged in duals, multiple baud rates can be supported within a dual with the use of dedicated, per channel /1, /2 and /11 rate dividers. Additionally, two duals can be arranged together to form x4 channel link.

ECP5UM devices and ECP5-5G devices are pin-to-pin compatible. But, the ECP5UM devices require 1.1 V on VCCA, VCCHRX and VCCHTX supplies. ECP5-5G devices require 1.2 V on these supplies. When designing either family device with migration in mind, these supplies need to be connected such that it is possible to adjust the voltage level on these supplies.

When a SERDES Dual in a 2-Dual device is not used, the power VCCA power supply for that Dual should be connected. It is advised to connect the VCCA of unused channel to core if the user knows he will not use the Dual at all, or it should be connected to a different regulated supply, if that Dual may be used in the future.

For an unused channel in a Dual, it is advised to connect the VCCHTX to VCCA, and user can leave VCCHRX unconnected.

For information on how to use the SERDES/PCS blocks to support specific protocols, as well on how to combine multiple protocols and baud rates within a device, refer to ECP5 and ECP5-5G SERDES/PCS Usage Guide (TN1261).

Figure 2.27. SERDES/PCS Duals (LFE5UM/LFE5UM5G-85)

| Standard                                       | Data Rate (Mb/s)                                           | Number of General/Link Width | Encoding Style |

|------------------------------------------------|------------------------------------------------------------|------------------------------|----------------|

| PCI Express 1.1 and 2.0                        | 2500                                                       | x1, x2, x4                   | 8b10b          |

| 2.02                                           | 5000 <sup>2</sup>                                          | x1, x2                       | 8b10b          |

| Gigabit Ethernet                               | 1250                                                       | x1                           | 8b10b          |

| COMU                                           | 1250                                                       | x1                           | 8b10b          |

| SGMII                                          | 2500                                                       | x1                           | 8b10b          |

| XAUI                                           | 3125                                                       | x4                           | 8b10b          |

| CPRI-1<br>CPRI-2<br>CPRI-3<br>CPRI-4<br>CPRI-5 | 614.4<br>1228.8<br>2457.6<br>3072.0<br>4915.2 <sup>2</sup> | x1                           | 8b10b          |

| SD-SDI (259M, 344M) 1                          | 270                                                        | x1                           | NRZI/Scrambled |

| HD-SDI (292M)                                  | 1483.5<br>1485                                             | x1                           | NRZI/Scrambled |

| 3G-SDI (424M)                                  | 2967<br>2970                                               | x1                           | NRZI/Scrambled |

|                                                | 5000                                                       | _                            | _              |

| JESD204A/B                                     | 3125                                                       | x1                           | 8b/10b         |

#### Notes:

1. For SD-SDI rate, the SERDES is bypassed and SERDES input signals are directly connected to the FPGA routing.

2. For ECP5-5G family devices only.

When an error is detected, and the user's error handling software determines the error did not create any risk to the system operation, the SEC tool allows the device to be re-configured in the background to correct the affected bit. This operation allows the user functions to continue to operate without stopping the system function.

Additional SEI tool is also available in the Diamond Software, by creating a frame of data to be programmed into the device in the background with one bit changed, without stopping the user functions on the device. This emulates an SEU situation, allowing the user to test and monitor its error handling software.

For further information on SED support, refer to LatticeECP3, ECP5 and ECP5-5G Soft Error Detection (SED)/Correction (SEC) Usage Guide (TN1184).

### 2.18.3. On-Chip Oscillator

Every ECP5/ECP5-5G device has an internal CMOS oscillator which is used to derive a Master Clock (MCLK) for configuration. The oscillator and the MCLK run continuously and are available to user logic after configuration is completed. The software default value of the MCLK is nominally 2.4 MHz. Table 2.16 lists all the available MCLK frequencies. When a different Master Clock is selected during the design process, the following sequence takes place:

- 1. Device powers up with a nominal Master Clock frequency of 2.4 MHz.

- 2. During configuration, users select a different master clock frequency.

- 3. The Master Clock frequency changes to the selected frequency once the clock configuration bits are received.

- 4. If the user does not select a master clock frequency, then the configuration bitstream defaults to the MCLK frequency of 2.4 MHz.

This internal oscillator is available to the user by routing it as an input clock to the clock tree. For further information on the use of this oscillator for configuration or user mode, refer to ECP5 and ECP5-5G sysCONFIG Usage Guide (TN1260) and ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263).

#### Table 2.16. Selectable Master Clock (MCLK) Frequencies during Configuration (Nominal)

| MCLK Frequency (MHz) |

|----------------------|

| 2.4                  |

| 4.8                  |

| 9.7                  |

| 19.4                 |

| 38.8                 |

| 62                   |

# 2.19. Density Shifting

The ECP5/ECP5-5G family is designed to ensure that different density devices in the same family and in the same package have the same pinout. Furthermore, the architecture ensures a high success rate when performing design migration from lower density devices to higher density devices. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likelihood of success in each case. An example is that some user I/Os may become No Connects in smaller devices in the same package. Refer to the ECP5/ECP5-5G Pin Migration Tables and Diamond software for specific restrictions and limitations.

# 3.15. Typical Building Block Function Performance

#### Table 3.19. Pin-to-Pin Performance

| Function        | –8 Timing | Unit |

|-----------------|-----------|------|

| Basic Functions |           |      |

| 16-Bit Decoder  | 5.06      | ns   |

| 32-Bit Decoder  | 6.08      | ns   |

| 64-Bit Decoder  | 5.06      | ns   |

| 4:1 Mux         | 4.45      | ns   |

| 8:1 Mux         | 4.63      | ns   |

| 16:1 Mux        | 4.81      | ns   |

| 32:1 Mux        | 4.85      | ns   |

Notes:

1. I/Os are configured with LVCMOS25 with V<sub>CCIO</sub>=2.5, 12 mA drive.

2. These functions were generated using Lattice Diamond design software tool. Exact performance may vary with the device and the design software tool version. The design software tool uses internal parameters that have been characterized but are not tested on every device.

3. Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from Lattice Diamond design software tool.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-DS-02012-1.9

#### Table 3.20. Register-to-Register Performance

| Function                                                                        | –8 Timing | Unit |

|---------------------------------------------------------------------------------|-----------|------|

| Basic Functions                                                                 |           |      |

| 16-Bit Decoder                                                                  | 441       | MHz  |

| 32-Bit Decoder                                                                  | 441       | MHz  |

| 64-Bit Decoder                                                                  | 332       | MHz  |

| 4:1 Mux                                                                         | 441       | MHz  |

| 8:1 Mux                                                                         | 441       | MHz  |

| 16:1 Mux                                                                        | 441       | MHz  |

| 32:1 Mux                                                                        | 441       | MHz  |

| 8-Bit Adder                                                                     | 441       | MHz  |

| 16-Bit Adder                                                                    | 441       | MHz  |

| 64-Bit Adder                                                                    | 441       | MHz  |

| 16-Bit Counter                                                                  | 384       | MHz  |

| 32-Bit Counter                                                                  | 317       | MHz  |

| 64-Bit Counter                                                                  | 263       | MHz  |

| 64-Bit Accumulator                                                              | 288       | MHz  |

| Embedded Memory Functions                                                       |           |      |

| 1024x18 True-Dual Port RAM (Write Through or Normal), with EBR Output Registers | 272       | MHz  |

| 1024x18 True-Dual Port RAM (Read-Before-Write), with EBR Output Registers       | 214       | MHz  |

| Distributed Memory Functions                                                    |           |      |

| 16 x 2 Pseudo-Dual Port or 16 x 4 Single Port RAM (One PFU)                     | 441       | MHz  |

| 16 x 4 Pseudo-Dual Port (Two PFUs)                                              | 441       | MHz  |

| DSP Functions                                                                   |           |      |

| 9 x 9 Multiplier (All Registers)                                                | 225       | MHz  |

| 18 x 18 Multiplier (All Registers)                                              | 225       | MHz  |

| 36 x 36 Multiplier (All Registers)                                              | 225       | MHz  |

| 18 x 18 Multiply-Add/Sub (All Registers)                                        | 225       | MHz  |

| 18 x 18 Multiply/Accumulate (Input and Output Registers)                        | 225       | MHz  |

Notes:

1. These functions were generated using Lattice Diamond design software tool. Exact performance may vary with the device and the design software tool version. The design software tool uses internal parameters that have been characterized but are not tested on every device.

2. Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from Lattice Diamond design software tool.

## 3.16. Derating Timing Tables

Logic timing provided in the following sections of this data sheet and the Diamond design tools are worst case numbers in the operating range. Actual delays at nominal temperature and voltage for best case process, can be much better than the values given in the tables. The Diamond design tool can provide logic timing numbers at a particular temperature and voltage.

# 3.18. External Switching Characteristics

Over recommended commercial operating conditions.

### Table 3.22. ECP5/ECP5-5G External Switching Characteristics

| Devenueter             | Description                                                       | Davias         | -8        |     | -7    |     | -6   |     | l lait |

|------------------------|-------------------------------------------------------------------|----------------|-----------|-----|-------|-----|------|-----|--------|

| Parameter              | Description                                                       | Device         | Min       | Max | Min   | Max | Min  | Max | Unit   |

| Clocks                 | Clocks                                                            |                |           |     |       |     |      |     |        |

| Primary Clock          |                                                                   |                |           |     |       |     |      |     |        |

| f <sub>MAX_PRI</sub>   | Frequency for Primary Clock Tree                                  | _              | —         | 370 | —     | 303 | _    | 257 | MHz    |

| t <sub>w_pri</sub>     | Clock Pulse Width for Primary<br>Clock                            | _              | 0.8       | —   | 0.9   | —   | 1.0  | —   | ns     |

| t <sub>skew_pri</sub>  | Primary Clock Skew within a<br>Device                             | -              | -         | 420 | _     | 462 | -    | 505 | ps     |

| Edge Clock             |                                                                   |                | -         |     |       |     |      |     |        |

| f <sub>MAX_EDGE</sub>  | Frequency for Edge Clock Tree                                     | —              | _         | 400 | —     | 350 | _    | 312 | MHz    |

| tw_edge                | Clock Pulse Width for Edge Clock                                  | _              | 1.175     | _   | 1.344 | _   | 1.50 | —   | ns     |

| t <sub>skew_edge</sub> | Edge Clock Skew within a Bank                                     | -              | -         | 160 | -     | 180 | -    | 200 | ps     |

| Generic SDR In         | put                                                               |                |           |     | •     |     |      |     | •      |

| General I/O Pin        | Parameters Using Dedicated Primary (                              | Clock Input w  | ithout PL | L   |       |     |      |     |        |

| t <sub>co</sub>        | Clock to Output - PIO Output<br>Register                          | All<br>Devices | -         | 5.4 | -     | 6.1 | -    | 6.8 | ns     |

| t <sub>su</sub>        | Clock to Data Setup - PIO Input<br>Register                       | All<br>Devices | 0         | _   | 0     | _   | 0    | _   | ns     |

| t <sub>H</sub>         | Clock to Data Hold - PIO Input<br>Register                        | All<br>Devices | 2.7       | -   | 3     | -   | 3.3  | _   | ns     |

| t <sub>su_del</sub>    | Clock to Data Setup - PIO Input<br>Register with Data Input Delay | All<br>Devices | 1.2       | -   | 1.33  | -   | 1.46 | _   | ns     |

| t <sub>h_del</sub>     | Clock to Data Hold - PIO Input<br>Register with Data Input Delay  | All<br>Devices | 0         | _   | 0     | _   | 0    | _   | ns     |

| f <sub>MAX_IO</sub>    | Clock Frequency of I/O and PFU Register                           | All<br>Devices | -         | 400 | _     | 350 | -    | 312 | MHz    |

| General I/O Pin        | Parameters Using Dedicated Primary (                              | Clock Input w  | ith PLL   |     |       |     |      |     |        |

| t <sub>copll</sub>     | Clock to Output - PIO Output<br>Register                          | All<br>Devices | _         | 3.5 | _     | 3.8 | _    | 4.1 | ns     |

| t <sub>supll</sub>     | Clock to Data Setup - PIO Input<br>Register                       | All<br>Devices | 0.7       | _   | 0.78  |     | 0.85 | _   | ns     |

| t <sub>HPLL</sub>      | Clock to Data Hold - PIO Input<br>Register                        | All<br>Devices | 0.8       | _   | 0.89  | -   | 0.98 | _   | ns     |

| t <sub>su_delpll</sub> | Clock to Data Setup - PIO Input<br>Register with Data Input Delay | All<br>Devices | 1.6       | _   | 1.78  | _   | 1.95 | _   | ns     |

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

| Davia materi                             | Description                                                                  | Device           | -8              |           | -7        |          | -6         |            | l lait           |

|------------------------------------------|------------------------------------------------------------------------------|------------------|-----------------|-----------|-----------|----------|------------|------------|------------------|

| Parameter                                |                                                                              |                  | Min             | Max       | Min       | Max      | Min        | Max        | Unit             |

| t <sub>h_delpll</sub>                    | Clock to Data Hold - PIO Input<br>Register with Data Input Delay All Devices |                  | 0               | -         | 0         | -        | 0          | -          | ns               |

| Generic DDR Input                        |                                                                              |                  |                 |           |           |          |            |            |                  |

| Generic DDRX1 Inp                        | uts With Clock and Data Centere                                              | d at Pin (GDDI   | RX1_RX.S        | CLK.Cen   | tered) Us | ing PCLk | Clock In   | put - Fig  | ure 3.6          |

| t <sub>SU_GDDRX1_centered</sub>          | Data Setup Before CLK Input                                                  | All Devices      | ·               |           | 0.52      | -        | 0.52       | -          | ns               |

| t <sub>HD_GDDRX1_centered</sub>          | Data Hold After CLK Input                                                    | All Devices      | 0.52            | _         | 0.52      | _        | 0.52       | _          | ns               |

| f <sub>DATA_GDDRX1_centered</sub>        | GDDRX1 Data Rate                                                             | All Devices      | All Devices — 5 |           | _         | 500      | _          | 500        | Mb/s             |

| f <sub>MAX_GDDRX1_centered</sub>         | GDDRX1 CLK Frequency (SCLK)                                                  | All Devices – 25 |                 | 250       | —         | 250      | _          | 250        | MHz              |

| Generic DDRX1 Inp                        | uts With Clock and Data Aligned                                              | at Pin (GDDR)    | (1_RX.SC        | LK.Aligne | ed) Using | PCLK Cl  | ock Input  | - Figure   | 3.7              |

| $t_{SU_GDDRX1_aligned}$                  | Data Setup from CLK Input                                                    | All Devices      | ·               |           | -         | -0.55    | -          | -0.55      | ns +<br>1/2 UI   |

| $t_{HD\_GDDRX1\_aligned}$                | Data Hold from CLK Input                                                     | All Devices      | 0.55            | -         | 0.55      | -        | 0.55       | _          | ns +<br>1/2 U    |

| $f_{DATA_GDDRX1_aligned}$                | GDDRX1 Data Rate                                                             | All Devices      | s — 500         |           | —         | 500      | —          | 500        | Mb/s             |

| $f_{MAX\_GDDRX1\_aligned}$               | GDDRX1 CLK Frequency (SCLK)                                                  | All Devices      | evices —        |           | —         | 250      | —          | 250        | MHz              |

| Generic DDRX2 Inp                        | uts With Clock and Data Centere                                              | d at Pin (GDDI   | RX2_RX.E        | CLK.Cen   | tered) Us | ing PCLK | Clock In   | put, Left  | and              |

| Right sides Only - F                     |                                                                              |                  | - 1             | - 1       | 1         | 1        | 1          | I          | 1                |

| $t_{SU_GDDRX2_centered}$                 | Data Setup before CLK Input                                                  | All Devices      | 0.321           | —         | 0.403     | —        | 0.471      | -          | ns               |

| t <sub>HD_GDDRX2_centered</sub>          | Data Hold after CLK Input                                                    | All Devices      | 0.321           | -         | 0.403     | _        | 0.471      | -          | ns               |

| $f_{DATA\_GDDRX2\_centered}$             | GDDRX2 Data Rate                                                             | All Devices      | -               | 800       | —         | 700      | -          | 624        | Mb/s             |

| $f_{MAX\_GDDRX2\_centered}$              | GDDRX2 CLK Frequency (ECLK)                                                  | All Devices      | -               | 400       | -         | 350      | -          | 312        | MHz              |

| Generic DDRX2 Inp<br>sides Only - Figure | uts With Clock and Data Aligned 3.7                                          | at Pin (GDDR)    | (2_RX.EC        | LK.Aligne | ed) Using | PCLK Cl  | ock Input  | t, Left an | d Right          |

| $t_{SU\_GDDRX2\_aligned}$                | Data Setup from CLK Input                                                    | All Devices      | _               | -0.344    | _         | -0.42    | -          | -0.495     | ns + 1/2<br>UI   |

| $t_{HD}_{GDDRX2}_{aligned}$              | Data Hold from CLK Input                                                     | All Devices      | 0.344           | —         | 0.42      | _        | 0.495      | —          | ns + 1/2<br>UI   |

| $f_{DATA\_GDDRX2\_aligned}$              | GDDRX2 Data Rate                                                             | All Devices      | —               | 800       | —         | 700      | —          | 624        | Mb/s             |

| $f_{MAX\_GDDRX2\_aligned}$               | GDDRX2 CLK Frequency                                                         | All Devices      | _               | 400       | —         | 350      | _          | 312        | MHz              |

| Video DDRX71 Inpu<br>Figure 3.11         | its With Clock and Data Aligned a                                            | at Pin (GDDRX    | 71_RX.E0        | CLK) Usin | g PLL Clo | ck Input | , Left and | l Right si | des Only         |

| t <sub>su_lvds71_i</sub>                 | Data Setup from CLK Input<br>(bit i)                                         | All Devices      | _               | -0.271    | _         | -0.39    | _          | -0.41      | ns+(1/2+<br>* UI |

| thd_lvds71_i                             | Data Hold from CLK Input<br>(bit i)                                          | All Devices      | 0.271           | _         | 0.39      | _        | 0.41       | _          | ns+(1/2+<br>* UI |

| f <sub>DATA_LVDS71</sub>                 | DDR71 Data Rate                                                              | All Devices      |                 | 756       | —         | 620      | _          | 525        | Mb/s             |

| f <sub>MAX_LVDS71</sub>                  | DDR71 CLK Frequency (ECLK)                                                   | All Devices      | Devices —       |           | _         | 310      | _          | 262.5      | MHz              |

### Table 3.22. ECP5/ECP5-5G External Switching Characteristics (Continued)

### Table 3.22. ECP5/ECP5-5G External Switching Characteristics (Continued)

|                                                                                                                               | 3.22. ECP5/ECP5-5G External Switching Characteristics |                 | -8 -7 -6   |           |            |            |             |            |                  |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------|------------|-----------|------------|------------|-------------|------------|------------------|

| Parameter                                                                                                                     | Description                                           | Device          | Min        | -o<br>Max | Min        | Max        | -<br>Min    | -o<br>Max  | Unit             |

| Generic DDR Outp                                                                                                              | ut                                                    |                 |            |           |            |            |             |            |                  |

| Generic DDRX1 Outputs With Clock and Data Centered at Pin (GDDRX1_TX.SCLK.Centered) Using PCLK Clock Input - Figure 3.6       |                                                       |                 |            |           |            |            |             | ure 3.6    |                  |

| $t_{\text{DVB}\_\text{GDDRX1}\_\text{centered}}$                                                                              | Data Output Valid before CLK<br>Output                | All Devices     | -0.67      | _         | -0.67      | -          | -0.67       | _          | ns +<br>1/2 UI   |

| $t_{\text{DVA}_{GDDRX1}_{centered}}$                                                                                          | Data Output Valid after CLK<br>Output                 | All Devices     | -0.67      | _         | -0.67      | _          | -0.67       | _          | ns +<br>1/2 UI   |

| f <sub>DATA_GDDRX1_centered</sub>                                                                                             | GDDRX1 Data Rate                                      | All Devices     | _          | 500       | —          | 500        | —           | 500        | Mb/s             |

| f <sub>MAX_GDDRX1_centered</sub>                                                                                              | GDDRX1 CLK Frequency (SCLK)                           | All Devices     | _          | 250       | _          | 250        | —           | 250        | MHz              |

| Generic DDRX1 Ou                                                                                                              | tputs With Clock and Data Aligne                      | ed at Pin (GDDI | RX1_TX.9   | CLK.Alig  | ned) Usin  | g PCLK C   | lock Inpu   | t - Figure | 3.9              |

| $t_{DIB\_GDDRX1\_aligned}$                                                                                                    | Data Output Invalid before<br>CLK Output              | All Devices     | -0.3       | —         | -0.3       | _          | -0.3        | _          | ns               |

| $t_{\text{DIA}_{GDDRX1}_{aligned}}$                                                                                           | Data Output Invalid after CLK<br>Output               | All Devices     | -          | 0.3       | _          | 0.3        | _           | 0.3        | ns               |

| $f_{DATA_GDDRX1_aligned}$                                                                                                     | GDDRX1 Data Rate                                      | All Devices     | _          | 500       | —          | 500        | —           | 500        | Mb/s             |

| $f_{MAX\_GDDRX1\_aligned}$                                                                                                    | GDDRX1 CLK Frequency (SCLK)                           | All Devices     | _          | 250       | —          | 250        | —           | 250        | MHz              |

| Generic DDRX2 Ou                                                                                                              | tputs With Clock and Data Cente                       | red at Pin (GD  | DRX2_TX    | .ECLK.Ce  | ntered) l  | Jsing PCL  | K Clock Ir  | nput, Left | and              |

| Right sides Only -                                                                                                            |                                                       |                 |            |           |            | 1          |             |            | 1                |

| $t_{\text{DVB}\_\text{GDDRX2}\_\text{centered}}$                                                                              | Data Output Valid Before CLK<br>Output                | All Devices     | –<br>0.442 | —         | -0.56      | -          | –<br>0.676  | —          | ns +<br>1/2 UI   |

| $t_{\text{DVA}_{GDDRX2}_{centered}}$                                                                                          | Data Output Valid After CLK<br>Output                 | All Devices     | _          | 0.442     | _          | 0.56       | _           | 0.676      | ns +<br>1/2 UI   |

| $f_{\text{DATA}\_\text{GDDRX2}\_\text{centered}}$                                                                             | GDDRX2 Data Rate                                      | All Devices     | _          | 800       | —          | 700        | —           | 624        | Mb/s             |

| $f_{MAX\_GDDRX2\_centered}$                                                                                                   | GDDRX2 CLK Frequency (ECLK)                           | All Devices     | —          | 400       | —          | 350        | —           | 312        | MHz              |

| Generic DDRX2 Ou<br>sides Only - Figure                                                                                       | tputs With Clock and Data Aligne                      | ed at Pin (GDDI | RX2_TX.E   | CLK.Alig  | ned) Usin  | g PCLK C   | lock Inpu   | t, Left an | d Right          |

| t <sub>DIB_GDDRX2_aligned</sub>                                                                                               | Data Output Invalid before<br>CLK Output              | All Devices     | -0.16      | _         | -0.18      | -          | -0.2        | _          | ns               |

| $t_{\text{DIA}\_\text{GDDRX2}\_\text{aligned}}$                                                                               | Data Output Invalid after CLK<br>Output               | All Devices     | _          | 0.16      | _          | 0.18       | _           | 0.2        | ns               |

| $f_{DATA\_GDDRX2\_aligned}$                                                                                                   | GDDRX2 Data Rate                                      | All Devices     | _          | 800       | —          | 700        | —           | 624        | Mb/s             |

| $f_{MAX\_GDDRX2\_aligned}$                                                                                                    | GDDRX2 CLK Frequency (ECLK)                           | All Devices     | _          | 400       | —          | 350        | —           | 312        | MHz              |

| Video DDRX71 Out                                                                                                              | puts With Clock and Data Aligne                       | d at Pin (GDDR  | х71_тх.    | ECLK) Usi | ing PLL Cl | ock Inpu   | t, Left and | d Right si | des Only         |

| - Figure 3.12                                                                                                                 |                                                       |                 |            |           |            | 1          |             |            |                  |

| t <sub>dib_lvds71_i</sub>                                                                                                     | Data Output Invalid before<br>CLK Output              | All Devices     | -0.16      | -         | -0.18      | _          | -0.2        | _          | ns +<br>(i) * UI |

| t <sub>dia_lvds71_i</sub>                                                                                                     | Data Output Invalid after CLK<br>Output               | All Devices     | _          | 0.16      | —          | 0.18       | -           | 0.2        | ns +<br>(i) * UI |

| f <sub>data_lvds71</sub>                                                                                                      | DDR71 Data Rate                                       | All Devices     | —          | 756       | _          | 620        | —           | 525        | Mb/s             |

| f <sub>MAX_LVDS71</sub>                                                                                                       | DDR71 CLK Frequency (ECLK)                            | All Devices     | _          | 378       | _          | 310        | -           | 262.5      | MHz              |

| Memory Interface                                                                                                              |                                                       |                 |            |           |            |            |             |            |                  |

| DDR2/DDR3/DDR3                                                                                                                | IL/LPDDR2/LPDDR3 READ (DQ In                          | put Data are A  | ligned to  | DQS)      |            |            |             |            |                  |

| t <sub>DVBDQ_DDR2</sub><br>t <sub>DVBDQ_DDR3</sub><br>t <sub>DVBDQ_DDR3L</sub><br>t <sub>DVBDQ_LPDDR2</sub>                   | Data Output Valid before DQS<br>Input                 | All Devices     | _          | -0.26     | _          | –<br>0.317 | _           | –<br>0.374 | ns + 1/2<br>UI   |

| tovbdo_lpddr3<br>tovado_ddr2<br>tovado_ddr3<br>tovado_ddr3<br>tovado_lddr3<br>tovado_lpddr2<br>tovado_lpddr2<br>tovado_lpddr3 | Data Output Valid after DQS<br>Input                  | All Devices     | 0.26       |           | 0.317      | _          | 0.374       |            | ns + 1/2<br>UI   |

### Table 3.22. ECP5/ECP5-5G External Switching Characteristics (Continued)

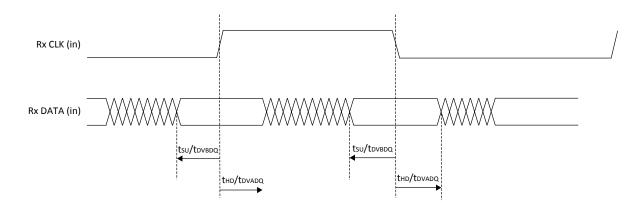

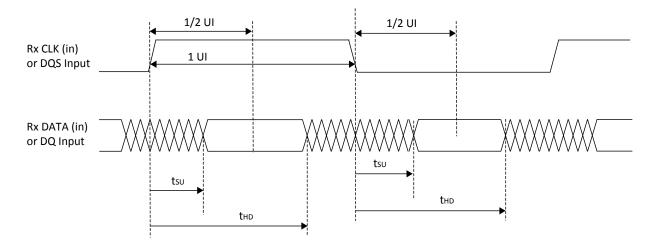

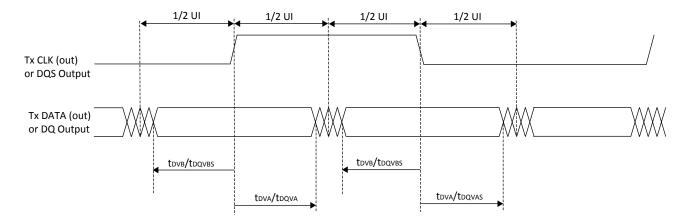

Figure 3.6. Receiver RX.CLK.Centered Waveforms

Figure 3.7. Receiver RX.CLK.Aligned and DDR Memory Input Waveforms

Figure 3.8. Transmit TX.CLK.Centered and DDR Memory Output Waveforms

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

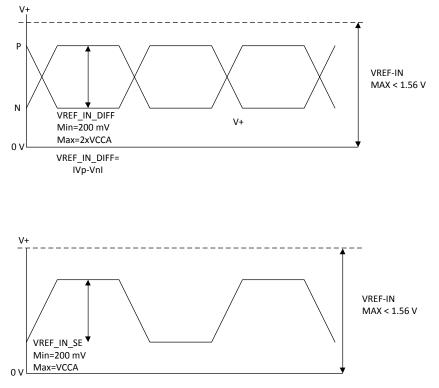

# 3.24. SERDES External Reference Clock

The external reference clock selection and its interface are a critical part of system applications for this product. Table 3.29 specifies reference clock requirements, over the full range of operating conditions.

| Symbol                        | Description                                     | Min   | Тур                   | Max                       | Unit                    |  |

|-------------------------------|-------------------------------------------------|-------|-----------------------|---------------------------|-------------------------|--|

| F <sub>REF</sub>              | Frequency range                                 | 50    | —                     | 320                       | MHz                     |  |

| F <sub>REF-PPM</sub>          | Frequency tolerance <sup>1</sup>                | -1000 | —                     | 1000                      | ppm                     |  |

| V <sub>REF-IN-SE</sub>        | Input swing, single-ended clock <sup>2, 4</sup> | 200   | – V <sub>CCAUXA</sub> |                           | mV, p-p                 |  |

| V <sub>REF-IN-DIFF</sub>      | Input swing, differential clock                 | 200   | _                     | 2*V <sub>CCAUXA</sub>     | mV, p-p<br>differential |  |

| V <sub>REF-IN</sub>           | Input levels                                    | 0     | —                     | V <sub>CCAUXA</sub> + 0.4 | V                       |  |

| D <sub>REF</sub>              | Duty cycle <sup>3</sup>                         | 40    | —                     | 60                        | %                       |  |

| T <sub>REF-R</sub>            | Rise time (20% to 80%)                          | 200   | 500                   | 1000                      | ps                      |  |

| T <sub>REF-F</sub>            | Fall time (80% to 20%)                          | 200   | 500                   | 1000                      | ps                      |  |

| Z <sub>REF-IN-TERM-DIFF</sub> | Differential input termination                  | -30%  | 100/HiZ               | +30%                      | Ω                       |  |

| C <sub>REF-IN-CAP</sub>       | Input capacitance                               | _     | _                     | 7                         | pF                      |  |

Table 3.29. External Reference Clock Specification (refclkp/refclkn)

#### Notes:

1. Depending on the application, the PLL\_LOL\_SET and CDR\_LOL\_SET control registers may be adjusted for other tolerance values as described in ECP5 and ECP5-5G SERDES/PCS Usage Guide (TN1261).

- 2. The signal swing for a single-ended input clock must be as large as the p-p differential swing of a differential input clock to get the same gain at the input receiver. With single-ended clock, a reference voltage needs to be externally connected to CLKREFN pin, and the input voltage needs to be swung around this reference voltage.

- 3. Measured at 50% amplitude.

- 4. Single-ended clocking is achieved by applying a reference voltage V<sub>REF</sub> on REFCLKN input, with the clock applied to REFCLKP input pin. V<sub>REF</sub> should be set to mid-point of the REFCLKP voltage swing.

Figure 3.14. SERDES External Reference Clock Waveforms

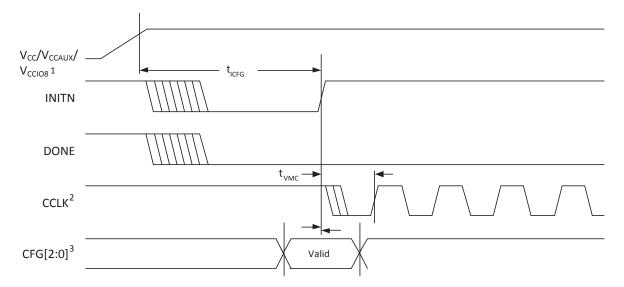

- 1. Time taken from  $V_{CC}$ ,  $V_{CCAUX}$  or  $V_{CCIO8}$ , whichever is the last to cross the POR trip point.

- 2. Device is in a Master Mode (SPI, SPIm).

- 3. The CFG pins are normally static (hardwired).

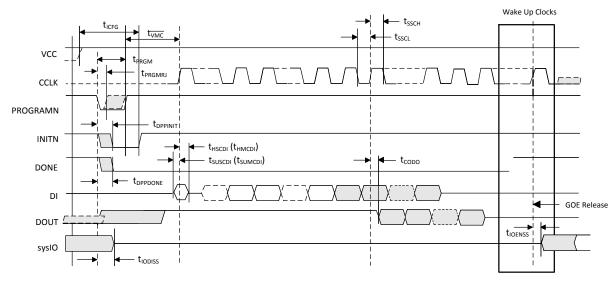

Figure 3.19. sysCONFIG Port Timing

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

# **Revision History**

| Date          | Version | Section                             | Change Summary                                                                                                                |

|---------------|---------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| March 2018    | 1.9     | All                                 | Updated formatting and page referencing.                                                                                      |

|               |         | General Description                 | Updated Table 1.1. ECP5 and ECP5-5G Family Selection Guide. Added caBGA256 package in LFE5U-45.                               |

|               |         | Architecture                        | Added a row for SGMII in Table 2.13. LFE5UM/LFE5UM5G SERDES<br>Standard Support. Updated footnote #1.                         |

|               |         | DC and Switching<br>Characteristics | Updated Table 3.2. Recommended Operating Conditions.                                                                          |

|               |         |                                     | Added 2 rows and updated values in Table 3.7. DC Electrical Characteristics.                                                  |

|               |         |                                     | Updated Table 3.8. ECP5/ECP5-5G Supply Current (Standby).                                                                     |

|               |         |                                     | Updated Table 3.11. sysl/O Recommended Operating Conditions.                                                                  |

|               |         |                                     | Updated Table 3.12. Single-Ended DC Characteristics.                                                                          |

|               |         |                                     | Updated Table 3.13. LVDS.                                                                                                     |

|               |         |                                     | Updated Table 3.14. LVDS25E DC Conditions.                                                                                    |

|               |         |                                     | Updated Table 3.21. ECP5/ECP5-5G Maximum I/O Buffer Speed.                                                                    |

|               |         |                                     | Updated Table 3.28. Receiver Total Jitter Tolerance Specification.                                                            |

|               |         |                                     | Updated header name of section 3.28 CPRI LV E.24/SGMII(2.5Gbps)<br>Electrical and Timing Characteristics.                     |

|               |         |                                     | Updated header name of section 3.29 Gigabit<br>Ethernet/SGMII(1.25Gbps)/CPRI LV E.12 Electrical and Timing<br>Characteristics |

|               |         | Pinout Information                  | Updated table in section 4.3.2 LFE5U.                                                                                         |

|               |         | Ordering Information                | Added table rows in 5.2.1 Commercial.                                                                                         |

|               |         |                                     | Added table rows in 5.2.2 Industrial.                                                                                         |

|               |         | Supplemental<br>Information         | Updated For Further Information section.                                                                                      |

| November 2017 | 1.8     | General Description                 | Updated Table 1.1. ECP5 and ECP5-5G Family Selection Guide. Added caBGA256 package in LFE5U-12 and LFE5U-25.                  |