# E.J. Lattice Semiconductor Corporation - <u>LFE5U-85F-8BG381C Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                       |

|--------------------------------|------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 21000                                                                        |

| Number of Logic Elements/Cells | 84000                                                                        |

| Total RAM Bits                 | 3833856                                                                      |

| Number of I/O                  | 205                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.045V ~ 1.155V                                                              |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                              |

| Package / Case                 | 381-FBGA                                                                     |

| Supplier Device Package        | 381-CABGA (17x17)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe5u-85f-8bg381c |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Copyright Notice**

Copyright © 2014-2018 Lattice Semiconductor Corporation. All rights reserved. The contents of these materials contain proprietary and confidential information (including trade secrets, copyright, and other Intellectual Property interests) of Lattice Semiconductor Corporation and/or its affiliates. All rights are reserved. You are permitted to use this document and any information contained therein expressly and only for bona fide non-commercial evaluation of products and/or services from Lattice Semiconductor Corporation or its affiliates; and only in connection with your bona fide consideration of purchase or license of products or services from Lattice Semiconductor Corporation or its affiliates, and only in accordance with the terms and conditions stipulated. Contents, (in whole or in part) may not be reproduced, downloaded, disseminated, published, or transferred in any form or by any means, except with the prior written permission of Lattice Semiconductor Corporation and/or its affiliates. Copyright infringement is a violation of federal law subject to criminal and civil penalties. You have no right to copy, modify, create derivative works of, transfer, sublicense, publicly display, distribute or otherwise make these materials available, in whole or in part, to any third party. You are not permitted to reverse engineer, disassemble, or decompile any device or object code provided herewith. Lattice Semiconductor Corporation reserves the right to revoke these permissions and require the destruction or return of any and all Lattice Semiconductor Corporation proprietary materials and/or data.

#### Patents

The subject matter described herein may contain one or more inventions claimed in patents or patents pending owned by Lattice Semiconductor Corporation and/or its affiliates.

#### **Trademark Acknowledgment**

Lattice Semiconductor Corporation<sup>®</sup>, the Lattice Semiconductor logo, Silicon Image<sup>®</sup>, the Silicon Image logo, Instaport<sup>®</sup>, the Instaport logo, InstaPrevue<sup>®</sup>, Simplay<sup>®</sup>, Simplay HD<sup>®</sup>, the Simplay HD logo, Simplay Labs<sup>™</sup>, the Simplay Labs logo, the SiBEAM Snap<sup>™</sup>, the SiBEAM Snap logo, UltraGig<sup>™</sup>, the UltraGig logo are trademarks or registered trademarks of Lattice Semiconductor Corporation in the United States and/or other countries. HDMI<sup>®</sup> and the HDMI logo with High-Definition Multimedia Interface are trademarks or registered trademarks of, and are used under license from, HDMI Licensing, LLC. in the United States or other countries. MHL<sup>®</sup> and the MHL logo with Mobile High-Definition Link are trademarks or registered trademarks of, and are used under license from, MHL, LLC. in the United States and/or other countries. WirelessHD<sup>®</sup>, the WirelessHD logo, WiHD<sup>®</sup> and the WiHD logo are trademarks, registered trademarks or service marks of SiBeam, Inc. in the United States or other countries. HDMI Licensing, LLC; Simplay Labs, LLC; and SiBeam, Inc. are wholly owned subsidiaries of Lattice Semiconductor Corporation.

All other trademarks and registered trademarks are the property of their respective owners in the United States or other countries. The absence of a trademark symbol does not constitute a waiver of Lattice Semiconductor's trademarks or other intellectual property rights with regard to a product name, logo or slogan.

#### **Export Controlled Document**

This document contains materials that are subject to the U.S. Export Administration Regulations and may also be subject to additional export control laws and regulations (collectively "Export Laws") and may be used only in compliance with such Export Laws. Unless otherwise authorized by an officer of Lattice Semiconductor Corporation in writing, this document and the information contained herein (a) may not be used in relation to nuclear, biological or chemical weapons, or missiles capable of delivering these weapons, and (b) may not be re-exported or otherwise transferred to a third party who is known or suspected to be involved in relation to nuclear, biological or chemical weapons, or missiles capable of delivering these weapons, or to any sanctioned persons or entities.

#### **Further Information**

To request other materials, documentation, and information, contact your local Lattice Semiconductor sales office or visit the Lattice Semiconductor web site at <u>www.latticesemi.com</u>.

#### Disclaimers

These materials are provided on an "AS IS" basis. Lattice Semiconductor Corporation and its affiliates disclaim all representations and warranties (express, implied, statutory or otherwise), including but not limited to: (i) all implied warranties of merchantability, fitness for a particular purpose, and/or non-infringement of third party rights; (ii) all warranties arising out of course-of-dealing, usage, and/or trade; and (iii) all warranties that the information or results provided in, or that may be obtained from use of, the materials are accurate, reliable, complete, up-to-date, or produce specific outcomes. Lattice Semiconductor Corporation and its affiliates assume no liability or responsibility for any errors or omissions in these materials, makes no commitment or warranty to correct any such errors or omissions or update or keep current the information contained in these materials, and expressly disclaims all direct, indirect, special, incidental, consequential, reliance and punitive damages, including WITHOUT LIMITATION any loss of profits arising out of your access to, use or interpretation of, or actions taken or not taken based on the content of these materials. Lattice Semiconductor Corporation and its affiliates reserve the right, without notice, to periodically modify the information in these materials, and to add to, delete, and/or change any of this information.

#### **Products and Services**

The products and services described in these materials, and any other information, services, designs, know-how and/or products provided by Lattice Semiconductor Corporation and/or its affiliates are provided on "AS IS" basis, except to the extent that Lattice Semiconductor Corporation and/or its affiliates provides an applicable written limited warranty in its standard form license agreements, standard Terms and Conditions of Sale and Service or its other applicable standard form agreements, in which case such limited warranty shall apply and shall govern in lieu of all other warranties (express, statutory, or implied). EXCEPT FOR SUCH LIMITED WARRANTY, LATTICE SEMICONDUCTOR CORPORATION AND ITS AFFILIATES DISCLAIM ALL REPRESENTATIONS AND WARRANTIES (EXPRESS, IMPLIED, STATUTORY OR OTHERWISE), REGARDING THE INFORMATION, SERVICES, DESIGNS, KNOW-HOW AND PRODUCTS PROVIDED BY LATTICE SEMICONDUCTOR CORPORATION AND/OR ITS AFFILIATES, INCLUDING BUT NOT LIMITED TO, ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND/OR NON-INFRINGEMENT OF THIRD PARTY RIGHTS. YOU ACKNOWLEDGE AND AGREE THAT SUCH INFORMATION, SERVICES, DESIGNS, KNOW-HOW AND PRODUCTS HAVE NOT BEEN DESIGNED, TESTED, OR MANUFACTURED FOR USE OR RESALE IN SYSTEMS WHERE THE FAILURE, MALFUNCTION, OR ANY INACCURACY OF THESE ITEMS CARRIES A RISK OF DEATH OR SERIOUS BODILY INJURY, INCLUDING, BUT NOT LIMITED TO, USE IN NUCLEAR FACILITIES, AIRCRAFT NAVIGATION OR COMMUNICATION, EMERGENCY SYSTEMS, OR OTHER SYSTEMS WITH A SIMILAR DEGREE OF POTENTIAL HAZARD. NO PERSON IS AUTHORIZED TO MAKE ANY OTHER WARRANTY OR REPRESENTATION CONCERNING THE PERFORMANCE OF THE INFORMATION, PRODUCTS, KNOW-HOW, DESIGNS OR SERVICES OTHER THAN AS PROVIDED IN THESE TERMS AND CONDITIONS.

## Contents

| Acronyms in This Document                                   |    |

|-------------------------------------------------------------|----|

| 1. General Description                                      | 10 |

| 1.1. Features                                               | 10 |

| 2. Architecture                                             | 12 |

| 2.1. Overview                                               | 12 |

| 2.2. PFU Blocks                                             | 13 |

| 2.2.1. Slice                                                | 14 |

| 2.2.2. Modes of Operation                                   | 17 |

| 2.3. Routing                                                |    |

| 2.4. Clocking Structure                                     |    |

| 2.4.1. sysCLOCK PLL                                         |    |

| 2.5. Clock Distribution Network                             | 19 |

| 2.5.1. Primary Clocks                                       | 20 |

| 2.5.2. Edge Clock                                           | 21 |

| 2.6. Clock Dividers                                         |    |

| 2.7. DDRDLL                                                 |    |

| 2.8. sysMEM Memory                                          |    |

| 2.8.1. sysMEM Memory Block                                  |    |

| 2.8.2. Bus Size Matching                                    |    |

| 2.8.3. RAM Initialization and ROM Operation                 |    |

| 2.8.4. Memory Cascading                                     |    |

| 2.8.5. Single, Dual and Pseudo-Dual Port Modes              |    |

| 2.8.6. Memory Core Reset                                    |    |

| 2.9. sysDSP <sup>™</sup> Slice                              |    |

| 2.9.1. sysDSP Slice Approach Compared to General DSP        |    |

| 2.9.2. sysDSP Slice Architecture Features                   |    |

| 2.10. Programmable I/O Cells                                |    |

| 2.11. PIO                                                   |    |

| 2.11. Input Register Block                                  |    |

| 2.11.2. Output Register Block                               |    |

| 2.12. Tristate Register Block                               |    |

| 2.12. DDR Memory Support                                    |    |

| 2.13. DQS Grouping for DDR Memory                           |    |

| 2.13.2. DLL Calibrated DQS Delay and Control Block (DQSBUF) |    |

| 2.14. sysl/O Buffer                                         |    |

| 2.14. sysi/O Buffer Banks                                   |    |

| 2.14.1. Syst/O Burlet Balliss                               |    |

| 2.14.2. Typical syst/O f/O Benavior during Power-up         |    |

| 2.14.3. Supported syst/O Standards                          |    |

| 2.14.4. On-Chip Programmable Termination                    |    |

| 2.14.5. For socketing                                       |    |

| 2.15. SERDES and Physical County Sublayer                   |    |

|                                                             |    |

|                                                             |    |

| 2.15.3. SERDES Client Interface Bus                         |    |

| 2.16. Flexible Dual SERDES Architecture                     |    |

| 2.17. IEEE 1149.1-Compliant Boundary Scan Testability       |    |

| 2.18. Device Configuration                                  |    |

| 2.18.1. Enhanced Configuration Options                      |    |

| 2.18.2. Single Event Upset (SEU) Support                    |    |

| 2.18.3. On-Chip Oscillator                                  |    |

| 2.19. Density Shifting                                      |    |

| 3. DC and Switching Characteristics                         | 47 |

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

## Acronyms in This Document

A list of acronyms used in this document.

| ALUArithmetic Logic UnitBGABall Grid ArrayCDRClock and Data RecoveryCRCCycle Redundancy CodeDCCDynamic Clock ControlDCSDynamic Clock SelectDDRDouble Data RateDLLDelay-Locked LoopsDSPDigital Signal ProcessingEBREmbedded Block RAMECLKEdge ClockFFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Transistor-Transistor LogicLVTLLow Voltage Transistor-Transistor LogicLVTLPripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSERDESSerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access PortTDMTime D | Acronym | Definition                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------------------------|

| CDRClock and Data RecoveryCRCCycle Redundancy CodeDCCDynamic Clock ControlDCSDynamic Clock SelectDDRDouble Data RateDLLDelay-Locked LoopsDSPDigital Signal ProcessingEBREmbedded Block RAMECLKEdge ClockFFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Transistor-Transistor LogicLVTLLow Voltage Positive Emitter Coupled LogicLVTLLow Voltage Transistor-Transistor LogicLVTLPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                       | ALU     | Arithmetic Logic Unit                               |

| CRCCycle Redundancy CodeDCCDynamic Clock ControlDCSDynamic Clock SelectDDRDouble Data RateDLLDelay-Locked LoopsDSPDigital Signal ProcessingEBREmbedded Block RAMECLKEdge ClockFFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                               | BGA     | Ball Grid Array                                     |

| DCCDynamic Clock ControlDCSDynamic Clock SelectDDRDouble Data RateDLLDelay-Locked LoopsDSPDigital Signal ProcessingEBREmbedded Block RAMECLKEdge ClockFFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                       | CDR     | Clock and Data Recovery                             |

| DCSDynamic Clock SelectDDRDouble Data RateDLLDelay-Locked LoopsDSPDigital Signal ProcessingEBREmbedded Block RAMECLKEdge ClockFFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICSeralizer/DeserializerSERDESSerializer/DeserializerSELUSingle Event UpsetSERDESSerializer/DeserializerSELUSingle Port RAMSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                               | CRC     | Cycle Redundancy Code                               |

| DDRDouble Data RateDLLDelay-Locked LoopsDSPDigital Signal ProcessingEBREmbedded Block RAMECLKEdge ClockFFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICSERDES Client InterfaceSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                            | DCC     | Dynamic Clock Control                               |

| DLLDelay-Locked LoopsDSPDigital Signal ProcessingEBREmbedded Block RAMECLKEdge ClockFFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICSERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                         | DCS     | Dynamic Clock Select                                |

| DSPDigital Signal ProcessingEBREmbedded Block RAMECLKEdge ClockFFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICSERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                             | DDR     | Double Data Rate                                    |

| EBREmbedded Block RAMECLKEdge ClockFFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable Functional UnitPICSERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                          | DLL     | Delay-Locked Loops                                  |

| ECLKEdge ClockFFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTLLow Voltage Transistor-Transistor LogicLVTTLLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                              | DSP     | Digital Signal Processing                           |

| FFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                             | EBR     | Embedded Block RAM                                  |

| FIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable Functional UnitPICSERDES Client InterfaceSCISERDES Client InterfaceSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                          | ECLK    | Edge Clock                                          |

| FIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable Functional UnitPICSERDES Client InterfaceSCISERDES Client InterfaceSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                | FFT     | Fast Fourier Transforms                             |

| LVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                    | FIFO    | First In First Out                                  |

| LVDSLow-Voltage Differential SignalingLVPECLLow-Voltage Positive Emitter Coupled LogicLVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FIR     | Finite Impulse Response                             |

| LVPECLLow Voltage Positive Emitter Coupled LogicLVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LVCMOS  | Low-Voltage Complementary Metal Oxide Semiconductor |

| LVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LVDS    | Low-Voltage Differential Signaling                  |

| LUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LVPECL  | Low Voltage Positive Emitter Coupled Logic          |

| MLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LVTTL   | Low Voltage Transistor-Transistor Logic             |

| PCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LUT     | Look Up Table                                       |

| PCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MLVDS   | Multipoint Low-Voltage Differential Signaling       |

| PCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PCI     | Peripheral Component Interconnect                   |

| PDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PCS     | Physical Coding Sublayer                            |

| PFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PCLK    | Primary Clock                                       |

| PICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PDPR    | Pseudo Dual Port RAM                                |

| PLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PFU     | Programmable Functional Unit                        |

| PORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PIC     | Programmable I/O Cells                              |

| SCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PLL     | Phase-Locked Loops                                  |

| SERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | POR     | Power On Reset                                      |

| SEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SCI     | SERDES Client Interface                             |

| SLVS     Scalable Low-Voltage Signaling       SPI     Serial Peripheral Interface       SPR     Single Port RAM       SRAM     Static Random-Access Memory       TAP     Test Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SERDES  | Serializer/Deserializer                             |

| SPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SEU     | Single Event Upset                                  |

| SPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SLVS    | Scalable Low-Voltage Signaling                      |

| SRAM     Static Random-Access Memory       TAP     Test Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SPI     | Serial Peripheral Interface                         |

| TAP Test Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SPR     | Single Port RAM                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SRAM    | Static Random-Access Memory                         |

| TDM Time Division Multiplexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ТАР     | Test Access Port                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TDM     | Time Division Multiplexing                          |

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

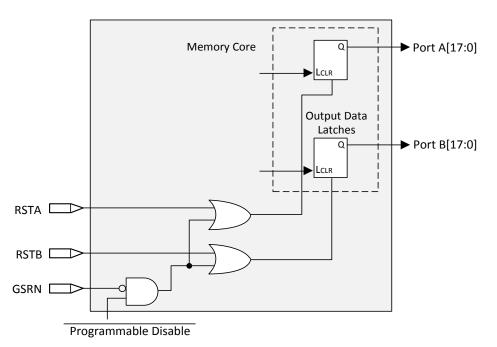

### 2.8.6. Memory Core Reset

The memory array in the EBR utilizes latches at the A and B output ports. These latches can be reset asynchronously or synchronously. RSTA and RSTB are local signals, which reset the output latches associated with Port A and Port B, respectively. The Global Reset (GSRN) signal can reset both ports. The output data latches and associated resets for both ports are as shown in Figure 2.12.

Figure 2.12. Memory Core Reset

For further information on the sysMEM EBR block, see the list of technical documentation in Supplemental Information section on page 102.

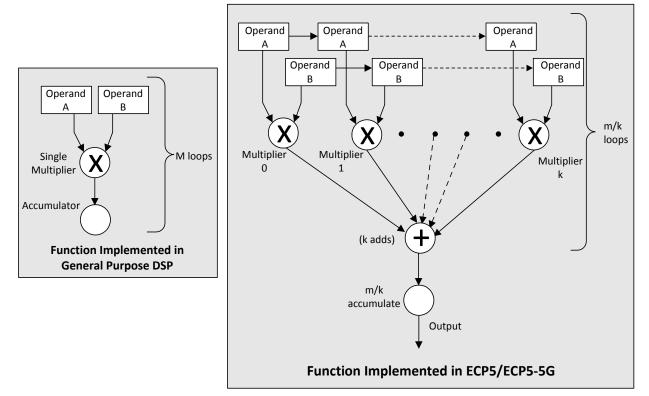

### 2.9. sysDSP<sup>™</sup> Slice

The ECP5/ECP5-5G family provides an enhanced sysDSP architecture, making it ideally suited for low-cost, high-performance Digital Signal Processing (DSP) applications. Typical functions used in these applications are Finite Impulse Response (FIR) filters, Fast Fourier Transforms (FFT) functions, Correlators, Reed-Solomon/Turbo/Convolution encoders and decoders. These complex signal processing functions use similar building blocks such as multiply-adders and multiply-accumulators.

### 2.9.1. sysDSP Slice Approach Compared to General DSP

Conventional general-purpose DSP chips typically contain one to four (Multiply and Accumulate) MAC units with fixed data-width multipliers; this leads to limited parallelism and limited throughput. Their throughput is increased by higher clock speeds. In the ECP5/ECP5-5G device family, there are many DSP slices that can be used to support different data widths. This allows designers to use highly parallel implementations of DSP functions. Designers can optimize DSP performance vs. area by choosing appropriate levels of parallelism. Figure 2.13 compares the fully serial implementation to the mixed parallel and serial implementation.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Figure 2.13. Comparison of General DSP and ECP5/ECP5-5G Approaches

### 2.9.2. sysDSP Slice Architecture Features

The ECP5/ECP5-5G sysDSP Slice has been significantly enhanced to provide functions needed for advanced processing applications. These enhancements provide improved flexibility and resource utilization.

The ECP5/ECP5-5G sysDSP Slice supports many functions that include the following:

- Symmetry support. The primary target application is wireless. 1D Symmetry is useful for many applications that use FIR filters when their coefficients have symmetry or asymmetry characteristics. The main motivation for using 1D symmetry is cost/size optimization. The expected size reduction is up to 2x.

- Odd mode Filter with Odd number of taps

- Even mode Filter with Even number of taps

- Two dimensional (2D) symmetry mode supports 2D filters for mainly video applications

- Dual-multiplier architecture. Lower accumulator overhead to half and the latency to half compared to single multiplier architecture

- Fully cascadable DSP across slices. Support for symmetric, asymmetric and non-symmetric filters.

- Multiply (one 18x36, two 18x18 or four 9x9 Multiplies per Slice)

- Multiply (36x36 by cascading across two sysDSP slices)

- Multiply Accumulate (supports one 18x36 multiplier result accumulation or two 18x18 multiplier result accumulation)

- Two Multiplies feeding one Accumulate per cycle for increased processing with lower latency (two 18x18 Multiplies feed into an accumulator that can accumulate up to 52 bits)

- Pipeline registers

- 1D Symmetry support. The coefficients of FIR filters have symmetry or negative symmetry characteristics.

- Odd mode Filter with Odd number of taps

- Even mode Filter with Even number of taps

- 2D Symmetry support. The coefficients of 2D FIR filters have symmetry or negative symmetry characteristics.

- 3\*3 and 3\*5 Internal DSP Slice support

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

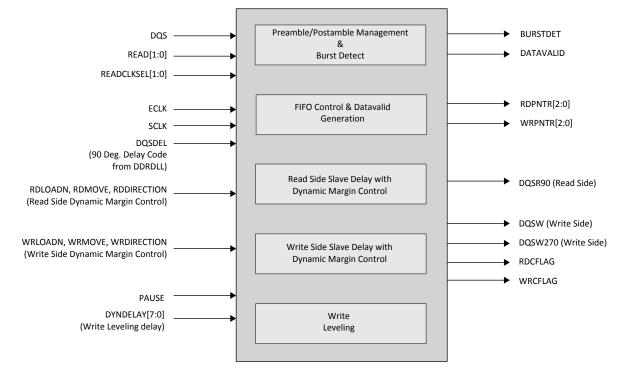

Figure 2.24. DQS Control and Delay Block (DQSBUF)

| Table 2.11 | DQSBUF | <b>Port List</b> | Description |

|------------|--------|------------------|-------------|

|------------|--------|------------------|-------------|

| Name                         | Туре   | Description                                                                                    |

|------------------------------|--------|------------------------------------------------------------------------------------------------|

| DQS                          | Input  | DDR memory DQS strobe                                                                          |

| READ[1:0]                    | Input  | Read Input from DDR Controller                                                                 |

| READCLKSEL[1:0]              | Input  | Read pulse selection                                                                           |

| SCLK                         | Input  | Slow System Clock                                                                              |

| ECLK                         | Input  | High Speed Edge Clock (same frequency as DDR memory)                                           |

| DQSDEL                       | Input  | 90° Delay Code from DDRDLL                                                                     |

| RDLOADN, RDMOVE, RDDIRECTION | Input  | Dynamic Margin Control ports for Read delay                                                    |

| WRLOADN, WRMOVE, WRDIRECTION | Input  | Dynamic Margin Control ports for Write delay                                                   |

| PAUSE                        | Input  | Used by DDR Controller to Pause write side signals during DDRDLL Code update or Write Leveling |

| DYNDELAY[7:0]                | Input  | Dynamic Write Leveling Delay Control                                                           |

| DQSR90                       | Output | 90° delay DQS used for Read                                                                    |

| DQSW270                      | Output | 90° delay clock used for DQ Write                                                              |

| DQSW                         | Output | Clock used for DQS Write                                                                       |

| RDPNTR[2:0]                  | Output | Read Pointer for IFIFO module                                                                  |

| WRPNTR[2:0]                  | Output | Write Pointer for IFIFO module                                                                 |

| DATAVALID                    | Output | Signal indicating start of valid data                                                          |

| BURSTDET                     | Output | Burst Detect indicator                                                                         |

| RDFLAG                       | Output | Read Dynamic Margin Control output to indicate max value                                       |

| WRFLAG                       | Output | Write Dynamic Margin Control output to indicate max value                                      |

<sup>© 2014-2018</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

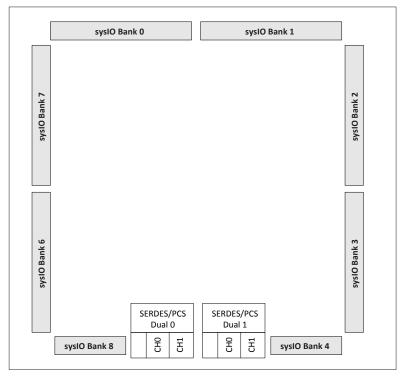

Figure 2.27. SERDES/PCS Duals (LFE5UM/LFE5UM5G-85)

| Standard                                       | Data Rate (Mb/s)                                           | Number of General/Link Width | Encoding Style |

|------------------------------------------------|------------------------------------------------------------|------------------------------|----------------|

| PCI Express 1.1 and 2.0                        | 2500                                                       | x1, x2, x4                   | 8b10b          |

| 2.02                                           | 5000 <sup>2</sup>                                          | x1, x2                       | 8b10b          |

| Gigabit Ethernet                               | 1250                                                       | x1                           | 8b10b          |

| COMU                                           | 1250                                                       | x1                           | 8b10b          |

| SGMII                                          | 2500                                                       | x1                           | 8b10b          |

| XAUI                                           | 3125                                                       | x4                           | 8b10b          |

| CPRI-1<br>CPRI-2<br>CPRI-3<br>CPRI-4<br>CPRI-5 | 614.4<br>1228.8<br>2457.6<br>3072.0<br>4915.2 <sup>2</sup> | x1                           | 8b10b          |

| SD-SDI (259M, 344M) 1                          | 270                                                        | x1                           | NRZI/Scrambled |

| HD-SDI (292M)                                  | 1483.5<br>1485                                             | x1                           | NRZI/Scrambled |

| 3G-SDI (424M)                                  | 2967<br>2970                                               | x1                           | NRZI/Scrambled |

|                                                | 5000                                                       | _                            | _              |

| JESD204A/B                                     | 3125                                                       | x1                           | 8b/10b         |

### Notes:

1. For SD-SDI rate, the SERDES is bypassed and SERDES input signals are directly connected to the FPGA routing.

2. For ECP5-5G family devices only.

#### Table 3.10. ECP5-5G

| Symbol                             | Description                                              | Тур | Max | Unit |  |

|------------------------------------|----------------------------------------------------------|-----|-----|------|--|

| Standby (Power Down)               |                                                          |     |     |      |  |

| I <sub>CCA-SB</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 4   | 9.5 | mA   |  |

| I <sub>CCHRX-SB</sub> <sup>4</sup> | V <sub>CCHRX</sub> , Input Buffer Current (Per Channel)  | _   | 0.1 | mA   |  |

| I <sub>CCHTX-SB</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | _   | 0.9 | mA   |  |

| Operating (Da                      | ata Rate = 5 Gb/s)                                       |     |     |      |  |

| I <sub>CCA-OP</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 58  | 67  | mA   |  |

| I <sub>CCHRX-OP</sub> <sup>5</sup> | V <sub>CCHRX</sub> , Input Buffer Current (Per Channel)  | 0.4 | 0.5 | mA   |  |

| I <sub>CCHTX-OP</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | 10  | 13  | mA   |  |

| Operating (D                       | ata Rate = 3.2 Gb/s)                                     |     |     |      |  |

| I <sub>CCA-OP</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 48  | 57  | mA   |  |

| I <sub>CCHRX-OP</sub> <sup>5</sup> | V <sub>CCHRX</sub> , Input Buffer Current (Per Channel)  | 0.4 | 0.5 | mA   |  |

| I <sub>CCHTX-OP</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | 10  | 13  | mA   |  |

| Operating (Da                      | ata Rate = 2.5 Gb/s)                                     |     |     |      |  |

| I <sub>CCA-OP</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 44  | 53  | mA   |  |

| I <sub>CCHRX-OP</sub> <sup>5</sup> | V <sub>CCHRx</sub> , Input Buffer Current (Per Channel)  | 0.4 | 0.5 | mA   |  |

| I <sub>CCHTX-OP</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | 10  | 13  | mA   |  |

| Operating (Da                      | ata Rate = 1.25 Gb/s)                                    |     |     |      |  |

| I <sub>CCA-OP</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 36  | 46  | mA   |  |

| I <sub>CCHRX-OP</sub> <sup>5</sup> | V <sub>CCHRX</sub> , Input Buffer Current (Per Channel)  | 0.4 | 0.5 | mA   |  |

| I <sub>CCHTX-OP</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | 10  | 13  | mA   |  |

| Operating (D                       | ata Rate = 270 Mb/s)                                     |     |     |      |  |

| I <sub>CCA-OP</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 30  | 40  | mA   |  |

| I <sub>CCHRX-OP</sub> <sup>5</sup> | V <sub>CCHRX</sub> , Input Buffer Current (Per Channel)  | 0.4 | 0.5 | mA   |  |

| I <sub>CCHTX-OP</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | 8   | 10  | mA   |  |

Notes:

1. Rx Equalization enabled, Tx De-emphasis (pre-cursor and post-cursor) disabled

2. Per Channel current is calculated with both channels on in a Dual, and divide current by two. If only one channel is on, current will be higher.

3. To calculate with Tx De-emphasis enabled, use the Diamond Power Calculator tool.

4. For ICCHRX-SB, during Standby, input termination on Rx are disabled.

5. For ICCHRX-OP, during operational, the max specified when external AC coupling is used. If externally DC coupled, the power is based on current pulled down by external driver when the input is driven to LOW.

### 3.14.4. LVDS25E

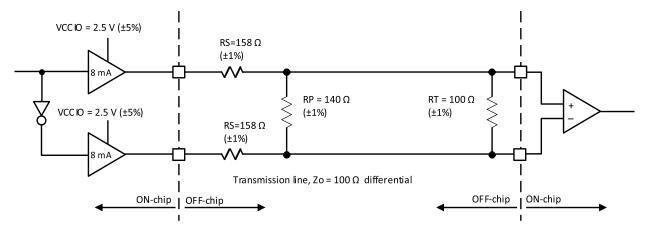

The top and bottom sides of ECP5/ECP5-5G devices support LVDS outputs via emulated complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The scheme shown in Figure 3.1 is one possible solution for point-to-point signals.

Figure 3.1. LVDS25E Output Termination Example

### Table 3.14. LVDS25E DC Conditions

| Parameter         | Description                    | Typical | Unit |

|-------------------|--------------------------------|---------|------|

| V <sub>CCIO</sub> | Output Driver Supply (±5%)     | 2.50    | V    |

| Z <sub>OUT</sub>  | Driver Impedance               | 20      | Ω    |

| Rs                | Driver Series Resistor (±1%)   | 158     | Ω    |

| R <sub>P</sub>    | Driver Parallel Resistor (±1%) | 140     | Ω    |

| R <sub>T</sub>    | Receiver Termination (±1%)     | 100     | Ω    |

| V <sub>OH</sub>   | Output High Voltage            | 1.43    | V    |

| V <sub>OL</sub>   | Output Low Voltage             | 1.07    | V    |

| V <sub>OD</sub>   | Output Differential Voltage    | 0.35    | V    |

| V <sub>CM</sub>   | Output Common Mode Voltage     | 1.25    | V    |

| ZBACK             | Back Impedance                 | 100.5   | Ω    |

| I <sub>DC</sub>   | DC Output Current              | 6.03    | mA   |

Note: For input buffer, see LVDS Table 3.13 on page 55.

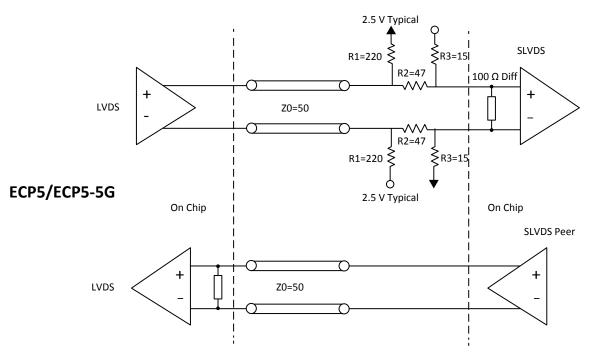

### 3.14.8. SLVS

Scalable Low-Voltage Signaling (SLVS) is based on a point-to-point signaling method defined in the JEDEC JESD8-13 (SLVS-400) standard. This standard evolved from the traditional LVDS standard and relies on the advantage of its use of smaller voltage swings and a lower common-mode voltage. The 200 mV (400 mV p-p) SLVS swing contributes to a reduction in power.

The ECP5/ECP5-5G devices can receive differential input up to 800 Mb/s with its LVDS input buffer. This LVDS input buffer is used to meet the SLVS input standard specified by the JEDEC standard. The SLVS output parameters are compared to ECP5/ECP5-5G LVDS input parameters, as listed in Table 3.18.

### Table 3.18. Input to SLVS

| Parameter                  | ECP5/ECP5-5G LVDS Input | SLVS Output | Unit |

|----------------------------|-------------------------|-------------|------|

| Vcm (min)                  | 50                      | 150         | mV   |

| Vcm (max)                  | 2350                    | 250         | mV   |

| Differential Voltage (min) | 100                     | 140         | mV   |

| Differential Voltage (max) | -                       | 270         | mV   |

ECP5/ECP5-5G does not support SLVS output. However, SLVS output can be created using ECP5/ECP5-5G LVDS outputs by level shift to meet the low Vcm/Vod levels required by SLVS. Figure 3.5 shows how the LVDS output can be shifted external to meet SLVS levels.

Figure 3.5. SLVS Interface

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

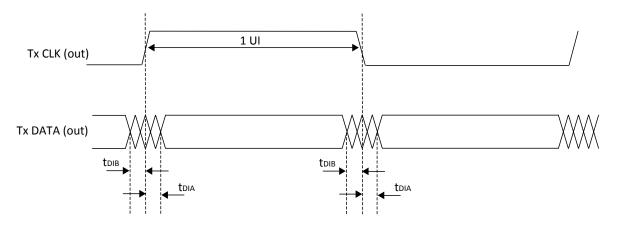

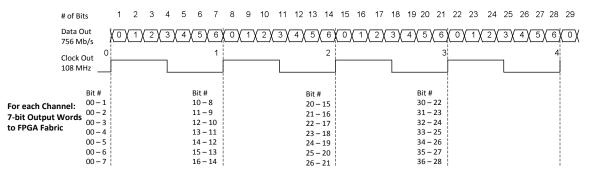

Figure 3.9. Transmit TX.CLK.Aligned Waveforms

#### Receiver – Shown for one LVDS Channel

#### Transmitter - Shown for one LVDS Channel

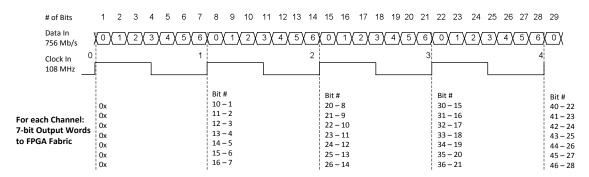

Figure 3.10. DDRX71 Video Timing Waveforms

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

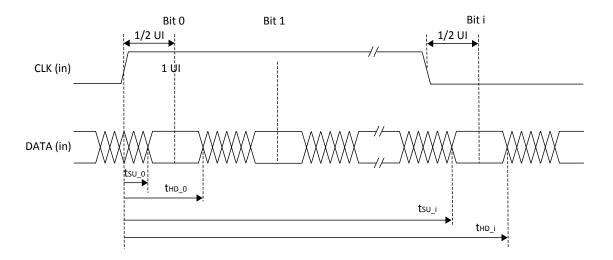

Figure 3.11. Receiver DDRX71\_RX Waveforms

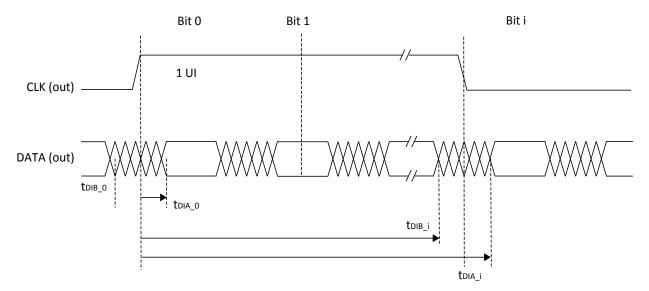

Figure 3.12. Transmitter DDRX71\_TX Waveforms

### 3.19. sysCLOCK PLL Timing

Over recommended operating conditions.

| Parameter                      | Descriptions                                                         | Conditions                 | Min   | Max   | Units      |

|--------------------------------|----------------------------------------------------------------------|----------------------------|-------|-------|------------|

| f <sub>IN</sub>                | Input Clock Frequency (CLKI, CLKFB)                                  | _                          | 8     | 400   | MHz        |

| f <sub>out</sub>               | Output Clock Frequency (CLKOP, CLKOS)                                | —                          | 3.125 | 400   | MHz        |

| f <sub>vco</sub>               | PLL VCO Frequency                                                    | —                          | 400   | 800   | MHz        |

| $f_{\text{PFD}}{}^3$           | Phase Detector Input Frequency                                       | _                          | 10    | 400   | MHz        |

| AC Characteris                 | itics                                                                |                            |       |       |            |

| t <sub>DT</sub>                | Output Clock Duty Cycle                                              | _                          | 45    | 55    | %          |

| t <sub>PH4</sub>               | Output Phase Accuracy                                                | _                          | -5    | 5     | %          |

|                                |                                                                      | f <sub>o∪T</sub> ≥ 100 MHz | _     | 100   | ps p-p     |

|                                | Output Clock Period Jitter                                           | f <sub>о∪т</sub> < 100 MHz | _     | 0.025 | UIPP       |

|                                |                                                                      | f <sub>o∪T</sub> ≥ 100 MHz | _     | 200   | ps p-p     |

| t <sub>opjit</sub> 1           | Output Clock Cycle-to-Cycle Jitter                                   | f <sub>о∪т</sub> < 100 MHz | _     | 0.050 | UIPP       |

|                                | Output Clock Phase Jitter                                            | f <sub>PFD</sub> ≥ 100 MHz | _     | 200   | ps p-p     |

|                                |                                                                      | f <sub>PFD</sub> < 100 MHz | _     | 0.011 | UIPP       |

| t <sub>spo</sub>               | Static Phase Offset                                                  | Divider ratio =<br>integer | _     | 400   | ps p-p     |

| t <sub>w</sub>                 | Output Clock Pulse Width                                             | At 90% or 10%              | 0.9   | _     | ns         |

| t <sub>LOCK</sub> <sup>2</sup> | PLL Lock-in Time                                                     | _                          | _     | 15    | ms         |

| t <sub>UNLOCK</sub>            | PLL Unlock Time                                                      | _                          | _     | 50    | ns         |