Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                              |

|--------------------------------|------------------------------------------------------------------------------|

| Product Status                 | Active                                                                       |

| Number of LABs/CLBs            | 21000                                                                        |

| Number of Logic Elements/Cells | 84000                                                                        |

| Total RAM Bits                 | 3833856                                                                      |

| Number of I/O                  | 365                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.045V ~ 1.155V                                                              |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                              |

| Package / Case                 | 756-FBGA                                                                     |

| Supplier Device Package        | 756-CABGA (27x27)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe5u-85f-8bg756c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

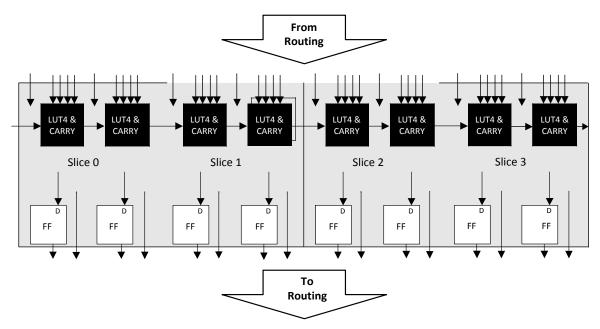

Figure 2.2. PFU Diagram

### 2.2.1. Slice

Each slice contains two LUT4s feeding two registers. In Distributed SRAM mode, Slice 0 through Slice 2 are configured as distributed memory, and Slice 3 is used as Logic or ROM. Table 2.1 shows the capability of the slices along with the operation modes they enable. In addition, each PFU contains logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7 and LUT8. There is control logic to perform set/reset functions (programmable as synchronous/ asynchronous), clock select, chip-select and wider RAM/ROM functions.

Table 2.1. Resources and Modes Available per Slice

| Slice   | PFU (Used in Distributed SRAM) |                    | PFU (Not used as Distributed SRAM) |                    |  |

|---------|--------------------------------|--------------------|------------------------------------|--------------------|--|

| Siice   | Resources                      | Modes              | Resources                          | Modes              |  |

| Slice 0 | 2 LUT4s and 2 Registers        | RAM                | 2 LUT4s and 2 Registers            | Logic, Ripple, ROM |  |

| Slice 1 | 2 LUT4s and 2 Registers        | RAM                | 2 LUT4s and 2 Registers            | Logic, Ripple, ROM |  |

| Slice 2 | 2 LUT4s and 2 Registers        | RAM                | 2 LUT4s and 2 Registers            | Logic, Ripple, ROM |  |

| Slice 3 | 2 LUT4s and 2 Registers        | Logic, Ripple, ROM | 2 LUT4s and 2 Registers            | Logic, Ripple, ROM |  |

Figure 2.3 shows an overview of the internal logic of the slice. The registers in the slice can be configured for positive/negative and edge triggered or level sensitive clocks.

Each slice has 14 input signals, 13 signals from routing and one from the carry-chain (from the adjacent slice or PFU). There are five outputs, four to routing and one to carry-chain (to the adjacent PFU). There are two inter slice/PFU output signals that are used to support wider LUT functions, such as LUT6, LUT7 and LUT8. Table 2.2 and Figure 2.3 list the signals associated with all the slices. Figure 2.4 on page 16 shows the connectivity of the inter-slice/PFU signals that support LUT5, LUT6, LUT7 and LUT8.

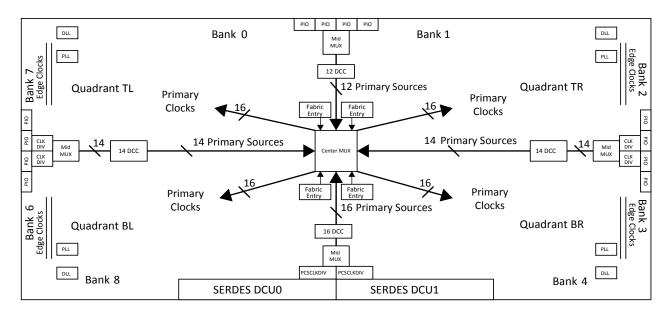

Figure 2.6. LFE5UM/LFE5UM5G-85 Clocking

### 2.5.1. Primary Clocks

The ECP5/ECP5-5G device family provides low-skew, high fan-out clock distribution to all synchronous elements in the FPGA fabric through the Primary Clock Network.

The primary clock network is divided into four clocking quadrants: Top Left (TL), Bottom Left (BL), Top Right (TR), and Bottom Right (BR). Each of these quadrants has 16 clocks that can be distributed to the fabric in the quadrant.

The Lattice Diamond software can automatically route each clock to one of the four quadrants up to a maximum of 16 clocks per quadrant. The user can change how the clocks are routed by specifying a preference in the Lattice Diamond software to locate the clock to specific. The ECP5/ECP5-5G device provides the user with a maximum of 64 unique clock input sources that can be routed to the primary Clock network.

Primary clock sources are:

- Dedicated clock input pins

- PLL outputs

- CLKDIV outputs

- Internal FPGA fabric entries (with minimum general routing)

- SERDES/PCS/PCSDIV clocks

- OSC clock

These sources are routed to one of four clock switches called a Mid Mux. The outputs of the Mid MUX are routed to the center of the FPGA where another clock switch, called the Center MUX, is used to route the primary clock sources to primary clock distribution to the ECP5/ECP5-5G fabric. These routing muxes are shown in Figure 2.6. Since there is a maximum of 60 unique clock input sources to the clocking quadrants, there are potentially 64 unique clock domains that can be used in the ECP5/ECP5-5G Device. For more information about the primary clock tree and connections, refer to ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263).

### 2.5.1.1. Dynamic Clock Control

The Dynamic Clock Control (DCC), Quadrant Clock enable/disable feature allows internal logic control of the quadrant primary clock network. When a clock network is disabled, the clock signal is static and not toggle. All the logic fed by that clock will not toggle, reducing the overall power consumption of the device. The disable function will not create glitch and increase the clock latency to the primary clock network.

This DCC controls the clock sources from the Primary CLOCK MIDMUX before they are fed to the Primary Center MUXs that drive the quadrant clock network. For more information about the DCC, refer to ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263).

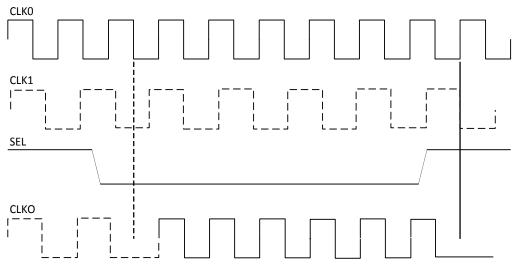

#### 2.5.1.2. Dynamic Clock Select

The Dynamic Clock Select (DCS) is a smart multiplexer function available in the primary clock routing. It switches between two independent input clock sources. Depending on the operation modes, it switches between two (2) independent input clock sources either with or without any glitches. This is achieved regardless of when the select signal is toggled. Both input clocks must be running to achieve functioning glitch-less DCS output clock, but it is not required running clocks when used as non-glitch-less normal clock multiplexer.

There are two DCS blocks per device that are fed to all quadrants. The inputs to the DCS block come from all the output of MIDMUXs and Clock from CIB located at the center of the PLC array core. The output of the DCS is connected to one of the inputs of Primary Clock Center MUX.

Figure 2.7 shows the timing waveforms of the default DCS operating mode. The DCS block can be programmed to other modes. For more information about the DCS, refer to ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263).

Figure 2.7. DCS Waveforms

# 2.5.2. Edge Clock

ECP5/ECP5-5G devices have a number of high-speed edge clocks that are intended for use with the PIOs in the implementation of high-speed interfaces. There are two ECLK networks per bank IO on the Left and Right sides of the devices.

Each Edge Clock can be sourced from the following:

- Dedicated Clock input pins (PCLK)

- DLLDEL output (Clock delayed by 90o)

- PLL outputs (CLKOP and CLKOS)

- ECLKBRIDGE

- Internal Nodes

**Table 2.6. sysMEM Block Configurations**

| Memory Mode      | Configurations |

|------------------|----------------|

|                  | 16,384 x 1     |

|                  | 8,192 x 2      |

| Cinalo Dort      | 4,096 x 4      |

| Single Port      | 2,048 x 9      |

|                  | 1,024 x 18     |

|                  | 512 x 36       |

|                  | 16,384 x 1     |

|                  | 8,192 x 2      |

| True Dual Port   | 4,096 x 4      |

|                  | 2,048 x 9      |

|                  | 1,024 x 18     |

|                  | 16,384 x 1     |

|                  | 8,192 x 2      |

| Pseudo Dual Port | 4,096 x 4      |

| Pseudo Duai Port | 2,048 x 9      |

|                  | 1,024 x 18     |

|                  | 512 x 36       |

### 2.8.2. Bus Size Matching

All of the multi-port memory modes support different widths on each of the ports. The RAM bits are mapped LSB word 0 to MSB word 0, LSB word 1 to MSB word 1, and so on. Although the word size and number of words for each port varies, this mapping scheme applies to each port.

### 2.8.3. RAM Initialization and ROM Operation

If desired, the contents of the RAM can be pre-loaded during device configuration. By preloading the RAM block during the chip configuration cycle and disabling the write controls, the sysMEM block can also be utilized as a ROM.

#### 2.8.4. **Memory Cascading**

Larger and deeper blocks of RAM can be created using EBR sysMEM Blocks. Typically, the Lattice design tools cascade memory transparently, based on specific design inputs.

### 2.8.5. Single, Dual and Pseudo-Dual Port Modes

In all the sysMEM RAM modes the input data and address for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the output.

EBR memory supports the following forms of write behavior for single port or dual port operation:

- **Normal** Data on the output appears only during a read cycle. During a write cycle, the data (at the current address) does not appear on the output. This mode is supported for all data widths.

- Write Through A copy of the input data appears at the output of the same port during a write cycle. This mode is supported for all data widths.

- **Read-Before-Write** When new data is written, the old content of the address appears at the output. This mode is supported for x9, x18, and x36 data widths.

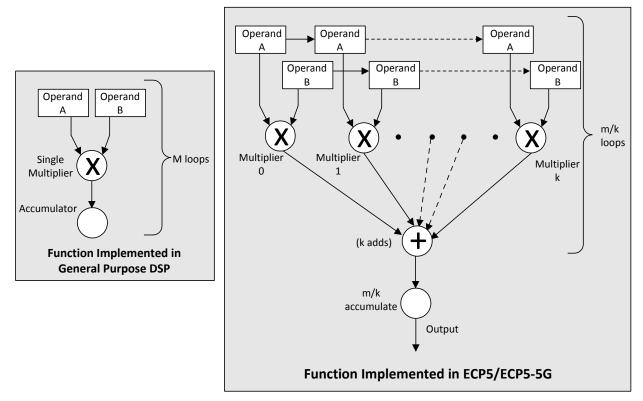

Figure 2.13. Comparison of General DSP and ECP5/ECP5-5G Approaches

## 2.9.2. sysDSP Slice Architecture Features

The ECP5/ECP5-5G sysDSP Slice has been significantly enhanced to provide functions needed for advanced processing applications. These enhancements provide improved flexibility and resource utilization.

The ECP5/ECP5-5G sysDSP Slice supports many functions that include the following:

- Symmetry support. The primary target application is wireless. 1D Symmetry is useful for many applications that use FIR filters when their coefficients have symmetry or asymmetry characteristics. The main motivation for using 1D symmetry is cost/size optimization. The expected size reduction is up to 2x.

- Odd mode Filter with Odd number of taps

- Even mode Filter with Even number of taps

- Two dimensional (2D) symmetry mode supports 2D filters for mainly video applications

- Dual-multiplier architecture. Lower accumulator overhead to half and the latency to half compared to single multiplier architecture

- Fully cascadable DSP across slices. Support for symmetric, asymmetric and non-symmetric filters.

- Multiply (one 18x36, two 18x18 or four 9x9 Multiplies per Slice)

- Multiply (36x36 by cascading across two sysDSP slices)

- Multiply Accumulate (supports one 18x36 multiplier result accumulation or two 18x18 multiplier result accumulation)

- Two Multiplies feeding one Accumulate per cycle for increased processing with lower latency (two 18x18 Multiplies feed into an accumulator that can accumulate up to 52 bits)

- Pipeline registers

- 1D Symmetry support. The coefficients of FIR filters have symmetry or negative symmetry characteristics.

- Odd mode Filter with Odd number of taps

- Even mode Filter with Even number of taps

- 2D Symmetry support. The coefficients of 2D FIR filters have symmetry or negative symmetry characteristics.

- 3\*3 and 3\*5 Internal DSP Slice support

### 2.11. **PIO**

The PIO contains three blocks: an input register block, output register block, and tristate register block. These blocks contain registers for operating in a variety of modes along with the necessary clock and selection logic.

### 2.11.1. Input Register Block

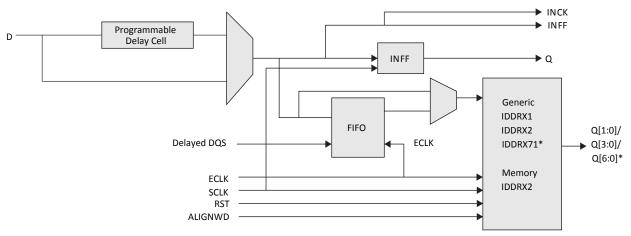

The input register blocks for the PIOs on all edges contain delay elements and registers that can be used to condition high-speed interface signals before they are passed to the device core. In addition, the input register blocks for the PIOs on the left and right edges include built-in FIFO logic to interface to DDR and LPDDR memory.

The Input register block on the right and left sides includes gearing logic and registers to implement IDDRX1 and IDDRX2 functions. With two PICs sharing the DDR register path, it can also implement IDDRX71 function used for 7:1 LVDS interfaces. It uses three sets of registers to shift, update, and transfer to implement gearing and the clock domain transfer. The first stage registers samples the high-speed input data by the high-speed edge clock on its rising and falling edges. The second stage registers perform data alignment based on the control signals. The third stage pipeline registers pass the data to the device core synchronized to the low-speed system clock. The top side of the device supports IDDRX1 gearing function. For more information on gearing function, refer to ECP5 and ECP5-5G High-Speed I/O Interface (TN1265).

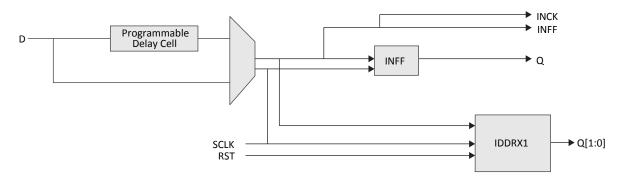

Figure 2.17 shows the input register block for the PIOs on the top edge.

Figure 2.17. Input Register Block for PIO on Top Side of the Device

Figure 2.18 shows the input register block for the PIOs located on the left and right edges.

<sup>\*</sup>For 7:1 LVDS interface only. It is required to use PIO pair pins (PIOA/B or PIOC/D).

Figure 2.18. Input Register Block for PIO on Left and Right Side of the Device

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

32

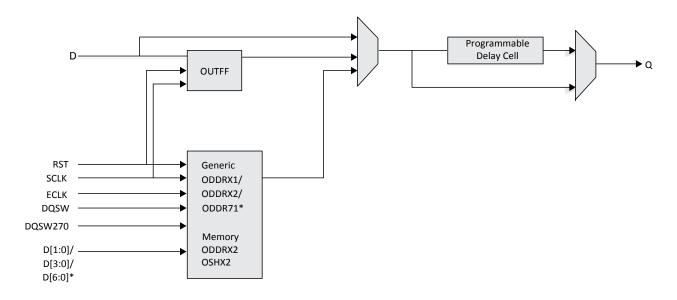

\*For 7:1 LVDS interface only. It is required to use PIO pair pins PIOA/B.

Figure 2.20. Output Register Block on Left and Right Sides

**Table 2.9. Output Block Port Description**

| Name                  | Туре   | Description                                                         |  |  |

|-----------------------|--------|---------------------------------------------------------------------|--|--|

| Q                     | Output | High Speed Data Output                                              |  |  |

| D                     | Input  | Data from core to output SDR register                               |  |  |

| D[1:0]/D[3:0]/ D[6:0] | Input  | Low Speed Data from device core to output DDR register              |  |  |

| RST                   | Input  | Reset to the Output Block                                           |  |  |

| SCLK                  | Input  | Slow Speed System Clock                                             |  |  |

| ECLK                  | Input  | High Speed Edge Clock                                               |  |  |

| DQSW                  | Input  | Clock from DQS control Block used to generate DDR memory DQS output |  |  |

| DQSW270               | Input  | Clock from DQS control Block used to generate DDR memory DQ output  |  |  |

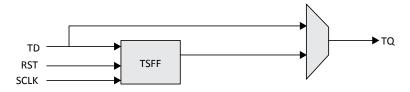

## 2.12. Tristate Register Block

The tristate register block registers tristate control signals from the core of the device before they are passed to the sysIO buffers. The block contains a register for SDR operation. In SDR, TD input feeds one of the flip-flops that then feeds the output. In DDR operation used mainly for DDR memory interface can be implemented on the left and right sides of the device. Here two inputs feed the tristate registers clocked by both ECLK and SCLK.

Figure 2.21 and Figure 2.22 show the Tristate Register Block functions on the device. For detailed description of the tristate register block modes and usage, refer to ECP5 and ECP5-5G High-Speed I/O Interface (TN1265).

Figure 2.21. Tristate Register Block on Top Side

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# 2.18. Device Configuration

All ECP5/ECP5-5G devices contain two ports that can be used for device configuration. The Test Access Port (TAP), which supports bit-wide configuration, and the sysCONFIG port, support dual-byte, byte and serial configuration. The TAP supports both the IEEE Standard 1149.1 Boundary Scan specification and the IEEE Standard 1532 In-System Configuration specification. There are 11 dedicated pins for TAP and sysConfig supports (TDI, TDO, TCK, TMS, CFG[2:0], PROGRAMN, DONE, INITN and CCLK). The remaining sysCONFIG pins are used as dual function pins. Refer to ECP5 and ECP5-5G sysCONFIG Usage Guide (TN1260) for more information about using the dual-use pins as general purpose I/Os.

There are various ways to configure an ECP5/ECP5-5G device:

- JTAG

- Standard Serial Peripheral Interface (SPI) Interface to boot PROM Support x1, x2, x4 wide SPI memory interfaces.

- System microprocessor to drive a x8 CPU port SPCM mode

- System microprocessor to drive a serial slave SPI port (SSPI mode)

- Slave Serial model (SCM)

On power-up, the FPGA SRAM is ready to be configured using the selected sysCONFIG port. Once a configuration port is selected, it will remain active throughout that configuration cycle. The IEEE 1149.1 port can be activated any time after power-up by sending the appropriate command through the TAP port.

ECP5/ECP5-5G devices also support the Slave SPI Interface. In this mode, the FPGA behaves like a SPI Flash device (slave mode) with the SPI port of the FPGA to perform read-write operations.

### 2.18.1. Enhanced Configuration Options

ECP5/ECP5-5G devices have enhanced configuration features such as: decryption support, decompression support, TransFR™ I/O and dual-boot and multi-boot image support.

### **TransFR (Transparent Field Reconfiguration)**

TransFR I/O (TFR) is a unique Lattice technology that allows users to update their logic in the field without interrupting system operation using a single ispVM command. TransFR I/O allows I/O states to be frozen during device configuration. This allows the device to be field updated with a minimum of system disruption and downtime. Refer to Minimizing System Interruption During Configuration Using TransFR Technology (TN1087) for details.

### **Dual-Boot and Multi-Boot Image Support**

Dual-boot and multi-boot images are supported for applications requiring reliable remote updates of configuration data for the system FPGA. After the system is running with a basic configuration, a new boot image can be downloaded remotely and stored in a separate location in the configuration storage device. Any time after the update the ECP5/ECP5-5G devices can be re-booted from this new configuration file. If there is a problem, such as corrupt data during download or incorrect version number with this new boot image, the ECP5/ECP5-5G device can revert back to the original backup golden configuration and try again. This all can be done without power cycling the system. For more information, refer to ECP5 and ECP5-5G sysCONFIG Usage Guide (TN1260).

### 2.18.2. Single Event Upset (SEU) Support

ECP5/ECP5-5G devices support SEU mitigation with three supporting functions:

- SED Soft Error Detect

- SEC Soft Error Correction

- SEI Soft Error Injection

ECP5/ECP5-5G devices have dedicated logic to perform Cycle Redundancy Code (CRC) checks. During configuration, the configuration data bitstream can be checked with the CRC logic block. In addition, the ECP5/ECP5-5G device can also be programmed to utilize a Soft Error Detect (SED) mode that checks for soft errors in configuration SRAM. The SED operation can be run in the background during user mode. If a soft error occurs, during user mode (normal operation) the device can be programmed to generate an error signal.

# 3.3. Power Supply Ramp Rates

#### **Table 3.3. Power Supply Ramp Rates**

| Symbol            | Parameter                                | Min  | Тур | Max | Unit |

|-------------------|------------------------------------------|------|-----|-----|------|

| t <sub>RAMP</sub> | Power Supply ramp rates for all supplies | 0.01 | 1   | 10  | V/ms |

Note: Assumes monotonic ramp rates.

# 3.4. Power-On-Reset Voltage Levels

Table 3.4. Power-On-Reset Voltage Levels

| Symbol             | Parameter                                                                        |                      | Min                | Тур  | Max  | Unit |   |

|--------------------|----------------------------------------------------------------------------------|----------------------|--------------------|------|------|------|---|

|                    |                                                                                  | Vcc                  | 0.90               | 1    | 1.00 | V    |   |

| V <sub>PORUP</sub> |                                                                                  | V <sub>CCAUX</sub>   | 2.00               | 1    | 2.20 | V    |   |

|                    | V <sub>CCAUX</sub> , and V <sub>CCIO8</sub> )                                    |                      | V <sub>CCIO8</sub> | 0.95 | 1    | 1.06 | V |

| V                  | All Davises                                                                      | Power-On-Reset ramp- | V <sub>CC</sub>    | 0.77 | -    | 0.87 | V |

| V <sub>PORDN</sub> | All Devices down trip point (Monitoring V <sub>CC</sub> , and V <sub>CCAUX</sub> | V <sub>CCAUX</sub>   | 1.80               | _    | 2.00 | V    |   |

#### Notes:

- These POR trip points are only provided for guidance. Device operation is only characterized for power supply voltages specified under recommended operating conditions.

- Only V<sub>CCIO8</sub> has a Power-On-Reset ramp up trip point. All other V<sub>CCIO8</sub> do not have Power-On-Reset ramp up detection.

- V<sub>CCIO8</sub> does not have a Power-On-Reset ramp down detection. V<sub>CCIO8</sub> must remain within the Recommended Operating

Conditions to ensure proper operation.

# 3.5. Power up Sequence

Power-On-Reset (POR) puts the ECP5/ECP5-5G device in a reset state. POR is released when V<sub>CC</sub>, V<sub>CCAUX</sub>, and V<sub>CCIO8</sub> are ramped above the V<sub>PORUP</sub> voltage, as specified above.

Vccio8 controls the voltage on the configuration I/O pins. If the ECP5/ECP5-5G device is using Master SPI mode to download configuration data from external SPI Flash, it is required to ramp Vccio8 above Vih of the external SPI Flash, before at least one of the other two supplies (Vcc and/or Vccaux) is ramped to VpoRUP voltage level. If the system cannot meet this power up sequence requirement, and requires the Vccio8 to be ramped last, then the system must keep either PROGRAMN or INITN pin LOW during power up, until Vccio8 reaches Vih of the external SPI Flash. This ensures the signals driven out on the configuration pins to the external SPI Flash meet the Vih voltage requirement of the SPI Flash. For LFE5UM/LFE5UM5G devices, it is required to power up Vcca, before Vccauxa is powered up.

# 3.6. Hot Socketing Specifications

Table 3.5. Hot Socketing Specifications

| Symbol | Parameter                                                        | Condition                                          | Min | Тур | Max | Unit |

|--------|------------------------------------------------------------------|----------------------------------------------------|-----|-----|-----|------|

| IDK_HS | Input or I/O Leakage Current<br>for Top and Bottom Banks<br>Only | $0 \le V_{IN} \le V_{IH}$ (Max)                    | _   | _   | ±1  | mA   |

| IDI    | Input or I/O Leakage Current                                     | $0 \le V_{IN} < V_{CCIO}$                          | _   | _   | ±1  | mA   |

| IDK    | for Left and Right Banks Only                                    | $V_{CCIO} \le V_{IN} \le V_{CCIO} + 0.5 \text{ V}$ | _   | 18  | _   | mA   |

#### Notes:

- 1. V<sub>CC</sub>, V<sub>CCAUX</sub> and V<sub>CCIO</sub> should rise/fall monotonically.

- 2. I<sub>DK</sub> is additive to I<sub>PU</sub>, I<sub>PW</sub> or I<sub>BH</sub>.

- 3. LVCMOS and LVTTL only.

- 4. Hot socket specification defines when the hot socketed device's junction temperature is at 85 °C or below. When the hot socketed device's junction temperature is above 85 °C, the I<sub>DK</sub> current can exceed ±1 mA.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# 3.7. Hot Socketing Requirements

### **Table 3.6. Hot Socketing Requirements**

| Description                                                                               | Min | Тур | Max | Unit |

|-------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Input current per SERDES I/O pin when device is powered down and inputs driven.           | -   | ı   | 8   | mA   |

| Input current per HDIN pin when device power supply is off, inputs driven <sup>1, 2</sup> | _   | -   | 15  | mA   |

| Current per HDIN pin when device power ramps up, input driven <sup>3</sup>                | _   | -   | 50  | mA   |

| Current per HDOUT pin when device power supply is off, outputs pulled up <sup>4</sup>     | _   | _   | 30  | mA   |

#### Notes:

- Device is powered down with all supplies grounded, both HDINP and HDINN inputs driven by a CML driver with maximum allowed output V<sub>CCHTX</sub>, 8b/10b data, no external AC coupling.

- 2. Each P and N input must have less than the specified maximum input current during hot plug. For a device with 2 DCU, the total input current would be 15 mA \* 4 channels \* 2 input pins per channel = 120 mA.

- Device power supplies are ramping up (V<sub>CCA</sub> and V<sub>CCAUX</sub>), both HDINP and HDINN inputs are driven by a CML driver with maximum allowed output V<sub>CCHTX</sub>, 8b/10b data, internal AC coupling.

- 4. Device is powered down with all supplies grounded. Both HDOUTP and HDOUN outputs are pulled up to  $V_{CCHTX}$  by the far end receiver termination of 50  $\Omega$  single ended.

### 3.8. ESD Performance

Refer to the ECP5 and ECP5-5G Product Family Qualification Summary for complete qualification data, including ESD performance.

# 3.9. DC Electrical Characteristics

**Over Recommended Operating Conditions**

**Table 3.7. DC Electrical Characteristics**

| Symbol                                            | Parameter                                                        | Condition                                                                                                                                               | Min | Тур | Max  | Unit |

|---------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| I <sub>IL</sub> , I <sub>IH</sub> <sup>1, 4</sup> | Input or I/O Low Leakage                                         | $0 \le V_{IN} \le V_{CCIO}$                                                                                                                             | _   | _   | 10   | μΑ   |

| I <sub>IH</sub> 1,3                               | Input or I/O High Leakage                                        | $V_{CCIO} < V_{IN} \le V_{IH(MAX)}$                                                                                                                     | _   | _   | 100  | μΑ   |

| I <sub>PU</sub>                                   | I/O Active Pull-up Current,<br>sustaining logic HIGH state       | $0.7 V_{CCIO} \le V_{IN} \le V_{CCIO}$                                                                                                                  | -30 | _   | ı    | μΑ   |

| IPU                                               | I/O Active Pull-up Current, pulling down from logic HIGH state   | $0 \le V_{IN} \le 0.7 \ V_{CCIO}$                                                                                                                       | _   | _   | -150 | μΑ   |

| I <sub>PD</sub>                                   | I/O Active Pull-down Current,<br>sustaining logic LOW state      | $0 \le V_{IN} \le V_{IL} (MAX)$                                                                                                                         | 30  | _   | -    | μΑ   |

| IPD                                               | I/O Active Pull-down Current,<br>pulling up from logic LOW state | $0 \le V_{IN} \le V_{CCIO}$                                                                                                                             | _   | _   | 150  | μΑ   |

| C1                                                | I/O Capacitance <sup>2</sup>                                     | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V}, \\ V_{CC} = 1.2 \text{ V}, V_{IO} = 0 \text{ to } V_{IH(MAX)}$   | _   | 5   | 8    | pf   |

| C2                                                | Dedicated Input Capacitance <sup>2</sup>                         | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V},$<br>$V_{CC} = 1.2 \text{ V}, V_{IO} = 0 \text{ to } V_{IH(MAX)}$ | _   | 5   | 7    | pf   |

| W                                                 | Hysteresis for Single-Ended                                      | V <sub>CCIO</sub> = 3.3 V                                                                                                                               | _   | 300 |      | mV   |

| V <sub>HYST</sub>                                 | Inputs                                                           | V <sub>CCIO</sub> = 2.5 V                                                                                                                               | _   | 250 | _    | mV   |

#### Notes:

- 1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tristated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

- 2. T<sub>Δ</sub> 25 °C, f = 1.0 MHz.

- 3. Applicable to general purpose I/Os in top and bottom banks.

- 4. When used as  $V_{REF}$ , maximum leakage= 25  $\mu$ A.

# 3.10. Supply Current (Standby)

Over recommended operating conditions.

Table 3.8. ECP5/ECP5-5G Supply Current (Standby)

| Symbol             | Parameter                            | Device                                            | Typical | Unit |

|--------------------|--------------------------------------|---------------------------------------------------|---------|------|

|                    |                                      | LFE5U-12F/ LFE5U-25F/ LFE5UM-25F                  | 77      | mA   |

|                    |                                      | LFE5UM5G-25F                                      | 77      | mA   |

|                    | Cons Bourse Consult Consult          | LFE5U-45F/ LFE5UM-45F                             | 116     | mA   |

| I <sub>CC</sub>    | Core Power Supply Current            | LFE5UM5G-45F                                      | 116     | mA   |

|                    |                                      | LFE5U-85F/ LFE5UM-85F                             | 212     | mA   |

|                    |                                      | LFE5UM5G-85F                                      | 212     | mA   |

|                    |                                      | LFE5U-12F/ LFE5U-25F/ LFE5UM-25F/<br>LFE5UM5G-25F | 16      | mA   |

| I <sub>CCAUX</sub> | Auxiliary Power Supply Current       | LFE5U-45F/ LFE5UM-45F/ LFE5UM5G-45F               | 17      | mA   |

|                    |                                      | LFE5U-85F/ LFE5UM-85F/ LFE5UM5G-85F               | 26      | mA   |

|                    | Bank Power Supply Current (Per Bank) | LFE5U-12F/ LFE5U-25F/ LFE5UM-25F/<br>LFE5UM5G-25F | 0.5     | mA   |

| I <sub>CCIO</sub>  |                                      | LFE5U-45F/ LFE5UM-45F/ LFE5UM5G-45F               | 0.5     | mA   |

|                    |                                      | LFE5U-85F/ LFE5UM-85F/ LFE5UM5G-85F               | 0.5     | mA   |

|                    |                                      | LFE5UM-25F                                        | 11      | mA   |

|                    |                                      | LFE5UM5G-25F                                      | 12      | mA   |

|                    | SERDES Power Supply Current (Per     | LFE5UM-45F                                        | 9.5     | mA   |

| I <sub>CCA</sub>   | Dual)                                | LFE5UM5G-45F                                      | 11      | mA   |

|                    |                                      | LFE5UM-85F                                        | 9.5     | mA   |

|                    |                                      | LFE5UM5G-85F                                      | 11      | mA   |

#### Notes:

- For further information on supply current, see the list of technical documentation in Supplemental Information section on page 102.

- Assumes all outputs are tristated, all inputs are configured as LVCMOS and held at the V<sub>CCIO</sub> or GND.

- Frequency 0 Hz.

- Pattern represents a "blank" configuration data file.

- T<sub>J</sub> = 85 °C, power supplies at nominal voltage.

- To determine the ECP5/ECP5-5G peak start-up current, use the Power Calculator tool in the Lattice Diamond Design Software.

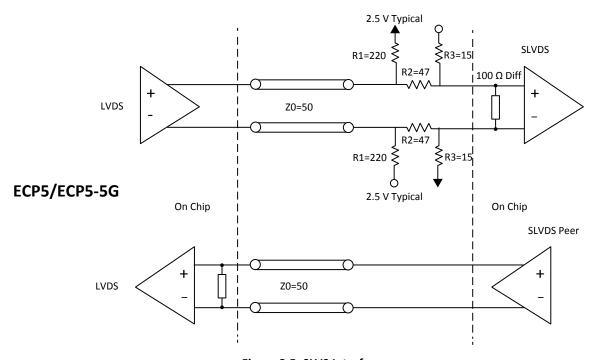

### 3.14.8. SLVS

Scalable Low-Voltage Signaling (SLVS) is based on a point-to-point signaling method defined in the JEDEC JESD8-13 (SLVS-400) standard. This standard evolved from the traditional LVDS standard and relies on the advantage of its use of smaller voltage swings and a lower common-mode voltage. The 200 mV (400 mV p-p) SLVS swing contributes to a reduction in power.

The ECP5/ECP5-5G devices can receive differential input up to 800 Mb/s with its LVDS input buffer. This LVDS input buffer is used to meet the SLVS input standard specified by the JEDEC standard. The SLVS output parameters are compared to ECP5/ECP5-5G LVDS input parameters, as listed in Table 3.18.

Table 3.18. Input to SLVS

| Parameter                  | ECP5/ECP5-5G LVDS Input | SLVS Output | Unit |

|----------------------------|-------------------------|-------------|------|

| Vcm (min)                  | 50                      | 150         | mV   |

| Vcm (max)                  | 2350                    | 250         | mV   |

| Differential Voltage (min) | 100                     | 140         | mV   |

| Differential Voltage (max) | _                       | 270         | mV   |

ECP5/ECP5-5G does not support SLVS output. However, SLVS output can be created using ECP5/ECP5-5G LVDS outputs by level shift to meet the low Vcm/Vod levels required by SLVS. Figure 3.5 shows how the LVDS output can be shifted external to meet SLVS levels.

Figure 3.5. SLVS Interface

# 3.15. Typical Building Block Function Performance

### Table 3.19. Pin-to-Pin Performance

| Function        | -8 Timing | Unit |

|-----------------|-----------|------|

| Basic Functions | ,         | ·    |

| 16-Bit Decoder  | 5.06      | ns   |

| 32-Bit Decoder  | 6.08      | ns   |

| 64-Bit Decoder  | 5.06      | ns   |

| 4:1 Mux         | 4.45      | ns   |

| 8:1 Mux         | 4.63      | ns   |

| 16:1 Mux        | 4.81      | ns   |

| 32:1 Mux        | 4.85      | ns   |

### Notes:

- 1. I/Os are configured with LVCMOS25 with V<sub>CCIO</sub>=2.5, 12 mA drive.

- These functions were generated using Lattice Diamond design software tool. Exact performance may vary with the device and the design software tool version. The design software tool uses internal parameters that have been characterized but are not tested on every device.

- 3. Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from Lattice Diamond design software tool.

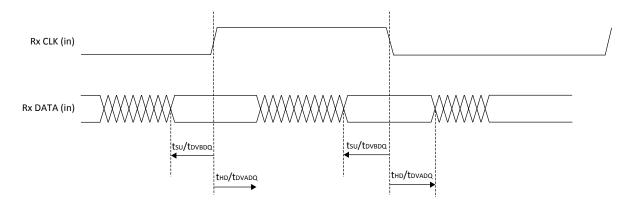

Figure 3.6. Receiver RX.CLK.Centered Waveforms

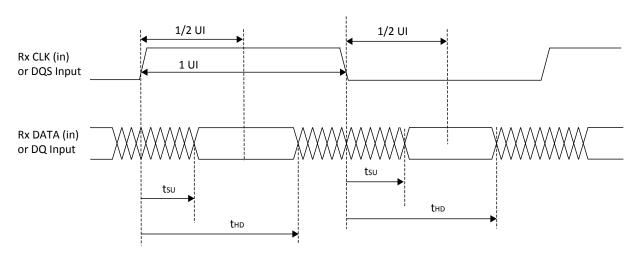

Figure 3.7. Receiver RX.CLK.Aligned and DDR Memory Input Waveforms

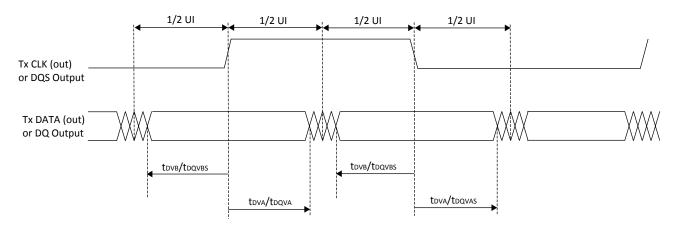

Figure 3.8. Transmit TX.CLK.Centered and DDR Memory Output Waveforms

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# 3.26. CPRI LV2 E.48 Electrical and Timing Characteristics – Preliminary

Table 3.32. CPRI LV2 E.48 Electrical and Timing Characteristics

| Symbol                      | Description                                                | Test Conditions                   | Min    | Тур    | Max                             | Unit        |

|-----------------------------|------------------------------------------------------------|-----------------------------------|--------|--------|---------------------------------|-------------|

| Transmit                    | 1                                                          |                                   | II.    |        |                                 |             |

| UI                          | Unit Interval                                              | _                                 | 203.43 | 203.45 | 203.47                          | ps          |

| T <sub>DCD</sub>            | Duty Cycle Distortion                                      | _                                 | _      | _      | 0.05                            | UI          |

| J <sub>UBHPJ</sub>          | Uncorrelated Bounded High<br>Probability Jitter            | _                                 | _      | _      | 0.15                            | UI          |

| J <sub>TOTAL</sub>          | Total Jitter                                               | _                                 | _      | _      | 0.3                             | UI          |

| Z <sub>RX-DIFF-DC</sub>     | DC differential Impedance                                  | _                                 | 80     | _      | 120                             | Ω           |

| T <sub>SKEW</sub>           | Skew between differential signals                          | _                                 | _      | _      | 9                               | ps          |

| R <sub>LTX-DIFF</sub>       | Tx Differential Return Loss (S22),                         | 100 MHz < freq<br>< 3.6864 GHz    | _      | _      | -8                              | dB          |

|                             | including package and silicon                              | 3.6864 GHz < freq<br>< 4.9152 GHz | -      | _      | -8 + 16.6 *log<br>(freq/3.6864) | dB          |

| R <sub>LTX-CM</sub>         | Tx Common Mode Return Loss, including package and silicon  | 100 MHz < freq<br>< 3.6864 GHz    | 6      | _      | _                               | dB          |

| I <sub>TX-SHORT</sub>       | Transmitter short-circuit current                          | _                                 | _      | _      | 100                             | mA          |

| T <sub>RISE_FALL-DIFF</sub> | Differential Rise and Fall Time                            | _                                 |        | _      | _                               | ps          |

| L <sub>TX-SKEW</sub>        | Lane-to-lane output skew                                   | _                                 | _      | _      |                                 | ps          |

| Receive                     |                                                            |                                   |        | •      |                                 |             |

| UI                          | Unit Interval                                              | _                                 | 203.43 | 203.45 | 203.47                          | ps          |

| V <sub>RX-DIFF-PP</sub>     | Differential Rx peak-peak voltage                          | _                                 | _      | _      | 1.2                             | V, p-p      |

| V <sub>RX-EYE_Y1_Y2</sub>   | Receiver eye opening mask, Y1 and Y2                       | _                                 | 62.5   | _      | 375                             | mV,<br>diff |

| V <sub>RX-EYE_X1</sub>      | Receiver eye opening mask, X1                              | _                                 | _      | _      | 0.3                             | UI          |

| T <sub>RX-TJ</sub>          | Receiver total jitter tolerance (not including sinusoidal) | _                                 | _      | _      | 0.6                             | UI          |

| R <sub>LRX-DIFF</sub>       | Receiver differential Return Loss,                         | 100 MHz < freq<br>< 3.6864 GHz    | _      | _      | -8                              | dB          |

|                             | package plus silicon                                       | 3.6864 GHz < freq<br>< 4.9152 GHz | _      | _      | -8 + 16.6 *log<br>(freq/3.6864) | dB          |

| R <sub>LRX-CM</sub>         | Receiver common mode Return<br>Loss, package plus silicon  | _                                 | 6      | _      | _                               | dB          |

| Z <sub>RX-DIFF-DC</sub>     | Receiver DC differential impedance                         | _                                 | 80     | 100    | 120                             | Ω           |

**Note**: Data is measured with PRBS7 data pattern, not with PRBS-31 pattern.

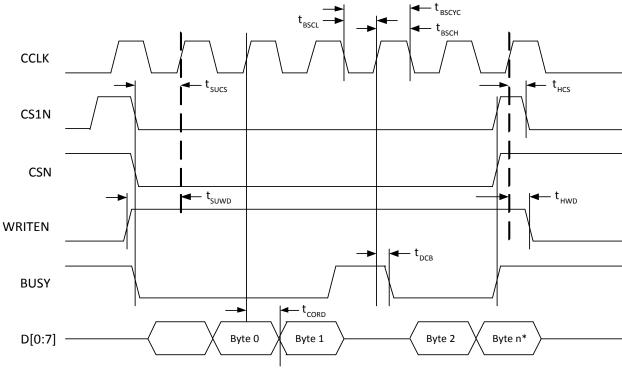

Table 3.42. ECP5/ECP5-5G sysCONFIG Port Timing Specifications (Continued)

| Symbol              | Parameter                        |   | Min | Max | Unit |  |  |

|---------------------|----------------------------------|---|-----|-----|------|--|--|

| Slave Parallel      |                                  |   |     |     |      |  |  |

| f <sub>CCLK</sub>   | CCLK input clock frequency       | _ | _   | 50  | MHz  |  |  |

| t <sub>BSCH</sub>   | CCLK input clock pulsewidth HIGH | _ | 6   | _   | ns   |  |  |

| t <sub>BSCL</sub>   | CCLK input clock pulsewidth LOW  | _ | 6   | _   | ns   |  |  |

| t <sub>CORD</sub>   | CCLK to DOUT for Read Data       | _ | _   | 12  | ns   |  |  |

| t <sub>SUCBDI</sub> | Data Setup Time to CCLK          | _ | 1.5 | _   | ns   |  |  |

| t <sub>HCBDI</sub>  | Data Hold Time to CCLK           | _ | 1.5 | _   | ns   |  |  |

| t <sub>SUCS</sub>   | CSN, CSN1 Setup Time to CCLK     | _ | 2.5 | _   | ns   |  |  |

| t <sub>HCS</sub>    | CSN, CSN1 Hold Time to CCLK      | _ | 1.5 | -   | ns   |  |  |

| t <sub>SUWD</sub>   | WRITEN Setup Time to CCLK        | _ | 45  | _   | ns   |  |  |

| t <sub>HCWD</sub>   | WRITEN Hold Time to CCLK         | _ | 2   | _   | ns   |  |  |

| t <sub>DCB</sub>    | CCLK to BUSY Delay Time          | _ | _   | 12  | ns   |  |  |

<sup>\*</sup>n = last byte of read cycle.

Figure 3.15. sysCONFIG Parallel Port Read Cycle

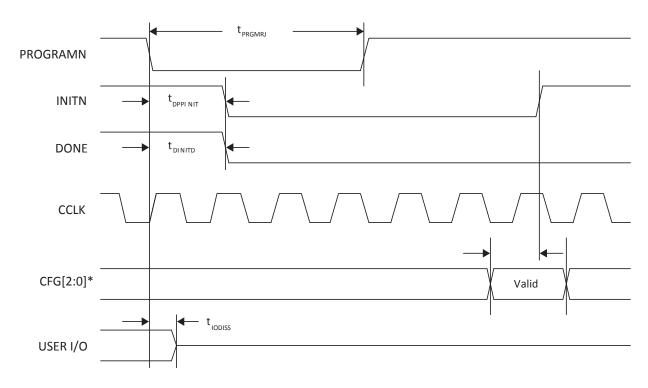

<sup>\*</sup>The CFG pins are normally static (hardwired).

Figure 3.20. Configuration from PROGRAMN Timing

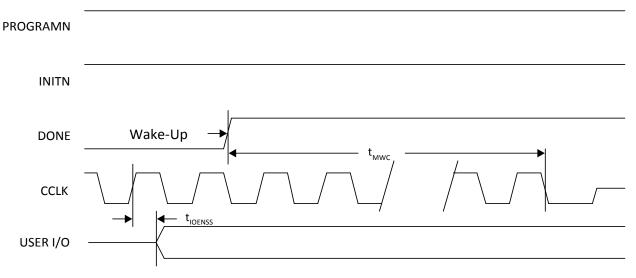

Figure 3.21. Wake-Up Timing

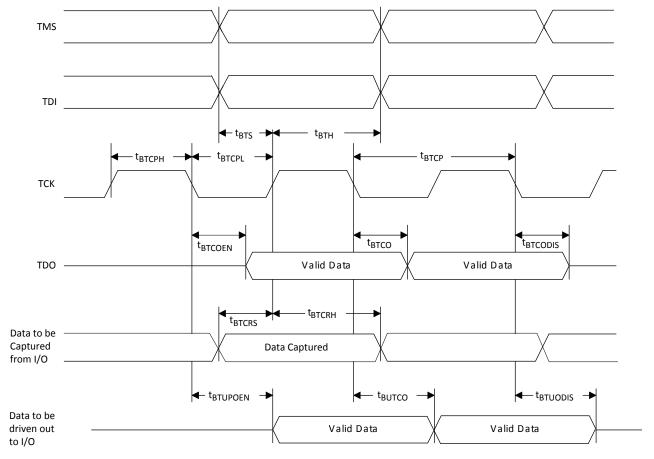

Figure 3.23. JTAG Port Timing Waveforms

# 3.33. Switching Test Conditions

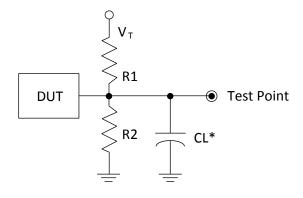

Figure 3.24 shows the output test load that is used for AC testing. The specific values for resistance, capacitance, voltage, and other test conditions are listed in Table 3.44.

\*CL Includes Test Fixture and Probe Capacitance

Figure 3.24. Output Test Load, LVTTL and LVCMOS Standards

| Signal Name                         | 1/0      | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL, DLL and Clock Functions (Conti | nued)    |                                                                                                                                                                                                                                                                                                                                                                                             |

| [L/R]DQS[group_num]                 | 1/0      | DQS input/output pads: T (top), R (right), group_ num = ball number associated with DQS[T] pin.                                                                                                                                                                                                                                                                                             |

| [T/R]]DQ[group_num] I/O             |          | DQ input/output pads: T (top), R (right), group_ num = ball number associated with DQS[T] pin.                                                                                                                                                                                                                                                                                              |

| Test and Programming (Dedicated     | Pins)    |                                                                                                                                                                                                                                                                                                                                                                                             |

| TMS                                 | ı        | Test Mode Select input, used to control the 1149.1 state machine. Pull-up is enabled during configuration. This is a dedicated input pin.                                                                                                                                                                                                                                                   |

| тск                                 | ı        | Test Clock input pin, used to clock the 1149.1 state machine. No pull-up enabled. This is a dedicated input pin.                                                                                                                                                                                                                                                                            |

| TDI                                 | I        | Test Data in pin. Used to load data into device using 1149.1 state machine. After power-up, this TAP port can be activated for configuration by sending appropriate command. (Note: once a configuration port is selected it is locked. Another configuration port cannot be selected until the power-up sequence). Pull-up is enabled during configuration. This is a dedicated input pin. |

| TDO                                 | 0        | Output pin. Test Data Out pin used to shift data out of a device using 1149.1. This is a dedicated output pin.                                                                                                                                                                                                                                                                              |

| Configuration Pads (Used during sy  | sCONFIG) |                                                                                                                                                                                                                                                                                                                                                                                             |

| CFG[2:0]                            | ı        | Mode pins used to specify configuration mode values latched on rising edge of INITN. During configuration, a pull-up is enabled. These are dedicated pins.                                                                                                                                                                                                                                  |

| INITN                               | I/O      | Open Drain pin. Indicates the FPGA is ready to be configured. During configuration, a pull-up is enabled. This is a dedicated pin.                                                                                                                                                                                                                                                          |

| PROGRAMN                            | ı        | Initiates configuration sequence when asserted low. This pin always has an active pull-up. This is a dedicated pin.                                                                                                                                                                                                                                                                         |

| DONE                                | 1/0      | Open Drain pin. Indicates that the configuration sequence is complete, and the startup sequence is in progress.  This is a dedicated pin.                                                                                                                                                                                                                                                   |

| CCLK                                | 1/0      | Input Configuration Clock for configuring an FPGA in Slave SPI, Serial, and CPU modes. Output Configuration Clock for configuring an FPGA in Master configuration modes (Master SPI, Master Serial).  This is a dedicated pin.                                                                                                                                                              |

| HOLDN/DI/BUSY/CSSPIN/CEN            | I/O      | Parallel configuration mode busy indicator. SPI/SPIm mode data output.  This is a shared I/O pin. This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O pin.                                                                                                                                                                                           |

| CSN/SN                              | 1/0      | Parallel configuration mode active-low chip select. Slave SPI chip select. This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O pin.                                                                                                                                                                                                                  |

| CS1N                                | I        | Parallel configuration mode active-low chip select. This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O pin.                                                                                                                                                                                                                                         |

| WRITEN                              | 1        | Write enable for parallel configuration modes.  This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O pin.                                                                                                                                                                                                                                             |

| DOUT/CSON                           | 0        | Serial data output. Chip select output. SPI/SPIm mode chip select. This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O                                                                                                                                                                                                                               |

| D0/MOSI/IO0                         | 1/0      | Parallel configuration I/O. Open drain during configuration. When in SPI modes, it is an output in Master mode, and input in Slave mode.  This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O pin.                                                                                                                                                   |

| Part number                                | Grade          | Package                          | Pins       | Temp.                 | LUTs (K) | SERDES     |

|--------------------------------------------|----------------|----------------------------------|------------|-----------------------|----------|------------|

| LFE5U-45F-8BG554C                          | -8             | Lead free caBGA                  | 554        | Commercial            | 44       | No         |

| LFE5U-85F-6MG285C                          | -6             | Lead free csfBGA                 | 285        | Commercial            | 84       | No         |

| LFE5U-85F-7MG285C                          | -7             | Lead free csfBGA                 | 285        | Commercial            | 84       | No         |

| LFE5U-85F-8MG285C                          | -8             | Lead free csfBGA                 | 285        | Commercial            | 84       | No         |

| LFE5U-85F-6BG381C                          | -6             | Lead free caBGA                  | 381        | Commercial            | 84       | No         |

| LFE5U-85F-7BG381C                          | <b>-</b> 7     | Lead free caBGA                  | 381        | Commercial            | 84       | No         |

| LFE5U-85F-8BG381C                          | -8             | Lead free caBGA                  | 381        | Commercial            | 84       | No         |

| LFE5U-85F-6BG554C                          | <b>-</b> 6     | Lead free caBGA                  | 554        | Commercial            | 84       | No         |

| LFE5U-85F-7BG554C                          | <b>-</b> 7     | Lead free caBGA                  | 554        | Commercial            | 84       | No         |

| LFE5U-85F-8BG554C                          | -8             | Lead free caBGA                  | 554        | Commercial            | 84       | No         |

| LFE5U-85F-6BG756C                          | -6             | Lead free caBGA                  | 756        | Commercial            | 84       | No         |

| LFE5U-85F-7BG756C                          | <b>-</b> 7     | Lead free caBGA                  | 756        | Commercial            | 84       | No         |

| LFE5U-85F-8BG756C                          | -8             | Lead free caBGA                  | 756        | Commercial            | 84       | No         |

| LFE5UM-25F-6MG285C                         | -6             | Lead free csfBGA                 | 285        | Commercial            | 24       | Yes        |

| LFE5UM-25F-7MG285C                         | <b>-</b> 7     | Lead free csfBGA                 | 285        | Commercial            | 24       | Yes        |

| LFE5UM-25F-8MG285C                         | -8             | Lead free csfBGA                 | 285        | Commercial            | 24       | Yes        |

| LFE5UM-25F-6BG381C                         | -6             | Lead free caBGA                  | 381        | Commercial            | 24       | Yes        |

| LFE5UM-25F-7BG381C                         | <b>-</b> 7     | Lead free caBGA                  | 381        | Commercial            | 24       | Yes        |

| LFE5UM-25F-8BG381C                         | -8             | Lead free caBGA                  | 381        | Commercial            | 24       | Yes        |

| LFE5UM-45F-6MG285C                         | -6             | Lead free csfBGA                 | 285        | Commercial            | 44       | Yes        |

| LFE5UM-45F-7MG285C                         | <b>-</b> 7     | Lead free csfBGA                 | 285        | Commercial            | 44       | Yes        |

| LFE5UM-45F-8MG285C                         | -8             | Lead free csfBGA                 | 285        | Commercial            | 44       | Yes        |

| LFE5UM-45F-6BG381C                         | -6             | Lead free caBGA                  | 381        | Commercial            | 44       | Yes        |

| LFE5UM-45F-7BG381C                         | -7             | Lead free caBGA                  | 381        | Commercial            | 44       | Yes        |

| LFE5UM-45F-8BG381C                         | -8             | Lead free caBGA                  | 381        | Commercial            | 44       | Yes        |

| LFE5UM-45F-6BG554C                         | -6             | Lead free caBGA                  | 554        | Commercial            | 44       | Yes        |

| LFE5UM-45F-7BG554C                         | <b>-</b> 7     | Lead free caBGA                  | 554        | Commercial            | 44       | Yes        |

| LFE5UM-45F-8BG554C                         | -8             | Lead free caBGA                  | 554        | Commercial            | 44       | Yes        |

| LFE5UM-85F-6MG285C                         | <del>-</del> 6 | Lead free csfBGA                 | 285        | Commercial            | 84       | Yes        |

| LFE5UM-85F-7MG285C                         | <b>-7</b>      | Lead free csfBGA                 | 285        | Commercial            | 84       | Yes        |

| LFE5UM-85F-8MG285C                         | -8             | Lead free csfBGA                 | 285        | Commercial            | 84       | Yes        |

| LFE5UM-85F-6BG381C                         | <del>-</del> 6 | Lead free caBGA                  | 381        | Commercial            | 84       | Yes        |

| LFE5UM-85F-7BG381C                         | <b>-7</b>      | Lead free caBGA                  | 381        | Commercial            | 84       | Yes        |

| LFE5UM-85F-8BG381C                         | -8             | Lead free caBGA                  | 381        | Commercial            | 84       | Yes        |

| LFESUM-85F-6BG554C                         | <del>-</del> 6 | Lead free caBGA                  | 554        | Commercial            | 84       | Yes        |

| LFE5UM-85F-7BG554C                         | -7<br>9        | Lead free caBGA                  | 554        | Commercial            | 84       | Yes        |

| LFESUM-85F-8BG554C                         | -8<br>-6       | Lead free caBGA                  | 554<br>756 | Commercial            | 84       | Yes        |

| LFE5UM-85F-6BG756C<br>LFE5UM-85F-7BG756C   | <i>−</i> 6     | Lead free caBGA  Lead free caBGA | 756<br>756 | Commercial Commercial | 84<br>84 | Yes        |

|                                            |                |                                  |            | Commercial            |          | Yes        |

| LFE5UM-85F-8BG756C<br>LFE5UM5G-25F-8MG285C | -8<br>-8       | Lead free caBGA Lead free csfBGA | 756<br>285 | Commercial            | 84<br>24 | Yes<br>Yes |

| LFE5UM5G-25F-8BG381C                       | -8<br>-8       | Lead free caBGA                  | 381        | Commercial            | 24       | Yes        |

|                                            |                |                                  |            |                       |          |            |

| LFE5UM5G-45F-8MG285C                       | -8<br>-8       | Lead free csfBGA                 | 285        | Commercial            | 44       | Yes        |

| LFE5UM5G-45F-8BG381C                       | -8             | Lead free caBGA                  | 381        | Commercial            | 44       | Yes        |

| LFE5UM5G-45F-8BG554C                       | -8             | Lead free caBGA                  | 554        | Commercial            | 44       | Yes        |

| LFE5UM5G-85F-8MG285C                       | -8             | Lead free csfBGA                 | 285        | Commercial            | 84       | Yes        |