# E.) Lattice Semiconductor Corporation - <u>LFE5U-85F-8BG756I Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                       |

|--------------------------------|------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 21000                                                                        |

| Number of Logic Elements/Cells | 84000                                                                        |

| Total RAM Bits                 | 3833856                                                                      |

| Number of I/O                  | 365                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.045V ~ 1.155V                                                              |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                           |

| Package / Case                 | 756-FBGA                                                                     |

| Supplier Device Package        | 756-CABGA (27x27)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe5u-85f-8bg756i |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 3.1.            | Absolute Maximum Ratings                                                                |    |

|-----------------|-----------------------------------------------------------------------------------------|----|

| 3.2.            | Recommended Operating Conditions                                                        |    |

| 3.3.            | Power Supply Ramp Rates                                                                 |    |

| 3.4.            | Power-On-Reset Voltage Levels                                                           |    |

| 3.5.            | Power up Sequence                                                                       |    |

| 3.6.            | Hot Socketing Specifications                                                            |    |

| 3.7.            | Hot Socketing Requirements                                                              |    |

| 3.8.            | ESD Performance                                                                         |    |

| 3.9.            | DC Electrical Characteristics                                                           | 49 |

| 3.10.           | Supply Current (Standby)                                                                |    |

| 3.11.           | SERDES Power Supply Requirements <sup>1,2,3</sup>                                       | 51 |

| 3.12.           | sysI/O Recommended Operating Conditions                                                 | 53 |

| 3.13.           | sysI/O Single-Ended DC Electrical Characteristics                                       | 54 |

| 3.14.           | sysI/O Differential Electrical Characteristics                                          | 55 |

| 3.14            | 4.1. LVDS                                                                               |    |

| 3.14            |                                                                                         |    |

| 3.14            |                                                                                         |    |

| 3.14            |                                                                                         |    |

| 3.14            |                                                                                         |    |

| 3.14            |                                                                                         |    |

| 3.14            |                                                                                         |    |

| 3.14            |                                                                                         |    |

|                 | Typical Building Block Function Performance                                             |    |

| 3.15.           | Derating Timing Tables                                                                  |    |

| 3.16.           |                                                                                         |    |

| 3.17.           | Maximum I/O Buffer Speed                                                                |    |

| 3.18.           | External Switching Characteristics                                                      |    |

| 3.19.           | sysCLOCK PLL Timing                                                                     |    |

| 3.20.           | SERDES High-Speed Data Transmitter                                                      |    |

| 3.21.           | SERDES/PCS Block Latency                                                                |    |

| 3.22.           | SERDES High-Speed Data Receiver                                                         |    |

| 3.23.           | Input Data Jitter Tolerance                                                             |    |

| 3.24.           | SERDES External Reference Clock                                                         |    |

| 3.25.           | PCI Express Electrical and Timing Characteristics                                       |    |

| 3.25            | 5.1. PCIe (2.5 Gb/s) AC and DC Characteristics                                          | 76 |

| 3.25            | 5.2. PCIe (5 Gb/s) – Preliminary AC and DC Characteristics                              | 77 |

| 3.26.           | CPRI LV2 E.48 Electrical and Timing Characteristics – Preliminary                       | 79 |

| 3.27.           | XAUI/CPRI LV E.30 Electrical and Timing Characteristics                                 | 80 |

| 3.27            | 7.1. AC and DC Characteristics                                                          | 80 |

| 3.28.           | CPRI LV E.24/SGMII(2.5Gbps) Electrical and Timing Characteristics                       | 80 |

| 3.28            | 8.1. AC and DC Characteristics                                                          | 80 |

| 3.29.           | Gigabit Ethernet/SGMII(1.25Gbps)/CPRI LV E.12 Electrical and Timing Characteristics     | 81 |

| 3.29            |                                                                                         |    |

| 3.30.           | SMPTE SD/HD-SDI/3G-SDI (Serial Digital Interface) Electrical and Timing Characteristics |    |

| 3.30            |                                                                                         |    |

| 3.31.           | sysCONFIG Port Timing Specifications                                                    |    |

| 3.32.           | JTAG Port Timing Specifications                                                         |    |

| 3.33.           | Switching Test Conditions                                                               |    |

|                 | out Information                                                                         |    |

| 4. Pint<br>4.1. | Signal Descriptions                                                                     |    |

| 4.1.<br>4.2.    | PICs and DDR Data (DQ) Pins Associated with the DDR Strobe (DQS) Pin                    |    |

|                 |                                                                                         |    |

| 4.3.            | Pin Information Summary                                                                 |    |

| 4.3.            |                                                                                         |    |

| 4.3.            |                                                                                         |    |

| 5. Ord          | lering Information                                                                      |    |

| Table 3.36. Receive and Jitter Tolerance                                |    |

|-------------------------------------------------------------------------|----|

| Table 3.37. Transmit                                                    |    |

| Table 3.38. Receive and Jitter Tolerance                                |    |

| Table 3.39. Transmit                                                    | 82 |

| Table 3.40. Receive                                                     | 82 |

| Table 3.41. Reference Clock                                             | 82 |

| Table 3.42. ECP5/ECP5-5G sysCONFIG Port Timing Specifications           | 83 |

| Table 3.43. JTAG Port Timing Specifications                             |    |

| Table 3.44. Test Fixture Required Components, Non-Terminated Interfaces |    |

|                                                                         |    |

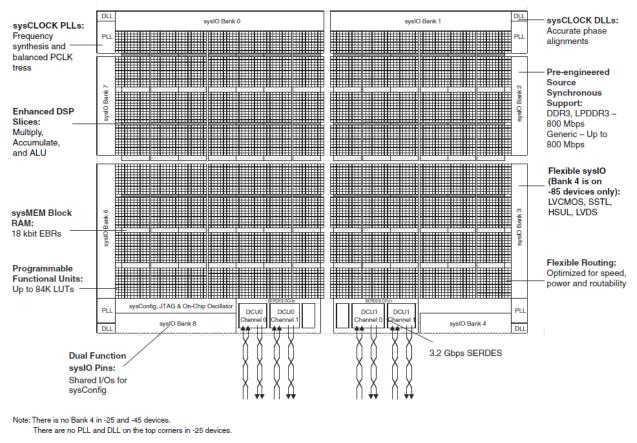

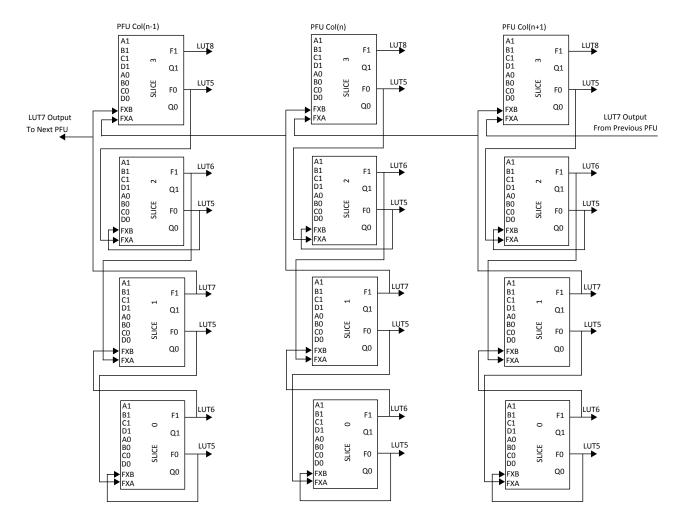

### 2.2. **PFU Blocks**

The core of the ECP5/ECP5-5G device consists of PFU blocks. Each PFU block consists of four interconnected slices numbered 0-3, as shown in Figure 2.2. Each slice contains two LUTs. All the interconnections to and from PFU blocks are from routing. There are 50 inputs and 23 outputs associated with each PFU block.

The PFU block can be used in Distributed RAM or ROM function, or used to perform Logic, Arithmetic, or ROM functions. Table 2.1 shows the functions each slice can perform in either mode.

Notes: For Slices 0 and 1, memory control signals are generated from Slice 2 as follows: WCK is CLK

WRE is from LSR

DI[3:2] for Slice 1 and DI[1:0] for Slice 0 data from Slice 2 WAD [A:D] is a 4-bit address from slice 2 LUT input

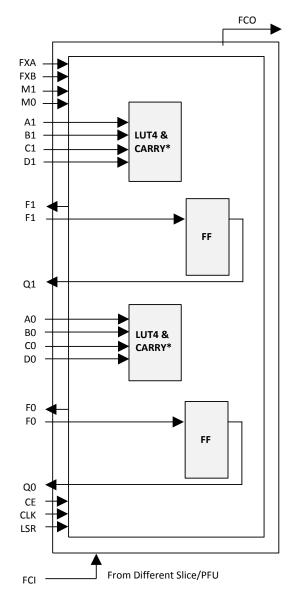

Figure 2.3. Slice Diagram

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

| Figure 2.4. Connectivity Supporting LUT5, LUT6, LUT | 7, and LUT8 |

|-----------------------------------------------------|-------------|

|-----------------------------------------------------|-------------|

| Table | 2.2. | Slice | Signal | Descriptions |

|-------|------|-------|--------|--------------|

|-------|------|-------|--------|--------------|

| Function | Туре               | Signal Names   | Description                                                      |

|----------|--------------------|----------------|------------------------------------------------------------------|

| Input    | Data signal        | A0, B0, C0, D0 | Inputs to LUT4                                                   |

| Input    | Data signal        | A1, B1, C1, D1 | Inputs to LUT4                                                   |

| Input    | Multi-purpose      | M0             | Multipurpose Input                                               |

| Input    | Multi-purpose      | M1             | Multipurpose Input                                               |

| Input    | Control signal     | CE             | Clock Enable                                                     |

| Input    | Control signal     | LSR            | Local Set/Reset                                                  |

| Input    | Control signal     | CLK            | System Clock                                                     |

| Input    | Inter-PFU signal   | FCI            | Fast Carry-in <sup>1</sup>                                       |

| Input    | Inter-slice signal | FXA            | Intermediate signal to generate LUT6, LUT7 and LUT8 <sup>2</sup> |

| Input    | Inter-slice signal | FXB            | Intermediate signal to generate LUT6, LUT7 and LUT8 <sup>2</sup> |

| Output   | Data signals       | F0, F1         | LUT4 output register bypass signals                              |

| Output   | Data signals       | Q0, Q1         | Register outputs                                                 |

| Output   | Inter-PFU signal   | FCO            | Fast carry chain output <sup>1</sup>                             |

Notes:

2. Requires two adjacent PFUs.

<sup>1.</sup> See Figure 2.3 on page 15 for connection details.

| Table 2.4 provides a description | of the signals in the PLL blocks. |

|----------------------------------|-----------------------------------|

|----------------------------------|-----------------------------------|

| Signal        | Туре   | Description                                                                     |

|---------------|--------|---------------------------------------------------------------------------------|

| CLKI          | Input  | Clock Input to PLL from external pin or routing                                 |

| CLKI2         | Input  | Muxed clock input to PLL                                                        |

| SEL           | Input  | Input Clock select, selecting from CLKI and CLKI2 inputs                        |

| CLKFB         | Input  | PLL Feedback Clock                                                              |

| PHASESEL[1:0] | Input  | Select which output to be adjusted on Phase by PHASEDIR, PHASESTEP, PHASELODREG |

| PHASEDIR      | Input  | Dynamic Phase adjustment direction.                                             |

| PHASESTEP     | Input  | Dynamic Phase adjustment step.                                                  |

| PHASELOADREG  | Input  | Load dynamic phase adjustment values into PLL.                                  |

| CLKOP         | Output | Primary PLL output clock (with phase shift adjustment)                          |

| CLKOS         | Output | Secondary PLL output clock (with phase shift adjust)                            |

| CLKOS2        | Output | Secondary PLL output clock2 (with phase shift adjust)                           |

| CLKOS3        | Output | Secondary PLL output clock3 (with phase shift adjust)                           |

| LOCK          | Output | PLL LOCK to CLKI, Asynchronous signal. Active high indicates PLL lock           |

| STDBY         | Input  | Standby signal to power down the PLL                                            |

| RST           | Input  | Resets the PLL                                                                  |

| ENCLKOP       | Input  | Enable PLL output CLKOP                                                         |

| ENCLKOS       | Input  | Enable PLL output CLKOS                                                         |

| ENCLKOS2      | Input  | Enable PLL output CLKOS2                                                        |

| ENCLKOS3      | Input  | Enable PLL output CLKOS3                                                        |

#### Table 2.4. PLL Blocks Signal Descriptions

For more details on the PLL you can refer to the ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263).

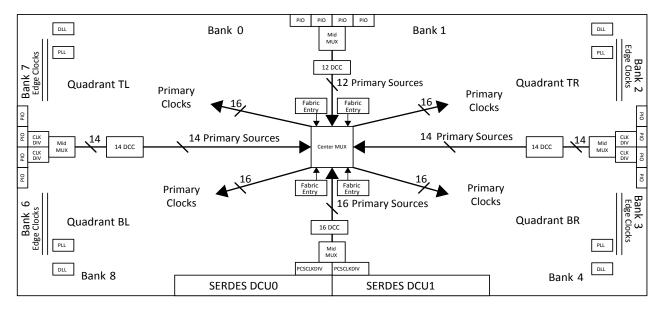

### 2.5. Clock Distribution Network

There are two main clock distribution networks for any member of the ECP5/ECP5-5G product family, namely Primary Clock (PCLK) and Edge Clock (ECLK). These clock networks have the clock sources come from many different sources, such as Clock Pins, PLL outputs, DLLDEL outputs, Clock divider outputs, SERDES/PCS clocks and some on chip generated clock signal. There are clock dividers (CLKDIV) blocks to provide the slower clock from these clock sources. ECP5/ECP5-5G also supports glitchless dynamic enable function (DCC) for the PCLK Clock to save dynamic power. There are also some logics to allow dynamic glitchless selection between two clocks for the PCLK network (DCS).

Overview of Clocking Network is shown in Figure 2.6 on page 20 for LFE5UM/LFE5UM5G-85 device.

Figure 2.6. LFE5UM/LFE5UM5G-85 Clocking

### 2.5.1. Primary Clocks

The ECP5/ECP5-5G device family provides low-skew, high fan-out clock distribution to all synchronous elements in the FPGA fabric through the Primary Clock Network.

The primary clock network is divided into four clocking quadrants: Top Left (TL), Bottom Left (BL), Top Right (TR), and Bottom Right (BR). Each of these quadrants has 16 clocks that can be distributed to the fabric in the quadrant.

The Lattice Diamond software can automatically route each clock to one of the four quadrants up to a maximum of 16 clocks per quadrant. The user can change how the clocks are routed by specifying a preference in the Lattice Diamond software to locate the clock to specific. The ECP5/ECP5-5G device provides the user with a maximum of 64 unique clock input sources that can be routed to the primary Clock network.

Primary clock sources are:

- Dedicated clock input pins

- PLL outputs

- CLKDIV outputs

- Internal FPGA fabric entries (with minimum general routing)

- SERDES/PCS/PCSDIV clocks

- OSC clock

These sources are routed to one of four clock switches called a Mid Mux. The outputs of the Mid MUX are routed to the center of the FPGA where another clock switch, called the Center MUX, is used to route the primary clock sources to primary clock distribution to the ECP5/ECP5-5G fabric. These routing muxes are shown in Figure 2.6. Since there is a maximum of 60 unique clock input sources to the clocking quadrants, there are potentially 64 unique clock domains that can be used in the ECP5/ECP5-5G Device. For more information about the primary clock tree and connections, refer to ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263).

#### 2.5.1.1. Dynamic Clock Control

The Dynamic Clock Control (DCC), Quadrant Clock enable/disable feature allows internal logic control of the quadrant primary clock network. When a clock network is disabled, the clock signal is static and not toggle. All the logic fed by that clock will not toggle, reducing the overall power consumption of the device. The disable function will not create glitch and increase the clock latency to the primary clock network.

This DCC controls the clock sources from the Primary CLOCK MIDMUX before they are fed to the Primary Center MUXs that drive the quadrant clock network. For more information about the DCC, refer to ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263).

#### 2.5.1.2. Dynamic Clock Select

The Dynamic Clock Select (DCS) is a smart multiplexer function available in the primary clock routing. It switches between two independent input clock sources. Depending on the operation modes, it switches between two (2) independent input clock sources either with or without any glitches. This is achieved regardless of when the select signal is toggled. Both input clocks must be running to achieve functioning glitch-less DCS output clock, but it is not required running clocks when used as non-glitch-less normal clock multiplexer.

There are two DCS blocks per device that are fed to all quadrants. The inputs to the DCS block come from all the output of MIDMUXs and Clock from CIB located at the center of the PLC array core. The output of the DCS is connected to one of the inputs of Primary Clock Center MUX.

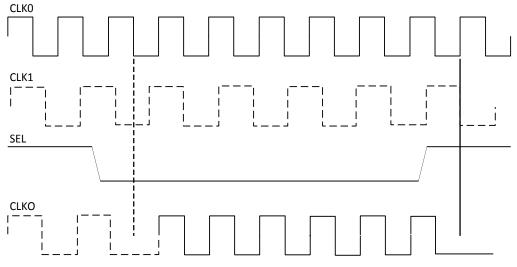

Figure 2.7 shows the timing waveforms of the default DCS operating mode. The DCS block can be programmed to other modes. For more information about the DCS, refer to ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263).

Figure 2.7. DCS Waveforms

### 2.5.2. Edge Clock

ECP5/ECP5-5G devices have a number of high-speed edge clocks that are intended for use with the PIOs in the implementation of high-speed interfaces. There are two ECLK networks per bank IO on the Left and Right sides of the devices.

Each Edge Clock can be sourced from the following:

- Dedicated Clock input pins (PCLK)

- DLLDEL output (Clock delayed by 90o)

- PLL outputs (CLKOP and CLKOS)

- ECLKBRIDGE

- Internal Nodes

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

In Figure 2.15, note that A\_ALU, B\_ALU and C\_ALU are internal signals generated by combining bits from AA, AB, BA BB and C inputs. For further information, refer to ECP5 and ECP5-5G sysDSP Usage Guide (TN1267).

The ECP5/ECP5-5G sysDSP block supports the following basic elements.

- MULT (Multiply)

- MAC (Multiply, Accumulate)

- MULTADDSUB (Multiply, Addition/Subtraction)

- MULTADDSUBSUM (Multiply, Addition/Subtraction, Summation)

Table 2.7 shows the capabilities of each of the ECP5/ECP5-5G slices versus the above functions.

#### Table 2.7. Maximum Number of Elements in a Slice

| Width of Multiply | x9 | x18 | x36 |

|-------------------|----|-----|-----|

| MULT              | 4  | 2   | 1/2 |

| MAC               | 1  | 1   | -   |

| MULTADDSUB        | 2  | 1   | -   |

| MULTADDSUBSUM     | 1* | 1/2 | _   |

\*Note: One slice can implement 1/2 9x9 m9x9addsubsum and two m9x9addsubsum with two slices.

Some options are available in the four elements. The input register in all the elements can be directly loaded or can be loaded as a shift register from previous operand registers. By selecting "dynamic operation" the following operations are possible:

- In the Add/Sub option the Accumulator can be switched between addition and subtraction on every cycle.

- The loading of operands can switch between parallel and serial operations.

For further information, refer to ECP5 and ECP5-5G sysDSP Usage Guide (TN1267).

### 2.10. Programmable I/O Cells

The programmable logic associated with an I/O is called a PIO. The individual PIO are connected to their respective sysIO buffers and pads. On the ECP5/ECP5-5G devices, the Programmable I/O cells (PIC) are assembled into groups of four PIO cells called a Programmable I/O Cell or PIC. The PICs are placed on all four sides of the device.

On all the ECP5/ECP5-5G devices, two adjacent PIOs can be combined to provide a complementary output driver pair. All PIO pairs can implement differential receivers. Half of the PIO pairs on the left and right edges of these devices can be configured as true LVDS transmit pairs.

### 2.18. Device Configuration

All ECP5/ECP5-5G devices contain two ports that can be used for device configuration. The Test Access Port (TAP), which supports bit-wide configuration, and the sysCONFIG port, support dual-byte, byte and serial configuration. The TAP supports both the IEEE Standard 1149.1 Boundary Scan specification and the IEEE Standard 1532 In-System Configuration specification. There are 11 dedicated pins for TAP and sysConfig supports (TDI, TDO, TCK, TMS, CFG[2:0], PROGRAMN, DONE, INITN and CCLK). The remaining sysCONFIG pins are used as dual function pins. Refer to ECP5 and ECP5-5G sysCONFIG Usage Guide (TN1260) for more information about using the dual-use pins as general purpose I/Os.

There are various ways to configure an ECP5/ECP5-5G device:

- JTAG

- Standard Serial Peripheral Interface (SPI) Interface to boot PROM Support x1, x2, x4 wide SPI memory interfaces.

- System microprocessor to drive a x8 CPU port SPCM mode

- System microprocessor to drive a serial slave SPI port (SSPI mode)

- Slave Serial model (SCM)

On power-up, the FPGA SRAM is ready to be configured using the selected sysCONFIG port. Once a configuration port is selected, it will remain active throughout that configuration cycle. The IEEE 1149.1 port can be activated any time after power-up by sending the appropriate command through the TAP port.

ECP5/ECP5-5G devices also support the Slave SPI Interface. In this mode, the FPGA behaves like a SPI Flash device (slave mode) with the SPI port of the FPGA to perform read-write operations.

#### 2.18.1. Enhanced Configuration Options

ECP5/ECP5-5G devices have enhanced configuration features such as: decryption support, decompression support, TransFR™ I/O and dual-boot and multi-boot image support.

#### TransFR (Transparent Field Reconfiguration)

TransFR I/O (TFR) is a unique Lattice technology that allows users to update their logic in the field without interrupting system operation using a single ispVM command. TransFR I/O allows I/O states to be frozen during device configuration. This allows the device to be field updated with a minimum of system disruption and downtime. Refer to Minimizing System Interruption During Configuration Using TransFR Technology (TN1087) for details.

#### **Dual-Boot and Multi-Boot Image Support**

Dual-boot and multi-boot images are supported for applications requiring reliable remote updates of configuration data for the system FPGA. After the system is running with a basic configuration, a new boot image can be downloaded remotely and stored in a separate location in the configuration storage device. Any time after the update the ECP5/ECP5-5G devices can be re-booted from this new configuration file. If there is a problem, such as corrupt data during download or incorrect version number with this new boot image, the ECP5/ECP5-5G device can revert back to the original backup golden configuration and try again. This all can be done without power cycling the system. For more information, refer to ECP5 and ECP5-5G sysCONFIG Usage Guide (TN1260).

### 2.18.2. Single Event Upset (SEU) Support

ECP5/ECP5-5G devices support SEU mitigation with three supporting functions:

- SED Soft Error Detect

- SEC Soft Error Correction

- SEI Soft Error Injection

ECP5/ECP5-5G devices have dedicated logic to perform Cycle Redundancy Code (CRC) checks. During configuration, the configuration data bitstream can be checked with the CRC logic block. In addition, the ECP5/ECP5-5G device can also be programmed to utilize a Soft Error Detect (SED) mode that checks for soft errors in configuration SRAM. The SED operation can be run in the background during user mode. If a soft error occurs, during user mode (normal operation) the device can be programmed to generate an error signal.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

When an error is detected, and the user's error handling software determines the error did not create any risk to the system operation, the SEC tool allows the device to be re-configured in the background to correct the affected bit. This operation allows the user functions to continue to operate without stopping the system function.

Additional SEI tool is also available in the Diamond Software, by creating a frame of data to be programmed into the device in the background with one bit changed, without stopping the user functions on the device. This emulates an SEU situation, allowing the user to test and monitor its error handling software.

For further information on SED support, refer to LatticeECP3, ECP5 and ECP5-5G Soft Error Detection (SED)/Correction (SEC) Usage Guide (TN1184).

### 2.18.3. On-Chip Oscillator

Every ECP5/ECP5-5G device has an internal CMOS oscillator which is used to derive a Master Clock (MCLK) for configuration. The oscillator and the MCLK run continuously and are available to user logic after configuration is completed. The software default value of the MCLK is nominally 2.4 MHz. Table 2.16 lists all the available MCLK frequencies. When a different Master Clock is selected during the design process, the following sequence takes place:

- 1. Device powers up with a nominal Master Clock frequency of 2.4 MHz.

- 2. During configuration, users select a different master clock frequency.

- 3. The Master Clock frequency changes to the selected frequency once the clock configuration bits are received.

- 4. If the user does not select a master clock frequency, then the configuration bitstream defaults to the MCLK frequency of 2.4 MHz.

This internal oscillator is available to the user by routing it as an input clock to the clock tree. For further information on the use of this oscillator for configuration or user mode, refer to ECP5 and ECP5-5G sysCONFIG Usage Guide (TN1260) and ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263).

#### Table 2.16. Selectable Master Clock (MCLK) Frequencies during Configuration (Nominal)

| MCLK Frequency (MHz) |

|----------------------|

| 2.4                  |

| 4.8                  |

| 9.7                  |

| 19.4                 |

| 38.8                 |

| 62                   |

### 2.19. Density Shifting

The ECP5/ECP5-5G family is designed to ensure that different density devices in the same family and in the same package have the same pinout. Furthermore, the architecture ensures a high success rate when performing design migration from lower density devices to higher density devices. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likelihood of success in each case. An example is that some user I/Os may become No Connects in smaller devices in the same package. Refer to the ECP5/ECP5-5G Pin Migration Tables and Diamond software for specific restrictions and limitations.

### 3.3. Power Supply Ramp Rates

#### Table 3.3. Power Supply Ramp Rates

| Symbol            | Parameter                                | Min  | Тур | Max | Unit |

|-------------------|------------------------------------------|------|-----|-----|------|

| t <sub>RAMP</sub> | Power Supply ramp rates for all supplies | 0.01 | -   | 10  | V/ms |

|                   |                                          |      |     |     |      |

**Note**: Assumes monotonic ramp rates.

### 3.4. **Power-On-Reset Voltage Levels**

#### Table 3.4. Power-On-Reset Voltage Levels

| Symbol | Parameter                                                                                                                       |                      | Min                | Тур  | Max  | Unit |   |

|--------|---------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|------|------|------|---|

| Vporup | All Devices Power-On-Reset ramp-up<br>trip point (Monitoring V <sub>CC</sub> ,<br>V <sub>CCAUX</sub> , and V <sub>CCI08</sub> ) | V <sub>cc</sub>      | 0.90               | -    | 1.00 | V    |   |

|        |                                                                                                                                 |                      | V <sub>CCAUX</sub> | 2.00 | Ι    | 2.20 | V |

|        |                                                                                                                                 | V <sub>CCIO8</sub>   | 0.95               | _    | 1.06 | V    |   |

| N      |                                                                                                                                 | Power-On-Reset ramp- | V <sub>cc</sub>    | 0.77 | Ι    | 0.87 | V |

| Vpordn | All Devices down trip point (Monitoring – V <sub>cc</sub> , and V <sub>ccAUX</sub>                                              | V <sub>CCAUX</sub>   | 1.80               | _    | 2.00 | V    |   |

Notes:

• These POR trip points are only provided for guidance. Device operation is only characterized for power supply voltages specified under recommended operating conditions.

- Only V<sub>CCIO8</sub> has a Power-On-Reset ramp up trip point. All other V<sub>CCIOs</sub> do not have Power-On-Reset ramp up detection.

- V<sub>CCIO8</sub> does not have a Power-On-Reset ramp down detection. V<sub>CCIO8</sub> must remain within the Recommended Operating Conditions to ensure proper operation.

### 3.5. Power up Sequence

Power-On-Reset (POR) puts the ECP5/ECP5-5G device in a reset state. POR is released when V<sub>CC</sub>, V<sub>CCAUX</sub>, and V<sub>CCI08</sub> are ramped above the V<sub>PORUP</sub> voltage, as specified above.

$V_{CCIO8}$  controls the voltage on the configuration I/O pins. If the ECP5/ECP5-5G device is using Master SPI mode to download configuration data from external SPI Flash, it is required to ramp  $V_{CCIO8}$  above  $V_{IH}$  of the external SPI Flash, before at least one of the other two supplies ( $V_{CC}$  and/or  $V_{CCAUX}$ ) is ramped to  $V_{PORUP}$  voltage level. If the system cannot meet this power up sequence requirement, and requires the  $V_{CCIO8}$  to be ramped last, then the system must keep either PROGRAMN or INITN pin LOW during power up, until  $V_{CCIO8}$  reaches  $V_{IH}$  of the external SPI Flash. This ensures the signals driven out on the configuration pins to the external SPI Flash meet the  $V_{IH}$  voltage requirement of the SPI Flash. For LFE5UM/LFE5UM5G devices, it is required to power up  $V_{CCA}$ , before  $V_{CCAUXA}$  is powered up.

### **3.6.** Hot Socketing Specifications

#### Table 3.5. Hot Socketing Specifications

| Symbol | Parameter                                                        | Condition                                      | Min | Тур | Max | Unit |

|--------|------------------------------------------------------------------|------------------------------------------------|-----|-----|-----|------|

| IDK_HS | Input or I/O Leakage Current<br>for Top and Bottom Banks<br>Only | $0 \le V_{IN} \le V_{IH}$ (Max)                | _   | _   | ±1  | mA   |

|        | Input or I/O Leakage Current                                     | $0 \leq V_{\text{IN}} < V_{\text{CCIO}}$       | —   | —   | ±1  | mA   |

| IDK    | for Left and Right Banks Only                                    | $V_{CCIO} \leq V_{IN} \leq V_{CCIO} + 0.5 \ V$ | _   | 18  | _   | mA   |

Notes:

1. V<sub>CC</sub>, V<sub>CCAUX</sub> and V<sub>CCIO</sub> should rise/fall monotonically.

2.  $I_{DK}$  is additive to  $I_{PU}$ ,  $I_{PW}$  or  $I_{BH}$ .

3. LVCMOS and LVTTL only.

4. Hot socket specification defines when the hot socketed device's junction temperature is at 85 °C or below. When the hot socketed device's junction temperature is above 85 °C, the I<sub>DK</sub> current can exceed ±1 mA.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

### 3.12. sysI/O Recommended Operating Conditions

#### Table 3.11. sysl/O Recommended Operating Conditions

| Standard                                             |       | V <sub>ccio</sub> |       |       | V <sub>REF</sub> (V) |       |

|------------------------------------------------------|-------|-------------------|-------|-------|----------------------|-------|

| Standard                                             | Min   | Тур               | Max   | Min   | Тур                  | Max   |

| LVCMOS33 <sup>1</sup>                                | 3.135 | 3.3               | 3.465 | _     | _                    | _     |

| LVCMOS33D <sup>3</sup> Output                        | 3.135 | 3.3               | 3.465 | _     | —                    | _     |

| LVCMOS25 <sup>1</sup>                                | 2.375 | 2.5               | 2.625 | _     | —                    | _     |

| LVCMOS18                                             | 1.71  | 1.8               | 1.89  | —     | —                    | -     |

| LVCMOS15                                             | 1.425 | 1.5               | 1.575 | —     | —                    | _     |

| LVCMOS12 <sup>1</sup>                                | 1.14  | 1.2               | 1.26  | _     | —                    | -     |

| LVTTL33 <sup>1</sup>                                 | 3.135 | 3.3               | 3.465 | —     | —                    | _     |

| SSTL15_I, _II <sup>2</sup>                           | 1.43  | 1.5               | 1.57  | 0.68  | 0.75                 | 0.9   |

| SSTL18_I, _II <sup>2</sup>                           | 1.71  | 1.8               | 1.89  | 0.833 | 0.9                  | 0.969 |

| SSTL135_I, _II <sup>2</sup>                          | 1.28  | 1.35              | 1.42  | 0.6   | 0.675                | 0.75  |

| HSUL12 <sup>2</sup>                                  | 1.14  | 1.2               | 1.26  | 0.588 | 0.6                  | 0.612 |

| MIPI D-PHY LP Input <sup>3, 5</sup>                  | 1.425 | 1.5               | 1.575 | —     | —                    | _     |

| LVDS25 <sup>1, 3</sup> Output                        | 2.375 | 2.5               | 2.625 | _     | —                    | _     |

| subLVS <sup>3</sup> (Input only)                     | —     | _                 | _     | _     | —                    | —     |

| SLVS <sup>3</sup> (Input only)                       | _     | _                 | _     | _     | —                    | -     |

| LVDS25E <sup>3</sup> Output                          | 2.375 | 2.5               | 2.625 | _     | —                    | _     |

| MLVDS <sup>3</sup> Output                            | 2.375 | 2.5               | 2.625 | —     | —                    | _     |

| LVPECL33 <sup>1, 3</sup> Output                      | 3.135 | 3.3               | 3.465 | _     | —                    | _     |

| BLVDS25 <sup>1, 3</sup> Output                       | 2.375 | 2.5               | 2.625 | _     | —                    | -     |

| HSULD12D <sup>2, 3</sup>                             | 1.14  | 1.2               | 1.26  | —     | _                    | _     |

| SSTL135D_I, II <sup>2, 3</sup>                       | 1.28  | 1.35              | 1.42  | —     | _                    | —     |

| SSTL15D_I, II <sup>2, 3</sup>                        | 1.43  | 1.5               | 1.57  | —     |                      | —     |

| SSTL18D_I <sup>1, 2, 3</sup> , II <sup>1, 2, 3</sup> | 1.71  | 1.8               | 1.89  | _     | _                    | _     |

#### Notes:

1. For input voltage compatibility, refer to ECP5 and ECP5-5G sysIO Usage Guide (TN1262).

2.  $V_{REF}$  is required when using Differential SSTL and HSUL to interface to DDR/LPDDR memories.

3. These differential inputs use LVDS input comparator, which uses  $V_{CCAUX}$  power

4. All differential inputs and LVDS25 output are supported in the Left and Right banks only. Refer to ECP5 and ECP5-5G sysIO Usage Guide (TN1262) for details.

5. MIPI D-PHY LP input can be implemented by powering VCCIO to 1.5V, and select MIPI LP primitive to meet MIPI Alliance spec on  $V_{IH}$  and  $V_{IL}$ . It can also be implemented as LVCMOS12 with VCCIO at 1.2V, which would meet  $V_{IH}/V_{IL}$  spec on LVCOM12.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

### 3.14. sysl/O Differential Electrical Characteristics

### 3.14.1. LVDS

Over recommended operating conditions.

#### Table 3.13. LVDS

| Parameter                        | Description                                                | Test Conditions                                              | Min   | Тур  | Max   | Unit |

|----------------------------------|------------------------------------------------------------|--------------------------------------------------------------|-------|------|-------|------|

| $V_{\text{INP}}, V_{\text{INM}}$ | Input Voltage                                              | -                                                            | 0     | _    | 2.4   | V    |

| V <sub>CM</sub>                  | Input Common Mode Voltage                                  | Half the sum of the two Inputs                               | 0.05  | —    | 2.35  | V    |

| V <sub>THD</sub>                 | Differential Input Threshold                               | Difference between the two Inputs                            | ±100  | _    | _     | mV   |

| I <sub>IN</sub>                  | Input Current                                              | Power On or Power Off                                        | -     | —    | ±10   | μΑ   |

| V <sub>OH</sub>                  | Output High Voltage for $V_{\text{OP}}$ or $V_{\text{OM}}$ | R <sub>T</sub> = 100 Ω                                       | -     | 1.38 | 1.60  | V    |

| V <sub>OL</sub>                  | Output Low Voltage for $V_{OP}$ or $V_{OM}$                | R <sub>T</sub> = 100 Ω                                       | 0.9 V | 1.03 | _     | V    |

| V <sub>OD</sub>                  | Output Voltage Differential                                | (V <sub>OP</sub> - V <sub>OM</sub> ), R <sub>T</sub> = 100 Ω | 250   | 350  | 450   | mV   |

| $\Delta V_{\text{OD}}$           | Change in $V_{\text{OD}}$ Between High and Low             | _                                                            | _     | _    | 50    | mV   |

| V <sub>OS</sub>                  | Output Voltage Offset                                      | $(V_{OP} + V_{OM})/2, R_T = 100 \Omega$                      | 1.125 | 1.25 | 1.375 | V    |

| $\Delta V_{OS}$                  | Change in Vos Between H and L                              | —                                                            | -     | _    | 50    | mV   |

| I <sub>SAB</sub>                 | Output Short Circuit Current                               | V <sub>OD</sub> = 0 V Driver outputs shorted to each other   | _     | _    | 12    | mA   |

**Note**: On the left and right sides of the device, this specification is valid only for  $V_{CCIO} = 2.5$  V or 3.3 V.

### 3.14.2. **SSTLD**

All differential SSTL outputs are implemented as a pair of complementary single-ended outputs. All allowable single-ended output classes (class I and class II) are supported in this mode.

### 3.14.3. LVCMOS33D

All I/O banks support emulated differential I/O using the LVCMOS33D I/O type. This option, along with the external resistor network, provides the system designer the flexibility to place differential outputs on an I/O bank with 3.3 V  $V_{CCIO}$ . The default drive current for LVCMOS33D output is 12 mA with the option to change the device strength to 4 mA, 8 mA, 12 mA or 16 mA. Follow the LVCMOS33 specifications for the DC characteristics of the LVCMOS33D.

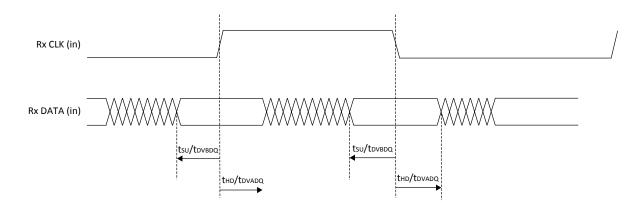

Figure 3.6. Receiver RX.CLK.Centered Waveforms

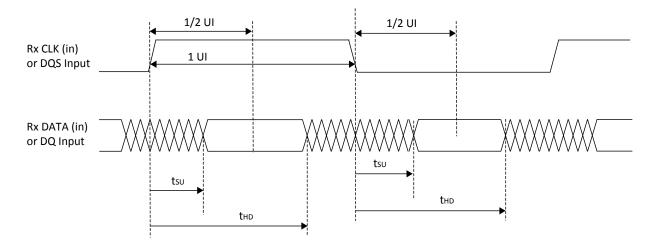

Figure 3.7. Receiver RX.CLK.Aligned and DDR Memory Input Waveforms

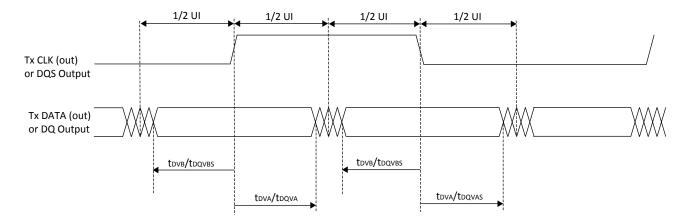

Figure 3.8. Transmit TX.CLK.Centered and DDR Memory Output Waveforms

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### 3.20. SERDES High-Speed Data Transmitter

#### Table 3.24. Serial Output Timing and Levels

| Symbol                                                    | Description                                                          | Min  | Тур                    | Max | Unit    |

|-----------------------------------------------------------|----------------------------------------------------------------------|------|------------------------|-----|---------|

| V <sub>TX-DIFF-PP</sub>                                   | Peak-Peak Differential voltage on selected amplitude <sup>1, 2</sup> | -25% | _                      | 25% | mV, p-p |

| V <sub>TX-CM-DC</sub>                                     | Output common mode voltage                                           | -    | V <sub>CCHTX</sub> / 2 | —   | mV, p-p |

| T <sub>TX-R</sub>                                         | Rise time (20% to 80%)                                               | 50   | _                      | —   | ps      |

| T <sub>TX-F</sub>                                         | Fall time (80% to 20%)                                               | 50   | _                      | —   | ps      |

| T <sub>TX-CM-AC-P</sub>                                   | RMS AC peak common-mode output voltage                               | -    | _                      | 20  | mV      |

| Single ended output impedance for 50/75 Ω                 |                                                                      | -20% | 50/75                  | 20% | Ω       |

| Z <sub>TX_SE</sub> Single ended output impedance for 6K Ω |                                                                      | -25% | 6K                     | 25% | Ω       |

| RL <sub>TX_DIFF</sub>                                     | Differential return loss (with package included) <sup>3</sup>        | -    | -                      | -10 | dB      |

| RL <sub>TX_COM</sub>                                      | Common mode return loss (with package included) <sup>3</sup>         | -    | _                      | -6  | dB      |

#### Notes:

1. Measured with 50  $\Omega$  Tx Driver impedance at V\_{CCHTx} \pm 5\%.

2. Refer to ECP5 and ECP5-5G SERDES/PCS Usage Guide (TN1261) for settings of Tx amplitude.

3. Return los = -10 dB (differential), -6 dB (common mode) for 100 MHz  $\leq$  f <= 1.6 GHz with 50  $\Omega$  output impedance configuration. This includes degradation due to package effects.

#### Table 3.25. Channel Output Jitter

| Description   | Frequency  | Min | Тур | Max  | Unit    |

|---------------|------------|-----|-----|------|---------|

| Deterministic | 5 Gb/s     | _   | _   | TBD  | UI, p-p |

| Random        | 5 Gb/s     | _   | —   | TBD  | UI, p-p |

| Total         | 5 Gb/s     | _   | —   | TBD  | UI, p-p |

| Deterministic | 3.125 Gb/s | —   | _   | 0.17 | UI, p-p |

| Random        | 3.125 Gb/s | _   | _   | 0.25 | UI, p-p |

| Total         | 3.125 Gb/s | _   | _   | 0.35 | UI, p-p |

| Deterministic | 2.5 Gb/s   | _   | _   | 0.17 | UI, p-p |

| Random        | 2.5 Gb/s   | _   | _   | 0.20 | UI, p-p |

| Total         | 2.5 Gb/s   | —   | _   | 0.35 | UI, p-p |

| Deterministic | 1.25 Gb/s  | —   | _   | 0.10 | UI, p-p |

| Random        | 1.25 Gb/s  | _   | -   | 0.22 | UI, p-p |

| Total         | 1.25 Gb/s  | _   | _   | 0.24 | UI, p-p |

Notes:

1. Values are measured with PRBS 2<sup>7</sup>-1, all channels operating, FPGA logic active, I/Os around SERDES pins quiet, reference clock @ 10X mode.

2. For ECP5-5G family devices only.

| Signal Name                          | I/O      | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL, DLL and Clock Functions (Contin | nued)    |                                                                                                                                                                                                                                                                                                                                                                                             |

| [L/R]DQS[group_num]                  | I/O      | DQS input/output pads: T (top), R (right), group_num = ball number associated with DQS[T] pin.                                                                                                                                                                                                                                                                                              |

| [T/R]]DQ[group_num]                  | I/O      | DQ input/output pads: T (top), R (right), group_ num = ball number associated with DQS[T] pin.                                                                                                                                                                                                                                                                                              |

| Test and Programming (Dedicated F    | Pins)    |                                                                                                                                                                                                                                                                                                                                                                                             |

| TMS                                  | I        | Test Mode Select input, used to control the 1149.1 state machine. Pull-up is enabled during configuration. This is a dedicated input pin.                                                                                                                                                                                                                                                   |

| тск                                  | I        | Test Clock input pin, used to clock the 1149.1 state machine. No pull-up enabled.<br>This is a dedicated input pin.                                                                                                                                                                                                                                                                         |

| TDI                                  | I        | Test Data in pin. Used to load data into device using 1149.1 state machine. After power-up, this TAP port can be activated for configuration by sending appropriate command. (Note: once a configuration port is selected it is locked. Another configuration port cannot be selected until the power-up sequence). Pull-up is enabled during configuration. This is a dedicated input pin. |

| TDO                                  | 0        | Output pin. Test Data Out pin used to shift data out of a device using 1149.1.<br>This is a dedicated output pin.                                                                                                                                                                                                                                                                           |

| Configuration Pads (Used during sys  | sCONFIG) |                                                                                                                                                                                                                                                                                                                                                                                             |

| CFG[2:0]                             | I        | Mode pins used to specify configuration mode values latched on rising edge of INITN. During configuration, a pull-up is enabled.<br>These are dedicated pins.                                                                                                                                                                                                                               |

| INITN                                | I/O      | Open Drain pin. Indicates the FPGA is ready to be configured. During configuration, a pull-up is enabled.<br>This is a dedicated pin.                                                                                                                                                                                                                                                       |

| PROGRAMN                             | 1        | Initiates configuration sequence when asserted low. This pin always has an active pull-up.<br>This is a dedicated pin.                                                                                                                                                                                                                                                                      |

| DONE                                 | I/O      | Open Drain pin. Indicates that the configuration sequence is complete, and the startup sequence is in progress.<br>This is a dedicated pin.                                                                                                                                                                                                                                                 |

| ССГК                                 | I/O      | Input Configuration Clock for configuring an FPGA in Slave SPI, Serial, and CPU modes. Output Configuration Clock for configuring an FPGA in Master configuration modes (Master SPI, Master Serial).<br>This is a dedicated pin.                                                                                                                                                            |

| HOLDN/DI/BUSY/CSSPIN/CEN             | I/O      | Parallel configuration mode busy indicator. SPI/SPIm mode data output.<br>This is a shared I/O pin. This is a shared I/O pin. When not in configuration, it can<br>be used as general purpose I/O pin.                                                                                                                                                                                      |

| CSN/SN                               | I/O      | Parallel configuration mode active-low chip select. Slave SPI chip select. This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O pin.                                                                                                                                                                                                                  |

| CS1N                                 | I        | Parallel configuration mode active-low chip select.<br>This is a shared I/O pin. When not in configuration, it can be used as general<br>purpose I/O pin.                                                                                                                                                                                                                                   |

| WRITEN                               | I        | Write enable for parallel configuration modes.<br>This is a shared I/O pin. When not in configuration, it can be used as general<br>purpose I/O pin.                                                                                                                                                                                                                                        |

| DOUT/CSON                            | о        | Serial data output. Chip select output. SPI/SPIm mode chip select. This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O                                                                                                                                                                                                                               |

| D0/MOSI/IO0                          | I/O      | Parallel configuration I/O. Open drain during configuration. When in SPI modes,<br>it is an output in Master mode, and input in Slave mode.<br>This is a shared I/O pin. When not in configuration, it can be used as general<br>purpose I/O pin.                                                                                                                                           |

<sup>© 2014-2018</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Part number          | Grade | Package          | Pins | Temp.      | LUTs (K) | SERDES |

|----------------------|-------|------------------|------|------------|----------|--------|

| LFE5U-85F-6BG756I    | -6    | Lead free caBGA  | 756  | Industrial | 84       | No     |

| LFE5U-85F-7BG756I    | -7    | Lead free caBGA  | 756  | Industrial | 84       | No     |

| LFE5U-85F-8BG756I    | -8    | Lead free caBGA  | 756  | Industrial | 84       | No     |

| LFE5UM-25F-6MG285I   | -6    | Lead free csfBGA | 285  | Industrial | 24       | Yes    |

| LFE5UM-25F-7MG285I   | -7    | Lead free csfBGA | 285  | Industrial | 24       | Yes    |

| LFE5UM-25F-8MG285I   | -8    | Lead free csfBGA | 285  | Industrial | 24       | Yes    |

| LFE5UM-25F-6BG381I   | -6    | Lead free caBGA  | 381  | Industrial | 24       | Yes    |

| LFE5UM-25F-7BG381I   | -7    | Lead free caBGA  | 381  | Industrial | 24       | Yes    |

| LFE5UM-25F-8BG381I   | -8    | Lead free caBGA  | 381  | Industrial | 24       | Yes    |

| LFE5UM-45F-6MG285I   | -6    | Lead free csfBGA | 285  | Industrial | 44       | Yes    |

| LFE5UM-45F-7MG285I   | -7    | Lead free csfBGA | 285  | Industrial | 44       | Yes    |

| LFE5UM-45F-8MG285I   | -8    | Lead free csfBGA | 285  | Industrial | 44       | Yes    |

| LFE5UM-45F-6BG381I   | -6    | Lead free caBGA  | 381  | Industrial | 44       | Yes    |

| LFE5UM-45F-7BG381I   | -7    | Lead free caBGA  | 381  | Industrial | 44       | Yes    |

| LFE5UM-45F-8BG381I   | -8    | Lead free caBGA  | 381  | Industrial | 44       | Yes    |

| LFE5UM-45F-6BG554I   | -6    | Lead free caBGA  | 554  | Industrial | 44       | Yes    |

| LFE5UM-45F-7BG554I   | -7    | Lead free caBGA  | 554  | Industrial | 44       | Yes    |

| LFE5UM-45F-8BG554I   | -8    | Lead free caBGA  | 554  | Industrial | 44       | Yes    |

| LFE5UM-85F-6MG285I   | -6    | Lead free csfBGA | 285  | Industrial | 84       | Yes    |

| LFE5UM-85F-7MG285I   | -7    | Lead free csfBGA | 285  | Industrial | 84       | Yes    |

| LFE5UM-85F-8MG285I   | -8    | Lead free csfBGA | 285  | Industrial | 84       | Yes    |

| LFE5UM-85F-6BG381I   | -6    | Lead free caBGA  | 381  | Industrial | 84       | Yes    |

| LFE5UM-85F-7BG381I   | -7    | Lead free caBGA  | 381  | Industrial | 84       | Yes    |

| LFE5UM-85F-8BG381I   | -8    | Lead free caBGA  | 381  | Industrial | 84       | Yes    |

| LFE5UM-85F-6BG554I   | -6    | Lead free caBGA  | 554  | Industrial | 84       | Yes    |

| LFE5UM-85F-7BG554I   | -7    | Lead free caBGA  | 554  | Industrial | 84       | Yes    |

| LFE5UM-85F-8BG554I   | -8    | Lead free caBGA  | 554  | Industrial | 84       | Yes    |

| LFE5UM-85F-6BG756I   | -6    | Lead free caBGA  | 756  | Industrial | 84       | Yes    |

| LFE5UM-85F-7BG756I   | -7    | Lead free caBGA  | 756  | Industrial | 84       | Yes    |

| LFE5UM-85F-8BG756I   | -8    | Lead free caBGA  | 756  | Industrial | 84       | Yes    |

| LFE5UM5G-25F-8MG285I | -8    | Lead free csfBGA | 285  | Industrial | 24       | Yes    |

| LFE5UM5G-25F-8BG381I | -8    | Lead free caBGA  | 381  | Industrial | 24       | Yes    |

| LFE5UM5G-45F-8MG285I | -8    | Lead free csfBGA | 285  | Industrial | 44       | Yes    |

| LFE5UM5G-45F-8BG381I | -8    | Lead free caBGA  | 381  | Industrial | 44       | Yes    |

| LFE5UM5G-45F-8BG554I | -8    | Lead free caBGA  | 554  | Industrial | 44       | Yes    |

| LFE5UM5G-85F-8MG285I | -8    | Lead free csfBGA | 285  | Industrial | 84       | Yes    |

| LFE5UM5G-85F-8BG381I | -8    | Lead free caBGA  | 381  | Industrial | 84       | Yes    |

| LFE5UM5G-85F-8BG554I | -8    | Lead free caBGA  | 554  | Industrial | 84       | Yes    |

| LFE5UM5G-85F-8BG756I | -8    | Lead free caBGA  | 756  | Industrial | 84       | Yes    |

# **Supplemental Information**

### **For Further Information**

A variety of technical notes for the ECP5/ECP5-5G family are available.

- High-Speed PCB Design Considerations (TN1033)

- Transmission of High-Speed Serial Signals Over Common Cable Media (TN1066)

- PCB Layout Recommendations for BGA Packages (TN1074)

- Minimizing System Interruption During Configuration Using TransFR Technology (TN1087)

- Electrical Recommendations for Lattice SERDES (FPGA-TN-02077)

- LatticeECP3, ECP-5 and ECP5-5G Soft Error Detection (SED)/Correction (SEC) Usage Guide (TN1184)

- Using TraceID (TN1207)

- Sub-LVDS Signaling Using Lattice Devices (TN1210)

- Advanced Security Encryption Key Programming Guide for ECP5, ECP5-5G, LatticeECP3, and LatticeECP2/MS Devices (TN1215)

- LatticeECP3, LatticeECP2/M, ECP5 and ECP5-5G Dual Boot and Multiple Boot Feature (TN1216)

- ECP5 and ECP5-5G sysCONFIG Usage Guide (TN1260)

- ECP5 and ECP5-5G SERDES/PCS Usage Guide (TN1261)

- ECP5 and ECP5-5G sysIO Usage Guide (TN1262)

- ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263)

- ECP5 and ECP5-5G Memory Usage Guide (TN1264)

- ECP5 and ECP5-5G High-Speed I/O Interface (TN1265)

- Power Consumption and Management for ECP5 and ECP5-5G Devices (TN1266)

- ECP5 and ECP5-5G sysDSP Usage Guide (TN1267)

- ECP5 and ECP5-5G Hardware Checklist (FPGA-TN-02038)

- Solder Reflow Guide for Surface Mount Devices (FPGA-TN-02041)

- ECP5 and ECP5-5G PCI Express Soft IP Ease of Use Guidelines (FPGA-TN-02045)

- Programming External SPI Flash through JTAG for ECP5/ECP5-5G (FPGA-TN-02050)

- Adding Scalable Power and Thermal Management to ECP5 Using L-ASC10 (AN6095)

For further information on interface standards refer to the following websites:

- JEDEC Standards (LVTTL, LVCMOS, SSTL): www.jedec.org

- PCI: www.pcisig.com

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

# **Revision History**

| Date          | Version | Section                     | Change Summary                                                                                                                |

|---------------|---------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| March 2018    | 1.9     | All                         | Updated formatting and page referencing.                                                                                      |

|               |         | General Description         | Updated Table 1.1. ECP5 and ECP5-5G Family Selection Guide. Added caBGA256 package in LFE5U-45.                               |

|               |         | Architecture                | Added a row for SGMII in Table 2.13. LFE5UM/LFE5UM5G SERDES<br>Standard Support. Updated footnote #1.                         |

|               |         | DC and Switching            | Updated Table 3.2. Recommended Operating Conditions.                                                                          |

|               |         | Characteristics             | Added 2 rows and updated values in Table 3.7. DC Electrical Characteristics.                                                  |

|               |         |                             | Updated Table 3.8. ECP5/ECP5-5G Supply Current (Standby).                                                                     |

|               |         |                             | Updated Table 3.11. sysl/O Recommended Operating Conditions.                                                                  |

|               |         |                             | Updated Table 3.12. Single-Ended DC Characteristics.                                                                          |

|               |         |                             | Updated Table 3.13. LVDS.                                                                                                     |

|               |         |                             | Updated Table 3.14. LVDS25E DC Conditions.                                                                                    |

|               |         |                             | Updated Table 3.21. ECP5/ECP5-5G Maximum I/O Buffer Speed.                                                                    |

|               |         |                             | Updated Table 3.28. Receiver Total Jitter Tolerance Specification.                                                            |

|               |         |                             | Updated header name of section 3.28 CPRI LV E.24/SGMII(2.5Gbps)<br>Electrical and Timing Characteristics.                     |

|               |         |                             | Updated header name of section 3.29 Gigabit<br>Ethernet/SGMII(1.25Gbps)/CPRI LV E.12 Electrical and Timing<br>Characteristics |

|               |         | Pinout Information          | Updated table in section 4.3.2 LFE5U.                                                                                         |

|               |         | Ordering Information        | Added table rows in 5.2.1 Commercial.                                                                                         |

|               |         |                             | Added table rows in 5.2.2 Industrial.                                                                                         |

|               |         | Supplemental<br>Information | Updated For Further Information section.                                                                                      |

| November 2017 | 1.8     | General Description         | Updated Table 1.1. ECP5 and ECP5-5G Family Selection Guide. Added caBGA256 package in LFE5U-12 and LFE5U-25.                  |