# E. Lattice Semiconductor Corporation - LFE5UM-45F-6BG554C Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                        |

|--------------------------------|-------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 11000                                                                         |

| Number of Logic Elements/Cells | 44000                                                                         |

| Total RAM Bits                 | 1990656                                                                       |

| Number of I/O                  | 245                                                                           |

| Number of Gates                | -                                                                             |

| Voltage - Supply               | 1.045V ~ 1.155V                                                               |

| Mounting Type                  | Surface Mount                                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                               |

| Package / Case                 | 554-FBGA                                                                      |

| Supplier Device Package        | 554-CABGA (23x23)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe5um-45f-6bg554c |

|                                |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Tables

| Table 1.1. ECP5 and ECP5-5G Family Selection Guide                                                                              | 11 |

|---------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2.1. Resources and Modes Available per Slice                                                                              | 14 |

| Table 2.2. Slice Signal Descriptions                                                                                            |    |

| Table 2.3. Number of Slices Required to Implement Distributed RAM                                                               |    |

| Table 2.4. PLL Blocks Signal Descriptions                                                                                       |    |

| Table 2.5. DDRDLL Ports List                                                                                                    |    |

| Table 2.6. sysMEM Block Configurations                                                                                          |    |

| Table 2.7. Maximum Number of Elements in a Slice                                                                                |    |

| Table 2.8. Input Block Port Description                                                                                         |    |

| Table 2.9. Output Block Port Description                                                                                        |    |

| Table 2.10. Tristate Block Port Description                                                                                     |    |

| Table 2.11. DQSBUF Port List Description                                                                                        |    |

| Table 2.12. On-Chip Termination Options for Input Modes                                                                         |    |

| Table 2.13. LFE5UM/LFE5UM5G SERDES Standard Support                                                                             |    |

| Table 2.14. Available SERDES Duals per LFE5UM/LFE5UM5G Devices                                                                  |    |

| Table 2.15. LFE5UM/LFE5UM5G Mixed Protocol Support                                                                              |    |

| Table 2.16. Selectable Master Clock (MCLK) Frequencies during Configuration (Nominal)                                           |    |

| Table 3.1. Absolute Maximum Ratings                                                                                             |    |

| Table 3.2. Recommended Operating Conditions                                                                                     |    |

| Table 3.3. Power Supply Ramp Rates                                                                                              |    |

| Table 3.4. Power-On-Reset Voltage Levels                                                                                        |    |

| Table 3.5. Hot Socketing Specifications                                                                                         |    |

| Table 3.6. Hot Socketing Requirements                                                                                           |    |

| Table 3.7. DC Electrical Characteristics                                                                                        |    |

| Table 3.8. ECP5/ECP5-5G Supply Current (Standby)                                                                                |    |

| Table 3.9. ECP5UM                                                                                                               |    |

| Table 3.10. ECP5-5G                                                                                                             |    |

| Table 3.11. sysI/O Recommended Operating Conditions                                                                             |    |

| Table 3.12. Single-Ended DC Characteristics                                                                                     |    |

| Table 3.13. LVDS                                                                                                                |    |

| Table 3.14. LVDS25E DC Conditions                                                                                               |    |

| Table 3.15. BLVDS25 DC Conditions                                                                                               |    |

| Table 3.16. LVPECL33 DC Conditions                                                                                              |    |

| Table 3.17. MLVDS25 DC Conditions                                                                                               |    |

| Table 3.18. Input to SLVS                                                                                                       |    |

| Table 3.19. Pin-to-Pin Performance                                                                                              |    |

| Table 3.20. Register-to-Register Performance                                                                                    |    |

| Table 3.21. ECP5/ECP5-5G Maximum I/O Buffer Speed                                                                               |    |

| Table 3.22. ECP5/ECP5-5G External Switching Characteristics                                                                     |    |

| Table 3.23. sysCLOCK PLL Timing                                                                                                 |    |

| Table 3.24. Serial Output Timing and Levels                                                                                     |    |

| Table 3.25. Channel Output Jitter                                                                                               |    |

| Table 3.26. SERDES/PCS Latency Breakdown                                                                                        |    |

| Table 3.27. Serial Input Data Specifications         Table 3.28. Passiver Table littler Talerance Specification                 |    |

| Table 3.28. Receiver Total Jitter Tolerance Specification         Table 3.20. External Reference Clock Specification (refeller) |    |

| Table 3.29. External Reference Clock Specification (refclkp/refclkn)         Table 3.20. PCIe (2.5. Ch/c)                       |    |

| Table 3.30. PCIe (2.5 Gb/s)                                                                                                     |    |

| Table 3.31. PCIe (5 Gb/s)<br>Table 3.32. CPRI LV2 E.48 Electrical and Timing Characteristics                                    |    |

| Table 3.32. CPRI LV2 E.48 Electrical and Timing Characteristics                                                                 |    |

| Table 3.33. Transmit                                                                                                            |    |

| Table 3.35. Transmit                                                                                                            |    |

|                                                                                                                                 | 80 |

# 1. General Description

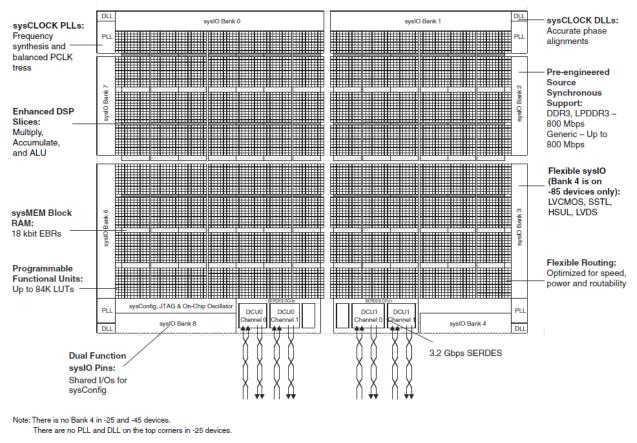

The ECP5/ECP5-5G family of FPGA devices is optimized to deliver high performance features such as an enhanced DSP architecture, high speed SERDES (Serializer/Deserializer), and high speed source synchronous interfaces, in an economical FPGA fabric. This combination is achieved through advances in device architecture and the use of 40 nm technology making the devices suitable for high-volume, highspeed, and low-cost applications.

The ECP5/ECP5-5G device family covers look-up-table (LUT) capacity to 84K logic elements and supports up to 365 user I/Os. The ECP5/ECP5-5G device family also offers up to 156 18 x 18 multipliers and a wide range of parallel I/O standards.

The ECP5/ECP5-5G FPGA fabric is optimized high performance with low power and low cost in mind. The ECP5/ ECP5-5G devices utilize reconfigurable SRAM logic technology and provide popular building blocks such as LUT-based logic, distributed and embedded memory, Phase-Locked Loops (PLLs), Delay-Locked Loops (DLLs), pre-engineered source synchronous I/O support, enhanced sysDSP slices and advanced configuration support, including encryption and dual-boot capabilities.

The pre-engineered source synchronous logic implemented in the ECP5/ECP5-5G device family supports a broad range of interface standards including DDR2/3, LPDDR2/3, XGMII, and 7:1 LVDS.

The ECP5/ECP5-5G device family also features high speed SERDES with dedicated Physical Coding Sublayer (PCS) functions. High jitter tolerance and low transmit jitter allow the SERDES plus PCS blocks to be configured to support an array of popular data protocols including PCI Express, Ethernet (XAUI, GbE, and SGMII) and CPRI. Transmit De-emphasis with pre- and post-cursors, and Receive Equalization settings make the SERDES suitable for transmission and reception over various forms of media.

The ECP5/ECP5-5G devices also provide flexible, reliable and secure configuration options, such as dual-boot capability, bit-stream encryption, and TransFR field upgrade features.

ECP5-5G family devices have made some enhancement in the SERDES compared to ECP5UM devices. These enhancements increase the performance of the SERDES to up to 5 Gb/s data rate.

The ECP5-5G family devices are pin-to-pin compatible with the ECP5UM devices. These allows a migration path for users to port designs from ECP5UM to ECP5-5G devices to get higher performance. The Lattice Diamond<sup>™</sup> design software allows large complex designs to be efficiently implemented using the ECP5/ECP5-5G FPGA family. Synthesis library support for ECP5/ECP5-5G devices is available for popular logic synthesis tools. The Diamond tools use the synthesis tool output along with the constraints from its floor planning tools to place and route the design in the ECP5/ECP5-5G device. The tools extract the timing from the routing and back-annotate it into the design for timing verification.

Lattice provides many pre-engineered IP (Intellectual Property) modules for the ECP5/ECP5-5G family. By using these configurable soft core IPs as standardized blocks, designers are free to concentrate on the unique aspects of their design, increasing their productivity.

### 1.1. Features

- Higher Logic Density for Increased System Integration

- 12K to 84K LUTs

- 197 to 365 user programmable I/Os

- Embedded SERDES

- 270 Mb/s, up to 3.2 Gb/s, SERDES interface (ECP5)

- 270 Mb/s, up to 5.0 Gb/s, SERDES interface (ECP5-5G)

- Supports eDP in RDR (1.62 Gb/s) and HDR (2.7 Gb/s)

- Up to four channels per device: PCI Express, Ethernet (1GbE, SGMII, XAUI), and CPRI

- sysDSP™

- Fully cascadable slice architecture

- 12 to 160 slices for high performance multiply and accumulate

- Powerful 54-bit ALU operations

- Time Division Multiplexing MAC Sharing

- Rounding and truncation

- Each slice supports

- Half 36 x 36, two 18 x 18 or four 9 x 9 multipliers

- Advanced 18 x 36 MAC and 18 x 18 Multiply-Multiply-Accumulate (MMAC) operations

- Flexible Memory Resources

- Up to 3.744 Mb sysMEM<sup>™</sup> Embedded Block RAM (EBR)

- 194K to 669K bits distributed RAM

- sysCLOCK Analog PLLs and DLLs

- Four DLLs and four PLLs in LFE5-45 and LFE5-85; two DLLs and two PLLs in LFE5-25 and LFE5-12

- Pre-Engineered Source Synchronous I/O

- DDR registers in I/O cells

- Dedicated read/write levelling functionality

- Dedicated gearing logic

- Source synchronous standards support

- ADC/DAC, 7:1 LVDS, XGMII

- High Speed ADC/DAC devices

- Dedicated DDR2/DDR3 and LPDDR2/LPDDR3 memory support with DQS logic, up to 800 Mb/s data-rate

- Programmable sysI/O<sup>™</sup> Buffer Supports Wide Range of Interfaces

- On-chip termination

- LVTTL and LVCMOS 33/25/18/15/12

- SSTL 18/15 I, II

- HSUL12

- LVDS, Bus-LVDS, LVPECL, RSDS, MLVDS

- subLVDS and SLVS, MIPI D-PHY input interfaces

- Flexible Device Configuration

- Shared bank for configuration I/Os

- SPI boot flash interface

- Dual-boot images supported

- Slave SPI

- TransFR<sup>™</sup> I/O for simple field updates

- Single Event Upset (SEU) Mitigation Support

- Soft Error Detect Embedded hard macro

- Soft Error Correction Without stopping user operation

- Soft Error Injection Emulate SEU event to debug system error handling

- System Level Support

- IEEE 1149.1 and IEEE 1532 compliant

- Reveal Logic Analyzer

- On-chip oscillator for initialization and general use

- 1.1 V core power supply for ECP5, 1.2 V core power supply for ECP5UM5G

| Device                              | LFE5UM-25<br>LFE5UM5G-25 | LFE5UM-45<br>LFE5UM5G-45 | LFE5UM-85<br>LFE5UM5G-85 | LFE5U-<br>12 | LFE5U-<br>25 | LFE5U-<br>45 | LFE5U-<br>85 |

|-------------------------------------|--------------------------|--------------------------|--------------------------|--------------|--------------|--------------|--------------|

| LUTs (K)                            | 24                       | 44                       | 84                       | 12           | 24           | 44           | 84           |

| sysMEM Blocks (18 Kb)               | 56                       | 108                      | 208                      | 32           | 56           | 108          | 208          |

| Embedded Memory (Kb)                | 1,008                    | 1944                     | 3744                     | 576          | 1,008        | 1944         | 3744         |

| Distributed RAM Bits (Kb)           | 194                      | 351                      | 669                      | 97           | 194          | 351          | 669          |

| 18 X 18 Multipliers                 | 28                       | 72                       | 156                      | 28           | 28           | 72           | 156          |

| SERDES (Dual/Channels)              | 1/2                      | 2/4                      | 2/4                      | 0            | 0            | 0            | 0            |

| PLLs/DLLs                           | 2/2                      | 4/4                      | 4/4                      | 2/2          | 2/2          | 4/4          | 4/4          |

| Packages (SERDES Channels /         | IO Count)                |                          |                          |              |              |              |              |

| 256 caBGA<br>(14 x 14 mm², 0.8 mm)  | _                        | _                        | -                        | 0/197        | 0/197        | 0/197        | _            |

| 285 csfBGA<br>(10 x 10 mm², 0.5 mm) | 2/118                    | 2/118                    | 2/118                    | 0/118        | 0/118        | 0/118        | 0/118        |

| 381 caBGA<br>(17 x 17 mm², 0.8 mm)  | 2/197                    | 4/203                    | 4/205                    | 0/197        | 0/197        | 0/203        | 0/205        |

| 554 caBGA<br>(23 x 23 mm², 0.8 mm)  | _                        | 4/245                    | 4/259                    | _            | _            | 0/245        | 0/259        |

| 756 caBGA<br>(27 x 27 mm², 0.8 mm)  | _                        | _                        | 4/365                    | _            | _            | _            | 0/365        |

#### Table 1.1. ECP5 and ECP5-5G Family Selection Guide

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

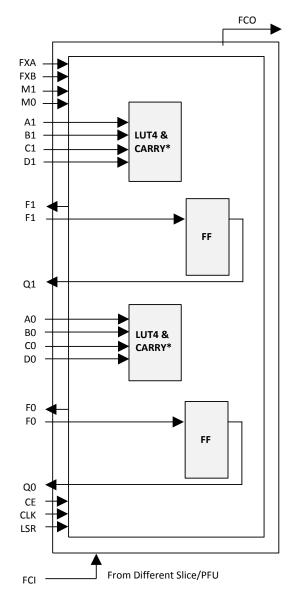

### 2.2. **PFU Blocks**

The core of the ECP5/ECP5-5G device consists of PFU blocks. Each PFU block consists of four interconnected slices numbered 0-3, as shown in Figure 2.2. Each slice contains two LUTs. All the interconnections to and from PFU blocks are from routing. There are 50 inputs and 23 outputs associated with each PFU block.

The PFU block can be used in Distributed RAM or ROM function, or used to perform Logic, Arithmetic, or ROM functions. Table 2.1 shows the functions each slice can perform in either mode.

Notes: For Slices 0 and 1, memory control signals are generated from Slice 2 as follows: WCK is CLK

WRE is from LSR

DI[3:2] for Slice 1 and DI[1:0] for Slice 0 data from Slice 2 WAD [A:D] is a 4-bit address from slice 2 LUT input

Figure 2.3. Slice Diagram

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

### 2.3. Routing

There are many resources provided in the ECP5/ECP5-5G devices to route signals individually or as busses with related control signals. The routing resources consist of switching circuitry, buffers and metal interconnect (routing) segments.

The ECP5/ECP5-5G family has an enhanced routing architecture that produces a compact design. The Diamond design software tool suites take the output of the synthesis tool and places and routes the design.

### 2.4. Clocking Structure

ECP5/ECP5-5G clocking structure consists of clock synthesis blocks (sysCLOCK PLL); balanced clock tree networks (PCLK and ECLK trees); and efficient clock logic modules (CLOCK DIVIDER and Dynamic Clock Select (DCS), Dynamic Clock Control (DCC) and DLL). All of these functions are described below.

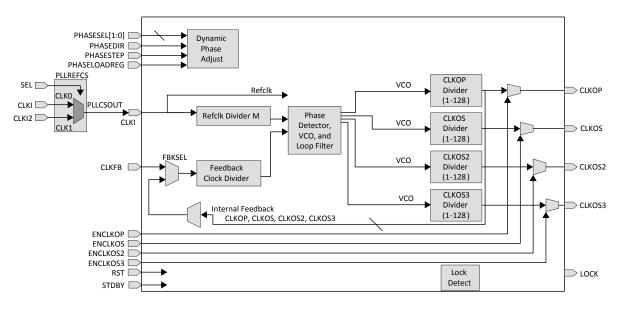

#### 2.4.1. sysCLOCK PLL

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. The devices in the ECP5/ECP5-5G family support two to four full-featured General Purpose PLLs. The sysCLOCK PLLs provide the ability to synthesize clock frequencies.

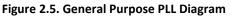

The architecture of the PLL is shown in Figure 2.5. A description of the PLL functionality follows.

CLKI is the reference frequency input to the PLL and its source can come from two different external CLK inputs or from internal routing. A non-glitchless 2-to-1 input multiplexor is provided to dynamically select between two different external reference clock sources. The CLKI input feeds into the input Clock Divider block.

CLKFB is the feedback signal to the PLL which can come from internal feedback path, routing or an external I/O pin. The feedback divider is used to multiply the reference frequency and thus synthesize a higher frequency clock output.

The PLL has four clock outputs CLKOP, CLKOS, CLKOS2 and CLKOS3. Each output has its own output divider, thus allowing the PLL to generate different frequencies for each output. The output dividers can have a value from 1 to 128. The CLKOP, CLKOS, CLKOS2, and CLKOS3 outputs can all be used to drive the primary clock network. Only CLKOP and CLKOS outputs can go to the edge clock network.

The setup and hold times of the device can be improved by programming a phase shift into the CLKOS, CLKOS2, and CLKOS3 output clocks which will advance or delay the output clock with reference to the CLKOP output clock. This phase shift can be either programmed during configuration or can be adjusted dynamically using the PHASESEL, PHASEDIR, PHASESTEP, and PHASELOADREG ports.

The LOCK signal is asserted when the PLL determines it has achieved lock and de-asserted if a loss of lock is detected.

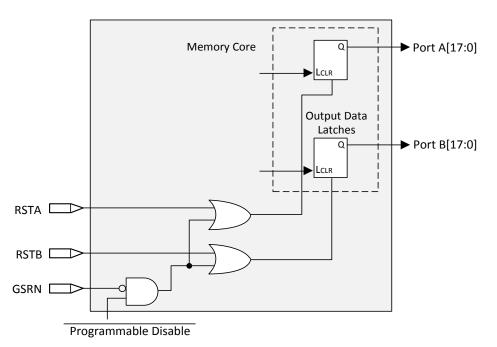

#### 2.8.6. Memory Core Reset

The memory array in the EBR utilizes latches at the A and B output ports. These latches can be reset asynchronously or synchronously. RSTA and RSTB are local signals, which reset the output latches associated with Port A and Port B, respectively. The Global Reset (GSRN) signal can reset both ports. The output data latches and associated resets for both ports are as shown in Figure 2.12.

Figure 2.12. Memory Core Reset

For further information on the sysMEM EBR block, see the list of technical documentation in Supplemental Information section on page 102.

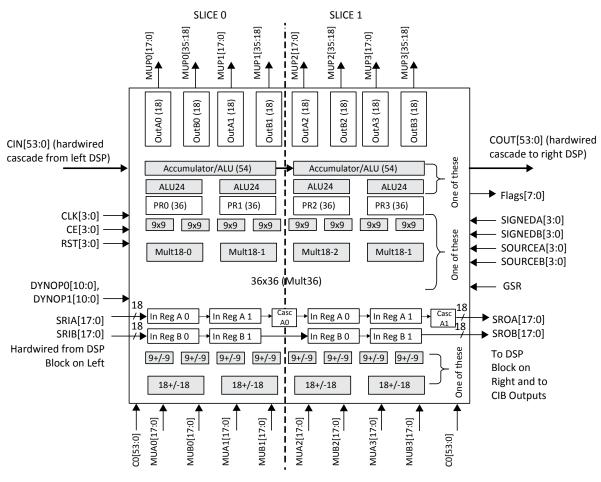

### 2.9. sysDSP<sup>™</sup> Slice

The ECP5/ECP5-5G family provides an enhanced sysDSP architecture, making it ideally suited for low-cost, high-performance Digital Signal Processing (DSP) applications. Typical functions used in these applications are Finite Impulse Response (FIR) filters, Fast Fourier Transforms (FFT) functions, Correlators, Reed-Solomon/Turbo/Convolution encoders and decoders. These complex signal processing functions use similar building blocks such as multiply-adders and multiply-accumulators.

#### 2.9.1. sysDSP Slice Approach Compared to General DSP

Conventional general-purpose DSP chips typically contain one to four (Multiply and Accumulate) MAC units with fixed data-width multipliers; this leads to limited parallelism and limited throughput. Their throughput is increased by higher clock speeds. In the ECP5/ECP5-5G device family, there are many DSP slices that can be used to support different data widths. This allows designers to use highly parallel implementations of DSP functions. Designers can optimize DSP performance vs. area by choosing appropriate levels of parallelism. Figure 2.13 compares the fully serial implementation to the mixed parallel and serial implementation.

- 5\*5 and larger size 2D blocks Semi internal DSP Slice support

- Flexible saturation and rounding options to satisfy a diverse set of applications situations

- Flexible cascading across DSP slices

- Minimizes fabric use for common DSP and ALU functions

- Enables implementation of FIR Filter or similar structures using dedicated sysDSP slice resources only

- Provides matching pipeline registers

- Can be configured to continue cascading from one row of sysDSP slices to another for longer cascade chains

- Flexible and Powerful Arithmetic Logic Unit (ALU) Supports:

- Dynamically selectable ALU OPCODE

- Ternary arithmetic (addition/subtraction of three inputs)

- Bit-wise two-input logic operations (AND, OR, NAND, NOR, XOR and XNOR)

- Eight flexible and programmable ALU flags that can be used for multiple pattern detection scenarios, such as, overflow, underflow and convergent rounding.

- Flexible cascading across slices to get larger functions

- RTL Synthesis friendly synchronous reset on all registers, while still supporting asynchronous reset for legacy users

- Dynamic MUX selection to allow Time Division Multiplexing (TDM) of resources for applications that require processor-like flexibility that enables different functions for each clock cycle

For most cases, as shown in Figure 2.14, the ECP5/ECP5-5G sysDSP slice is backwards-compatible with the LatticeECP2<sup>™</sup> and LatticeECP3<sup>™</sup> sysDSP block, such that, legacy applications can be targeted to the ECP5/ECP5-5G sysDSP slice. Figure 2.14 shows the diagram of sysDSP, and Figure 2.15 shows the detailed diagram.

Figure 2.14. Simplified sysDSP Slice Block Diagram

In Figure 2.15, note that A\_ALU, B\_ALU and C\_ALU are internal signals generated by combining bits from AA, AB, BA BB and C inputs. For further information, refer to ECP5 and ECP5-5G sysDSP Usage Guide (TN1267).

The ECP5/ECP5-5G sysDSP block supports the following basic elements.

- MULT (Multiply)

- MAC (Multiply, Accumulate)

- MULTADDSUB (Multiply, Addition/Subtraction)

- MULTADDSUBSUM (Multiply, Addition/Subtraction, Summation)

Table 2.7 shows the capabilities of each of the ECP5/ECP5-5G slices versus the above functions.

#### Table 2.7. Maximum Number of Elements in a Slice

| Width of Multiply | x9 | x18 | x36 |

|-------------------|----|-----|-----|

| MULT              | 4  | 2   | 1/2 |

| MAC               | 1  | 1   | -   |

| MULTADDSUB        | 2  | 1   | -   |

| MULTADDSUBSUM     | 1* | 1/2 | _   |

\*Note: One slice can implement 1/2 9x9 m9x9addsubsum and two m9x9addsubsum with two slices.

Some options are available in the four elements. The input register in all the elements can be directly loaded or can be loaded as a shift register from previous operand registers. By selecting "dynamic operation" the following operations are possible:

- In the Add/Sub option the Accumulator can be switched between addition and subtraction on every cycle.

- The loading of operands can switch between parallel and serial operations.

For further information, refer to ECP5 and ECP5-5G sysDSP Usage Guide (TN1267).

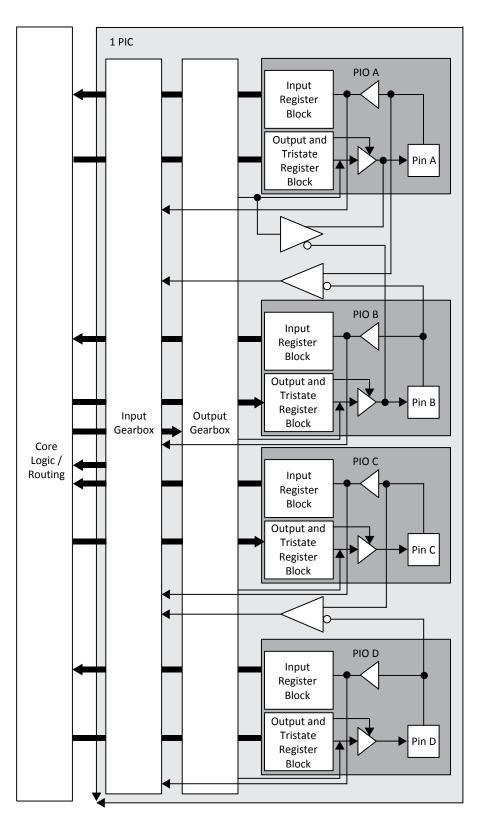

#### 2.10. Programmable I/O Cells

The programmable logic associated with an I/O is called a PIO. The individual PIO are connected to their respective sysIO buffers and pads. On the ECP5/ECP5-5G devices, the Programmable I/O cells (PIC) are assembled into groups of four PIO cells called a Programmable I/O Cell or PIC. The PICs are placed on all four sides of the device.

On all the ECP5/ECP5-5G devices, two adjacent PIOs can be combined to provide a complementary output driver pair. All PIO pairs can implement differential receivers. Half of the PIO pairs on the left and right edges of these devices can be configured as true LVDS transmit pairs.

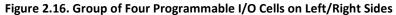

Figure 2.24. DQS Control and Delay Block (DQSBUF)

| Table 2.11 | DQSBUF | <b>Port List</b> | Description |

|------------|--------|------------------|-------------|

|------------|--------|------------------|-------------|

| Name                         | Туре                                               | Description                                                                                    |  |

|------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------|--|

| DQS                          | Input                                              | DDR memory DQS strobe                                                                          |  |

| READ[1:0]                    | Input                                              | Read Input from DDR Controller                                                                 |  |

| READCLKSEL[1:0]              | Input                                              | Read pulse selection                                                                           |  |

| SCLK                         | Input                                              | Slow System Clock                                                                              |  |

| ECLK                         | Input                                              | High Speed Edge Clock (same frequency as DDR memory)                                           |  |

| DQSDEL                       | Input                                              | 90° Delay Code from DDRDLL                                                                     |  |

| RDLOADN, RDMOVE, RDDIRECTION | Input                                              | Dynamic Margin Control ports for Read delay                                                    |  |

| WRLOADN, WRMOVE, WRDIRECTION | Input Dynamic Margin Control ports for Write delay |                                                                                                |  |

| PAUSE                        | Input                                              | Used by DDR Controller to Pause write side signals during DDRDLL Code update or Write Leveling |  |

| DYNDELAY[7:0]                | Input                                              | Dynamic Write Leveling Delay Control                                                           |  |

| DQSR90                       | Output                                             | 90° delay DQS used for Read                                                                    |  |

| DQSW270                      | Output                                             | 90° delay clock used for DQ Write                                                              |  |

| DQSW                         | Output                                             | Clock used for DQS Write                                                                       |  |

| RDPNTR[2:0]                  | Output                                             | Read Pointer for IFIFO module                                                                  |  |

| WRPNTR[2:0]                  | Output                                             | Write Pointer for IFIFO module                                                                 |  |

| DATAVALID                    | Output                                             | Signal indicating start of valid data                                                          |  |

| BURSTDET                     | Output                                             | Burst Detect indicator                                                                         |  |

| RDFLAG                       | Output                                             | Read Dynamic Margin Control output to indicate max value                                       |  |

| WRFLAG                       | Output                                             | Write Dynamic Margin Control output to indicate max value                                      |  |

<sup>© 2014-2018</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Package    | LFE5UM/LFE5UM5G-25 | LFE5UM/LFE5UM5G-45 | LFE5UM/LFE5UM5G-85 |

|------------|--------------------|--------------------|--------------------|

| 285 csfBGA | 1                  | 1                  | 1                  |

| 381 caBGA  | 1                  | 2                  | 2                  |

| 554 caBGA  | -                  | 2                  | 2                  |

| 756 caBGA  | -                  | -                  | 2                  |

#### Table 2.14. Available SERDES Duals per LFE5UM/LFE5UM5G Devices

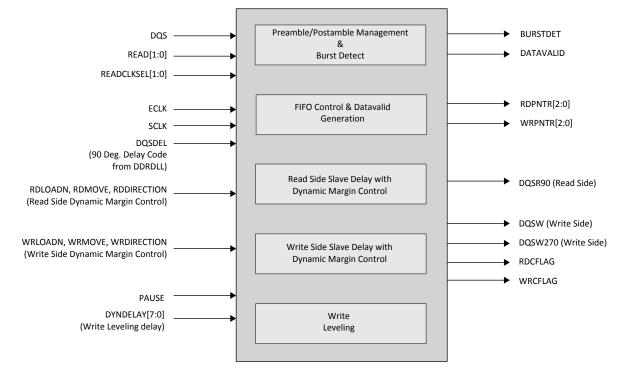

#### 2.15.1. SERDES Block

A SERDES receiver channel may receive the serial differential data stream, equalize the signal, perform Clock and Data Recovery (CDR) and de-serialize the data stream before passing the 8- or 10-bit data to the PCS logic. The SERDES transmitter channel may receive the parallel 8- or 10-bit data, serialize the data and transmit the serial bit stream through the differential drivers. Figure 2.28 shows a single-channel SERDES/PCS block. Each SERDES channel provides a recovered clock and a SERDES transmit clock to the PCS block and to the FPGA core logic.

Each transmit channel, receiver channel, and SERDES PLL shares the same power supply (VCCA). The output and input buffers of each channel have their own independent power supplies (VCCHTX and VCCHRX).

Figure 2.28. Simplified Channel Block Diagram for SERDES/PCS Block

#### 2.15.2. PCS

As shown in Figure 2.28, the PCS receives the parallel digital data from the deserializer and selects the polarity, performs word alignment, decodes (8b/10b), provides Clock Tolerance Compensation and transfers the clock domain from the recovered clock to the FPGA clock via the Down Sample FIFO.

For the transmit channel, the PCS block receives the parallel data from the FPGA core, encodes it with 8b/10b, selects the polarity and passes the 8/10 bit data to the transmit SERDES channel.

The PCS also provides bypass modes that allow a direct 8-bit or 10-bit interface from the SERDES to the FPGA logic. The PCS interface to the FPGA can also be programmed to run at 1/2 speed for a 16-bit or 20-bit interface to the FPGA logic. Some of the enhancements in LFE5UM/LFE5UM5G SERDES/PCS include:

- Higher clock/channel granularity: Dual channel architecture provides more clock resource per channel.

- Enhanced Tx de-emphasis: Programmable pre- and post-cursors improves Tx output signaling

- Bit-slip function in PCS: Improves logic needed to perform Word Alignment function

Refer to ECP5 and ECP5-5G SERDES/PCS Usage Guide (TN1261) for more information.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-DS-02012-1 9

### 3.7. Hot Socketing Requirements

#### **Table 3.6. Hot Socketing Requirements**

| Description                                                                               | Min | Тур | Max | Unit |

|-------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Input current per SERDES I/O pin when device is powered down and inputs driven.           | _   | _   | 8   | mA   |

| Input current per HDIN pin when device power supply is off, inputs driven <sup>1, 2</sup> | _   | _   | 15  | mA   |

| Current per HDIN pin when device power ramps up, input driven <sup>3</sup>                | _   | _   | 50  | mA   |

| Current per HDOUT pin when device power supply is off, outputs pulled up <sup>4</sup>     | —   | —   | 30  | mA   |

Notes:

1. Device is powered down with all supplies grounded, both HDINP and HDINN inputs driven by a CML driver with maximum allowed output V<sub>CCHTX</sub>, 8b/10b data, no external AC coupling.

2. Each P and N input must have less than the specified maximum input current during hot plug. For a device with 2 DCU, the total input current would be 15 mA \* 4 channels \* 2 input pins per channel = 120 mA.

- Device power supplies are ramping up (V<sub>CCA</sub> and V<sub>CCAUX</sub>), both HDINP and HDINN inputs are driven by a CML driver with maximum allowed output V<sub>CCHTX</sub>, 8b/10b data, internal AC coupling.

- 4. Device is powered down with all supplies grounded. Both HDOUTP and HDOUN outputs are pulled up to  $V_{CCHTX}$  by the far end receiver termination of 50  $\Omega$  single ended.

### 3.8. ESD Performance

Refer to the ECP5 and ECP5-5G Product Family Qualification Summary for complete qualification data, including ESD performance.

### 3.9. DC Electrical Characteristics

**Over Recommended Operating Conditions**

| Symbol                                            | Parameter                                                        | Condition                                                                                                                                             | Min | Тур | Max  | Unit |

|---------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| I <sub>IL</sub> , I <sub>IH</sub> <sup>1, 4</sup> | Input or I/O Low Leakage                                         | $0 \leq V_{\text{IN}} \leq V_{\text{CCIO}}$                                                                                                           | _   | —   | 10   | μA   |

| I <sub>IH</sub> <sup>1, 3</sup>                   | Input or I/O High Leakage                                        | $V_{CCIO} < V_{IN} \leq V_{IH(MAX)}$                                                                                                                  | —   | —   | 100  | μA   |

| I                                                 | I/O Active Pull-up Current,<br>sustaining logic HIGH state       | $0.7 \: V_{CCIO} \! \leq \! V_{IN} \! \leq \! V_{CCIO}$                                                                                               | -30 | _   | _    | μA   |

| I <sub>PU</sub>                                   | I/O Active Pull-up Current, pulling down from logic HIGH state   | $0 \leq V_{\text{IN}} \leq 0.7 \; V_{\text{CCIO}}$                                                                                                    |     | _   | -150 | μA   |

| IPD                                               | I/O Active Pull-down Current,<br>sustaining logic LOW state      | $0 \le V_{IN} \le V_{IL}$ (MAX)                                                                                                                       | 30  | —   | —    | μA   |

| IDD                                               | I/O Active Pull-down Current,<br>pulling up from logic LOW state | $0 \leq V_{IN} \leq V_{CCIO}$                                                                                                                         | —   | —   | 150  | μA   |

| C1                                                | I/O Capacitance <sup>2</sup>                                     | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V}, \\ V_{CC} = 1.2 \text{ V}, V_{IO} = 0 \text{ to } V_{IH(MAX)}$ | _   | 5   | 8    | pf   |

| C2                                                | Dedicated Input Capacitance <sup>2</sup>                         | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V}, \\ V_{CC} = 1.2 \text{ V}, V_{IO} = 0 \text{ to } V_{IH(MAX)}$ | _   | 5   | 7    | pf   |

| V                                                 | Hysteresis for Single-Ended                                      | V <sub>CCIO</sub> = 3.3 V                                                                                                                             | -   | 300 | _    | mV   |

| V <sub>HYST</sub>                                 | Inputs                                                           | V <sub>CCIO</sub> = 2.5 V                                                                                                                             | _   | 250 | _    | mV   |

#### **Table 3.7. DC Electrical Characteristics**

Notes:

1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tristated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

2. T<sub>A</sub> 25 °C, f = 1.0 MHz.

- 3. Applicable to general purpose I/Os in top and bottom banks.

- 4. When used as  $V_{REF}$ , maximum leakage= 25  $\mu$ A.

### 3.12. sysI/O Recommended Operating Conditions

#### Table 3.11. sysl/O Recommended Operating Conditions

| Standard                                             |       | V <sub>ccio</sub> |       |       | V <sub>REF</sub> (V) |       |

|------------------------------------------------------|-------|-------------------|-------|-------|----------------------|-------|

| Standard                                             | Min   | Тур               | Max   | Min   | Тур                  | Max   |

| LVCMOS33 <sup>1</sup>                                | 3.135 | 3.3               | 3.465 | —     | _                    | _     |

| LVCMOS33D <sup>3</sup> Output                        | 3.135 | 3.3               | 3.465 | —     | _                    | _     |

| LVCMOS25 <sup>1</sup>                                | 2.375 | 2.5               | 2.625 | —     | —                    | —     |

| LVCMOS18                                             | 1.71  | 1.8               | 1.89  | —     | —                    | -     |

| LVCMOS15                                             | 1.425 | 1.5               | 1.575 | —     | —                    | —     |

| LVCMOS12 <sup>1</sup>                                | 1.14  | 1.2               | 1.26  | —     | —                    | -     |

| LVTTL33 <sup>1</sup>                                 | 3.135 | 3.3               | 3.465 | —     | —                    | —     |

| SSTL15_I, _II <sup>2</sup>                           | 1.43  | 1.5               | 1.57  | 0.68  | 0.75                 | 0.9   |

| SSTL18_I, _II <sup>2</sup>                           | 1.71  | 1.8               | 1.89  | 0.833 | 0.9                  | 0.969 |

| SSTL135_I, _II <sup>2</sup>                          | 1.28  | 1.35              | 1.42  | 0.6   | 0.675                | 0.75  |

| HSUL12 <sup>2</sup>                                  | 1.14  | 1.2               | 1.26  | 0.588 | 0.6                  | 0.612 |

| MIPI D-PHY LP Input <sup>3, 5</sup>                  | 1.425 | 1.5               | 1.575 | —     | —                    | —     |

| LVDS25 <sup>1, 3</sup> Output                        | 2.375 | 2.5               | 2.625 | —     | —                    | —     |

| subLVS <sup>3</sup> (Input only)                     | —     | _                 | _     | —     | —                    | —     |

| SLVS <sup>3</sup> (Input only)                       | _     | _                 | _     | —     | —                    | -     |

| LVDS25E <sup>3</sup> Output                          | 2.375 | 2.5               | 2.625 | —     | —                    | —     |

| MLVDS <sup>3</sup> Output                            | 2.375 | 2.5               | 2.625 | —     | —                    | —     |

| LVPECL33 <sup>1, 3</sup> Output                      | 3.135 | 3.3               | 3.465 | —     | —                    | -     |

| BLVDS25 <sup>1, 3</sup> Output                       | 2.375 | 2.5               | 2.625 | —     | _                    | _     |

| HSULD12D <sup>2, 3</sup>                             | 1.14  | 1.2               | 1.26  | —     | _                    | _     |

| SSTL135D_I, II <sup>2, 3</sup>                       | 1.28  | 1.35              | 1.42  | —     | _                    | —     |

| SSTL15D_I, II <sup>2, 3</sup>                        | 1.43  | 1.5               | 1.57  | —     | _                    | _     |

| SSTL18D_I <sup>1, 2, 3</sup> , II <sup>1, 2, 3</sup> | 1.71  | 1.8               | 1.89  | —     | _                    | _     |

#### Notes:

1. For input voltage compatibility, refer to ECP5 and ECP5-5G sysIO Usage Guide (TN1262).

2.  $V_{REF}$  is required when using Differential SSTL and HSUL to interface to DDR/LPDDR memories.

3. These differential inputs use LVDS input comparator, which uses  $V_{CCAUX}$  power

4. All differential inputs and LVDS25 output are supported in the Left and Right banks only. Refer to ECP5 and ECP5-5G sysIO Usage Guide (TN1262) for details.

5. MIPI D-PHY LP input can be implemented by powering VCCIO to 1.5V, and select MIPI LP primitive to meet MIPI Alliance spec on  $V_{IH}$  and  $V_{IL}$ . It can also be implemented as LVCMOS12 with VCCIO at 1.2V, which would meet  $V_{IH}/V_{IL}$  spec on LVCOM12.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

### 3.25. PCI Express Electrical and Timing Characteristics

#### 3.25.1. PCIe (2.5 Gb/s) AC and DC Characteristics

Over recommended operating conditions.

#### Table 3.30. PCIe (2.5 Gb/s)

| Symbol                                    | Description                                                          | Test Conditions                                        | Min               | Тур  | Max                | Unit |

|-------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------|-------------------|------|--------------------|------|

| Transmit <sup>1</sup>                     | · · · · · · · · · · · · · · · · · · ·                                |                                                        |                   |      |                    |      |

| UI                                        | Unit interval                                                        | -                                                      | 399.88            | 400  | 400.12             | ps   |

| V <sub>TX-DIFF_P-P</sub>                  | Differential peak-to-peak output                                     | -                                                      | 0.8               | 1.0  | 1.2                | V    |

| V <sub>TX-DE-RATIO</sub>                  | De-emphasis differential output voltage ratio                        | _                                                      | -3                | -3.5 | -4                 | dB   |

| V <sub>TX-CM-AC_P</sub>                   | RMS AC peak common-mode output voltage                               | -                                                      | -                 | _    | 20                 | mV   |

| V <sub>TX-RCV-DETECT</sub>                | Amount of voltage change allowed during receiver detection           | _                                                      | _                 | _    | 600                | mV   |

| V <sub>TX-CM-DC</sub>                     | Tx DC common mode voltage                                            | _                                                      | 0                 | _    | V <sub>CCHTX</sub> | V    |

| I <sub>TX-SHORT</sub>                     | Output short circuit current                                         | V <sub>TX-D+</sub> =0.0 V<br>V <sub>TX-D-</sub> =0.0 V | _                 | _    | 90                 | mA   |

| Z <sub>TX-DIFF-DC</sub>                   | Differential output impedance                                        | —                                                      | 80                | 100  | 120                | Ω    |

| RL <sub>TX-DIFF</sub>                     | Differential return loss                                             | _                                                      | 10                | —    | —                  | dB   |

| RL <sub>TX-CM</sub>                       | Common mode return loss                                              | _                                                      | 6.0               | —    | —                  | dB   |

| T <sub>TX-RISE</sub>                      | Tx output rise time                                                  | 20% to 80%                                             | 0.125             | _    | —                  | UI   |

| T <sub>TX-FALL</sub>                      | Tx output fall time                                                  | 20% to 80%                                             | 0.125             | —    | _                  | UI   |

| L <sub>TX-SKEW</sub>                      | Lane-to-lane static output skew for all lanes in port/link           | -                                                      | -                 | _    | 1.3                | ns   |

| T <sub>TX-EYE</sub>                       | Transmitter eye width                                                | -                                                      | 0.75              | _    | _                  | UI   |

| T <sub>TX-EYE-MEDIAN-TO-MAX-</sub> JITTER | Maximum time between jitter median and maximum deviation from median | _                                                      | _                 | _    | 0.125              | UI   |

| Receive <sup>1, 2</sup>                   |                                                                      |                                                        |                   |      |                    |      |

| UI                                        | Unit Interval                                                        | _                                                      | 399.88            | 400  | 400.12             | ps   |

| V <sub>RX-DIFF_P-P</sub>                  | Differential peak-to-peak input voltage                              | _                                                      | 0.34 <sup>3</sup> | _    | 1.2                | v    |

| V <sub>RX-IDLE-DET-DIFF_P-P</sub>         | Idle detect threshold voltage                                        | _                                                      | 65                | _    | 340 <sup>3</sup>   | mV   |

| V <sub>RX-CM-AC_P</sub>                   | RMS AC peak common-mode input voltage                                | _                                                      | _                 | _    | 150                | mV   |

| Z <sub>RX-DIFF-DC</sub>                   | DC differential input impedance                                      | _                                                      | 80                | 100  | 120                | Ω    |

| Z <sub>RX-DC</sub>                        | DC input impedance                                                   | _                                                      | 40                | 50   | 60                 | Ω    |

| Z <sub>RX-HIGH-IMP-DC</sub>               | Power-down DC input impedance                                        | _                                                      | 200K              | _    | _                  | Ω    |

| RL <sub>RX-DIFF</sub>                     | Differential return loss                                             | _                                                      | 10                | _    | _                  | dB   |

| RL <sub>RX-CM</sub>                       | Common mode return loss                                              | _                                                      | 6.0               | _    | _                  | dB   |

#### Notes:

- 1. Values are measured at 2.5 Gb/s.

- 2. Measured with external AC-coupling on the receiver.

- 3. Not in compliance with PCI Express 1.1 standard.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

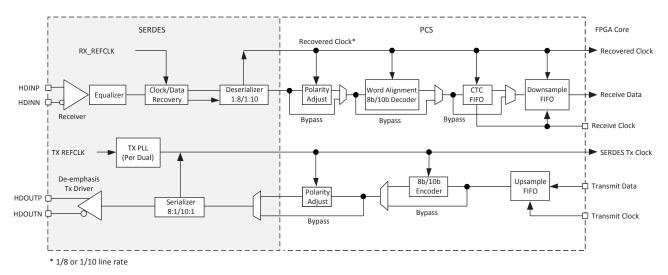

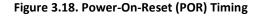

- 1. Time taken from  $V_{CC}$ ,  $V_{CCAUX}$  or  $V_{CCIO8}$ , whichever is the last to cross the POR trip point.

- 2. Device is in a Master Mode (SPI, SPIm).

- 3. The CFG pins are normally static (hardwired).

Figure 3.19. sysCONFIG Port Timing

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

| Signal Name                            | I/O       | Description                                                                                                                                                                                                                                                                                        |

|----------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration Pads (Used during sysCON | FIG) (Con | tinued)                                                                                                                                                                                                                                                                                            |

| D1/MISO/IO1                            | I/O       | Parallel configuration I/O. Open drain during configuration. When in SPI modes, it is an input in Master mode, and output in Slave mode.<br>This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O pin.                                                        |

| D2/IO2                                 | I/O       | Parallel configuration I/O. Open drain during configuration.<br>This is a shared I/O pin. When not in configuration, it can be used as general<br>purpose I/O pin.                                                                                                                                 |

| D3/IO3                                 | I/O       | Parallel configuration I/O. Open drain during configuration.<br>This is a shared I/O pin. When not in configuration, it can be used as general<br>purpose I/O pin.                                                                                                                                 |

| D4/IO4                                 | I/O       | Parallel configuration I/O. Open drain during configuration. This is a shared I/ O pin. When not in configuration, it can be used as general purpose I/O pin.                                                                                                                                      |

| D5/IO5                                 | I/O       | Parallel configuration I/O. Open drain during configuration. This is a shared I/ O pin. When not in configuration, it can be used as general purpose I/O pin.                                                                                                                                      |

| D6/IO6                                 | I/O       | Parallel configuration I/O. Open drain during configuration. When in SPI modes, it is an output in Master mode, and input in Slave mode.<br>This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O pin.                                                        |

| D7/IO7                                 | I/O       | Parallel configuration I/O. Open drain during configuration. When in SPI modes, it is an output in Master mode, and input in Slave mode.<br>This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O pin                                                         |

| SERDES Function                        |           |                                                                                                                                                                                                                                                                                                    |

| VCCAx                                  | _         | SERDES, transmit, receive, PLL and reference clock buffer power supply for<br>SERDES Dual x. All VCCA supply pins must always be powered to the<br>recommended operating voltage range. If no SERDES channels are used,<br>connect VCCA to VCC. VCCAx = 1.1 V for ECP5, VCCAx = 1.2 V for ECP5-5G. |

| VCCAUXAx                               |           | SERDES Aux Power Supply pin for SERDES Dual x. VCCAUXAx = 2.5 V.                                                                                                                                                                                                                                   |

| HDRX[P/N]_D[dual_num]CH[chan_num]      | Ι         | High-speed SERDES inputs, P = Positive, N = Negative, dual_num = [0, 1],<br>chan_num = [0, 1]. These are dedicated SERDES input pins.                                                                                                                                                              |

| HDTX[P/N]_D[dual_num]CH[chan_num]      | 0         | High-speed SERDES outputs, P = Positive, N = Negative, dual_num = [0, 1],<br>chan_num = [0, 1]. These are dedicated SERDES output pins.                                                                                                                                                            |

| REFCLK[P/N]_D[dual_num]                | Ι         | SERDES Reference Clock inputs, P = Positive, N = Negative, dual_num = [0, 1].<br>These are dedicated SERDES input pins.                                                                                                                                                                            |

| VCCHRX_D[dual_num]CH[chan_num]         | _         | SERDES High-Speed Inputs Termination Voltage Supplies, dual_num = [0, 1],<br>chan_num = [0, 1]. These pins should be powered to 1.1 V on ECP5, or<br>1.2 V on ECP5-5G.                                                                                                                             |

| VCCHTX_D[dual_num]CH[chan_num]         | _         | SERDES High-Speed Outputs Buffer Voltage Supplies, dual_num = [0, 1],<br>chan_num = [0, 1]. These pins should be powered to 1.1 V on ECP5, or 1.2 V<br>on ECP5-5G.                                                                                                                                 |

Notes:

1. When placing switching I/Os around these critical pins that are designed to supply the device with the proper reference or supply voltage, care must be given.

2. These pins are dedicated inputs or can be used as general purpose I/O.

3. m defines the associated channel in the quad.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

### 4.2. PICs and DDR Data (DQ) Pins Associated with the DDR Strobe (DQS) Pin

| PICs Associated with DQS Strobe             | PIO within PIC | DDR Strobe (DQS) and Data (DQ) Pins |  |  |  |  |  |  |

|---------------------------------------------|----------------|-------------------------------------|--|--|--|--|--|--|

| For Left and Right Edges of the Device Only |                |                                     |  |  |  |  |  |  |

|                                             | А              | DQ                                  |  |  |  |  |  |  |

|                                             | В              | DQ                                  |  |  |  |  |  |  |

| P[L/R] [n-6]                                | С              | DQ                                  |  |  |  |  |  |  |

| Γ                                           | D              | DQ                                  |  |  |  |  |  |  |

|                                             | А              | DQ                                  |  |  |  |  |  |  |

|                                             | В              | DQ                                  |  |  |  |  |  |  |

| P[L/R] [n-3]                                | С              | DQ                                  |  |  |  |  |  |  |

|                                             | D              | DQ                                  |  |  |  |  |  |  |

|                                             | А              | DQS (P)                             |  |  |  |  |  |  |

|                                             | В              | DQS (N)                             |  |  |  |  |  |  |

| P[L/R] [n] -                                | С              | DQ                                  |  |  |  |  |  |  |

| Γ                                           | D              | DQ                                  |  |  |  |  |  |  |

|                                             | A              | DQ                                  |  |  |  |  |  |  |

|                                             | В              | DQ                                  |  |  |  |  |  |  |

| P[L/R] [n+3]                                | С              | DQ                                  |  |  |  |  |  |  |

|                                             | D              | DQ                                  |  |  |  |  |  |  |

**Note**: "n" is a row PIC number.

### 4.3. **Pin Information Summary**

#### 4.3.1. **LFE5UM/LFE5UM5G**

| Pin Information Summary Pin Type |        | LFE5UM/<br>LFE5UM5G-25 |              | M5G-45        | LFE5UM/LFE5UM5G-85 |              |               |             |              |              |

|----------------------------------|--------|------------------------|--------------|---------------|--------------------|--------------|---------------|-------------|--------------|--------------|

|                                  |        | 285<br>csfBG           | 381<br>caBGA | 285<br>csfBGA | 381<br>caBG        | 554<br>caBGA | 285<br>csfBGA | 381<br>caBG | 554<br>caBGA | 756<br>caBGA |

|                                  | Bank 0 | 6                      | 24           | 6             | 27                 | 32           | 6             | 27          | 32           | 56           |

|                                  | Bank 1 | 6                      | 32           | 6             | 33                 | 40           | 6             | 33          | 40           | 48           |

|                                  | Bank 2 | 21                     | 32           | 21            | 32                 | 32           | 21            | 34          | 32           | 48           |

| General Purpose                  | Bank 3 | 28                     | 32           | 28            | 33                 | 48           | 28            | 33          | 48           | 64           |

| Inputs/Outputs per Bank          | Bank 4 | 0                      | 0            | 0             | 0                  | 0            | 0             | 0           | 14           | 24           |

|                                  | Bank 6 | 26                     | 32           | 26            | 33                 | 48           | 26            | 33          | 48           | 64           |

|                                  | Bank 7 | 18                     | 32           | 18            | 32                 | 32           | 18            | 32          | 32           | 48           |

|                                  | Bank 8 | 13                     | 13           | 13            | 13                 | 13           | 13            | 13          | 13           | 13           |

| Total Single-Ended User I/O      |        | 118                    | 197          | 118           | 203                | 245          | 118           | 205         | 259          | 365          |

| VCC                              |        | 13                     | 20           | 13            | 20                 | 24           | 13            | 20          | 24           | 36           |

| VCCAUX (Core)                    |        | 3                      | 4            | 3             | 4                  | 9            | 3             | 4           | 9            | 8            |

|                                  | Bank O | 1                      | 2            | 1             | 2                  | 3            | 1             | 2           | 3            | 4            |

|                                  | Bank 1 | 1                      | 2            | 1             | 2                  | 3            | 1             | 2           | 3            | 4            |

|                                  | Bank 2 | 2                      | 3            | 2             | 3                  | 4            | 2             | 3           | 4            | 4            |

| VICEIO                           | Bank 3 | 2                      | 3            | 2             | 3                  | 3            | 2             | 3           | 3            | 4            |

| VCCIO                            | Bank 4 | 0                      | 0            | 0             | 0                  | 0            | 0             | 0           | 2            | 2            |

|                                  | Bank 6 | 2                      | 3            | 2             | 3                  | 4            | 2             | 3           | 4            | 4            |

|                                  | Bank 7 | 2                      | 3            | 2             | 3                  | 3            | 2             | 3           | 3            | 4            |

|                                  | Bank 8 | 2                      | 2            | 2             | 2                  | 2            | 2             | 2           | 2            | 2            |

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

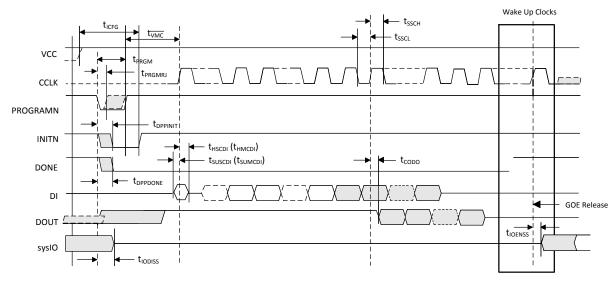

# 5. Ordering Information

#### 5.1. ECP5/ECP5-5G Part Number Description

# **Revision History**

| Date           | Version                             | Section                                                                                               | Change Summary                                                                                                                |

|----------------|-------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| March 2018 1.9 | 1.9                                 | All                                                                                                   | Updated formatting and page referencing.                                                                                      |

|                |                                     | General Description                                                                                   | Updated Table 1.1. ECP5 and ECP5-5G Family Selection Guide. Added caBGA256 package in LFE5U-45.                               |

|                | Architecture                        | Added a row for SGMII in Table 2.13. LFE5UM/LFE5UM5G SERDES<br>Standard Support. Updated footnote #1. |                                                                                                                               |

|                | DC and Switching<br>Characteristics | Updated Table 3.2. Recommended Operating Conditions.                                                  |                                                                                                                               |

|                |                                     | Added 2 rows and updated values in Table 3.7. DC Electrical Characteristics.                          |                                                                                                                               |

|                |                                     | Updated Table 3.8. ECP5/ECP5-5G Supply Current (Standby).                                             |                                                                                                                               |

|                |                                     | Updated Table 3.11. sysl/O Recommended Operating Conditions.                                          |                                                                                                                               |

|                |                                     |                                                                                                       | Updated Table 3.12. Single-Ended DC Characteristics.                                                                          |

|                |                                     |                                                                                                       | Updated Table 3.13. LVDS.                                                                                                     |

|                |                                     |                                                                                                       | Updated Table 3.14. LVDS25E DC Conditions.                                                                                    |

|                |                                     | Updated Table 3.21. ECP5/ECP5-5G Maximum I/O Buffer Speed.                                            |                                                                                                                               |

|                |                                     |                                                                                                       | Updated Table 3.28. Receiver Total Jitter Tolerance Specification.                                                            |

|                |                                     |                                                                                                       | Updated header name of section 3.28 CPRI LV E.24/SGMII(2.5Gbps)<br>Electrical and Timing Characteristics.                     |

|                |                                     |                                                                                                       | Updated header name of section 3.29 Gigabit<br>Ethernet/SGMII(1.25Gbps)/CPRI LV E.12 Electrical and Timing<br>Characteristics |

|                |                                     | Pinout Information                                                                                    | Updated table in section 4.3.2 LFE5U.                                                                                         |

|                | Ordering Information                | Added table rows in 5.2.1 Commercial.                                                                 |                                                                                                                               |

|                |                                     | Added table rows in 5.2.2 Industrial.                                                                 |                                                                                                                               |

|                |                                     | Supplemental<br>Information                                                                           | Updated For Further Information section.                                                                                      |

| November 2017  | 1.8                                 | General Description                                                                                   | Updated Table 1.1. ECP5 and ECP5-5G Family Selection Guide. Added caBGA256 package in LFE5U-12 and LFE5U-25.                  |