# E. Attice Semiconductor Corporation - <u>LFE5UM-45F-7MG285C Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                        |

|--------------------------------|-------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 11000                                                                         |

| Number of Logic Elements/Cells | 44000                                                                         |

| Total RAM Bits                 | 1990656                                                                       |

| Number of I/O                  | 118                                                                           |

| Number of Gates                |                                                                               |

| Voltage - Supply               | 1.045V ~ 1.155V                                                               |

| Mounting Type                  | Surface Mount                                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                               |

| Package / Case                 | 285-LFBGA, CSPBGA                                                             |

| Supplier Device Package        | 285-CSFBGA (10x10)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe5um-45f-7mg285c |

|                                |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 5.1. ECP5/ECP5-5G Part Number Description | 97 |

|-------------------------------------------|----|

| 5.2. Ordering Part Numbers                |    |

| 5.2.1. Commercial                         |    |

| 5.2.2. Industrial                         |    |

| Supplemental Information                  |    |

| For Further Information                   |    |

| Revision History                          |    |

# 2. Architecture

# 2.1. Overview

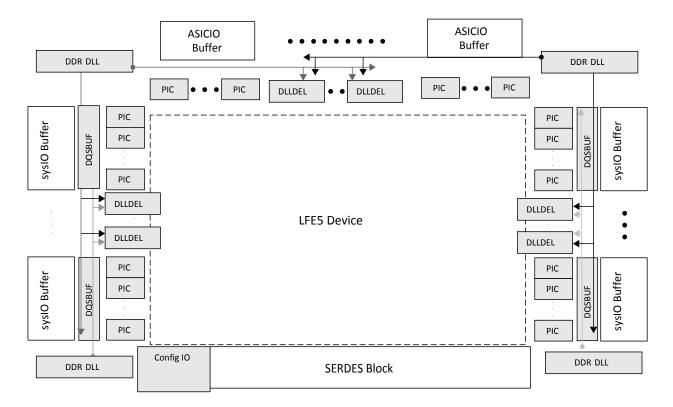

Each ECP5/ECP5-5G device contains an array of logic blocks surrounded by Programmable I/O Cells (PIC). Interspersed between the rows of logic blocks are rows of sysMEM<sup>™</sup> Embedded Block RAM (EBR) and rows of sysDSP<sup>™</sup> Digital Signal Processing slices, as shown in Figure 2.1 on page 13. The LFE5-85 devices have three rows of DSP slices, the LFE5-45 devices have two rows, and both LFE5-25 and LFE5-12 devices have one. In addition, the LFE5UM/LFE5UM5G devices contain SERDES Duals on the bottom of the device.

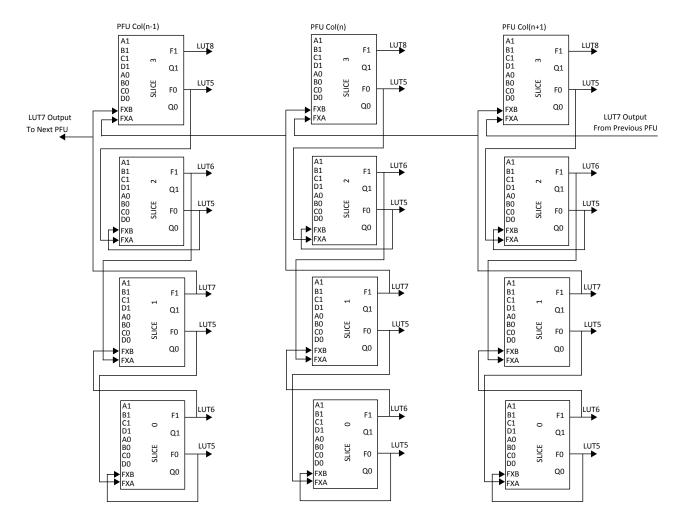

The Programmable Functional Unit (PFU) contains the building blocks for logic, arithmetic, RAM and ROM functions. The PFU block is optimized for flexibility, allowing complex designs to be implemented quickly and efficiently. Logic Blocks are arranged in a two-dimensional array.

The ECP5/ECP5-5G devices contain one or more rows of sysMEM EBR blocks. sysMEM EBRs are large, dedicated 18 Kb fast memory blocks. Each sysMEM block can be configured in a variety of depths and widths as RAM or ROM. In addition, ECP5/ECP5-5G devices contain up to three rows of DSP slices. Each DSP slice has multipliers and adder/accumulators, which are the building blocks for complex signal processing capabilities.

The ECP5 devices feature up to four embedded 3.2 Gb/s SERDES channels, and the ECP5-5G devices feature up to four embedded 5 Gb/s SERDES channels. Each SERDES channel contains independent 8b/10b encoding / decoding, polarity adjust and elastic buffer logic. Each group of two SERDES channels, along with its Physical Coding Sublayer (PCS) block, creates a dual DCU (Dual Channel Unit). The functionality of the SERDES/PCS duals can be controlled by SRAM cell settings during device configuration or by registers that are addressable during device operation. The registers in every dual can be programmed via the SERDES Client Interface (SCI). These DCUs (up to two) are located at the bottom of the devices.

Each PIC block encompasses two PIOs (PIO pairs) with their respective sysI/O buffers. The sysI/O buffers of the ECP5/ECP5-5G devices are arranged in seven banks (eight banks for LFE5-85 devices in caBGA756 and caBGA554 packages), allowing the implementation of a wide variety of I/O standards. One of these banks (Bank 8) is shared with the programming interfaces. Half of the PIO pairs on the left and right edges of the device can be configured as LVDS transmit pairs, and all pairs on left and right can be configured as LVDS receive pairs. The PIC logic in the left and right banks also includes pre-engineered support to aid in the implementation of high speed source synchronous standards such as XGMII, 7:1 LVDS, along with memory interfaces including DDR3 and LPDDR3.

The ECP5/ECP5-5G registers in PFU and sysl/O can be configured to be SET or RESET. After power up and the device is configured, it enters into user mode with these registers SET/RESET according to the configuration setting, allowing the device entering to a known state for predictable system function.

Other blocks provided include PLLs, DLLs and configuration functions. The ECP5/ECP5-5G architecture provides up to four Delay-Locked Loops (DLLs) and up to four Phase-Locked Loops (PLLs). The PLL and DLL blocks are located at the corners of each device.

The configuration block that supports features such as configuration bit-stream decryption, transparent updates and dual-boot support is located at the bottom of each device, to the left of the SERDES blocks. Every device in the ECP5/ECP5-5G family supports a sysCONFIG<sup>™</sup> ports located in that same corner, powered by Vccio8, allowing for serial or parallel device configuration.

In addition, every device in the family has a JTAG port. This family also provides an on-chip oscillator and soft error detect capability. The ECP5 devices use 1.1 V and ECP5UM5G devices use 1.2 V as their core voltage.

| Figure 2.4. Connectivity Supporting LUT5, LUT6, LUT | 7, and LUT8 |

|-----------------------------------------------------|-------------|

|-----------------------------------------------------|-------------|

| Table | 2.2. | Slice | Signal | Descriptions |

|-------|------|-------|--------|--------------|

|-------|------|-------|--------|--------------|

| Function | Туре               | Signal Names   | Description                                                      |

|----------|--------------------|----------------|------------------------------------------------------------------|

| Input    | Data signal        | A0, B0, C0, D0 | Inputs to LUT4                                                   |

| Input    | Data signal        | A1, B1, C1, D1 | Inputs to LUT4                                                   |

| Input    | Multi-purpose      | M0             | Multipurpose Input                                               |

| Input    | Multi-purpose      | M1             | Multipurpose Input                                               |

| Input    | Control signal     | CE             | Clock Enable                                                     |

| Input    | Control signal     | LSR            | Local Set/Reset                                                  |

| Input    | Control signal     | CLK            | System Clock                                                     |

| Input    | Inter-PFU signal   | FCI            | Fast Carry-in <sup>1</sup>                                       |

| Input    | Inter-slice signal | FXA            | Intermediate signal to generate LUT6, LUT7 and LUT8 <sup>2</sup> |

| Input    | Inter-slice signal | FXB            | Intermediate signal to generate LUT6, LUT7 and LUT8 <sup>2</sup> |

| Output   | Data signals       | F0, F1         | LUT4 output register bypass signals                              |

| Output   | Data signals       | Q0, Q1         | Register outputs                                                 |

| Output   | Inter-PFU signal   | FCO            | Fast carry chain output <sup>1</sup>                             |

Notes:

2. Requires two adjacent PFUs.

<sup>1.</sup> See Figure 2.3 on page 15 for connection details.

### 2.2.2. Modes of Operation

Slices 0-2 have up to four potential modes of operation: Logic, Ripple, RAM and ROM. Slice 3 is not needed for RAM mode, it can be used in Logic, Ripple, or ROM modes.

### Logic Mode

In this mode, the LUTs in each slice are configured as 4-input combinatorial lookup tables. A LUT4 can have 16 possible input combinations. Any four input logic functions can be generated by programming this lookup table. Since there are two LUT4s per slice, a LUT5 can be constructed within one slice. Larger look-up tables such as LUT6, LUT7 and LUT8 can be constructed by concatenating other slices. Note that LUT8 requires more than four slices.

### **Ripple Mode**

Ripple mode supports the efficient implementation of small arithmetic functions. In ripple mode, the following functions can be implemented by each slice:

- Addition 2-bit

- Subtraction 2-bit

- Add/Subtract 2-bit using dynamic control

- Up counter 2-bit

- Down counter 2-bit

- Up/Down counter with asynchronous clear

- Up/Down counter with preload (sync)

- Ripple mode multiplier building block

- Multiplier support

- Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Ripple Mode includes an optional configuration that performs arithmetic using fast carry chain methods. In this configuration (also referred to as CCU2 mode) two additional signals, Carry Generate and Carry Propagate, are generated on a per slice basis to allow fast arithmetic functions to be constructed by concatenating Slices.

#### **RAM Mode**

In this mode, a 16x4-bit distributed single port RAM (SPR) can be constructed in one PFU using each LUT block in Slice 0 and Slice 1 as a 16 x 2-bit memory in each slice. Slice 2 is used to provide memory address and control signals. A 16 x 2-bit pseudo dual port RAM (PDPR) memory is created in one PFU by using one Slice as the read-write port and the other companion slice as the read-only port. The slice with the read-write port updates the SRAM data contents in both slices at the same write cycle.

ECP5/ECP5-5G devices support distributed memory initialization.

The Lattice design tools support the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2.3 lists the number of slices required to implement different distributed RAM primitives. For more information about using RAM in ECP5/ECP5-5G devices, refer to ECP5 and ECP5-5G Memory Usage Guide (TN1264).

#### Table 2.3. Number of Slices Required to Implement Distributed RAM

|                  | SPR 16 X 4 | PDPR 16 X 4 |  |  |

|------------------|------------|-------------|--|--|

| Number of slices | 3          | 6           |  |  |

|                  |            |             |  |  |

Note: SPR = Single Port RAM, PDPR = Pseudo Dual Port RAM

#### ROM Mode

ROM mode uses the LUT logic; hence, Slices 0 through 3 can be used in ROM mode. Preloading is accomplished through the programming interface during PFU configuration.

For more information, refer to ECP5 and ECP5-5G Memory Usage Guide (TN1264).

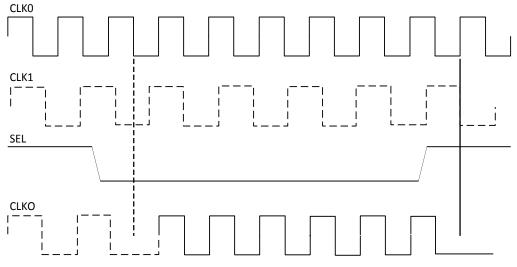

### 2.5.1.2. Dynamic Clock Select

The Dynamic Clock Select (DCS) is a smart multiplexer function available in the primary clock routing. It switches between two independent input clock sources. Depending on the operation modes, it switches between two (2) independent input clock sources either with or without any glitches. This is achieved regardless of when the select signal is toggled. Both input clocks must be running to achieve functioning glitch-less DCS output clock, but it is not required running clocks when used as non-glitch-less normal clock multiplexer.

There are two DCS blocks per device that are fed to all quadrants. The inputs to the DCS block come from all the output of MIDMUXs and Clock from CIB located at the center of the PLC array core. The output of the DCS is connected to one of the inputs of Primary Clock Center MUX.

Figure 2.7 shows the timing waveforms of the default DCS operating mode. The DCS block can be programmed to other modes. For more information about the DCS, refer to ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263).

Figure 2.7. DCS Waveforms

### 2.5.2. Edge Clock

ECP5/ECP5-5G devices have a number of high-speed edge clocks that are intended for use with the PIOs in the implementation of high-speed interfaces. There are two ECLK networks per bank IO on the Left and Right sides of the devices.

Each Edge Clock can be sourced from the following:

- Dedicated Clock input pins (PCLK)

- DLLDEL output (Clock delayed by 90o)

- PLL outputs (CLKOP and CLKOS)

- ECLKBRIDGE

- Internal Nodes

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Figure 2.11. ECP5/ECP5-5G DLL Top Level View (For LFE-45 and LFE-85)

# 2.8. sysMEM Memory

ECP5/ECP5-5G devices contain a number of sysMEM Embedded Block RAM (EBR). The EBR consists of an 18 Kb RAM with memory core, dedicated input registers and output registers with separate clock and clock enable. Each EBR includes functionality to support true dual-port, pseudo dual-port, single-port RAM, ROM and FIFO buffers (via external PFUs).

## 2.8.1. sysMEM Memory Block

The sysMEM block can implement single port, dual port or pseudo dual port memories. Each block can be used in a variety of depths and widths as listed in Table 2.6 on page 25. FIFOs can be implemented in sysMEM EBR blocks by implementing support logic with PFUs. The EBR block facilitates parity checking by supporting an optional parity bit for each data byte. EBR blocks provide byte-enable support for configurations with 18-bit and 36-bit data widths. For more information, refer to ECP5 and ECP5-5G Memory Usage Guide (TN1264).

\*For 7:1 LVDS interface only. It is required to use PIO pair pins PIOA/B.

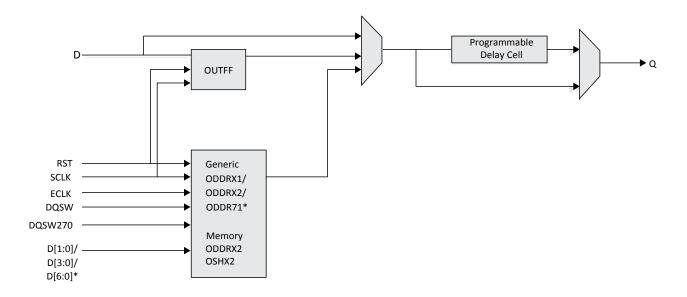

#### Figure 2.20. Output Register Block on Left and Right Sides

| Name                  | Туре   | Description                                                         |

|-----------------------|--------|---------------------------------------------------------------------|

| Q                     | Output | High Speed Data Output                                              |

| D                     | Input  | Data from core to output SDR register                               |

| D[1:0]/D[3:0]/ D[6:0] | Input  | Low Speed Data from device core to output DDR register              |

| RST                   | Input  | Reset to the Output Block                                           |

| SCLK                  | Input  | Slow Speed System Clock                                             |

| ECLK                  | Input  | High Speed Edge Clock                                               |

| DQSW                  | Input  | Clock from DQS control Block used to generate DDR memory DQS output |

| DQSW270               | Input  | Clock from DQS control Block used to generate DDR memory DQ output  |

#### Table 2.9. Output Block Port Description

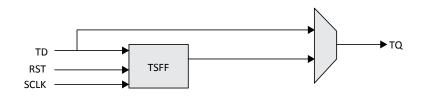

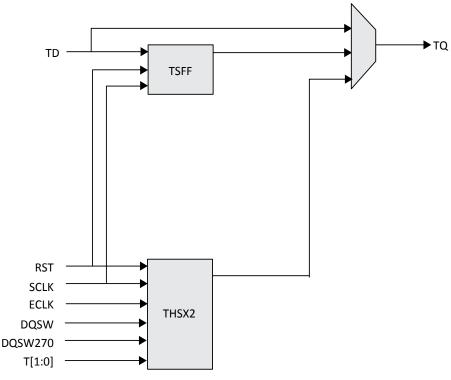

## 2.12. Tristate Register Block

The tristate register block registers tristate control signals from the core of the device before they are passed to the sysIO buffers. The block contains a register for SDR operation. In SDR, TD input feeds one of the flip-flops that then feeds the output. In DDR operation used mainly for DDR memory interface can be implemented on the left and right sides of the device. Here two inputs feed the tristate registers clocked by both ECLK and SCLK.

Figure 2.21 and Figure 2.22 show the Tristate Register Block functions on the device. For detailed description of the tristate register block modes and usage, refer to ECP5 and ECP5-5G High-Speed I/O Interface (TN1265).

Figure 2.21. Tristate Register Block on Top Side

| Name    | Туре   | Description                                                         |

|---------|--------|---------------------------------------------------------------------|

| TD      | Input  | Tristate Input to Tristate SDR Register                             |

| RST     | Input  | Reset to the Tristate Block                                         |

| TD[1:0] | Input  | Tristate input to TSHX2 function                                    |

| SCLK    | Input  | Slow Speed System Clock                                             |

| ECLK    | Input  | High Speed Edge Clock                                               |

| DQSW    | Input  | Clock from DQS control Block used to generate DDR memory DQS output |

| DQSW270 | Input  | Clock from DQS control Block used to generate DDR memory DQ output  |

| TQ      | Output | Output of the Tristate block                                        |

# 2.13. DDR Memory Support

### 2.13.1. DQS Grouping for DDR Memory

Certain PICs have additional circuitry to allow the implementation of high-speed source synchronous and DDR2, DDR3, LPDDR2 or LPDDR3 memory interfaces. The support varies by the edge of the device as detailed below.

The left and right sides of the PIC have fully functional elements supporting DDR2, DDR3, LPDDR2 or LPDDR3 memory interfaces. Every 16 PIOs on the left and right sides are grouped into one DQS group, as shown in Figure 2.23 on page 36. Within each DQS group, there are two pre-placed pins for DQS and DQS# signals. The rest of the pins in the DQS group can be used as DQ signals and DM signal. The number of pins in each DQS group bonded out is package dependent. DQS groups with less than 11 pins bonded out can only be used for LPDDR2/3 Command/ Address busses. In DQS groups with more than 11 pins bonded out, up to two pre-defined pins are assigned to be used as "virtual" VCCIO, by driving these pins to HIGH, with the user connecting these pins to VCCIO power supply. These connections create "soft" connections to V<sub>CCIO</sub> thru these output pins, and make better connections on VCCIO to help to reduce SSO noise. For details, refer to ECP5 and ECP5-5G High-Speed I/O Interface (TN1265).

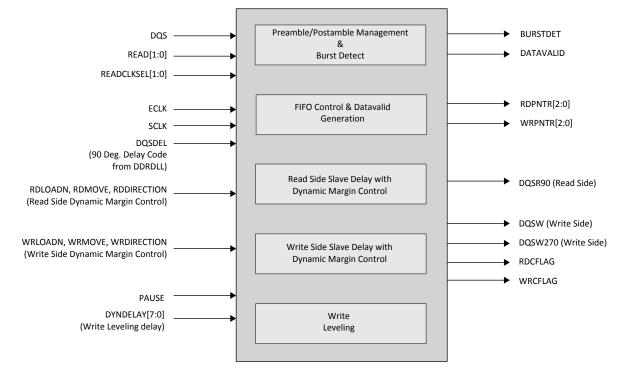

Figure 2.24. DQS Control and Delay Block (DQSBUF)

| Table 2.11 | DQSBUF | <b>Port List</b> | Description |

|------------|--------|------------------|-------------|

|------------|--------|------------------|-------------|

| Name                         | Туре   | Description                                                                                    |  |  |

|------------------------------|--------|------------------------------------------------------------------------------------------------|--|--|

| DQS                          | Input  | DDR memory DQS strobe                                                                          |  |  |

| READ[1:0]                    | Input  | Read Input from DDR Controller                                                                 |  |  |

| READCLKSEL[1:0]              | Input  | Read pulse selection                                                                           |  |  |

| SCLK                         | Input  | Slow System Clock                                                                              |  |  |

| ECLK                         | Input  | High Speed Edge Clock (same frequency as DDR memory)                                           |  |  |

| DQSDEL                       | Input  | 90° Delay Code from DDRDLL                                                                     |  |  |

| RDLOADN, RDMOVE, RDDIRECTION | Input  | Dynamic Margin Control ports for Read delay                                                    |  |  |

| WRLOADN, WRMOVE, WRDIRECTION | Input  | Dynamic Margin Control ports for Write delay                                                   |  |  |

| PAUSE                        | Input  | Used by DDR Controller to Pause write side signals during DDRDLL Code update or Write Leveling |  |  |

| DYNDELAY[7:0]                | Input  | Dynamic Write Leveling Delay Control                                                           |  |  |

| DQSR90                       | Output | 90° delay DQS used for Read                                                                    |  |  |

| DQSW270                      | Output | 90° delay clock used for DQ Write                                                              |  |  |

| DQSW                         | Output | Clock used for DQS Write                                                                       |  |  |

| RDPNTR[2:0]                  | Output | Read Pointer for IFIFO module                                                                  |  |  |

| WRPNTR[2:0]                  | Output | Write Pointer for IFIFO module                                                                 |  |  |

| DATAVALID                    | Output | Signal indicating start of valid data                                                          |  |  |

| BURSTDET                     | Output | Burst Detect indicator                                                                         |  |  |

| RDFLAG                       | Output | Read Dynamic Margin Control output to indicate max value                                       |  |  |

| WRFLAG                       | Output | Write Dynamic Margin Control output to indicate max value                                      |  |  |

<sup>© 2014-2018</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# 2.15. SERDES and Physical Coding Sublayer

LFE5UM/LFE5UM5G devices feature up to 4 channels of embedded SERDES/PCS arranged in dual-channel blocks at the bottom of the devices. Each channel supports up to 3.2 Gb/s (ECP5), or up to 5 Gb/s (ECP5-5G) data rate. Figure 2.27 shows the position of the dual blocks for the LFE5-85. Table 2.13 shows the location of available SERDES Duals for all devices. The LFE5UM/LFE5UM5G SERDES/PCS supports a range of popular serial protocols, including:

- PCI Express Gen1 and Gen2 (2.5 Gb/s) on ECP5UM; Gen 1, Gen2 (2.5 Gb/s and 5 Gb/s) on ECP5-5G

- Ethernet (XAUI, GbE 1000 Base CS/SX/LX and SGMII)

- SMPTE SDI (3G-SDI, HD-SDI, SD-SDI)

- CPRI (E.6.LV: 614.4 Mb/s, E.12.LV: 1228.8 Mb/s, E.24.LV: 2457.6 Mb/s, E.30.LV: 3072 Mb/s), also E.48.LV2:4915 Mb/s in ECP5-5G

- JESD204A/B ADC and DAC converter interface: 312.5 Mb/s to 3.125 Gb/s (ECP5) / 5 Gb/s (ECP5-5G)

Each dual contains two dedicated SERDES for high speed, full duplex serial data transfer. Each dual also has a PCS block that interfaces to the SERDES channels and contains protocol specific digital logic to support the standards listed above. The PCS block also contains interface logic to the FPGA fabric. All PCS logic for dedicated protocol support can also be bypassed to allow raw 8-bit or 10-bit interfaces to the FPGA fabric.

Even though the SERDES/PCS blocks are arranged in duals, multiple baud rates can be supported within a dual with the use of dedicated, per channel /1, /2 and /11 rate dividers. Additionally, two duals can be arranged together to form x4 channel link.

ECP5UM devices and ECP5-5G devices are pin-to-pin compatible. But, the ECP5UM devices require 1.1 V on VCCA, VCCHRX and VCCHTX supplies. ECP5-5G devices require 1.2 V on these supplies. When designing either family device with migration in mind, these supplies need to be connected such that it is possible to adjust the voltage level on these supplies.

When a SERDES Dual in a 2-Dual device is not used, the power VCCA power supply for that Dual should be connected. It is advised to connect the VCCA of unused channel to core if the user knows he will not use the Dual at all, or it should be connected to a different regulated supply, if that Dual may be used in the future.

For an unused channel in a Dual, it is advised to connect the VCCHTX to VCCA, and user can leave VCCHRX unconnected.

For information on how to use the SERDES/PCS blocks to support specific protocols, as well on how to combine multiple protocols and baud rates within a device, refer to ECP5 and ECP5-5G SERDES/PCS Usage Guide (TN1261).

# 3.13. sysI/O Single-Ended DC Electrical Characteristics

| Input/Output                   | VIL     |                             | V <sub>IH</sub>          |         | V <sub>oL</sub> Max | V <sub>он</sub> Min      | L 1 (m A)              | 1 1 (                  |

|--------------------------------|---------|-----------------------------|--------------------------|---------|---------------------|--------------------------|------------------------|------------------------|

| Standard                       | Min (V) | Max (V)                     | Min (V)                  | Max (V) | (V)                 | (V)                      | I <sub>OL</sub> 1 (mA) | I <sub>он</sub> 1 (mA) |

| LVCMOS33                       | -0.3    | 0.8                         | 2.0                      | 3.465   | 0.4                 | V <sub>CCIO</sub> – 0.4  | 16, 12, 8, 4           | -16, -12,<br>-8, -4    |

| LVCMOS25                       | -0.3    | 0.7                         | 1.7                      | 3.465   | 0.4                 | V <sub>CCIO</sub> – 0.4  | 12, 8, 4               | -12, -8, -4            |

| LVCMOS18                       | -0.3    | 0.35 V <sub>CCIO</sub>      | 0.65 V <sub>CCIO</sub>   | 3.465   | 0.4                 | V <sub>CCIO</sub> – 0.4  | 12, 8, 4               | -12, -8, -4            |

| LVCMOS15                       | -0.3    | 0.35 V <sub>CCIO</sub>      | 0.65 V <sub>CCIO</sub>   | 3.465   | 0.4                 | $V_{CCIO} - 0.4$         | 8, 4                   | -8, -4                 |

| LVCMOS12                       | -0.3    | 0.35 V <sub>CCIO</sub>      | 0.65 V <sub>CCIO</sub>   | 3.465   | 0.4                 | $V_{CCIO} - 0.4$         | 8, 4                   | -8, -4                 |

| LVTTL33                        | -0.3    | 0.8                         | 2.0                      | 3.465   | 0.4                 | V <sub>CCIO</sub> – 0.4  | 16, 12, 8, 4           | -16, -12,<br>-8, -4    |

| SSTL18_I<br>(DDR2 Memory)      | -0.3    | V <sub>REF</sub> –<br>0.125 | V <sub>REF</sub> + 0.125 | 3.465   | 0.4                 | V <sub>CCIO</sub> – 0.4  | 6.7                    | -6.7                   |

| SSTL18_II                      | -0.3    | V <sub>REF</sub> -          | V <sub>REF</sub> + 0.125 | 3.465   | 0.28                | V <sub>CCIO</sub> -0.28  | 13.4                   | -13.4                  |

| SSTL15 _I<br>(DDR3 Memory)     | -0.3    | $V_{REF} - 0.1$             | V <sub>REF</sub> + 0.1   | 3.465   | 0.31                | V <sub>CCIO</sub> -0.31  | 7.5                    | -7.5                   |

| SSTL15_II<br>(DDR3 Memory)     | -0.3    | V <sub>REF</sub> -0.1       | V <sub>REF</sub> + 0.1   | 3.465   | 0.31                | V <sub>CCIO</sub> -0.31  | 8.8                    | -8.8                   |

| SSTL135_I<br>(DDR3L Memory)    | -0.3    | V <sub>REF</sub> -0.09      | V <sub>REF</sub> + 0.09  | 3.465   | 0.27                | V <sub>CCIO</sub> – 0.27 | 7                      | -7                     |

| SSTL135_II<br>(DDR3L Memory)   | -0.3    | V <sub>REF</sub> -0.09      | V <sub>REF</sub> + 0.09  | 3.465   | 0.27                | V <sub>CCIO</sub> – 0.27 | 8                      | -8                     |

| MIPI D-PHY (LP) <sup>3</sup>   | -0.3    | 0.55                        | 0.88                     | 3.465   | _                   | _                        | _                      | _                      |

| HSUL12<br>(LPDDR2/3<br>Memory) | -0.3    | V <sub>REF</sub> -0.1       | V <sub>REF</sub> + 0.1   | 3.465   | 0.3                 | V <sub>CCIO</sub> – 0.3  | 4                      | -4                     |

### Table 3.12. Single-Ended DC Characteristics

Notes:

1. For electromigration, the average DC current drawn by the I/O pads within a bank of I/Os shall not exceed 10 mA per I/O (All I/Os used in the same V<sub>CCIO</sub>).

2. Not all IO types are supported in all banks. Refer to ECP5 and ECP5-5G sysIO Usage Guide (TN1262) for details.

3. MIPI D-PHY LP input can be implemented by powering VCCIO to 1.5V, and select MIPI LP primitive to meet MIPI Alliance spec on V<sub>IH</sub> and V<sub>IL</sub>. It can also be implemented as LVCMOS12 with VCCIO at 1.2V, which would meet V<sub>IH</sub>/V<sub>IL</sub> spec on LVCOM12.

# 3.14. sysl/O Differential Electrical Characteristics

### 3.14.1. LVDS

Over recommended operating conditions.

### Table 3.13. LVDS

| Parameter                        | Description                                                | Test Conditions                                              | Min   | Тур  | Max   | Unit |

|----------------------------------|------------------------------------------------------------|--------------------------------------------------------------|-------|------|-------|------|

| $V_{\text{INP}}, V_{\text{INM}}$ | Input Voltage                                              | -                                                            | 0     | _    | 2.4   | V    |

| V <sub>CM</sub>                  | Input Common Mode Voltage                                  | Half the sum of the two Inputs                               | 0.05  | —    | 2.35  | V    |

| V <sub>THD</sub>                 | Differential Input Threshold                               | Difference between the two Inputs                            | ±100  | _    | _     | mV   |

| I <sub>IN</sub>                  | Input Current                                              | Power On or Power Off                                        | -     | —    | ±10   | μΑ   |

| V <sub>OH</sub>                  | Output High Voltage for $V_{\text{OP}}$ or $V_{\text{OM}}$ | R <sub>T</sub> = 100 Ω                                       | -     | 1.38 | 1.60  | V    |

| V <sub>OL</sub>                  | Output Low Voltage for $V_{OP}$ or $V_{OM}$                | R <sub>T</sub> = 100 Ω                                       | 0.9 V | 1.03 | _     | V    |

| V <sub>OD</sub>                  | Output Voltage Differential                                | (V <sub>OP</sub> - V <sub>OM</sub> ), R <sub>T</sub> = 100 Ω | 250   | 350  | 450   | mV   |

| $\Delta V_{\text{OD}}$           | Change in $V_{\text{OD}}$ Between High and Low             | _                                                            | _     | _    | 50    | mV   |

| V <sub>OS</sub>                  | Output Voltage Offset                                      | $(V_{OP} + V_{OM})/2, R_T = 100 \Omega$                      | 1.125 | 1.25 | 1.375 | V    |

| $\Delta V_{OS}$                  | Change in Vos Between H and L                              | —                                                            | -     | _    | 50    | mV   |

| I <sub>SAB</sub>                 | Output Short Circuit Current                               | V <sub>OD</sub> = 0 V Driver outputs shorted to each other   | _     | _    | 12    | mA   |

**Note**: On the left and right sides of the device, this specification is valid only for  $V_{CCIO} = 2.5$  V or 3.3 V.

### 3.14.2. **SSTLD**

All differential SSTL outputs are implemented as a pair of complementary single-ended outputs. All allowable single-ended output classes (class I and class II) are supported in this mode.

### 3.14.3. LVCMOS33D

All I/O banks support emulated differential I/O using the LVCMOS33D I/O type. This option, along with the external resistor network, provides the system designer the flexibility to place differential outputs on an I/O bank with 3.3 V  $V_{CCIO}$ . The default drive current for LVCMOS33D output is 12 mA with the option to change the device strength to 4 mA, 8 mA, 12 mA or 16 mA. Follow the LVCMOS33 specifications for the DC characteristics of the LVCMOS33D.

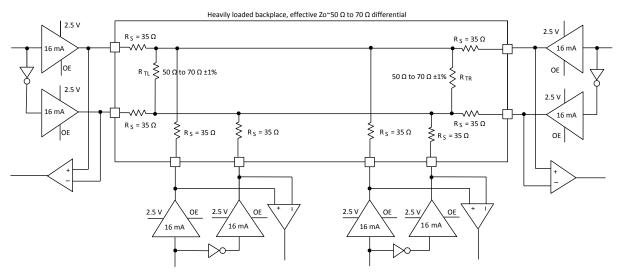

# 3.14.7. MLVDS25

The ECP5/ECP5-5G devices support the differential MLVDS standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The MLVDS input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3.4 is one possible solution for MLVDS standard implementation. Resistor values in the figure are industry standard values for 1% resistors.

Figure 3.4. MLVDS25 (Multipoint Low Voltage Differential Signaling)

| Devenetor         | Description                    | Туј     | Typical |      |  |  |  |

|-------------------|--------------------------------|---------|---------|------|--|--|--|

| Parameter         | Description                    | Zo=50 Ω | Zo=70 Ω | Unit |  |  |  |

| V <sub>CCIO</sub> | Output Driver Supply (±5%)     | 2.50    | 2.50    | V    |  |  |  |

| Z <sub>OUT</sub>  | Driver Impedance               | 10.00   | 10.00   | Ω    |  |  |  |

| R <sub>s</sub>    | Driver Series Resistor (±1%)   | 35.00   | 35.00   | Ω    |  |  |  |

| R <sub>TL</sub>   | Driver Parallel Resistor (±1%) | 50.00   | 70.00   | Ω    |  |  |  |

| R <sub>TR</sub>   | Receiver Termination (±1%)     | 50.00   | 70.00   | Ω    |  |  |  |

| V <sub>OH</sub>   | Output High Voltage            | 1.52    | 1.60    | V    |  |  |  |

| V <sub>OL</sub>   | Output Low Voltage             | 0.98    | 0.90    | V    |  |  |  |

| V <sub>OD</sub>   | Output Differential Voltage    | 0.54    | 0.70    | V    |  |  |  |

| V <sub>CM</sub>   | Output Common Mode Voltage     | 1.25    | 1.25    | V    |  |  |  |

| I <sub>DC</sub>   | DC Output Current              | 21.74   | 20.00   | mA   |  |  |  |

### Table 3.17. MLVDS25 DC Conditions

**Note**: For input buffer, see LVDS Table 3.13 on page 55.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Davamatar                                | Description                                                      | Device         |          | -8        | -         | -7       | -          | -6         | 11               |

|------------------------------------------|------------------------------------------------------------------|----------------|----------|-----------|-----------|----------|------------|------------|------------------|

| Parameter                                | Description                                                      | Device         | Min      | Max       | Min       | Max      | Min        | Max        | Unit             |

| t <sub>h_delpll</sub>                    | Clock to Data Hold - PIO Input<br>Register with Data Input Delay | All Devices    | 0        | -         | 0         | -        | 0          | -          | ns               |

| Generic DDR Input                        |                                                                  |                |          |           |           |          |            |            |                  |

| Generic DDRX1 Inp                        | uts With Clock and Data Centere                                  | d at Pin (GDDI | RX1_RX.S | CLK.Cen   | tered) Us | ing PCLk | Clock In   | put - Fig  | ure 3.6          |

| t <sub>SU_GDDRX1_centered</sub>          | Data Setup Before CLK Input                                      | All Devices    | 0.52     | -         | 0.52      | -        | 0.52       | -          | ns               |

| $t_{HD_GDDRX1_centered}$                 | Data Hold After CLK Input                                        | All Devices    | 0.52     | _         | 0.52      | _        | 0.52       | _          | ns               |

| $f_{DATA\_GDDRX1\_centered}$             | GDDRX1 Data Rate                                                 | All Devices    | _        | 500       | —         | 500      | —          | 500        | Mb/s             |

| $f_{MAX\_GDDRX1\_centered}$              | GDDRX1 CLK Frequency (SCLK)                                      | All Devices    | _        | 250       | —         | 250      | _          | 250        | MHz              |

| Generic DDRX1 Inp                        | uts With Clock and Data Aligned                                  | at Pin (GDDR)  | (1_RX.SC | LK.Aligne | ed) Using | PCLK Cl  | ock Input  | t - Figure | 3.7              |

| $t_{SU\_GDDRX1\_aligned}$                | Data Setup from CLK Input                                        | All Devices    | -        | -0.55     | -         | -0.55    | -          | -0.55      | ns +<br>1/2 UI   |

| $t_{HD\_GDDRX1\_aligned}$                | Data Hold from CLK Input                                         | All Devices    | 0.55     | -         | 0.55      | -        | 0.55       | _          | ns +<br>1/2 U    |

| $f_{DATA_GDDRX1_aligned}$                | GDDRX1 Data Rate                                                 | All Devices    | —        | 500       | —         | 500      | —          | 500        | Mb/s             |

| $f_{MAX\_GDDRX1\_aligned}$               | GDDRX1 CLK Frequency (SCLK)                                      | All Devices    | _        | 250       | —         | 250      | —          | 250        | MHz              |

| Generic DDRX2 Inp                        | uts With Clock and Data Centere                                  | d at Pin (GDDI | RX2_RX.E | CLK.Cen   | tered) Us | ing PCLK | Clock In   | put, Left  | and              |

| Right sides Only - F                     |                                                                  | T              |          |           | -         | 1        | 1          |            |                  |

| $t_{SU_GDDRX2\_centered}$                | Data Setup before CLK Input                                      | All Devices    | 0.321    | —         | 0.403     | _        | 0.471      | —          | ns               |

| $t_{HD_GDDRX2\_centered}$                | Data Hold after CLK Input                                        | All Devices    | 0.321    | —         | 0.403     | _        | 0.471      | —          | ns               |

| $f_{DATA\_GDDRX2\_centered}$             | GDDRX2 Data Rate                                                 | All Devices    | -        | 800       | —         | 700      | -          | 624        | Mb/s             |

| $f_{MAX\_GDDRX2\_centered}$              | GDDRX2 CLK Frequency (ECLK)                                      | All Devices    | -        | 400       | -         | 350      | -          | 312        | MHz              |

| Generic DDRX2 Inp<br>sides Only - Figure | uts With Clock and Data Aligned 3.7                              | at Pin (GDDR)  | (2_RX.EC | LK.Aligne | ed) Using | PCLK Cl  | ock Input  | t, Left an | d Right          |

| $t_{su\_GDDRX2\_aligned}$                | Data Setup from CLK Input                                        | All Devices    | -        | -0.344    | —         | -0.42    | -          | -0.495     | ns + 1/2<br>UI   |

| $t_{HD}_{GDDRX2}_{aligned}$              | Data Hold from CLK Input                                         | All Devices    | 0.344    | —         | 0.42      | _        | 0.495      | —          | ns + 1/2<br>UI   |

| $f_{DATA\_GDDRX2\_aligned}$              | GDDRX2 Data Rate                                                 | All Devices    | —        | 800       | —         | 700      | —          | 624        | Mb/s             |

| $f_{MAX\_GDDRX2\_aligned}$               | GDDRX2 CLK Frequency                                             | All Devices    | _        | 400       | —         | 350      | _          | 312        | MHz              |

| Video DDRX71 Inpu<br>Figure 3.11         | its With Clock and Data Aligned a                                | at Pin (GDDRX  | 71_RX.E0 | CLK) Usin | g PLL Clo | ck Input | , Left and | l Right si | des Only         |

| t <sub>su_lvds71_i</sub>                 | Data Setup from CLK Input<br>(bit i)                             | All Devices    | -        | -0.271    | -         | -0.39    | _          | -0.41      | ns+(1/2+<br>* UI |

| t <sub>HD_LVDS71_i</sub>                 | Data Hold from CLK Input<br>(bit i)                              | All Devices    | 0.271    | _         | 0.39      | -        | 0.41       | _          | ns+(1/2+<br>* UI |

| f <sub>DATA_LVDS71</sub>                 | DDR71 Data Rate                                                  | All Devices    | 1        | 756       | —         | 620      | -          | 525        | Mb/s             |

| f <sub>MAX_LVDS71</sub>                  | DDR71 CLK Frequency (ECLK)                                       | All Devices    |          | 378       | _         | 310      | _          | 262.5      | MHz              |

### Table 3.22. ECP5/ECP5-5G External Switching Characteristics (Continued)

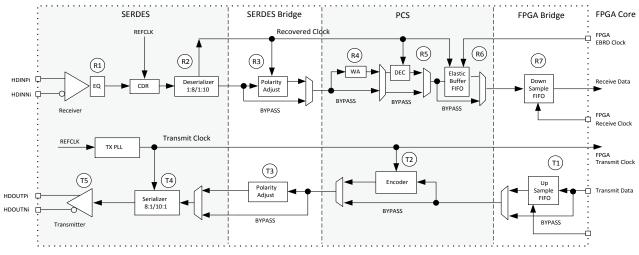

# 3.21. SERDES/PCS Block Latency

Table 3.26 describes the latency of each functional block in the transmitter and receiver. Latency is given in parallel clock cycles. Figure 3.13 shows the location of each block.

| • | Table 3.2 | 6. SERDES/PCS Latency Breakdown |

|---|-----------|---------------------------------|

|   |           |                                 |

| Item    | Description                                     | Min | Avg | Max | Fixed           | Bypass | Unit <sup>3</sup> |

|---------|-------------------------------------------------|-----|-----|-----|-----------------|--------|-------------------|

| Transm  | it Data Latency <sup>1</sup>                    |     |     |     |                 |        |                   |

| T1      | FPGA Bridge - Gearing disabled with same clocks | 3   | —   | 4   | _               | 1      | byte clk          |

| 11      | FPGA Bridge - Gearing enabled                   | 5   | —   | 7   | _               | —      | word clk          |

| Т2      | 8b10b Encoder                                   | _   | -   | -   | 2               | 1      | byte clk          |

| Т3      | SERDES Bridge transmit                          | —   | -   | -   | 2               | 1      | byte clk          |

| T4      | Serializer: 8-bit mode                          | -   | —   | -   | 15 + ∆1         | —      | UI + ps           |

| 14      | Serializer: 10-bit mode                         | _   | —   | -   | 18 + <b>Δ</b> 1 | —      | UI + ps           |

| T5      | Pre-emphasis ON                                 | —   | -   | -   | <b>1</b> + Δ2   | -      | UI + ps           |

| 15      | Pre-emphasis OFF                                | _   | _   | _   | 0 + Δ3          | _      | UI + ps           |

| Receive | Data Latency <sup>2</sup>                       |     |     |     |                 |        |                   |

| R1      | Equalization ON                                 | -   | —   | -   | Δ1              | —      | UI + ps           |

| KI      | Equalization OFF                                | —   | -   | -   | Δ2              | -      | UI + ps           |

| R2      | Deserializer: 8-bit mode                        | _   | —   | _   | 10 + ∆3         | —      | UI + ps           |

| κz      | Deserializer: 10-bit mode                       | -   | —   | -   | 12 + ∆3         | —      | UI + ps           |

| R3      | SERDES Bridge receive                           | —   | -   | -   | 2               | -      | byte clk          |

| R4      | Word alignment                                  | 3.1 | —   | 4   | —               | 1      | byte clk          |

| R5      | 8b10b decoder                                   | -   | —   | -   | 1               | 0      | byte clk          |

| R6      | Clock Tolerance Compensation                    | 7   | 15  | 23  | _               | 1      | byte clk          |

| 07      | FPGA Bridge - Gearing disabled with same clocks | 4   | _   | 5   | _               | 1      | byte clk          |

| R7      | FPGA Bridge - Gearing enabled                   | 7   | -   | 9   | -               | -      | word clk          |

Notes:

1.  $\Delta 1 = -245 \text{ ps}, \Delta 2 = +88 \text{ ps}, \Delta 3 = +112 \text{ ps}.$

2.  $\Delta 1 = +118 \text{ ps}, \Delta 2 = +132 \text{ ps}, \Delta 3 = +700 \text{ ps}.$

3. byte clk = 8UIs (8-bit mode), or 10 UIs (10-bit mode); word clk = 16UIs (8-bit mode), or 20 UIs (10-bit mode).

# 3.25.2. PCIe (5 Gb/s) – Preliminary AC and DC Characteristics

Over recommended operating conditions.

### Table 3.31. PCIe (5 Gb/s)

| Symbol                            | Description                                                 | Test Conditions              | Min    | Тур | Max    | Unit       |

|-----------------------------------|-------------------------------------------------------------|------------------------------|--------|-----|--------|------------|

| Transmit <sup>1</sup>             |                                                             |                              |        |     |        |            |

| UI                                | Unit Interval                                               | —                            | 199.94 | 200 | 200.06 | ps         |

| B <sub>WTX-PKG-PLL2</sub>         | Tx PLL bandwidth corresponding to<br>PKGTX-PLL2             | _                            | 5      | -   | 16     | MHz        |

| P <sub>KGTX-PLL2</sub>            | Tx PLL Peaking                                              | —                            | -      | —   | 1      | dB         |

| V <sub>TX-DIFF-PP</sub>           | Differential p-p Tx voltage swing                           | —                            | 0.8    | _   | 1.2    | V, p-p     |

| V <sub>TX-DIFF-PP-LOW</sub>       | Low power differential p-p Tx voltage swing                 | _                            | 0.4    | _   | 1.2    | V, p-p     |

| V <sub>TX-DE-RATIO-3.5dB</sub>    | Tx de-emphasis level ratio at 3.5dB                         | —                            | 3      | —   | 4      | dB         |

| V <sub>TX-DE-RATIO-6dB</sub>      | Tx de-emphasis level ratio at 6dB                           | —                            | 5.5    | —   | 6.5    | dB         |

| T <sub>MIN-PULSE</sub>            | Instantaneous lone pulse width                              | —                            |        | —   | _      | UI         |

| T <sub>TX-RISE-FALL</sub>         | Transmitter rise and fall time                              | _                            |        | —   | _      | UI         |

| T <sub>TX-EYE</sub>               | Transmitter Eye, including all jitter sources               | _                            | 0.75   | _   | _      | UI         |

| T <sub>TX-DJ</sub>                | Tx deterministic jitter > 1.5 MHz                           | _                            | _      | —   | 0.15   | UI         |

| T <sub>TX-RJ</sub>                | Tx RMS jitter < 1.5 MHz                                     | _                            | _      | _   | 3      | ps,<br>RMS |

| T <sub>RF-MISMATCH</sub>          | Tx rise/fall time mismatch                                  | —                            | _      | —   |        | UI         |

| D                                 | Tx Differential Return Loss, including                      | 50 MHz < freq <<br>1.25 GHz  | 10     | _   | _      | dB         |

| R <sub>LTX-DIFF</sub>             | package and silicon                                         | 1.25 GHz < freq<br>< 2.5 GHz | 8      | _   | _      | dB         |

| R <sub>LTX-CM</sub>               | Tx Common Mode Return Loss, including package and silicon   | 50 MHz < freq <<br>2.5 GHz   | 6      | _   | _      | dB         |

| Z <sub>TX-DIFF-DC</sub>           | DC differential Impedance                                   | _                            | -      | _   | 120    | Ω          |

| V <sub>TX-CM-AC-PP</sub>          | Tx AC peak common mode voltage, peak-peak                   | -                            | -      | -   |        | mV,<br>p-p |

| I <sub>TX-SHORT</sub>             | Transmitter short-circuit current                           | —                            | _      | —   | 90     | mA         |

| V <sub>TX-DC-CM</sub>             | Transmitter DC common-mode voltage                          | _                            | 0      | -   | 1.2    | V          |

| V <sub>TX-IDLE-DIFF-DC</sub>      | Electrical Idle Output DC voltage                           | —                            | 0      | —   | 5      | mV         |

| V <sub>TX-IDLE-DIFF-AC-p</sub>    | Electrical Idle Differential Output<br>peak voltage         | -                            | _      | -   |        | mV         |

| V <sub>TX-RCV-DETECT</sub>        | Voltage change allowed during<br>Receiver Detect            | _                            | _      | -   | 600    | mV         |

| T <sub>TX-IDLE-MIN</sub>          | Min. time in Electrical Idle                                | —                            | 20     | —   | _      | ns         |

| T <sub>TX-IDLE-SET-TO-IDLE</sub>  | Max. time from El Order Set to valid<br>Electrical Idle     | _                            | _      | _   | 8      | ns         |

| T <sub>TX-IDLE-TO-DIFF-DATA</sub> | Max. time from Electrical Idle to valid differential output | _                            | _      | _   | 8      | ns         |

| L <sub>TX-SKEW</sub>              | Lane-to-lane output skew                                    | _                            | _      | —   |        | ps         |

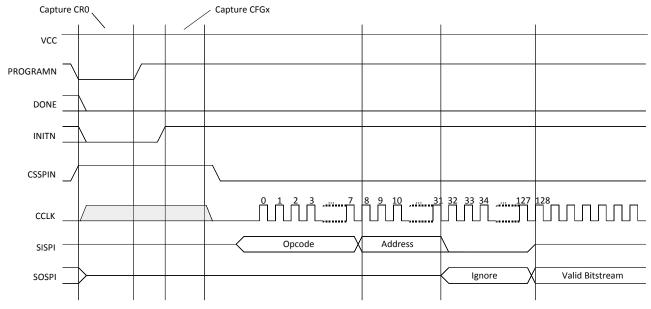

Figure 3.22. Master SPI Configuration Waveforms

# 3.32. JTAG Port Timing Specifications

Over recommended operating conditions.

#### Table 3.43. JTAG Port Timing Specifications

| Symbol                      | Parameter                                                          | Min | Max | Units |

|-----------------------------|--------------------------------------------------------------------|-----|-----|-------|

| f <sub>MAX</sub>            | TCK clock frequency                                                | -   | 25  | MHz   |

| t <sub>втсрн</sub>          | TCK [BSCAN] clock pulse width high                                 | 20  | —   | ns    |

| t <sub>btcpl</sub>          | TCK [BSCAN] clock pulse width low                                  | 20  | —   | ns    |

| t <sub>BTS</sub>            | TCK [BSCAN] setup time                                             | 10  | —   | ns    |

| t <sub>BTH</sub>            | TCK [BSCAN] hold time                                              | 8   | —   | ns    |

| t <sub>BTRF</sub>           | TCK [BSCAN] rise/fall time                                         | 50  | —   | mV/ns |

| t <sub>BTCO</sub>           | TAP controller falling edge of clock to valid output               | -   | 10  | ns    |

| t <sub>BTCODIS</sub>        | TAP controller falling edge of clock to valid disable              | —   | 10  | ns    |

| t <sub>btcoen</sub>         | TAP controller falling edge of clock to valid enable               | -   | 10  | ns    |

| t <sub>BTCRS</sub>          | BSCAN test capture register setup time                             | 8   | —   | ns    |

| t <sub>btcrh</sub>          | BSCAN test capture register hold time                              | 25  | —   | ns    |

| t <sub>BUTCO</sub>          | BSCAN test update register, falling edge of clock to valid output  | -   | 25  | ns    |

| t <sub>BTUODIS</sub>        | BSCAN test update register, falling edge of clock to valid disable | -   | 25  | ns    |

| <b>t</b> <sub>BTUPOEN</sub> | BSCAN test update register, falling edge of clock to valid enable  | -   | 25  | ns    |

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

# 4.2. PICs and DDR Data (DQ) Pins Associated with the DDR Strobe (DQS) Pin

| PICs Associated with DQS Strobe | PIO within PIC                        | DDR Strobe (DQS) and Data (DQ) Pins |

|---------------------------------|---------------------------------------|-------------------------------------|

| F                               | or Left and Right Edges of the Device | Only                                |

|                                 | А                                     | DQ                                  |

|                                 | В                                     | DQ                                  |

| P[L/R] [n-6]                    | С                                     | DQ                                  |

|                                 | D                                     | DQ                                  |

|                                 | А                                     | DQ                                  |

|                                 | В                                     | DQ                                  |

| P[L/R] [n-3]                    | С                                     | DQ                                  |

|                                 | D                                     | DQ                                  |

|                                 | А                                     | DQS (P)                             |

|                                 | В                                     | DQS (N)                             |

| P[L/R] [n]                      | С                                     | DQ                                  |

|                                 | D                                     | DQ                                  |

|                                 | А                                     | DQ                                  |

|                                 | В                                     | DQ                                  |

| P[L/R] [n+3]                    | С                                     | DQ                                  |

|                                 | D                                     | DQ                                  |

**Note**: "n" is a row PIC number.

# 4.3. **Pin Information Summary**

### 4.3.1. **LFE5UM/LFE5UM5G**

| Pin Information Summary     |        |              | 5UM/<br>M5G-25 | LFE5UN        | LFE5UM/LFE5UM5G-45 LFE5UM/LFE5UM5G-85 |              |               |             |              | -85          |

|-----------------------------|--------|--------------|----------------|---------------|---------------------------------------|--------------|---------------|-------------|--------------|--------------|

| Pin Type                    |        | 285<br>csfBG | 381<br>caBGA   | 285<br>csfBGA | 381<br>caBG                           | 554<br>caBGA | 285<br>csfBGA | 381<br>caBG | 554<br>caBGA | 756<br>caBGA |

|                             | Bank 0 | 6            | 24             | 6             | 27                                    | 32           | 6             | 27          | 32           | 56           |

|                             | Bank 1 | 6            | 32             | 6             | 33                                    | 40           | 6             | 33          | 40           | 48           |

|                             | Bank 2 | 21           | 32             | 21            | 32                                    | 32           | 21            | 34          | 32           | 48           |

| General Purpose             | Bank 3 | 28           | 32             | 28            | 33                                    | 48           | 28            | 33          | 48           | 64           |

| Inputs/Outputs per Bank     | Bank 4 | 0            | 0              | 0             | 0                                     | 0            | 0             | 0           | 14           | 24           |

|                             | Bank 6 | 26           | 32             | 26            | 33                                    | 48           | 26            | 33          | 48           | 64           |

|                             | Bank 7 | 18           | 32             | 18            | 32                                    | 32           | 18            | 32          | 32           | 48           |

|                             | Bank 8 | 13           | 13             | 13            | 13                                    | 13           | 13            | 13          | 13           | 13           |

| Total Single-Ended User I/O |        | 118          | 197            | 118           | 203                                   | 245          | 118           | 205         | 259          | 365          |

| VCC                         |        | 13           | 20             | 13            | 20                                    | 24           | 13            | 20          | 24           | 36           |

| VCCAUX (Core)               |        | 3            | 4              | 3             | 4                                     | 9            | 3             | 4           | 9            | 8            |

|                             | Bank O | 1            | 2              | 1             | 2                                     | 3            | 1             | 2           | 3            | 4            |

|                             | Bank 1 | 1            | 2              | 1             | 2                                     | 3            | 1             | 2           | 3            | 4            |

|                             | Bank 2 | 2            | 3              | 2             | 3                                     | 4            | 2             | 3           | 4            | 4            |

| VICEIO                      | Bank 3 | 2            | 3              | 2             | 3                                     | 3            | 2             | 3           | 3            | 4            |

| VCCIO                       | Bank 4 | 0            | 0              | 0             | 0                                     | 0            | 0             | 0           | 2            | 2            |

|                             | Bank 6 | 2            | 3              | 2             | 3                                     | 4            | 2             | 3           | 4            | 4            |

|                             | Bank 7 | 2            | 3              | 2             | 3                                     | 3            | 2             | 3           | 3            | 4            |

|                             | Bank 8 | 2            | 2              | 2             | 2                                     | 2            | 2             | 2           | 2            | 2            |

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## 4.3.2. LFE5U

| Pin Information<br>Summary             |         | L            | .FE5U-1       | 2            | L            | .FE5U-2       | 5            | LFE5U-45     |               |              |              | LFE5U-85     |              |              |             |

|----------------------------------------|---------|--------------|---------------|--------------|--------------|---------------|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|-------------|

| Pin Type                               |         | 256<br>caBGA | 285<br>csfBGA | 381<br>caBGA | 256<br>caBGA | 285<br>csfBGA | 381<br>caBGA | 256<br>caBGA | 285<br>csfBGA | 381<br>caBGA | 554<br>caBGA | 285<br>csfBG | 381<br>caBGA | 554<br>caBGA | 756<br>caBG |

|                                        | Bank 0  | 24           | 6             | 24           | 24           | 6             | 24           | 24           | 6             | 27           | 32           | 6            | 27           | 32           | 56          |

|                                        | Bank 1  | 32           | 6             | 32           | 32           | 6             | 32           | 32           | 6             | 33           | 40           | 6            | 33           | 40           | 48          |

| General                                | Bank 2  | 32           | 21            | 32           | 32           | 21            | 32           | 32           | 21            | 32           | 32           | 21           | 34           | 32           | 48          |

| Purpose                                | Bank 3  | 32           | 28            | 32           | 32           | 28            | 32           | 32           | 28            | 33           | 48           | 28           | 33           | 48           | 64          |

| Inputs/Outputs                         | Bank 4  | 0            | 0             | 0            | 0            | 0             | 0            | 0            | 0             | 0            | 0            | 0            | 0            | 14           | 24          |

| per Bank                               | Bank 6  | 32           | 26            | 32           | 32           | 26            | 32           | 32           | 26            | 33           | 48           | 26           | 33           | 48           | 64          |

|                                        | Bank 7  | 32           | 18            | 32           | 32           | 18            | 32           | 32           | 18            | 32           | 32           | 18           | 32           | 32           | 48          |

|                                        | Bank 8  | 13           | 13            | 13           | 13           | 13            | 13           | 13           | 13            | 13           | 13           | 13           | 13           | 13           | 13          |

| Total Single-Ende                      | d User  | 197          | 118           | 197          | 197          | 118           | 197          | 197          | 118           | 203          | 245          | 118          | 205          | 259          | 365         |

| VCC                                    |         | 6            | 13            | 20           | 6            | 13            | 20           | 6            | 13            | 20           | 24           | 13           | 20           | 24           | 36          |

| VCCAUX (Core)                          |         | 2            | 3             | 4            | 2            | 3             | 4            | 2            | 3             | 4            | 9            | 3            | 4            | 9            | 8           |

|                                        | Bank 0  | 2            | 1             | 2            | 2            | 1             | 2            | 2            | 1             | 2            | 3            | 1            | 2            | 3            | 4           |

|                                        | Bank 1  | 2            | 1             | 2            | 2            | 1             | 2            | 2            | 1             | 2            | 3            | 1            | 2            | 3            | 4           |

|                                        | Bank 2  | 2            | 2             | 3            | 2            | 2             | 3            | 2            | 2             | 3            | 4            | 2            | 3            | 4            | 4           |

| VCCIO                                  | Bank 3  | 2            | 2             | 3            | 2            | 2             | 3            | 2            | 2             | 3            | 3            | 2            | 3            | 3            | 4           |

| Veelo                                  | Bank 4  | 0            | 0             | 0            | 0            | 0             | 0            | 0            | 0             | 0            | 0            | 0            | 0            | 2            | 2           |

|                                        | Bank 6  | 2            | 2             | 3            | 2            | 2             | 3            | 2            | 2             | 3            | 4            | 2            | 3            | 4            | 4           |

|                                        | Bank 7  | 2            | 2             | 3            | 2            | 2             | 3            | 2            | 2             | 3            | 3            | 2            | 3            | 3            | 4           |

|                                        | Bank 8  | 1            | 2             | 2            | 1            | 2             | 2            | 1            | 2             | 2            | 2            | 2            | 2            | 2            | 2           |

| ТАР                                    |         | 4            | 4             | 4            | 4            | 4             | 4            | 4            | 4             | 4            | 4            | 4            | 4            | 4            | 4           |

| Miscellaneous De                       | dicated | 7            | 7             | 7            | 7            | 7             | 7            | 7            | 7             | 7            | 7            | 7            | 7            | 7            | 7           |

| GND                                    |         | 27           | 123           | 99           | 27           | 123           | 99           | 27           | 123           | 99           | 198          | 123          | 99           | 198          | 267         |

| NC                                     |         | 0            | 1             | 26           | 0            | 1             | 26           | 0            | 1             | 26           | 33           | 1            | 26           | 33           | 29          |

| Reserved                               |         | 0            | 4             | 6            | 0            | 4             | 6            | 0            | 4             | 6            | 12           | 4            | 6            | 12           | 12          |

| Total Balls                            |         | 256          | 285           | 381          | 256          | 285           | 381          | 256          | 285           | 381          | 554          | 285          | 381          | 554          | 756         |

|                                        |         | Bank         | 0             | 0            | 0            | 0             | 0            | 0            | 0             | 0            | 0            | 0            | 0            | 0            | 0           |

|                                        |         | Bank         | 0             | 0            | 0            | 0             | 0            | 0            | 0             | 0            | 0            | 0            | 0            | 0            | 0           |

|                                        |         | Bank         | 16/8          | 10/8         | 16/8         | 16/8          | 10/8         | 16/8         | 16/8          | 10/8         | 16/8         | 16/8         | 10/8         | 17/9         | 16/8        |

| High Speed Differ<br>Input / Output Pa |         | Bank<br>Bank | 16/8<br>0     | 14/7<br>0    | 16/8<br>0    | 16/8<br>0     | 14/7<br>0    | 16/8<br>0    | 16/8<br>0     | 14/7<br>0    | 16/8<br>0    | 24/12<br>0   | 14/7<br>0    | 16/8<br>0    | 24/1<br>0   |

|                                        | 111 3   | Bank         |               |              | -            | -             | -            | -            | -             | -            | -            | 24/12        | -            |              |             |

|                                        |         | Bank         | 16/8<br>16/8  | 13/6<br>8/6  | 16/8<br>16/8 | 16/8<br>16/8  | 13/6<br>8/6  | 16/8<br>16/8 | 16/8<br>16/8  | 13/6<br>8/6  | 16/8<br>16/8 | 16/8         | 13/6<br>8/6  | 16/8<br>16/8 | 24/1        |

|                                        |         | Bank         | 0             | 0            | 0            | 0             | 0            | 0            | 0             | 0            | 10/8         | 0            | 0            | 0            | 16/8<br>0   |

| Total High Speed                       |         | 64/32        | 45/27         | 64/32        | 64/32        | -             | 64/32        | 64/32        | -             | 64/32        | 80/40        | 45/27        | 65/33        | 80/40        | 112/        |

| Total High Speed                       |         | Bank         | 43/27         | 04/32        | 04/32        | 43/27         | 04/32        | 04/32        | 43/27         | 04/32        | 0            | 43/27        | 03/33        | 0            | 0           |

|                                        |         | Bank         | 0             | 0            | 0            | 0             | 0            | 0            | 0             | 0            | 0            | 0            | 0            | 0            | 0           |

|                                        |         | Bank         | 2             | 1            | 2            | 2             | 1            | 2            | 2             | 1            | 2            | 2            | 1            | 2            | 2           |

|                                        |         | Bank         | 2             | 2            | 2            | 2             | 2            | 2            | 2             | 2            | 2            | 3            | 2            | 2            | 3           |

| DQS Groups<br>(> 11 pins in grou       | (a      | Bank         | 0             | 0            | 0            | 0             | 0            | 0            | 0             | 0            | 0            | 0            | 0            | 0            | 0           |

| , <u>1</u>                             | . /     | Bank         | 2             | 2            | 2            | 2             | 2            | 2            | 2             | 2            | 2            | 3            | 2            | 2            | 3           |

|                                        |         | Bank         | 2             | 1            | 2            | 2             | 1            | 2            | 2             | 1            | 2            | 2            | 1            | 2            | 2           |

|                                        |         | Bank         | 0             | 0            | 0            | 0             | 0            | 0            | 0             | 0            | 0            | 0            | 0            | 0            | 0           |

| Total DQS Groups                       | 5       | 8            | 6             | 8            | 8            | 6             | 8            | 8            | 6             | 8            | 10           | 6            | 8            | 10           | 14          |

| Part number          | Grade | Package          | Pins | Temp.      | LUTs (K) | SERDES |

|----------------------|-------|------------------|------|------------|----------|--------|

| LFE5U-85F-6BG756I    | -6    | Lead free caBGA  | 756  | Industrial | 84       | No     |

| LFE5U-85F-7BG756I    | -7    | Lead free caBGA  | 756  | Industrial | 84       | No     |

| LFE5U-85F-8BG756I    | -8    | Lead free caBGA  | 756  | Industrial | 84       | No     |

| LFE5UM-25F-6MG285I   | -6    | Lead free csfBGA | 285  | Industrial | 24       | Yes    |

| LFE5UM-25F-7MG285I   | -7    | Lead free csfBGA | 285  | Industrial | 24       | Yes    |

| LFE5UM-25F-8MG285I   | -8    | Lead free csfBGA | 285  | Industrial | 24       | Yes    |

| LFE5UM-25F-6BG381I   | -6    | Lead free caBGA  | 381  | Industrial | 24       | Yes    |

| LFE5UM-25F-7BG381I   | -7    | Lead free caBGA  | 381  | Industrial | 24       | Yes    |

| LFE5UM-25F-8BG381I   | -8    | Lead free caBGA  | 381  | Industrial | 24       | Yes    |

| LFE5UM-45F-6MG285I   | -6    | Lead free csfBGA | 285  | Industrial | 44       | Yes    |

| LFE5UM-45F-7MG285I   | -7    | Lead free csfBGA | 285  | Industrial | 44       | Yes    |

| LFE5UM-45F-8MG285I   | -8    | Lead free csfBGA | 285  | Industrial | 44       | Yes    |

| LFE5UM-45F-6BG381I   | -6    | Lead free caBGA  | 381  | Industrial | 44       | Yes    |

| LFE5UM-45F-7BG381I   | -7    | Lead free caBGA  | 381  | Industrial | 44       | Yes    |

| LFE5UM-45F-8BG381I   | -8    | Lead free caBGA  | 381  | Industrial | 44       | Yes    |

| LFE5UM-45F-6BG554I   | -6    | Lead free caBGA  | 554  | Industrial | 44       | Yes    |

| LFE5UM-45F-7BG554I   | -7    | Lead free caBGA  | 554  | Industrial | 44       | Yes    |

| LFE5UM-45F-8BG554I   | -8    | Lead free caBGA  | 554  | Industrial | 44       | Yes    |

| LFE5UM-85F-6MG285I   | -6    | Lead free csfBGA | 285  | Industrial | 84       | Yes    |

| LFE5UM-85F-7MG285I   | -7    | Lead free csfBGA | 285  | Industrial | 84       | Yes    |

| LFE5UM-85F-8MG285I   | -8    | Lead free csfBGA | 285  | Industrial | 84       | Yes    |

| LFE5UM-85F-6BG381I   | -6    | Lead free caBGA  | 381  | Industrial | 84       | Yes    |

| LFE5UM-85F-7BG381I   | -7    | Lead free caBGA  | 381  | Industrial | 84       | Yes    |

| LFE5UM-85F-8BG381I   | -8    | Lead free caBGA  | 381  | Industrial | 84       | Yes    |

| LFE5UM-85F-6BG554I   | -6    | Lead free caBGA  | 554  | Industrial | 84       | Yes    |

| LFE5UM-85F-7BG554I   | -7    | Lead free caBGA  | 554  | Industrial | 84       | Yes    |

| LFE5UM-85F-8BG554I   | -8    | Lead free caBGA  | 554  | Industrial | 84       | Yes    |

| LFE5UM-85F-6BG756I   | -6    | Lead free caBGA  | 756  | Industrial | 84       | Yes    |

| LFE5UM-85F-7BG756I   | -7    | Lead free caBGA  | 756  | Industrial | 84       | Yes    |

| LFE5UM-85F-8BG756I   | -8    | Lead free caBGA  | 756  | Industrial | 84       | Yes    |

| LFE5UM5G-25F-8MG285I | -8    | Lead free csfBGA | 285  | Industrial | 24       | Yes    |

| LFE5UM5G-25F-8BG381I | -8    | Lead free caBGA  | 381  | Industrial | 24       | Yes    |

| LFE5UM5G-45F-8MG285I | -8    | Lead free csfBGA | 285  | Industrial | 44       | Yes    |

| LFE5UM5G-45F-8BG381I | -8    | Lead free caBGA  | 381  | Industrial | 44       | Yes    |

| LFE5UM5G-45F-8BG554I | -8    | Lead free caBGA  | 554  | Industrial | 44       | Yes    |

| LFE5UM5G-85F-8MG285I | -8    | Lead free csfBGA | 285  | Industrial | 84       | Yes    |

| LFE5UM5G-85F-8BG381I | -8    | Lead free caBGA  | 381  | Industrial | 84       | Yes    |

| LFE5UM5G-85F-8BG554I | -8    | Lead free caBGA  | 554  | Industrial | 84       | Yes    |

| LFE5UM5G-85F-8BG756I | -8    | Lead free caBGA  | 756  | Industrial | 84       | Yes    |