# E: Lattice Semiconductor Corporation - LFE5UM-85F-6BG554I Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                        |

|--------------------------------|-------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 21000                                                                         |

| Number of Logic Elements/Cells | 84000                                                                         |

| Total RAM Bits                 | 3833856                                                                       |

| Number of I/O                  | 259                                                                           |

| Number of Gates                | -                                                                             |

| Voltage - Supply               | 1.045V ~ 1.155V                                                               |

| Mounting Type                  | Surface Mount                                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                            |

| Package / Case                 | 554-FBGA                                                                      |

| Supplier Device Package        | 554-CABGA (23x23)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe5um-85f-6bg554i |

|                                |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| Acronyms in This Document                                   |    |

|-------------------------------------------------------------|----|

| 1. General Description                                      | 10 |

| 1.1. Features                                               | 10 |

| 2. Architecture                                             | 12 |

| 2.1. Overview                                               | 12 |

| 2.2. PFU Blocks                                             | 13 |

| 2.2.1. Slice                                                | 14 |

| 2.2.2. Modes of Operation                                   | 17 |

| 2.3. Routing                                                |    |

| 2.4. Clocking Structure                                     |    |

| 2.4.1. sysCLOCK PLL                                         |    |

| 2.5. Clock Distribution Network                             | 19 |

| 2.5.1. Primary Clocks                                       | 20 |

| 2.5.2. Edge Clock                                           | 21 |

| 2.6. Clock Dividers                                         |    |

| 2.7. DDRDLL                                                 |    |

| 2.8. sysMEM Memory                                          |    |

| 2.8.1. sysMEM Memory Block                                  |    |

| 2.8.2. Bus Size Matching                                    |    |

| 2.8.3. RAM Initialization and ROM Operation                 |    |

| 2.8.4. Memory Cascading                                     |    |

| 2.8.5. Single, Dual and Pseudo-Dual Port Modes              |    |

| 2.8.6. Memory Core Reset                                    |    |

| 2.9. sysDSP <sup>™</sup> Slice                              |    |

| 2.9.1. sysDSP Slice Approach Compared to General DSP        |    |

| 2.9.2. sysDSP Slice Architecture Features                   |    |

| 2.10. Programmable I/O Cells                                |    |

| 2.11. PIO                                                   |    |

| 2.11. Input Register Block                                  |    |

| 2.11.2. Output Register Block                               |    |

| 2.12. Tristate Register Block                               |    |

| 2.12. DDR Memory Support                                    |    |

| 2.13. DQS Grouping for DDR Memory                           |    |

| 2.13.2. DLL Calibrated DQS Delay and Control Block (DQSBUF) |    |

| 2.14. sysl/O Buffer                                         |    |

| 2.14. sysi/O Buffer Banks                                   |    |

| 2.14.1. Syst/O Burlet Balliss                               |    |

| 2.14.2. Typical syst/O f/O Benavior during Power-up         |    |

| 2.14.3. Supported syst/O Standards                          |    |

| 2.14.4. On-Chip Programmable Termination                    |    |

| 2.14.5. For socketing                                       |    |

| 2.15. SERDES and Physical County Sublayer                   |    |

|                                                             |    |

|                                                             |    |

| 2.15.3. SERDES Client Interface Bus                         |    |

| 2.16. Flexible Dual SERDES Architecture                     |    |

| 2.17. IEEE 1149.1-Compliant Boundary Scan Testability       |    |

| 2.18. Device Configuration                                  |    |

| 2.18.1. Enhanced Configuration Options                      |    |

| 2.18.2. Single Event Upset (SEU) Support                    |    |

| 2.18.3. On-Chip Oscillator                                  |    |

| 2.19. Density Shifting                                      |    |

| 3. DC and Switching Characteristics                         | 47 |

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Table 3.36. Receive and Jitter Tolerance                                |    |

|-------------------------------------------------------------------------|----|

| Table 3.37. Transmit                                                    |    |

| Table 3.38. Receive and Jitter Tolerance                                |    |

| Table 3.39. Transmit                                                    | 82 |

| Table 3.40. Receive                                                     | 82 |

| Table 3.41. Reference Clock                                             | 82 |

| Table 3.42. ECP5/ECP5-5G sysCONFIG Port Timing Specifications           | 83 |

| Table 3.43. JTAG Port Timing Specifications                             |    |

| Table 3.44. Test Fixture Required Components, Non-Terminated Interfaces |    |

|                                                                         |    |

# 2. Architecture

# 2.1. Overview

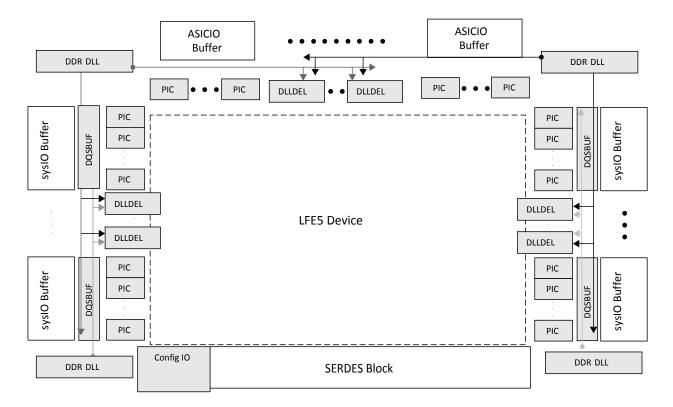

Each ECP5/ECP5-5G device contains an array of logic blocks surrounded by Programmable I/O Cells (PIC). Interspersed between the rows of logic blocks are rows of sysMEM<sup>™</sup> Embedded Block RAM (EBR) and rows of sysDSP<sup>™</sup> Digital Signal Processing slices, as shown in Figure 2.1 on page 13. The LFE5-85 devices have three rows of DSP slices, the LFE5-45 devices have two rows, and both LFE5-25 and LFE5-12 devices have one. In addition, the LFE5UM/LFE5UM5G devices contain SERDES Duals on the bottom of the device.

The Programmable Functional Unit (PFU) contains the building blocks for logic, arithmetic, RAM and ROM functions. The PFU block is optimized for flexibility, allowing complex designs to be implemented quickly and efficiently. Logic Blocks are arranged in a two-dimensional array.

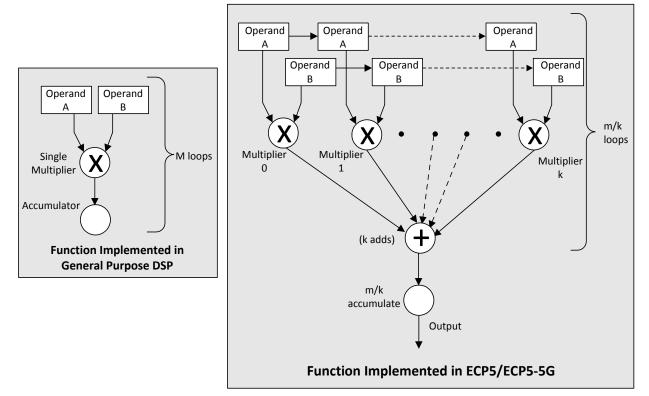

The ECP5/ECP5-5G devices contain one or more rows of sysMEM EBR blocks. sysMEM EBRs are large, dedicated 18 Kb fast memory blocks. Each sysMEM block can be configured in a variety of depths and widths as RAM or ROM. In addition, ECP5/ECP5-5G devices contain up to three rows of DSP slices. Each DSP slice has multipliers and adder/accumulators, which are the building blocks for complex signal processing capabilities.

The ECP5 devices feature up to four embedded 3.2 Gb/s SERDES channels, and the ECP5-5G devices feature up to four embedded 5 Gb/s SERDES channels. Each SERDES channel contains independent 8b/10b encoding / decoding, polarity adjust and elastic buffer logic. Each group of two SERDES channels, along with its Physical Coding Sublayer (PCS) block, creates a dual DCU (Dual Channel Unit). The functionality of the SERDES/PCS duals can be controlled by SRAM cell settings during device configuration or by registers that are addressable during device operation. The registers in every dual can be programmed via the SERDES Client Interface (SCI). These DCUs (up to two) are located at the bottom of the devices.

Each PIC block encompasses two PIOs (PIO pairs) with their respective sysI/O buffers. The sysI/O buffers of the ECP5/ECP5-5G devices are arranged in seven banks (eight banks for LFE5-85 devices in caBGA756 and caBGA554 packages), allowing the implementation of a wide variety of I/O standards. One of these banks (Bank 8) is shared with the programming interfaces. Half of the PIO pairs on the left and right edges of the device can be configured as LVDS transmit pairs, and all pairs on left and right can be configured as LVDS receive pairs. The PIC logic in the left and right banks also includes pre-engineered support to aid in the implementation of high speed source synchronous standards such as XGMII, 7:1 LVDS, along with memory interfaces including DDR3 and LPDDR3.

The ECP5/ECP5-5G registers in PFU and sysl/O can be configured to be SET or RESET. After power up and the device is configured, it enters into user mode with these registers SET/RESET according to the configuration setting, allowing the device entering to a known state for predictable system function.

Other blocks provided include PLLs, DLLs and configuration functions. The ECP5/ECP5-5G architecture provides up to four Delay-Locked Loops (DLLs) and up to four Phase-Locked Loops (PLLs). The PLL and DLL blocks are located at the corners of each device.

The configuration block that supports features such as configuration bit-stream decryption, transparent updates and dual-boot support is located at the bottom of each device, to the left of the SERDES blocks. Every device in the ECP5/ECP5-5G family supports a sysCONFIG<sup>™</sup> ports located in that same corner, powered by Vccio8, allowing for serial or parallel device configuration.

In addition, every device in the family has a JTAG port. This family also provides an on-chip oscillator and soft error detect capability. The ECP5 devices use 1.1 V and ECP5UM5G devices use 1.2 V as their core voltage.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

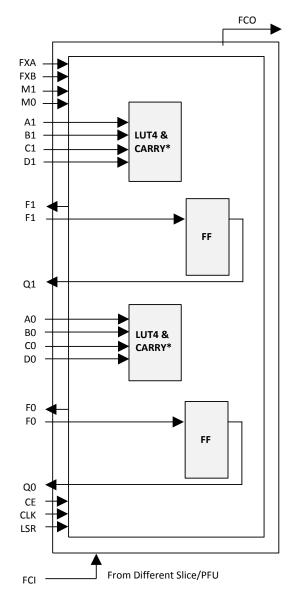

Notes: For Slices 0 and 1, memory control signals are generated from Slice 2 as follows: WCK is CLK

WRE is from LSR

DI[3:2] for Slice 1 and DI[1:0] for Slice 0 data from Slice 2 WAD [A:D] is a 4-bit address from slice 2 LUT input

Figure 2.3. Slice Diagram

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Figure 2.11. ECP5/ECP5-5G DLL Top Level View (For LFE-45 and LFE-85)

# 2.8. sysMEM Memory

ECP5/ECP5-5G devices contain a number of sysMEM Embedded Block RAM (EBR). The EBR consists of an 18 Kb RAM with memory core, dedicated input registers and output registers with separate clock and clock enable. Each EBR includes functionality to support true dual-port, pseudo dual-port, single-port RAM, ROM and FIFO buffers (via external PFUs).

### 2.8.1. sysMEM Memory Block

The sysMEM block can implement single port, dual port or pseudo dual port memories. Each block can be used in a variety of depths and widths as listed in Table 2.6 on page 25. FIFOs can be implemented in sysMEM EBR blocks by implementing support logic with PFUs. The EBR block facilitates parity checking by supporting an optional parity bit for each data byte. EBR blocks provide byte-enable support for configurations with 18-bit and 36-bit data widths. For more information, refer to ECP5 and ECP5-5G Memory Usage Guide (TN1264).

Figure 2.13. Comparison of General DSP and ECP5/ECP5-5G Approaches

### 2.9.2. sysDSP Slice Architecture Features

The ECP5/ECP5-5G sysDSP Slice has been significantly enhanced to provide functions needed for advanced processing applications. These enhancements provide improved flexibility and resource utilization.

The ECP5/ECP5-5G sysDSP Slice supports many functions that include the following:

- Symmetry support. The primary target application is wireless. 1D Symmetry is useful for many applications that use FIR filters when their coefficients have symmetry or asymmetry characteristics. The main motivation for using 1D symmetry is cost/size optimization. The expected size reduction is up to 2x.

- Odd mode Filter with Odd number of taps

- Even mode Filter with Even number of taps

- Two dimensional (2D) symmetry mode supports 2D filters for mainly video applications

- Dual-multiplier architecture. Lower accumulator overhead to half and the latency to half compared to single multiplier architecture

- Fully cascadable DSP across slices. Support for symmetric, asymmetric and non-symmetric filters.

- Multiply (one 18x36, two 18x18 or four 9x9 Multiplies per Slice)

- Multiply (36x36 by cascading across two sysDSP slices)

- Multiply Accumulate (supports one 18x36 multiplier result accumulation or two 18x18 multiplier result accumulation)

- Two Multiplies feeding one Accumulate per cycle for increased processing with lower latency (two 18x18 Multiplies feed into an accumulator that can accumulate up to 52 bits)

- Pipeline registers

- 1D Symmetry support. The coefficients of FIR filters have symmetry or negative symmetry characteristics.

- Odd mode Filter with Odd number of taps

- Even mode Filter with Even number of taps

- 2D Symmetry support. The coefficients of 2D FIR filters have symmetry or negative symmetry characteristics.

- 3\*3 and 3\*5 Internal DSP Slice support

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

### 2.11.1.1. Input FIFO

The ECP5/ECP5-5G PIO has dedicated input FIFO per single-ended pin for input data register for DDR Memory interfaces. The FIFO resides before the gearing logic. It transfers data from DQS domain to continuous ECLK domain. On the Write side of the FIFO, it is clocked by DQS clock which is the delayed version of the DQS Strobe signal from DDR memory. On the Read side of FIFO, it is clocked by ECLK. ECLK may be any high speed clock with identical frequency as DQS (the frequency of the memory chip). Each DQS group has one FIFO control block. It distributes FIFO read/write pointer to every PIC in same DQS group. DQS Grouping and DQS Control Block is described in DDR Memory Support section on page 35.

| Name                 | Туре   | Description                                                |

|----------------------|--------|------------------------------------------------------------|

| D                    | Input  | High Speed Data Input                                      |

| Q[1:0]/Q[3:0]/Q[6:0] | Output | Low Speed Data to the device core                          |

| RST                  | Input  | Reset to the Output Block                                  |

| SCLK                 | Input  | Slow Speed System Clock                                    |

| ECLK                 | Input  | High Speed Edge Clock                                      |

| DQS                  | Input  | Clock from DQS control Block used to clock DDR memory data |

| ALIGNWD              | Input  | Data Alignment signal from device core.                    |

### Table 2.8. Input Block Port Description

### 2.11.2. Output Register Block

The output register block registers signal from the core of the device before they are passed to the sysIO buffers.

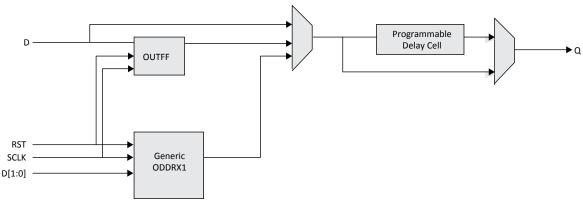

ECP5/ECP5-5G output data path has output programmable flip flops and output gearing logic. On the left and right sides, the output register block can support 1x, 2x and 7:1 gearing enabling high speed DDR interfaces and DDR memory interfaces. On the top side, the banks support 1x gearing. ECP5/ECP5-5G output data path diagram is shown in Figure 2.19. The programmable delay cells are also available in the output data path.

For detailed description of the output register block modes and usage, refer to ECP5 and ECP5-5G High-Speed I/O Interface (TN1265).

Figure 2.19. Output Register Block on Top Side

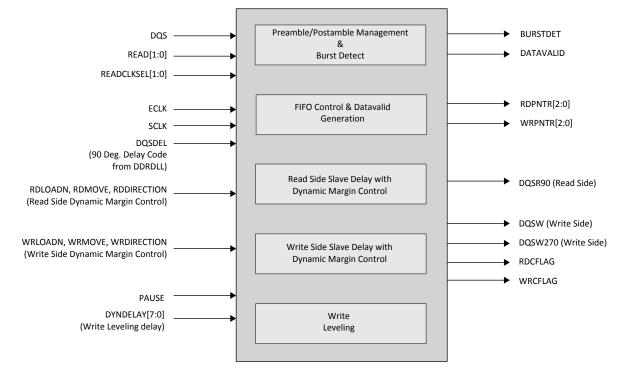

Figure 2.24. DQS Control and Delay Block (DQSBUF)

| Table 2.11 | DQSBUF | <b>Port List</b> | Description |

|------------|--------|------------------|-------------|

|------------|--------|------------------|-------------|

| Name                         | Туре   | Description                                                                                    |

|------------------------------|--------|------------------------------------------------------------------------------------------------|

| DQS                          | Input  | DDR memory DQS strobe                                                                          |

| READ[1:0]                    | Input  | Read Input from DDR Controller                                                                 |

| READCLKSEL[1:0]              | Input  | Read pulse selection                                                                           |

| SCLK                         | Input  | Slow System Clock                                                                              |

| ECLK                         | Input  | High Speed Edge Clock (same frequency as DDR memory)                                           |

| DQSDEL                       | Input  | 90° Delay Code from DDRDLL                                                                     |

| RDLOADN, RDMOVE, RDDIRECTION | Input  | Dynamic Margin Control ports for Read delay                                                    |

| WRLOADN, WRMOVE, WRDIRECTION | Input  | Dynamic Margin Control ports for Write delay                                                   |

| PAUSE                        | Input  | Used by DDR Controller to Pause write side signals during DDRDLL Code update or Write Leveling |

| DYNDELAY[7:0]                | Input  | Dynamic Write Leveling Delay Control                                                           |

| DQSR90                       | Output | 90° delay DQS used for Read                                                                    |

| DQSW270                      | Output | 90° delay clock used for DQ Write                                                              |

| DQSW                         | Output | Clock used for DQS Write                                                                       |

| RDPNTR[2:0]                  | Output | Read Pointer for IFIFO module                                                                  |

| WRPNTR[2:0]                  | Output | Write Pointer for IFIFO module                                                                 |

| DATAVALID                    | Output | Signal indicating start of valid data                                                          |

| BURSTDET                     | Output | Burst Detect indicator                                                                         |

| RDFLAG                       | Output | Read Dynamic Margin Control output to indicate max value                                       |

| WRFLAG                       | Output | Write Dynamic Margin Control output to indicate max value                                      |

<sup>© 2014-2018</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# 3.11. SERDES Power Supply Requirements<sup>1,2,3</sup>

Over recommended operating conditions.

#### Table 3.9. ECP5UM

| Symbol                             | Description                                              | Тур | Max | Unit |

|------------------------------------|----------------------------------------------------------|-----|-----|------|

| Standby (Pow                       | ver Down)                                                |     |     | '    |

| I <sub>CCA-SB</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 4   | 9.5 | mA   |

| I <sub>CCHRX-SB</sub> <sup>4</sup> | V <sub>CCHRX</sub> , Input Buffer Current (Per Channel)  | —   | 0.1 | mA   |

| I <sub>CCHTX-SB</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | _   | 0.9 | mA   |

| Operating (Da                      | ata Rate = 3.125 Gb/s)                                   |     |     |      |

| I <sub>CCA-OP</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 43  | 54  | mA   |

| I <sub>CCHRX-OP</sub> <sup>5</sup> | V <sub>CCHRX</sub> , Input Buffer Current (Per Channel)  | 0.4 | 0.5 | mA   |

| I <sub>CCHTX-OP</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | 10  | 13  | mA   |

| Operating (Da                      | ata Rate = 2.5 Gb/s)                                     |     |     |      |

| I <sub>CCA-OP</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 40  | 50  | mA   |

| I <sub>CCHRX-OP</sub> 5            | V <sub>CCHRX</sub> , Input Buffer Current (Per Channel)  | 0.4 | 0.5 | mA   |

| I <sub>CCHTX-OP</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | 10  | 13  | mA   |

| Operating (Da                      | ata Rate = 1.25 Gb/s)                                    |     |     |      |

| I <sub>CCA-OP</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 34  | 43  | mA   |

| I <sub>CCHRX-OP</sub> <sup>5</sup> | V <sub>CCHRX</sub> , Input Buffer Current (Per Channel)  | 0.4 | 0.5 | mA   |

| I <sub>CCHTX-OP</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | 10  | 13  | mA   |

| Operating (Da                      | ata Rate = 270 Mb/s)                                     |     |     |      |

| I <sub>CCA-OP</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 28  | 38  | mA   |

| I <sub>CCHRX-OP</sub> <sup>5</sup> | V <sub>CCHRX</sub> , Input Buffer Current (Per Channel)  | 0.4 | 0.5 | mA   |

| I <sub>CCHTX-OP</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | 8   | 10  | mA   |

Notes:

1. Rx Equalization enabled, Tx De-emphasis (pre-cursor and post-cursor) disabled

2. Per Channel current is calculated with both channels on in a Dual, and divide current by two. If only one channel is on, current will be higher.

3. To calculate with Tx De-emphasis enabled, use the Diamond Power Calculator tool.

4. For ICCHRX-SB, during Standby, input termination on Rx are disabled.

5. For ICCHRX-OP, during operational, the max specified when external AC coupling is used. If externally DC coupled, the power is based on current pulled down by external driver when the input is driven to LOW.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-DS-02012-1.9

#### Table 3.10. ECP5-5G

| Symbol                             | Description                                              | Тур | Max | Unit |

|------------------------------------|----------------------------------------------------------|-----|-----|------|

| Standby (Pov                       | ver Down)                                                | I   | •   |      |

| I <sub>CCA-SB</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 4   | 9.5 | mA   |

| I <sub>CCHRX-SB</sub> <sup>4</sup> | V <sub>CCHRX</sub> , Input Buffer Current (Per Channel)  | _   | 0.1 | mA   |

| I <sub>CCHTX-SB</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | _   | 0.9 | mA   |

| Operating (Da                      | ata Rate = 5 Gb/s)                                       |     |     |      |

| I <sub>CCA-OP</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 58  | 67  | mA   |

| I <sub>CCHRX-OP</sub> <sup>5</sup> | V <sub>CCHRX</sub> , Input Buffer Current (Per Channel)  | 0.4 | 0.5 | mA   |

| I <sub>CCHTX-OP</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | 10  | 13  | mA   |

| Operating (Da                      | ata Rate = 3.2 Gb/s)                                     |     |     |      |

| I <sub>CCA-OP</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 48  | 57  | mA   |

| I <sub>CCHRX-OP</sub> <sup>5</sup> | V <sub>CCHRX</sub> , Input Buffer Current (Per Channel)  | 0.4 | 0.5 | mA   |

| I <sub>CCHTX-OP</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | 10  | 13  | mA   |

| Operating (Da                      | ata Rate = 2.5 Gb/s)                                     |     |     |      |

| I <sub>CCA-OP</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 44  | 53  | mA   |

| I <sub>CCHRX-OP</sub> <sup>5</sup> | V <sub>CCHRx</sub> , Input Buffer Current (Per Channel)  | 0.4 | 0.5 | mA   |

| I <sub>CCHTX-OP</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | 10  | 13  | mA   |

| Operating (Da                      | ata Rate = 1.25 Gb/s)                                    |     |     |      |

| I <sub>CCA-OP</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 36  | 46  | mA   |

| I <sub>CCHRX-OP</sub> <sup>5</sup> | V <sub>CCHRX</sub> , Input Buffer Current (Per Channel)  | 0.4 | 0.5 | mA   |

| I <sub>CCHTX-OP</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | 10  | 13  | mA   |

| Operating (D                       | ata Rate = 270 Mb/s)                                     |     |     |      |

| I <sub>CCA-OP</sub>                | V <sub>CCA</sub> Power Supply Current (Per Channel)      | 30  | 40  | mA   |

| I <sub>CCHRX-OP</sub> <sup>5</sup> | V <sub>CCHRX</sub> , Input Buffer Current (Per Channel)  | 0.4 | 0.5 | mA   |

| I <sub>CCHTX-OP</sub>              | V <sub>CCHTX</sub> , Output Buffer Current (Per Channel) | 8   | 10  | mA   |

Notes:

1. Rx Equalization enabled, Tx De-emphasis (pre-cursor and post-cursor) disabled

2. Per Channel current is calculated with both channels on in a Dual, and divide current by two. If only one channel is on, current will be higher.

3. To calculate with Tx De-emphasis enabled, use the Diamond Power Calculator tool.

4. For ICCHRX-SB, during Standby, input termination on Rx are disabled.

5. For ICCHRX-OP, during operational, the max specified when external AC coupling is used. If externally DC coupled, the power is based on current pulled down by external driver when the input is driven to LOW.

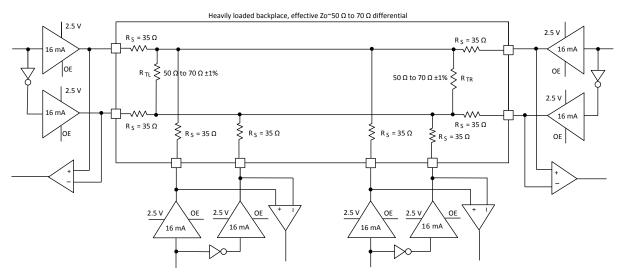

## 3.14.7. MLVDS25

The ECP5/ECP5-5G devices support the differential MLVDS standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The MLVDS input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3.4 is one possible solution for MLVDS standard implementation. Resistor values in the figure are industry standard values for 1% resistors.

Figure 3.4. MLVDS25 (Multipoint Low Voltage Differential Signaling)

| Parameter         | Description                    | Тур     | Typical |      |  |

|-------------------|--------------------------------|---------|---------|------|--|

|                   | Description                    | Zo=50 Ω | Zo=70 Ω | Unit |  |

| V <sub>CCIO</sub> | Output Driver Supply (±5%)     | 2.50    | 2.50    | V    |  |

| Z <sub>OUT</sub>  | Driver Impedance               | 10.00   | 10.00   | Ω    |  |

| R <sub>s</sub>    | Driver Series Resistor (±1%)   | 35.00   | 35.00   | Ω    |  |

| R <sub>TL</sub>   | Driver Parallel Resistor (±1%) | 50.00   | 70.00   | Ω    |  |

| R <sub>TR</sub>   | Receiver Termination (±1%)     | 50.00   | 70.00   | Ω    |  |

| V <sub>он</sub>   | Output High Voltage            | 1.52    | 1.60    | V    |  |

| V <sub>OL</sub>   | Output Low Voltage             | 0.98    | 0.90    | V    |  |

| V <sub>OD</sub>   | Output Differential Voltage    | 0.54    | 0.70    | V    |  |

| V <sub>CM</sub>   | Output Common Mode Voltage     | 1.25    | 1.25    | V    |  |

| I <sub>DC</sub>   | DC Output Current              | 21.74   | 20.00   | mA   |  |

#### Table 3.17. MLVDS25 DC Conditions

Note: For input buffer, see LVDS Table 3.13 on page 55.

FPGA-DS-02012-1.9

# 3.18. External Switching Characteristics

Over recommended commercial operating conditions.

### Table 3.22. ECP5/ECP5-5G External Switching Characteristics

| Devenueter             | Description                                                       | Davias         | -8        |     | -7    |     | -6   |     | l lait |

|------------------------|-------------------------------------------------------------------|----------------|-----------|-----|-------|-----|------|-----|--------|

| Parameter              | Description                                                       | Device         | Min       | Max | Min   | Max | Min  | Max | Unit   |

| Clocks                 | Clocks                                                            |                |           |     |       |     |      |     |        |

| Primary Clock          |                                                                   |                |           |     |       |     |      |     |        |

| f <sub>MAX_PRI</sub>   | Frequency for Primary Clock Tree                                  | _              | —         | 370 | —     | 303 | _    | 257 | MHz    |

| t <sub>w_pri</sub>     | Clock Pulse Width for Primary<br>Clock                            | _              | 0.8       | —   | 0.9   | —   | 1.0  | —   | ns     |

| t <sub>skew_pri</sub>  | Primary Clock Skew within a<br>Device                             | -              | -         | 420 | _     | 462 | -    | 505 | ps     |

| Edge Clock             |                                                                   |                | -         |     |       |     |      |     |        |

| f <sub>MAX_EDGE</sub>  | Frequency for Edge Clock Tree                                     | —              | _         | 400 | —     | 350 | _    | 312 | MHz    |

| tw_edge                | Clock Pulse Width for Edge Clock                                  | _              | 1.175     | _   | 1.344 | _   | 1.50 | —   | ns     |

| t <sub>skew_edge</sub> | Edge Clock Skew within a Bank                                     | -              | -         | 160 | -     | 180 | -    | 200 | ps     |

| Generic SDR In         | put                                                               |                |           |     | •     |     |      |     | •      |

| General I/O Pin        | Parameters Using Dedicated Primary (                              | Clock Input w  | ithout PL | L   |       |     |      |     |        |

| t <sub>co</sub>        | Clock to Output - PIO Output<br>Register                          | All<br>Devices | -         | 5.4 | -     | 6.1 | -    | 6.8 | ns     |

| t <sub>su</sub>        | Clock to Data Setup - PIO Input<br>Register                       | All<br>Devices | 0         | _   | 0     | _   | 0    | _   | ns     |

| t <sub>H</sub>         | Clock to Data Hold - PIO Input<br>Register                        | All<br>Devices | 2.7       | -   | 3     | -   | 3.3  | _   | ns     |

| t <sub>su_del</sub>    | Clock to Data Setup - PIO Input<br>Register with Data Input Delay | All<br>Devices | 1.2       | -   | 1.33  | -   | 1.46 | _   | ns     |

| t <sub>h_del</sub>     | Clock to Data Hold - PIO Input<br>Register with Data Input Delay  | All<br>Devices | 0         | _   | 0     | _   | 0    | _   | ns     |

| f <sub>MAX_IO</sub>    | Clock Frequency of I/O and PFU Register                           | All<br>Devices | -         | 400 | _     | 350 | -    | 312 | MHz    |

| General I/O Pin        | Parameters Using Dedicated Primary (                              | Clock Input w  | ith PLL   |     |       |     |      |     |        |

| t <sub>copll</sub>     | Clock to Output - PIO Output<br>Register                          | All<br>Devices | _         | 3.5 | _     | 3.8 | _    | 4.1 | ns     |

| t <sub>supll</sub>     | Clock to Data Setup - PIO Input<br>Register                       | All<br>Devices | 0.7       | _   | 0.78  |     | 0.85 | _   | ns     |

| t <sub>HPLL</sub>      | Clock to Data Hold - PIO Input<br>Register                        | All<br>Devices | 0.8       | _   | 0.89  | -   | 0.98 | _   | ns     |

| t <sub>su_delpll</sub> | Clock to Data Setup - PIO Input<br>Register with Data Input Delay | All<br>Devices | 1.6       | _   | 1.78  | _   | 1.95 | _   | ns     |

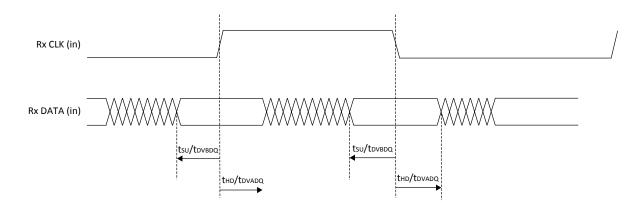

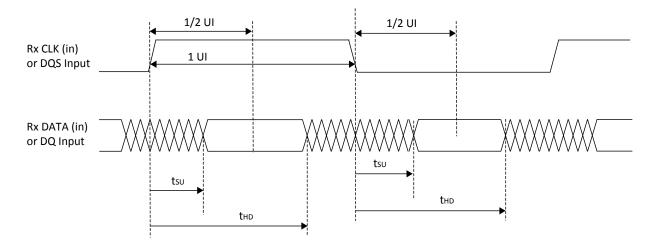

Figure 3.6. Receiver RX.CLK.Centered Waveforms

Figure 3.7. Receiver RX.CLK.Aligned and DDR Memory Input Waveforms

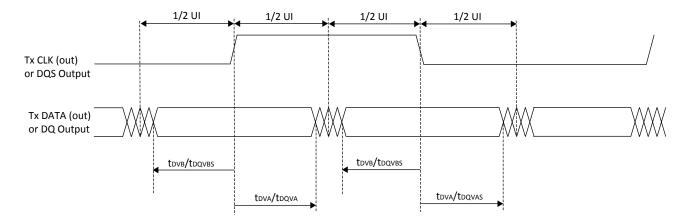

Figure 3.8. Transmit TX.CLK.Centered and DDR Memory Output Waveforms

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

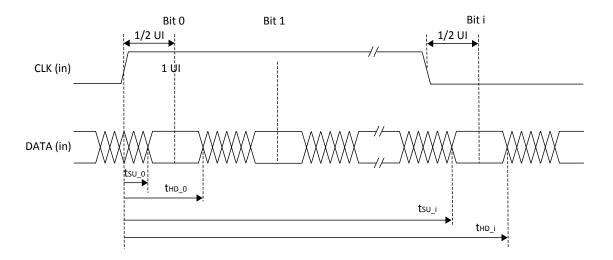

Figure 3.11. Receiver DDRX71\_RX Waveforms

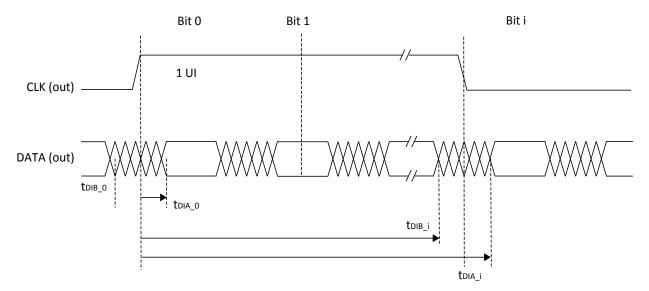

Figure 3.12. Transmitter DDRX71\_TX Waveforms

# 3.19. sysCLOCK PLL Timing

Over recommended operating conditions.

| Parameter                      | Descriptions                                                         | Conditions                 | Min   | Max   | Units      |

|--------------------------------|----------------------------------------------------------------------|----------------------------|-------|-------|------------|

| f <sub>IN</sub>                | Input Clock Frequency (CLKI, CLKFB)                                  | _                          | 8     | 400   | MHz        |

| f <sub>out</sub>               | Output Clock Frequency (CLKOP, CLKOS)                                | —                          | 3.125 | 400   | MHz        |

| f <sub>vco</sub>               | PLL VCO Frequency                                                    | —                          | 400   | 800   | MHz        |

| $f_{\text{PFD}}{}^3$           | Phase Detector Input Frequency                                       | _                          | 10    | 400   | MHz        |

| AC Characteris                 | itics                                                                |                            |       |       |            |

| t <sub>DT</sub>                | Output Clock Duty Cycle                                              | _                          | 45    | 55    | %          |

| t <sub>PH4</sub>               | Output Phase Accuracy                                                | _                          | -5    | 5     | %          |

|                                |                                                                      | f <sub>o∪T</sub> ≥ 100 MHz | _     | 100   | ps p-p     |

|                                | Output Clock Period Jitter                                           | f <sub>о∪т</sub> < 100 MHz | _     | 0.025 | UIPP       |

|                                |                                                                      | f <sub>o∪T</sub> ≥ 100 MHz | _     | 200   | ps p-p     |

| t <sub>opjit</sub> 1           | Output Clock Cycle-to-Cycle Jitter                                   | f <sub>о∪т</sub> < 100 MHz | _     | 0.050 | UIPP       |

|                                | Output Clock Phase Jitter                                            | f <sub>PFD</sub> ≥ 100 MHz | _     | 200   | ps p-p     |

|                                |                                                                      | f <sub>PFD</sub> < 100 MHz | _     | 0.011 | UIPP       |

| t <sub>spo</sub>               | Static Phase Offset                                                  | Divider ratio =<br>integer | _     | 400   | ps p-p     |

| t <sub>w</sub>                 | Output Clock Pulse Width                                             | At 90% or 10%              | 0.9   | _     | ns         |

| t <sub>LOCK</sub> <sup>2</sup> | PLL Lock-in Time                                                     | _                          | _     | 15    | ms         |

| t <sub>UNLOCK</sub>            | PLL Unlock Time                                                      | _                          | _     | 50    | ns         |

| _                              |                                                                      | f <sub>PFD</sub> ≥ 20 MHz  | _     | 1,000 | ps p-p     |

| t <sub>IPJIT</sub>             | Input Clock Period Jitter                                            | f <sub>PFD</sub> < 20 MHz  | _     | 0.02  | UIPP       |

| t <sub>HI</sub>                | Input Clock High Time                                                | 90% to 90%                 | 0.5   | _     | ns         |

| t <sub>LO</sub>                | Input Clock Low Time                                                 | 10% to 10%                 | 0.5   | _     | ns         |

| t <sub>RST</sub>               | RST/ Pulse Width                                                     | _                          | 1     | _     | ms         |

| t <sub>rstrec</sub>            | RST Recovery Time                                                    | _                          | 1     | -     | ns         |

| t <sub>load_reg</sub>          | Min Pulse for CIB_LOAD_REG                                           | _                          | 10    | _     | ns         |

| t <sub>ROTATE-SETUP</sub>      | Min time for CIB dynamic phase controls to be stable fore CIB_ROTATE | _                          | 5     | _     | ns         |

| t <sub>rotate-wd</sub>         | Min pulse width for CIB_ROTATE to maintain "0" or                    | _                          | 4     | -     | VCO cycles |

Notes:

1. Jitter sample is taken over 10,000 samples for Periodic jitter, and 2,000 samples for Cycle-to-Cycle jitter of the primary PLL output with clean reference clock with no additional I/O toggling.

2. Output clock is valid after  $t_{LOCK}$  for PLL reset and dynamic delay adjustment.

3. Period jitter and cycle-to-cycle jitter numbers are guaranteed for  $f_{PFD} > 10$  MHz. For  $f_{PFD} < 10$  MHz, the jitter numbers may not be met in certain conditions.

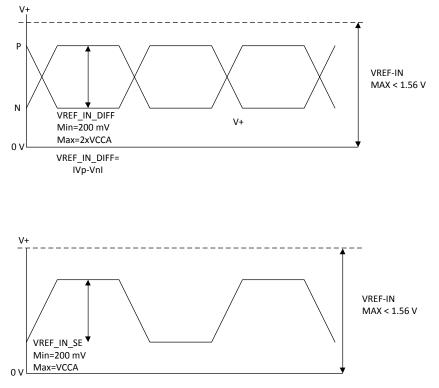

# 3.24. SERDES External Reference Clock

The external reference clock selection and its interface are a critical part of system applications for this product. Table 3.29 specifies reference clock requirements, over the full range of operating conditions.

| Symbol                        | Description                                     | Min                       | Тур     | Max                       | Unit                    |

|-------------------------------|-------------------------------------------------|---------------------------|---------|---------------------------|-------------------------|

| F <sub>REF</sub>              | Frequency range                                 | 50                        | —       | 320                       | MHz                     |

| F <sub>REF-PPM</sub>          | Frequency tolerance <sup>1</sup>                | -1000                     | —       | 1000                      | ppm                     |

| V <sub>REF-IN-SE</sub>        | Input swing, single-ended clock <sup>2, 4</sup> | 200 — V <sub>CCAUXA</sub> |         |                           | тV, р-р                 |

| V <sub>REF-IN-DIFF</sub>      | Input swing, differential clock                 | 200 – 2*V <sub>CCA</sub>  |         | 2*V <sub>CCAUXA</sub>     | mV, p-p<br>differential |

| V <sub>REF-IN</sub>           | Input levels                                    | 0                         | —       | V <sub>CCAUXA</sub> + 0.4 | V                       |

| D <sub>REF</sub>              | Duty cycle <sup>3</sup>                         | 40                        | —       | 60                        | %                       |

| T <sub>REF-R</sub>            | Rise time (20% to 80%)                          | 200                       | 500     | 1000                      | ps                      |

| T <sub>REF-F</sub>            | Fall time (80% to 20%)                          | 200                       | 500     | 1000                      | ps                      |

| Z <sub>REF-IN-TERM-DIFF</sub> | Differential input termination                  | -30%                      | 100/HiZ | +30%                      | Ω                       |

| C <sub>REF-IN-CAP</sub>       | Input capacitance                               | _                         | _       | 7                         | pF                      |

Table 3.29. External Reference Clock Specification (refclkp/refclkn)

#### Notes:

1. Depending on the application, the PLL\_LOL\_SET and CDR\_LOL\_SET control registers may be adjusted for other tolerance values as described in ECP5 and ECP5-5G SERDES/PCS Usage Guide (TN1261).

- 2. The signal swing for a single-ended input clock must be as large as the p-p differential swing of a differential input clock to get the same gain at the input receiver. With single-ended clock, a reference voltage needs to be externally connected to CLKREFN pin, and the input voltage needs to be swung around this reference voltage.

- 3. Measured at 50% amplitude.

- 4. Single-ended clocking is achieved by applying a reference voltage V<sub>REF</sub> on REFCLKN input, with the clock applied to REFCLKP input pin. V<sub>REF</sub> should be set to mid-point of the REFCLKP voltage swing.

Figure 3.14. SERDES External Reference Clock Waveforms

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

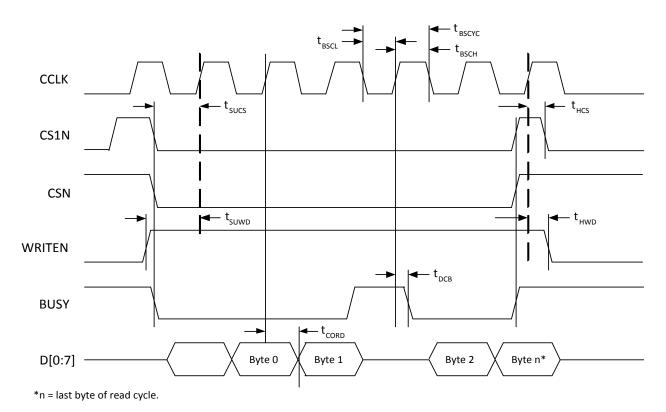

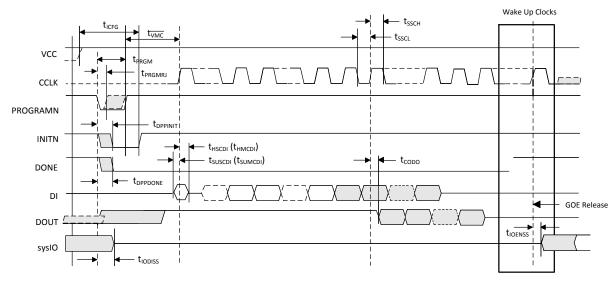

### Table 3.42. ECP5/ECP5-5G sysCONFIG Port Timing Specifications (Continued)

| Symbol              | Parameter                        |   | Min | Max | Unit |  |

|---------------------|----------------------------------|---|-----|-----|------|--|

| Slave Parallel      |                                  |   |     |     |      |  |

| f <sub>cclк</sub>   | CCLK input clock frequency       | — | —   | 50  | MHz  |  |

| t <sub>BSCH</sub>   | CCLK input clock pulsewidth HIGH | — | 6   | _   | ns   |  |

| t <sub>BSCL</sub>   | CCLK input clock pulsewidth LOW  | — | 6   | _   | ns   |  |

| t <sub>CORD</sub>   | CCLK to DOUT for Read Data       | — | —   | 12  | ns   |  |

| t <sub>sucbdi</sub> | Data Setup Time to CCLK          | — | 1.5 | _   | ns   |  |

| t <sub>HCBDI</sub>  | Data Hold Time to CCLK           | — | 1.5 | _   | ns   |  |

| t <sub>sucs</sub>   | CSN, CSN1 Setup Time to CCLK     | — | 2.5 | _   | ns   |  |

| t <sub>HCS</sub>    | CSN, CSN1 Hold Time to CCLK      | — | 1.5 | _   | ns   |  |

| t <sub>suwd</sub>   | WRITEN Setup Time to CCLK        | — | 45  | _   | ns   |  |

| t <sub>HCWD</sub>   | WRITEN Hold Time to CCLK         | — | 2   | _   | ns   |  |

| t <sub>DCB</sub>    | CCLK to BUSY Delay Time          | — | _   | 12  | ns   |  |

Figure 3.15. sysCONFIG Parallel Port Read Cycle

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

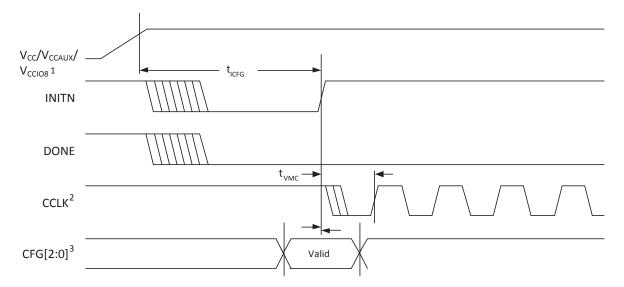

- 1. Time taken from  $V_{CC}$ ,  $V_{CCAUX}$  or  $V_{CCIO8}$ , whichever is the last to cross the POR trip point.

- 2. Device is in a Master Mode (SPI, SPIm).

- 3. The CFG pins are normally static (hardwired).

Figure 3.19. sysCONFIG Port Timing

| Signal Name                          | I/O      | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL, DLL and Clock Functions (Contin | nued)    |                                                                                                                                                                                                                                                                                                                                                                                             |

| [L/R]DQS[group_num]                  | I/O      | DQS input/output pads: T (top), R (right), group_num = ball number associated with DQS[T] pin.                                                                                                                                                                                                                                                                                              |

| [T/R]]DQ[group_num]                  | I/O      | DQ input/output pads: T (top), R (right), group_ num = ball number associated with DQS[T] pin.                                                                                                                                                                                                                                                                                              |

| Test and Programming (Dedicated F    | Pins)    |                                                                                                                                                                                                                                                                                                                                                                                             |

| TMS                                  |          | Test Mode Select input, used to control the 1149.1 state machine. Pull-up is enabled during configuration. This is a dedicated input pin.                                                                                                                                                                                                                                                   |

| тск                                  | I        | Test Clock input pin, used to clock the 1149.1 state machine. No pull-up enabled.<br>This is a dedicated input pin.                                                                                                                                                                                                                                                                         |

| TDI                                  | I        | Test Data in pin. Used to load data into device using 1149.1 state machine. After power-up, this TAP port can be activated for configuration by sending appropriate command. (Note: once a configuration port is selected it is locked. Another configuration port cannot be selected until the power-up sequence). Pull-up is enabled during configuration. This is a dedicated input pin. |

| TDO                                  | О        | Output pin. Test Data Out pin used to shift data out of a device using 1149.1.<br>This is a dedicated output pin.                                                                                                                                                                                                                                                                           |

| Configuration Pads (Used during sys  | sCONFIG) |                                                                                                                                                                                                                                                                                                                                                                                             |

| CFG[2:0]                             | I        | Mode pins used to specify configuration mode values latched on rising edge of INITN. During configuration, a pull-up is enabled.<br>These are dedicated pins.                                                                                                                                                                                                                               |

| INITN                                | I/O      | Open Drain pin. Indicates the FPGA is ready to be configured. During configuration, a pull-up is enabled.<br>This is a dedicated pin.                                                                                                                                                                                                                                                       |

| PROGRAMN                             | I        | Initiates configuration sequence when asserted low. This pin always has an active pull-up.<br>This is a dedicated pin.                                                                                                                                                                                                                                                                      |

| DONE                                 | ı/o      | Open Drain pin. Indicates that the configuration sequence is complete, and the startup sequence is in progress.<br>This is a dedicated pin.                                                                                                                                                                                                                                                 |

| CCLK                                 | I/O      | Input Configuration Clock for configuring an FPGA in Slave SPI, Serial, and CPU modes. Output Configuration Clock for configuring an FPGA in Master configuration modes (Master SPI, Master Serial).<br>This is a dedicated pin.                                                                                                                                                            |

| HOLDN/DI/BUSY/CSSPIN/CEN             | I/O      | Parallel configuration mode busy indicator. SPI/SPIm mode data output.<br>This is a shared I/O pin. This is a shared I/O pin. When not in configuration, it can<br>be used as general purpose I/O pin.                                                                                                                                                                                      |

| CSN/SN                               | I/O      | Parallel configuration mode active-low chip select. Slave SPI chip select. This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O pin.                                                                                                                                                                                                                  |

| CS1N                                 | I        | Parallel configuration mode active-low chip select.<br>This is a shared I/O pin. When not in configuration, it can be used as general<br>purpose I/O pin.                                                                                                                                                                                                                                   |

| WRITEN                               | I        | Write enable for parallel configuration modes.<br>This is a shared I/O pin. When not in configuration, it can be used as general<br>purpose I/O pin.                                                                                                                                                                                                                                        |

| DOUT/CSON                            | о        | Serial data output. Chip select output. SPI/SPIm mode chip select. This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O                                                                                                                                                                                                                               |

| D0/MOSI/IO0                          | I/O      | Parallel configuration I/O. Open drain during configuration. When in SPI modes,<br>it is an output in Master mode, and input in Slave mode.<br>This is a shared I/O pin. When not in configuration, it can be used as general<br>purpose I/O pin.                                                                                                                                           |

<sup>© 2014-2018</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### (Continued)

| Date        | Version | Section                             | Change Summary                                                                                                                                                                                                                               |

|-------------|---------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| August 2014 | 1.2     | DC and Switching<br>Characteristics | SERDES High-Speed Data Receiver section. Updated Table 3.26. Serial<br>Input Data Specifications, Table 3.28. Receiver Total Jitter Tolerance<br>Specification, and Table 3.29. External Reference Clock Specification<br>(refclkp/refclkn). |

|             |         |                                     | Modified section heading to XXAUI/CPRI LV E.30 Electrical and Timing<br>Characteristics. Updated Table 3.33 Transmit and Table 3.34. Receive<br>and Jitter Tolerance.                                                                        |

|             |         |                                     | Modified section heading to CPRI LV E.24 Electrical and Timing<br>Characteristics. Updated Table 3.35. Transmit and Table 3.36. Receive<br>and Jitter Tolerance.                                                                             |

|             |         |                                     | Modified section heading to Gigabit Ethernet/SGMII/CPRI LV E.12<br>Electrical and Timing Characteristics. Updated Table 3.37. Transmit and<br>Table 3.38. Receive and Jitter Tolerance.                                                      |

| June 2014   | 1.1     | Ordering Information                | Updated ECP5/ECP5-5G Part Number Description and Ordering Part Numbers sections.                                                                                                                                                             |

| March 2014  | 1.0     | All                                 | Initial release.                                                                                                                                                                                                                             |

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.