# E. Attice Semiconductor Corporation - <u>LFE5UM-85F-6MG285C Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                        |

|--------------------------------|-------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 21000                                                                         |

| Number of Logic Elements/Cells | 84000                                                                         |

| Total RAM Bits                 | 3833856                                                                       |

| Number of I/O                  | 118                                                                           |

| Number of Gates                | -                                                                             |

| Voltage - Supply               | 1.045V ~ 1.155V                                                               |

| Mounting Type                  | Surface Mount                                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                               |

| Package / Case                 | 285-LFBGA, CSPBGA                                                             |

| Supplier Device Package        | 285-CSFBGA (10x10)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe5um-85f-6mg285c |

|                                |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 3.1.            | Absolute Maximum Ratings                                                                |    |

|-----------------|-----------------------------------------------------------------------------------------|----|

| 3.2.            | Recommended Operating Conditions                                                        |    |

| 3.3.            | Power Supply Ramp Rates                                                                 |    |

| 3.4.            | Power-On-Reset Voltage Levels                                                           |    |

| 3.5.            | Power up Sequence                                                                       |    |

| 3.6.            | Hot Socketing Specifications                                                            |    |

| 3.7.            | Hot Socketing Requirements                                                              |    |

| 3.8.            | ESD Performance                                                                         |    |

| 3.9.            | DC Electrical Characteristics                                                           | 49 |

| 3.10.           | Supply Current (Standby)                                                                |    |

| 3.11.           | SERDES Power Supply Requirements <sup>1,2,3</sup>                                       | 51 |

| 3.12.           | sysI/O Recommended Operating Conditions                                                 | 53 |

| 3.13.           | sysI/O Single-Ended DC Electrical Characteristics                                       | 54 |

| 3.14.           | sysI/O Differential Electrical Characteristics                                          | 55 |

| 3.14            | 4.1. LVDS                                                                               |    |

| 3.14            |                                                                                         |    |

| 3.14            |                                                                                         |    |

| 3.14            |                                                                                         |    |

| 3.14            |                                                                                         |    |

| 3.14            |                                                                                         |    |

| 3.14            |                                                                                         |    |

| 3.14            |                                                                                         |    |

|                 | Typical Building Block Function Performance                                             |    |

| 3.15.           | Derating Timing Tables                                                                  |    |

| 3.16.           |                                                                                         |    |

| 3.17.           | Maximum I/O Buffer Speed                                                                |    |

| 3.18.           | External Switching Characteristics                                                      |    |

| 3.19.           | sysCLOCK PLL Timing                                                                     |    |

| 3.20.           | SERDES High-Speed Data Transmitter                                                      |    |

| 3.21.           | SERDES/PCS Block Latency                                                                |    |

| 3.22.           | SERDES High-Speed Data Receiver                                                         |    |

| 3.23.           | Input Data Jitter Tolerance                                                             |    |

| 3.24.           | SERDES External Reference Clock                                                         |    |

| 3.25.           | PCI Express Electrical and Timing Characteristics                                       |    |

| 3.25            | 5.1. PCIe (2.5 Gb/s) AC and DC Characteristics                                          | 76 |

| 3.25            | 5.2. PCIe (5 Gb/s) – Preliminary AC and DC Characteristics                              | 77 |

| 3.26.           | CPRI LV2 E.48 Electrical and Timing Characteristics – Preliminary                       | 79 |

| 3.27.           | XAUI/CPRI LV E.30 Electrical and Timing Characteristics                                 | 80 |

| 3.27            | 7.1. AC and DC Characteristics                                                          | 80 |

| 3.28.           | CPRI LV E.24/SGMII(2.5Gbps) Electrical and Timing Characteristics                       | 80 |

| 3.28            | 8.1. AC and DC Characteristics                                                          | 80 |

| 3.29.           | Gigabit Ethernet/SGMII(1.25Gbps)/CPRI LV E.12 Electrical and Timing Characteristics     | 81 |

| 3.29            |                                                                                         |    |

| 3.30.           | SMPTE SD/HD-SDI/3G-SDI (Serial Digital Interface) Electrical and Timing Characteristics |    |

| 3.30            |                                                                                         |    |

| 3.31.           | sysCONFIG Port Timing Specifications                                                    |    |

| 3.32.           | JTAG Port Timing Specifications                                                         |    |

| 3.33.           | Switching Test Conditions                                                               |    |

|                 | out Information                                                                         |    |

| 4. Pint<br>4.1. | Signal Descriptions                                                                     |    |

| 4.1.<br>4.2.    | PICs and DDR Data (DQ) Pins Associated with the DDR Strobe (DQS) Pin                    |    |

|                 |                                                                                         |    |

| 4.3.            | Pin Information Summary                                                                 |    |

| 4.3.            |                                                                                         |    |

| 4.3.            |                                                                                         |    |

| 5. Ord          | lering Information                                                                      |    |

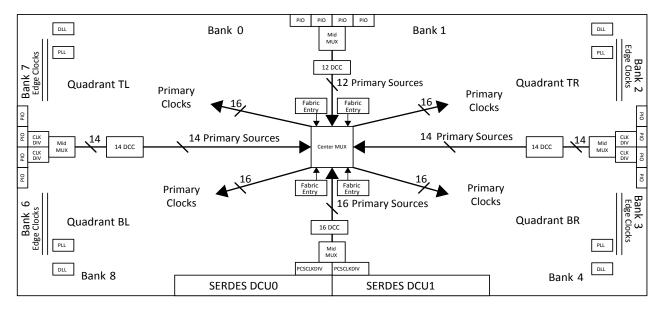

Figure 2.6. LFE5UM/LFE5UM5G-85 Clocking

### 2.5.1. Primary Clocks

The ECP5/ECP5-5G device family provides low-skew, high fan-out clock distribution to all synchronous elements in the FPGA fabric through the Primary Clock Network.

The primary clock network is divided into four clocking quadrants: Top Left (TL), Bottom Left (BL), Top Right (TR), and Bottom Right (BR). Each of these quadrants has 16 clocks that can be distributed to the fabric in the quadrant.

The Lattice Diamond software can automatically route each clock to one of the four quadrants up to a maximum of 16 clocks per quadrant. The user can change how the clocks are routed by specifying a preference in the Lattice Diamond software to locate the clock to specific. The ECP5/ECP5-5G device provides the user with a maximum of 64 unique clock input sources that can be routed to the primary Clock network.

Primary clock sources are:

- Dedicated clock input pins

- PLL outputs

- CLKDIV outputs

- Internal FPGA fabric entries (with minimum general routing)

- SERDES/PCS/PCSDIV clocks

- OSC clock

These sources are routed to one of four clock switches called a Mid Mux. The outputs of the Mid MUX are routed to the center of the FPGA where another clock switch, called the Center MUX, is used to route the primary clock sources to primary clock distribution to the ECP5/ECP5-5G fabric. These routing muxes are shown in Figure 2.6. Since there is a maximum of 60 unique clock input sources to the clocking quadrants, there are potentially 64 unique clock domains that can be used in the ECP5/ECP5-5G Device. For more information about the primary clock tree and connections, refer to ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263).

### 2.5.1.1. Dynamic Clock Control

The Dynamic Clock Control (DCC), Quadrant Clock enable/disable feature allows internal logic control of the quadrant primary clock network. When a clock network is disabled, the clock signal is static and not toggle. All the logic fed by that clock will not toggle, reducing the overall power consumption of the device. The disable function will not create glitch and increase the clock latency to the primary clock network.

This DCC controls the clock sources from the Primary CLOCK MIDMUX before they are fed to the Primary Center MUXs that drive the quadrant clock network. For more information about the DCC, refer to ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263).

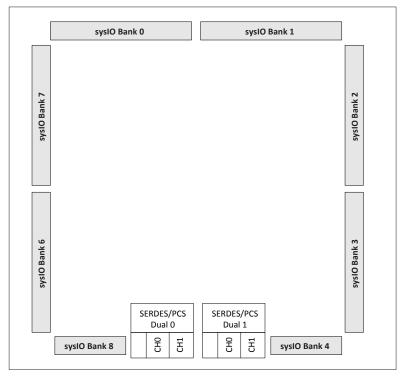

Figure 2.27. SERDES/PCS Duals (LFE5UM/LFE5UM5G-85)

| Standard                                                                                                                                                                       | Data Rate (Mb/s)                                           | Number of General/Link Width | Encoding Style |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------------------|----------------|

| PCI Express 1.1 and 2.0                                                                                                                                                        | 2500                                                       | x1, x2, x4                   | 8b10b          |

| 2.02                                                                                                                                                                           | 5000 <sup>2</sup>                                          | x1, x2                       | 8b10b          |

| Gigabit Ethernet                                                                                                                                                               | 1250                                                       | x1                           | 8b10b          |

| COMU                                                                                                                                                                           | 1250                                                       | x1                           | 8b10b          |

| PCI Express 1.1 and 2.0   2.02   Gigabit Ethernet   GGMII   GAUI   CPRI-1   CPRI-2   CPRI-3   CPRI-4   CPRI-5   GD-SDI (259M, 344M) <sup>1</sup> HD-SDI (292M)   3G-SDI (424M) | 2500                                                       | x1                           | 8b10b          |

| XAUI                                                                                                                                                                           | 3125                                                       | x4                           | 8b10b          |

| CPRI-1<br>CPRI-2<br>CPRI-3<br>CPRI-4<br>CPRI-5                                                                                                                                 | 614.4<br>1228.8<br>2457.6<br>3072.0<br>4915.2 <sup>2</sup> | x1                           | 8b10b          |

| SD-SDI (259M, 344M) 1                                                                                                                                                          | 270                                                        | x1                           | NRZI/Scrambled |

| HD-SDI (292M)                                                                                                                                                                  | 1483.5<br>1485                                             | x1                           | NRZI/Scrambled |

| 3G-SDI (424M)                                                                                                                                                                  | 2967<br>2970                                               | x1                           | NRZI/Scrambled |

|                                                                                                                                                                                | 5000                                                       | _                            | _              |

| JESD204A/B                                                                                                                                                                     | 3125                                                       | x1                           | 8b/10b         |

#### Notes:

1. For SD-SDI rate, the SERDES is bypassed and SERDES input signals are directly connected to the FPGA routing.

2. For ECP5-5G family devices only.

# 2.18. Device Configuration

All ECP5/ECP5-5G devices contain two ports that can be used for device configuration. The Test Access Port (TAP), which supports bit-wide configuration, and the sysCONFIG port, support dual-byte, byte and serial configuration. The TAP supports both the IEEE Standard 1149.1 Boundary Scan specification and the IEEE Standard 1532 In-System Configuration specification. There are 11 dedicated pins for TAP and sysConfig supports (TDI, TDO, TCK, TMS, CFG[2:0], PROGRAMN, DONE, INITN and CCLK). The remaining sysCONFIG pins are used as dual function pins. Refer to ECP5 and ECP5-5G sysCONFIG Usage Guide (TN1260) for more information about using the dual-use pins as general purpose I/Os.

There are various ways to configure an ECP5/ECP5-5G device:

- JTAG

- Standard Serial Peripheral Interface (SPI) Interface to boot PROM Support x1, x2, x4 wide SPI memory interfaces.

- System microprocessor to drive a x8 CPU port SPCM mode

- System microprocessor to drive a serial slave SPI port (SSPI mode)

- Slave Serial model (SCM)

On power-up, the FPGA SRAM is ready to be configured using the selected sysCONFIG port. Once a configuration port is selected, it will remain active throughout that configuration cycle. The IEEE 1149.1 port can be activated any time after power-up by sending the appropriate command through the TAP port.

ECP5/ECP5-5G devices also support the Slave SPI Interface. In this mode, the FPGA behaves like a SPI Flash device (slave mode) with the SPI port of the FPGA to perform read-write operations.

### 2.18.1. Enhanced Configuration Options

ECP5/ECP5-5G devices have enhanced configuration features such as: decryption support, decompression support, TransFR™ I/O and dual-boot and multi-boot image support.

### TransFR (Transparent Field Reconfiguration)

TransFR I/O (TFR) is a unique Lattice technology that allows users to update their logic in the field without interrupting system operation using a single ispVM command. TransFR I/O allows I/O states to be frozen during device configuration. This allows the device to be field updated with a minimum of system disruption and downtime. Refer to Minimizing System Interruption During Configuration Using TransFR Technology (TN1087) for details.

### **Dual-Boot and Multi-Boot Image Support**

Dual-boot and multi-boot images are supported for applications requiring reliable remote updates of configuration data for the system FPGA. After the system is running with a basic configuration, a new boot image can be downloaded remotely and stored in a separate location in the configuration storage device. Any time after the update the ECP5/ECP5-5G devices can be re-booted from this new configuration file. If there is a problem, such as corrupt data during download or incorrect version number with this new boot image, the ECP5/ECP5-5G device can revert back to the original backup golden configuration and try again. This all can be done without power cycling the system. For more information, refer to ECP5 and ECP5-5G sysCONFIG Usage Guide (TN1260).

### 2.18.2. Single Event Upset (SEU) Support

ECP5/ECP5-5G devices support SEU mitigation with three supporting functions:

- SED Soft Error Detect

- SEC Soft Error Correction

- SEI Soft Error Injection

ECP5/ECP5-5G devices have dedicated logic to perform Cycle Redundancy Code (CRC) checks. During configuration, the configuration data bitstream can be checked with the CRC logic block. In addition, the ECP5/ECP5-5G device can also be programmed to utilize a Soft Error Detect (SED) mode that checks for soft errors in configuration SRAM. The SED operation can be run in the background during user mode. If a soft error occurs, during user mode (normal operation) the device can be programmed to generate an error signal.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

# 3.7. Hot Socketing Requirements

### **Table 3.6. Hot Socketing Requirements**

| Description                                                                               | Min | Тур | Max | Unit |

|-------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Input current per SERDES I/O pin when device is powered down and inputs driven.           | _   | _   | 8   | mA   |

| Input current per HDIN pin when device power supply is off, inputs driven <sup>1, 2</sup> | _   | _   | 15  | mA   |

| Current per HDIN pin when device power ramps up, input driven <sup>3</sup>                | _   | _   | 50  | mA   |

| Current per HDOUT pin when device power supply is off, outputs pulled up <sup>4</sup>     | —   | —   | 30  | mA   |

Notes:

1. Device is powered down with all supplies grounded, both HDINP and HDINN inputs driven by a CML driver with maximum allowed output V<sub>CCHTX</sub>, 8b/10b data, no external AC coupling.

2. Each P and N input must have less than the specified maximum input current during hot plug. For a device with 2 DCU, the total input current would be 15 mA \* 4 channels \* 2 input pins per channel = 120 mA.

- Device power supplies are ramping up (V<sub>CCA</sub> and V<sub>CCAUX</sub>), both HDINP and HDINN inputs are driven by a CML driver with maximum allowed output V<sub>CCHTX</sub>, 8b/10b data, internal AC coupling.

- 4. Device is powered down with all supplies grounded. Both HDOUTP and HDOUN outputs are pulled up to  $V_{CCHTX}$  by the far end receiver termination of 50  $\Omega$  single ended.

### 3.8. ESD Performance

Refer to the ECP5 and ECP5-5G Product Family Qualification Summary for complete qualification data, including ESD performance.

### 3.9. DC Electrical Characteristics

**Over Recommended Operating Conditions**

| Symbol                                            | Parameter                                                        | Condition                                                                                                                                             | Min | Тур | Max  | Unit |

|---------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| I <sub>IL</sub> , I <sub>IH</sub> <sup>1, 4</sup> | Input or I/O Low Leakage                                         | $0 \leq V_{\text{IN}} \leq V_{\text{CCIO}}$                                                                                                           | _   | —   | 10   | μA   |

| I <sub>IH</sub> <sup>1, 3</sup>                   | Input or I/O High Leakage                                        | $V_{CCIO} < V_{IN} \leq V_{IH(MAX)}$                                                                                                                  | —   | —   | 100  | μA   |

| I                                                 | I/O Active Pull-up Current,<br>sustaining logic HIGH state       | $0.7 \: V_{CCIO} \! \leq \! V_{IN} \! \leq \! V_{CCIO}$                                                                                               | -30 | _   | _    | μA   |

| I <sub>PU</sub>                                   | I/O Active Pull-up Current, pulling down from logic HIGH state   | $0 \leq V_{\text{IN}} \leq 0.7 \; V_{\text{CCIO}}$                                                                                                    |     | _   | -150 | μA   |

| IPD                                               | I/O Active Pull-down Current,<br>sustaining logic LOW state      | $0 \le V_{IN} \le V_{IL}$ (MAX)                                                                                                                       | 30  | —   | —    | μA   |

| IDD                                               | I/O Active Pull-down Current,<br>pulling up from logic LOW state | $0 \leq V_{IN} \leq V_{CCIO}$                                                                                                                         | —   | —   | 150  | μA   |

| C1                                                | I/O Capacitance <sup>2</sup>                                     | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V}, \\ V_{CC} = 1.2 \text{ V}, V_{IO} = 0 \text{ to } V_{IH(MAX)}$ | _   | 5   | 8    | pf   |

| C2                                                | Dedicated Input Capacitance <sup>2</sup>                         | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V}, \\ V_{CC} = 1.2 \text{ V}, V_{IO} = 0 \text{ to } V_{IH(MAX)}$ | _   | 5   | 7    | pf   |

| V                                                 | Hysteresis for Single-Ended                                      | V <sub>CCIO</sub> = 3.3 V                                                                                                                             | -   | 300 | _    | mV   |

| V <sub>HYST</sub>                                 | Inputs                                                           | V <sub>CCIO</sub> = 2.5 V                                                                                                                             | _   | 250 | _    | mV   |

#### **Table 3.7. DC Electrical Characteristics**

Notes:

1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tristated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

2. T<sub>A</sub> 25 °C, f = 1.0 MHz.

- 3. Applicable to general purpose I/Os in top and bottom banks.

- 4. When used as  $V_{REF}$ , maximum leakage= 25  $\mu$ A.

# 3.15. Typical Building Block Function Performance

### Table 3.19. Pin-to-Pin Performance

| Function        | –8 Timing | Unit |

|-----------------|-----------|------|

| Basic Functions |           |      |

| 16-Bit Decoder  | 5.06      | ns   |

| 32-Bit Decoder  | 6.08      | ns   |

| 64-Bit Decoder  | 5.06      | ns   |

| 4:1 Mux         | 4.45      | ns   |

| 8:1 Mux         | 4.63      | ns   |

| 16:1 Mux        | 4.81      | ns   |

| 32:1 Mux        | 4.85      | ns   |

Notes:

1. I/Os are configured with LVCMOS25 with V<sub>CCIO</sub>=2.5, 12 mA drive.

2. These functions were generated using Lattice Diamond design software tool. Exact performance may vary with the device and the design software tool version. The design software tool uses internal parameters that have been characterized but are not tested on every device.

3. Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from Lattice Diamond design software tool.

# 3.18. External Switching Characteristics

Over recommended commercial operating conditions.

### Table 3.22. ECP5/ECP5-5G External Switching Characteristics

| D                      | Description                                                       | Device         | -         | 8   | -7    |     | -6   |     |      |

|------------------------|-------------------------------------------------------------------|----------------|-----------|-----|-------|-----|------|-----|------|

| Parameter              | Description                                                       | Device         | Min       | Max | Min   | Max | Min  | Max | Unit |

| Clocks                 |                                                                   |                |           |     |       |     |      |     |      |

| Primary Clock          |                                                                   |                |           |     |       |     |      |     |      |

| f <sub>MAX_PRI</sub>   | Frequency for Primary Clock Tree                                  | -              | _         | 370 | —     | 303 | -    | 257 | MHz  |

| t <sub>w_pri</sub>     | Clock Pulse Width for Primary<br>Clock                            | _              | 0.8       | _   | 0.9   | —   | 1.0  | —   | ns   |

| t <sub>skew_pri</sub>  | Primary Clock Skew within a<br>Device                             | -              | -         | 420 | _     | 462 | -    | 505 | ps   |

| Edge Clock             |                                                                   |                | -         |     |       |     |      |     |      |

| f <sub>MAX_EDGE</sub>  | Frequency for Edge Clock Tree                                     | _              | _         | 400 | _     | 350 | _    | 312 | MHz  |

| tw_edge                | Clock Pulse Width for Edge Clock                                  | _              | 1.175     | _   | 1.344 | _   | 1.50 | _   | ns   |

| t <sub>skew_edge</sub> | Edge Clock Skew within a Bank                                     | _              | _         | 160 | —     | 180 | _    | 200 | ps   |

| Generic SDR In         | put                                                               |                | •         |     | •     |     |      |     |      |

| General I/O Pin        | Parameters Using Dedicated Primary (                              | Clock Input w  | ithout PL | L   |       |     |      |     |      |

| t <sub>co</sub>        | Clock to Output - PIO Output<br>Register                          | All<br>Devices | _         | 5.4 | _     | 6.1 | _    | 6.8 | ns   |

| t <sub>su</sub>        | Clock to Data Setup - PIO Input<br>Register                       | All<br>Devices | 0         | _   | 0     | _   | 0    | _   | ns   |

| t <sub>H</sub>         | Clock to Data Hold - PIO Input<br>Register                        | All<br>Devices | 2.7       | -   | 3     | -   | 3.3  | -   | ns   |

| t <sub>su_del</sub>    | Clock to Data Setup - PIO Input<br>Register with Data Input Delay | All<br>Devices | 1.2       | -   | 1.33  | -   | 1.46 | -   | ns   |

| t <sub>H_DEL</sub>     | Clock to Data Hold - PIO Input<br>Register with Data Input Delay  | All<br>Devices | 0         | -   | 0     | -   | 0    | -   | ns   |

| f <sub>MAX_IO</sub>    | Clock Frequency of I/O and PFU<br>Register                        | All<br>Devices | _         | 400 | _     | 350 | _    | 312 | MHz  |

| General I/O Pin        | Parameters Using Dedicated Primary (                              | Clock Input w  | ith PLL   |     |       |     |      |     |      |

| t <sub>copll</sub>     | Clock to Output - PIO Output<br>Register                          | All<br>Devices | _         | 3.5 | _     | 3.8 | _    | 4.1 | ns   |

| t <sub>supll</sub>     | Clock to Data Setup - PIO Input<br>Register                       | All<br>Devices | 0.7       | _   | 0.78  | _   | 0.85 | _   | ns   |

| t <sub>HPLL</sub>      | Clock to Data Hold - PIO Input<br>Register                        | All<br>Devices | 0.8       | _   | 0.89  | _   | 0.98 | _   | ns   |

| t <sub>su_delpll</sub> | Clock to Data Setup - PIO Input<br>Register with Data Input Delay | All<br>Devices | 1.6       | _   | 1.78  | _   | 1.95 | _   | ns   |

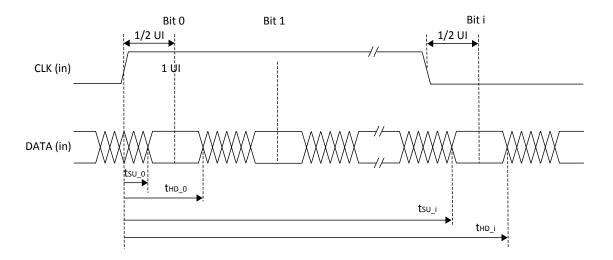

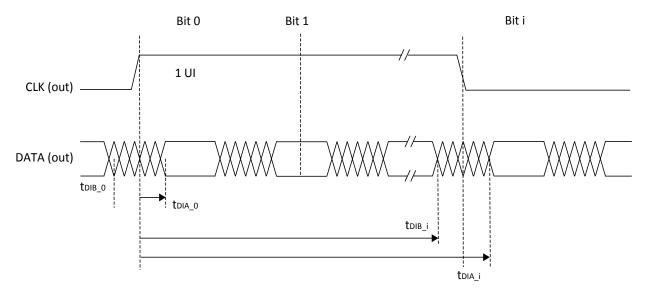

Figure 3.11. Receiver DDRX71\_RX Waveforms

Figure 3.12. Transmitter DDRX71\_TX Waveforms

### Table 3.31. PCIe (5 Gb/s) (Continued)

| Symbol                           | Description                                            | Test Conditions                      | Min               | Тур | Max              | Unit        |

|----------------------------------|--------------------------------------------------------|--------------------------------------|-------------------|-----|------------------|-------------|

| Receive <sup>1, 2</sup>          |                                                        | '                                    |                   | '   | '                |             |

| UI                               | Unit Interval                                          | —                                    | 199.94            | 200 | 200.06           | ps          |

| V <sub>RX-DIFF-PP</sub>          | Differential Rx peak-peak voltage                      | -                                    | 0.34 <sup>3</sup> | —   | 1.2              | V, p-p      |

| T <sub>RX-RJ-RMS</sub>           | Receiver random jitter tolerance<br>(RMS)              | 1.5 MHz – 100<br>MHz Random<br>noise | -                 | _   | 4.2              | ps,<br>RMS  |

| T <sub>RX-DJ</sub>               | Receiver deterministic jitter tolerance                | —                                    | —                 | —   | 88               | ps          |

| V <sub>RX-CM-AC</sub>            | Common mode noise from Rx                              | -                                    | -                 | _   |                  | mV,<br>p-p  |

| D                                | Receiver differential Return Loss,                     | 50 MHz < freq <<br>1.25 GHz          | 10                | _   | -                | dB          |

| R <sub>LRX-DIFF</sub>            | package plus silicon                                   | 1.25 GHz < freq<br>< 2.5 GHz         | 8                 | _   | -                | dB          |

| R <sub>LRX-CM</sub>              | Receiver common mode Return Loss, package plus silicon | -                                    | 6                 | _   | -                | dB          |

| Z <sub>RX-DC</sub>               | Receiver DC single ended impedance                     | -                                    | 40                | _   | 60               | Ω           |

| Z <sub>RX-HIGH-IMP-DC</sub>      | Receiver DC single ended impedance when powered down   | -                                    | 200K              | _   | -                | Ω           |

| V <sub>RX-CM-AC-P</sub>          | Rx AC peak common mode voltage                         | -                                    | _                 | _   |                  | mV,<br>peak |

| V <sub>RX-IDLE-DET-DIFF-PP</sub> | Electrical Idle Detect Threshold                       | -                                    | 65                | _   | 340 <sup>3</sup> | mv,         |

| L <sub>RX-SKEW</sub>             | Receiver lane-lane skew                                | -                                    | —                 | —   | 8                | ns          |

Notes:

1. Values are measured at 5 Gb/s.

2. Measured with external AC-coupling on the receiver.

3. Not in compliance with PCI Express standard.

# 3.27. XAUI/CPRI LV E.30 Electrical and Timing Characteristics

### 3.27.1. AC and DC Characteristics

Over recommended operating conditions.

### Table 3.33. Transmit

| Symbol                                | Description                      | Test Conditions | Min | Тур | Max  | Unit |

|---------------------------------------|----------------------------------|-----------------|-----|-----|------|------|

| T <sub>RF</sub>                       | Differential rise/fall time      | 20% to 80%      | —   | 80  | -    | ps   |

| Z <sub>TX_DIFF_DC</sub>               | Differential impedance           | —               | 80  | 100 | 120  | Ω    |

| J <sub>TX_DDJ</sub> <sup>2, 3</sup>   | Output data deterministic jitter | —               | —   | —   | 0.17 | UI   |

| J <sub>TX_TJ</sub> <sup>1, 2, 3</sup> | Total output data jitter         | —               | —   | —   | 0.35 | UI   |

Notes:

- 1. Total jitter includes both deterministic jitter and random jitter.

- 2. Jitter values are measured with each CML output AC coupled into a 50  $\Omega$  impedance (100  $\Omega$  differential impedance).

- 3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

Over recommended operating conditions.

#### Table 3.34. Receive and Jitter Tolerance

| Symbol                                | Description                                   | Test Conditions | Min  | Тур | Max  | Unit |

|---------------------------------------|-----------------------------------------------|-----------------|------|-----|------|------|

| DI                                    | Differential return loss                      | From 100 MHz    | 10   |     |      | dB   |

| RL <sub>RX_DIFF</sub>                 | Differencial return loss                      | to 3.125 GHz    | 10   | -   | -    | ив   |

| Ы                                     | Common mode return loss                       | From 100 MHz    | 6    |     |      | dB   |

| RL <sub>RX_CM</sub>                   | common mode return loss                       | to 3.125 GHz    | 0    | -   | _    | ив   |

| Z <sub>RX_DIFF</sub>                  | Differential termination resistance           | —               | 80   | 100 | 120  | Ω    |

| J <sub>RX_DJ</sub> 1, 2, 3            | Deterministic jitter tolerance (peak-to-peak) | -               | -    | -   | 0.37 | UI   |

| J <sub>RX_RJ</sub> 1, 2, 3            | Random jitter tolerance (peak-to-peak)        | —               | -    | _   | 0.18 | UI   |

| J <sub>RX_SJ</sub> <sup>1, 2, 3</sup> | Sinusoidal jitter tolerance (peak-to-peak)    | _               | _    | _   | 0.10 | UI   |

| J <sub>RX_TJ</sub> <sup>1, 2, 3</sup> | Total jitter tolerance (peak-to-peak)         | _               | _    | _   | 0.65 | UI   |

| T <sub>RX_EYE</sub>                   | Receiver eye opening                          | _               | 0.35 | _   | _    | UI   |

Notes:

1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter.

2. Jitter values are measured with each high-speed input AC coupled into a 50  $\Omega$  impedance.

3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

### 3.28. CPRI LV E.24/SGMII(2.5Gbps) Electrical and Timing Characteristics

### 3.28.1. AC and DC Characteristics

#### Table 3.35. Transmit

| Symbol                                | Description                      | Test Conditions | Min | Тур | Max  | Unit |

|---------------------------------------|----------------------------------|-----------------|-----|-----|------|------|

| T <sub>RF</sub> <sup>1</sup>          | Differential rise/fall time      | 20% to 80%      | -   | 80  | —    | ps   |

| Z <sub>TX_DIFF_DC</sub>               | Differential impedance           | —               | 80  | 100 | 120  | Ω    |

| J <sub>TX_DDJ</sub> <sup>3, 4</sup>   | Output data deterministic jitter | —               | _   | _   | 0.17 | UI   |

| J <sub>TX_TJ</sub> <sup>2, 3, 4</sup> | Total output data jitter         | _               | _   | _   | 0.35 | UI   |

Notes:

1. Rise and Fall times measured with board trace, connector and approximately 2.5 pf load.

- 2. Total jitter includes both deterministic jitter and random jitter. The random jitter is the total jitter minus the actual deterministic jitter.

- 3. Jitter values are measured with each CML output AC coupled into a 50  $\Omega$  impedance (100  $\Omega$  differential impedance).

- 4. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

#### Table 3.36. Receive and Jitter Tolerance

| Symbol                                       | Description                                   | Test Conditions         | Min  | Тур | Max  | Unit |

|----------------------------------------------|-----------------------------------------------|-------------------------|------|-----|------|------|

| RL <sub>RX_DIFF</sub>                        | Differential return loss                      | From 100 MHz to 2.5 GHz | 10   | —   | —    | dB   |

| RL <sub>RX_CM</sub>                          | Common mode return loss                       | From 100 MHz to 2.5 GHz | 6    | —   | —    | dB   |

| Z <sub>RX_DIFF</sub>                         | Differential termination resistance           | —                       | 80   | 100 | 120  | Ω    |

| J <sub>RX_DJ</sub> <sup>2, 3, 4</sup>        | Deterministic jitter tolerance (peak-to-peak) | _                       | —    | _   | 0.37 | UI   |

| J <sub>RX_RJ</sub> <sup>2, 3, 4</sup>        | Random jitter tolerance (peak-to-peak)        | -                       | —    | _   | 0.18 | UI   |

| <b>J</b> <sub>RX_SJ</sub> <sup>2, 3, 4</sup> | Sinusoidal jitter tolerance (peak-to-peak)    | _                       | —    | _   | 0.10 | UI   |

| J <sub>RX_TJ</sub> <sup>1, 2, 3, 4</sup>     | Total jitter tolerance (peak-to-peak)         | -                       | —    | _   | 0.65 | UI   |

| T <sub>RX_EYE</sub>                          | Receiver eye opening                          | _                       | 0.35 | _   | —    | UI   |

Notes:

- 1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter.

- 2. Jitter values are measured with each high-speed input AC coupled into a 50  $\Omega$  impedance.

- 3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 4. Jitter tolerance, Differential Input Sensitivity and Receiver Eye Opening parameters are characterized when Full Rx Equalization is enabled.

# 3.29. Gigabit Ethernet/SGMII(1.25Gbps)/CPRI LV E.12 Electrical and Timing Characteristics

### 3.29.1. AC and DC Characteristics

#### Table 3.37. Transmit

| Symbol                                | Description                      | Test Conditions | Min | Тур | Max  | Unit |

|---------------------------------------|----------------------------------|-----------------|-----|-----|------|------|

| T <sub>RF</sub>                       | Differential rise/fall time      | 20% to 80%      | -   | 80  | —    | ps   |

| Z <sub>TX_DIFF_DC</sub>               | Differential impedance           | _               | 80  | 100 | 120  | Ω    |

| J <sub>TX_DDJ</sub> <sup>2, 3</sup>   | Output data deterministic jitter | —               | -   | -   | 0.10 | UI   |

| J <sub>TX_TJ</sub> <sup>1, 2, 3</sup> | Total output data jitter         | —               | _   | _   | 0.24 | UI   |

Notes:

1. Total jitter includes both deterministic jitter and random jitter. The random jitter is the total jitter minus the actual deterministic jitter.

2. Jitter values are measured with each CML output AC coupled into a 50  $\Omega$  impedance (100  $\Omega$  differential impedance).

3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

#### Table 3.38. Receive and Jitter Tolerance

| Symbol                                   | Description                                   | Test Conditions          | Min  | Тур | Max  | Unit |

|------------------------------------------|-----------------------------------------------|--------------------------|------|-----|------|------|

| RL <sub>RX_DIFF</sub>                    | Differential return loss                      | From 100 MHz to 1.25 GHz | 10   | -   | —    | dB   |

| RL <sub>RX_CM</sub>                      | Common mode return loss                       | From 100 MHz to 1.25 GHz | 6    | -   | —    | dB   |

| Z <sub>RX_DIFF</sub>                     | Differential termination resistance           | -                        | 80   | 100 | 120  | Ω    |

| J <sub>RX_DJ</sub> <sup>1, 2, 3, 4</sup> | Deterministic jitter tolerance (peak-to-peak) | -                        | -    | _   | 0.34 | UI   |

| J <sub>RX_RJ</sub> <sup>1, 2, 3, 4</sup> | Random jitter tolerance (peak-to-peak)        | -                        | -    | -   | 0.26 | UI   |

| J <sub>RX_SJ</sub> <sup>1, 2, 3, 4</sup> | Sinusoidal jitter tolerance (peak-to-peak)    | -                        | -    | _   | 0.11 | UI   |

| J <sub>RX_TJ</sub> <sup>1, 2, 3, 4</sup> | Total jitter tolerance (peak-to-peak)         | —                        | _    | _   | 0.71 | UI   |

| T <sub>RX_EYE</sub>                      | Receiver eye opening                          | —                        | 0.29 | -   | _    | UI   |

Notes:

1. Total jitter includes deterministic jitter, random jitter and sinusoidal jitter.

- 2. Jitter values are measured with each high-speed input AC coupled into a 50 Ω impedance.

- 3. Jitter and skew are specified between differential crossings of the 50% threshold of the reference signal.

- 4. Jitter tolerance, Differential Input Sensitivity and Receiver Eye Opening parameters are characterized when Full Rx Equalization is enabled.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

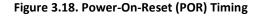

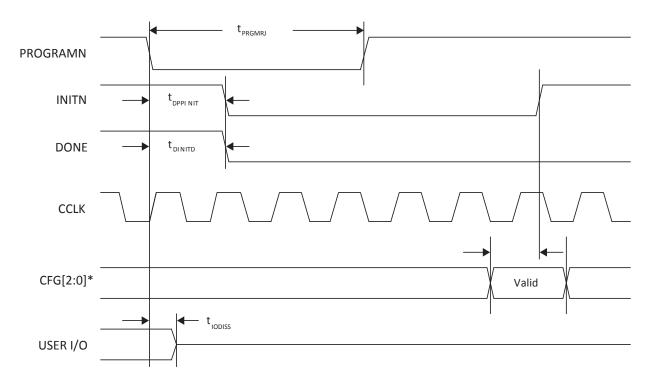

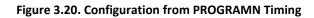

# 3.31. sysCONFIG Port Timing Specifications

Over recommended operating conditions.

### Table 3.42. ECP5/ECP5-5G sysCONFIG Port Timing Specifications

| Symbol                      | Parameter                                                                                                                                |                          | Min | Max | Unit |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----|-----|------|

| POR, Confi                  | guration Initialization, and Wakeup                                                                                                      | I                        | 1   | 1   | 1    |

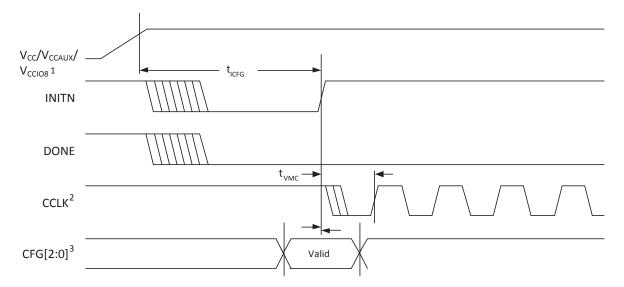

| t <sub>ICFG</sub>           | Time from the Application of $V_{CC, V}$ V <sub>CCAUX</sub> or V <sub>CCI08</sub><br>(whichever is the last) to the rising edge of INITN | -                        | _   | 33  | ms   |

| t <sub>VMC</sub>            | Time from $t_{ICFG}$ to the valid Master CCLK                                                                                            | _                        | _   | 5   | us   |

| t <sub>cz</sub>             | CCLK from Active to High-Z                                                                                                               | _                        | _   | 300 | ns   |

| Master CCI                  | LK                                                                                                                                       | T                        | 1   | 1   | 1    |

| f <sub>MCLK</sub>           | Frequency                                                                                                                                | All selected frequencies | -20 | 20  | %    |

| t <sub>MCLK-DC</sub>        | Duty Cycle                                                                                                                               | All selected frequencies | 40  | 60  | %    |

| All Configu                 | ration Modes                                                                                                                             |                          |     |     |      |

| t <sub>PRGM</sub>           | PROGRAMN LOW pulse accepted                                                                                                              | _                        | 110 | _   | ns   |

| t <sub>PRGMRJ</sub>         | PROGRAMN LOW pulse rejected                                                                                                              | _                        | _   | 50  | ns   |

| t <sub>INITL</sub>          | INITN LOW time                                                                                                                           | _                        | _   | 55  | ns   |

| t <sub>dppint</sub>         | PROGRAMN LOW to INITN LOW                                                                                                                | _                        | _   | 70  | ns   |

| <b>t</b> <sub>DPPDONE</sub> | PROGRAMN LOW to DONE LOW                                                                                                                 | _                        | _   | 80  | ns   |

| t <sub>IODISS</sub>         | PROGRAMN LOW to I/O Disabled                                                                                                             | _                        | _   | 150 | ns   |

| Slave SPI                   |                                                                                                                                          | T                        | 1   |     | 1    |

| f <sub>CCLK</sub>           | CCLK input clock frequency                                                                                                               | _                        | _   | 60  | MHz  |

| t <sub>CCLKH</sub>          | CCLK input clock pulsewidth HIGH                                                                                                         | _                        | 6   | _   | ns   |

| t <sub>cclkl</sub>          | CCLK input clock pulsewidth LOW                                                                                                          | _                        | 6   | _   | ns   |

| t <sub>stsu</sub>           | CCLK setup time                                                                                                                          | _                        | 1   | _   | ns   |

| t <sub>sth</sub>            | CCLK hold time                                                                                                                           | _                        | 1   | _   | ns   |

| t <sub>sтсо</sub>           | CCLK falling edge to valid output                                                                                                        | _                        | _   | 10  | ns   |

| t <sub>stoz</sub>           | CCLK falling edge to valid disable                                                                                                       | _                        | _   | 10  | ns   |

| t <sub>stov</sub>           | CCLK falling edge to valid enable                                                                                                        | _                        | _   | 10  | ns   |

| t <sub>scs</sub>            | Chip Select HIGH time                                                                                                                    | _                        | 25  | _   | ns   |

| t <sub>scss</sub>           | Chip Select setup time                                                                                                                   | _                        | 3   | _   | ns   |

| t <sub>scsн</sub>           | Chip Select hold time                                                                                                                    | _                        | 3   | _   | ns   |

| Master SPI                  |                                                                                                                                          | ,                        | ,   |     |      |

| f <sub>CCLK</sub>           | Max selected CCLK output frequency                                                                                                       | _                        | _   | 62  | MHz  |

| t <sub>cclкн</sub>          | CCLK output clock pulse width HIGH                                                                                                       | _                        | 3.5 | _   | ns   |

| t <sub>CCLKL</sub>          | CCLK output clock pulse width LOW                                                                                                        | _                        | 3.5 | _   | ns   |

| t <sub>sтsu</sub>           | CCLK setup time                                                                                                                          | _                        | 5   | _   | ns   |

| t <sub>sтн</sub>            | CCLK hold time                                                                                                                           | _                        | 1   | _   | ns   |

| t <sub>CSSPI</sub>          | INITN HIGH to Chip Select LOW                                                                                                            | _                        | 100 | 200 | ns   |

| t <sub>CFGX</sub>           | INITN HIGH to first CCLK edge                                                                                                            | _                        | _   | 150 | ns   |

| Slave Seria                 | l l                                                                                                                                      |                          |     |     | 1    |

| f <sub>CCLK</sub>           | CCLK input clock frequency                                                                                                               | _                        | _   | 66  | MHz  |

| t <sub>sscн</sub>           | CCLK input clock pulse width HIGH                                                                                                        | _                        | 5   | _   | ns   |

| t <sub>SSCL</sub>           | CCLK input clock pulse width LOW                                                                                                         | _                        | 5   | _   | ns   |

| t <sub>SUSCDI</sub>         | CCLK setup time                                                                                                                          | _                        | 0.5 | _   | ns   |

| t <sub>HSCDI</sub>          | CCLK hold time                                                                                                                           | _                        | 1.5 | _   | ns   |

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

- 1. Time taken from  $V_{CC}$ ,  $V_{CCAUX}$  or  $V_{CCIO8}$ , whichever is the last to cross the POR trip point.

- 2. Device is in a Master Mode (SPI, SPIm).

- 3. The CFG pins are normally static (hardwired).

Figure 3.19. sysCONFIG Port Timing

\*The CFG pins are normally static (hardwired).

| Signal Name                          | I/O      | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL, DLL and Clock Functions (Contin | nued)    |                                                                                                                                                                                                                                                                                                                                                                                             |

| [L/R]DQS[group_num]                  | I/O      | DQS input/output pads: T (top), R (right), group_num = ball number associated with DQS[T] pin.                                                                                                                                                                                                                                                                                              |

| [T/R]]DQ[group_num]                  | I/O      | DQ input/output pads: T (top), R (right), group_ num = ball number associated with DQS[T] pin.                                                                                                                                                                                                                                                                                              |

| Test and Programming (Dedicated F    | Pins)    |                                                                                                                                                                                                                                                                                                                                                                                             |

| TMS                                  | I        | Test Mode Select input, used to control the 1149.1 state machine. Pull-up is enabled during configuration. This is a dedicated input pin.                                                                                                                                                                                                                                                   |

| тск                                  | I        | Test Clock input pin, used to clock the 1149.1 state machine. No pull-up enabled.<br>This is a dedicated input pin.                                                                                                                                                                                                                                                                         |

| TDI                                  | I        | Test Data in pin. Used to load data into device using 1149.1 state machine. After power-up, this TAP port can be activated for configuration by sending appropriate command. (Note: once a configuration port is selected it is locked. Another configuration port cannot be selected until the power-up sequence). Pull-up is enabled during configuration. This is a dedicated input pin. |

| TDO                                  | 0        | Output pin. Test Data Out pin used to shift data out of a device using 1149.1.<br>This is a dedicated output pin.                                                                                                                                                                                                                                                                           |

| Configuration Pads (Used during sys  | sCONFIG) |                                                                                                                                                                                                                                                                                                                                                                                             |

| CFG[2:0]                             | I        | Mode pins used to specify configuration mode values latched on rising edge of INITN. During configuration, a pull-up is enabled.<br>These are dedicated pins.                                                                                                                                                                                                                               |

| INITN                                | I/O      | Open Drain pin. Indicates the FPGA is ready to be configured. During configuration, a pull-up is enabled.<br>This is a dedicated pin.                                                                                                                                                                                                                                                       |

| PROGRAMN                             | 1        | Initiates configuration sequence when asserted low. This pin always has an active pull-up.<br>This is a dedicated pin.                                                                                                                                                                                                                                                                      |

| DONE                                 | I/O      | Open Drain pin. Indicates that the configuration sequence is complete, and the startup sequence is in progress.<br>This is a dedicated pin.                                                                                                                                                                                                                                                 |

| ССГК                                 | I/O      | Input Configuration Clock for configuring an FPGA in Slave SPI, Serial, and CPU modes. Output Configuration Clock for configuring an FPGA in Master configuration modes (Master SPI, Master Serial).<br>This is a dedicated pin.                                                                                                                                                            |

| HOLDN/DI/BUSY/CSSPIN/CEN             | I/O      | Parallel configuration mode busy indicator. SPI/SPIm mode data output.<br>This is a shared I/O pin. This is a shared I/O pin. When not in configuration, it can<br>be used as general purpose I/O pin.                                                                                                                                                                                      |

| CSN/SN                               | ı/o      | Parallel configuration mode active-low chip select. Slave SPI chip select. This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O pin.                                                                                                                                                                                                                  |

| CS1N                                 | I        | Parallel configuration mode active-low chip select.<br>This is a shared I/O pin. When not in configuration, it can be used as general<br>purpose I/O pin.                                                                                                                                                                                                                                   |

| WRITEN                               | I        | Write enable for parallel configuration modes.<br>This is a shared I/O pin. When not in configuration, it can be used as general<br>purpose I/O pin.                                                                                                                                                                                                                                        |

| DOUT/CSON                            | о        | Serial data output. Chip select output. SPI/SPIm mode chip select. This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O                                                                                                                                                                                                                               |

| D0/MOSI/IO0                          | I/O      | Parallel configuration I/O. Open drain during configuration. When in SPI modes,<br>it is an output in Master mode, and input in Slave mode.<br>This is a shared I/O pin. When not in configuration, it can be used as general<br>purpose I/O pin.                                                                                                                                           |

<sup>© 2014-2018</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Signal Name                            | I/O       | Description                                                                                                                                                                                                                                                                                        |

|----------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration Pads (Used during sysCON | FIG) (Con | tinued)                                                                                                                                                                                                                                                                                            |

| D1/MISO/IO1                            | I/O       | Parallel configuration I/O. Open drain during configuration. When in SPI modes, it is an input in Master mode, and output in Slave mode.<br>This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O pin.                                                        |

| D2/IO2                                 | I/O       | Parallel configuration I/O. Open drain during configuration.<br>This is a shared I/O pin. When not in configuration, it can be used as general<br>purpose I/O pin.                                                                                                                                 |

| D3/IO3                                 | I/O       | Parallel configuration I/O. Open drain during configuration.<br>This is a shared I/O pin. When not in configuration, it can be used as general<br>purpose I/O pin.                                                                                                                                 |

| D4/IO4                                 | I/O       | Parallel configuration I/O. Open drain during configuration. This is a shared I/ O pin. When not in configuration, it can be used as general purpose I/O pin.                                                                                                                                      |

| D5/IO5                                 | I/O       | Parallel configuration I/O. Open drain during configuration. This is a shared I/ O pin. When not in configuration, it can be used as general purpose I/O pin.                                                                                                                                      |

| D6/IO6                                 | I/O       | Parallel configuration I/O. Open drain during configuration. When in SPI modes, it is an output in Master mode, and input in Slave mode.<br>This is a shared I/O pin. When not in configuration, it can be used as general purpose I/O pin.                                                        |

| D7/I07                                 | I/O       | Parallel configuration I/O. Open drain during configuration. When in SPI<br>modes, it is an output in Master mode, and input in Slave mode.<br>This is a shared I/O pin. When not in configuration, it can be used as general<br>purpose I/O pin                                                   |

| SERDES Function                        |           |                                                                                                                                                                                                                                                                                                    |

| VCCAx                                  | -         | SERDES, transmit, receive, PLL and reference clock buffer power supply for<br>SERDES Dual x. All VCCA supply pins must always be powered to the<br>recommended operating voltage range. If no SERDES channels are used,<br>connect VCCA to VCC. VCCAx = 1.1 V for ECP5, VCCAx = 1.2 V for ECP5-5G. |

| VCCAUXAx                               | _         | SERDES Aux Power Supply pin for SERDES Dual x. VCCAUXAx = 2.5 V.                                                                                                                                                                                                                                   |

| HDRX[P/N]_D[dual_num]CH[chan_num]      | Ι         | High-speed SERDES inputs, P = Positive, N = Negative, dual_num = [0, 1],<br>chan_num = [0, 1]. These are dedicated SERDES input pins.                                                                                                                                                              |

| HDTX[P/N]_D[dual_num]CH[chan_num]      | 0         | High-speed SERDES outputs, P = Positive, N = Negative, dual_num = [0, 1],<br>chan_num = [0, 1]. These are dedicated SERDES output pins.                                                                                                                                                            |

| REFCLK[P/N]_D[dual_num]                | Ι         | SERDES Reference Clock inputs, P = Positive, N = Negative, dual_num = [0, 1].<br>These are dedicated SERDES input pins.                                                                                                                                                                            |

| VCCHRX_D[dual_num]CH[chan_num]         | _         | SERDES High-Speed Inputs Termination Voltage Supplies, dual_num = [0, 1],<br>chan_num = [0, 1]. These pins should be powered to 1.1 V on ECP5, or<br>1.2 V on ECP5-5G.                                                                                                                             |

| VCCHTX_D[dual_num]CH[chan_num]         | _         | SERDES High-Speed Outputs Buffer Voltage Supplies, dual_num = [0, 1],<br>chan_num = [0, 1]. These pins should be powered to 1.1 V on ECP5, or 1.2 V<br>on ECP5-5G.                                                                                                                                 |

Notes:

1. When placing switching I/Os around these critical pins that are designed to supply the device with the proper reference or supply voltage, care must be given.

2. These pins are dedicated inputs or can be used as general purpose I/O.

3. m defines the associated channel in the quad.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

### 4.2. PICs and DDR Data (DQ) Pins Associated with the DDR Strobe (DQS) Pin

| PICs Associated with DQS Strobe | PIO within PIC                        | DDR Strobe (DQS) and Data (DQ) Pins |

|---------------------------------|---------------------------------------|-------------------------------------|

| F                               | or Left and Right Edges of the Device | Only                                |

|                                 | А                                     | DQ                                  |

|                                 | В                                     | DQ                                  |

| P[L/R] [n-6]                    | С                                     | DQ                                  |

|                                 | D                                     | DQ                                  |

|                                 | А                                     | DQ                                  |

|                                 | В                                     | DQ                                  |

| P[L/R] [n-3]                    | С                                     | DQ                                  |

|                                 | D                                     | DQ                                  |

|                                 | А                                     | DQS (P)                             |

|                                 | В                                     | DQS (N)                             |

| P[L/R] [n]                      | С                                     | DQ                                  |

|                                 | D                                     | DQ                                  |

|                                 | А                                     | DQ                                  |

|                                 | В                                     | DQ                                  |

| P[L/R] [n+3]                    | С                                     | DQ                                  |

|                                 | D                                     | DQ                                  |

**Note**: "n" is a row PIC number.

# 4.3. **Pin Information Summary**

### 4.3.1. **LFE5UM/LFE5UM5G**

| Pin Information Summary     |        |              | 5UM/<br>M5G-25 | LFE5UM/LFE5UM5G-45 |             |              | LFE5UM/LFE5UM5G-85 |             |              |              |

|-----------------------------|--------|--------------|----------------|--------------------|-------------|--------------|--------------------|-------------|--------------|--------------|

| Pin Type                    |        | 285<br>csfBG | 381<br>caBGA   | 285<br>csfBGA      | 381<br>caBG | 554<br>caBGA | 285<br>csfBGA      | 381<br>caBG | 554<br>caBGA | 756<br>caBGA |

|                             | Bank 0 | 6            | 24             | 6                  | 27          | 32           | 6                  | 27          | 32           | 56           |

|                             | Bank 1 | 6            | 32             | 6                  | 33          | 40           | 6                  | 33          | 40           | 48           |

|                             | Bank 2 | 21           | 32             | 21                 | 32          | 32           | 21                 | 34          | 32           | 48           |

| General Purpose             | Bank 3 | 28           | 32             | 28                 | 33          | 48           | 28                 | 33          | 48           | 64           |

| Inputs/Outputs per Bank     | Bank 4 | 0            | 0              | 0                  | 0           | 0            | 0                  | 0           | 14           | 24           |

|                             | Bank 6 | 26           | 32             | 26                 | 33          | 48           | 26                 | 33          | 48           | 64           |

|                             | Bank 7 | 18           | 32             | 18                 | 32          | 32           | 18                 | 32          | 32           | 48           |

|                             | Bank 8 | 13           | 13             | 13                 | 13          | 13           | 13                 | 13          | 13           | 13           |

| Total Single-Ended User I/O |        | 118          | 197            | 118                | 203         | 245          | 118                | 205         | 259          | 365          |

| VCC                         |        | 13           | 20             | 13                 | 20          | 24           | 13                 | 20          | 24           | 36           |

| VCCAUX (Core)               |        | 3            | 4              | 3                  | 4           | 9            | 3                  | 4           | 9            | 8            |

|                             | Bank O | 1            | 2              | 1                  | 2           | 3            | 1                  | 2           | 3            | 4            |

|                             | Bank 1 | 1            | 2              | 1                  | 2           | 3            | 1                  | 2           | 3            | 4            |

|                             | Bank 2 | 2            | 3              | 2                  | 3           | 4            | 2                  | 3           | 4            | 4            |

| VICEIO                      | Bank 3 | 2            | 3              | 2                  | 3           | 3            | 2                  | 3           | 3            | 4            |

| VCCIO                       | Bank 4 | 0            | 0              | 0                  | 0           | 0            | 0                  | 0           | 2            | 2            |

|                             | Bank 6 | 2            | 3              | 2                  | 3           | 4            | 2                  | 3           | 4            | 4            |

|                             | Bank 7 | 2            | 3              | 2                  | 3           | 3            | 2                  | 3           | 3            | 4            |

|                             | Bank 8 | 2            | 2              | 2                  | 2           | 2            | 2                  | 2           | 2            | 2            |

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

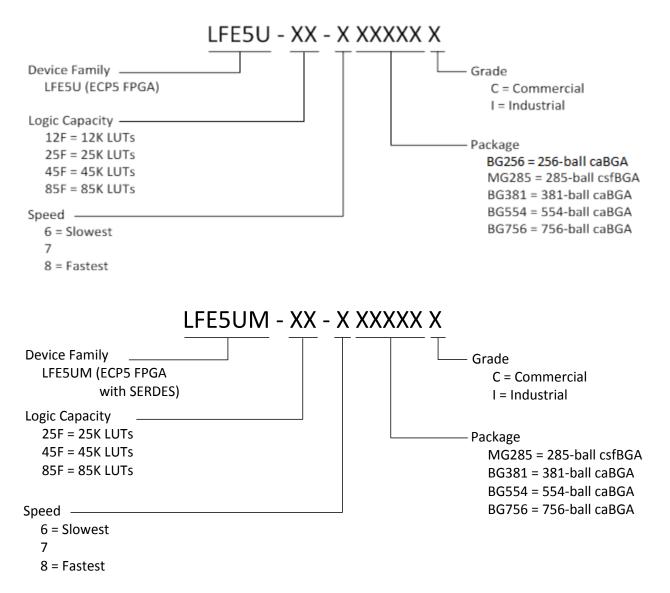

# 5. Ordering Information

### 5.1. ECP5/ECP5-5G Part Number Description