# E: Lattice Semiconductor Corporation - LFE5UM-85F-7BG554I Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                        |

|--------------------------------|-------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 21000                                                                         |

| Number of Logic Elements/Cells | 84000                                                                         |

| Total RAM Bits                 | 3833856                                                                       |

| Number of I/O                  | 259                                                                           |

| Number of Gates                | -                                                                             |

| Voltage - Supply               | 1.045V ~ 1.155V                                                               |

| Mounting Type                  | Surface Mount                                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                            |

| Package / Case                 | 554-FBGA                                                                      |

| Supplier Device Package        | 554-CABGA (23x23)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe5um-85f-7bg554i |

|                                |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Figures

| Figure 2.1. Simplified Block Diagram, LFE5UM/LFE5UM5G-85 Device (Top Level)    | 13 |

|--------------------------------------------------------------------------------|----|

| Figure 2.2. PFU Diagram                                                        | 14 |

| Figure 2.3. Slice Diagram                                                      | 15 |

| Figure 2.4. Connectivity Supporting LUT5, LUT6, LUT7, and LUT8                 | 16 |

| Figure 2.5. General Purpose PLL Diagram                                        | 18 |

| Figure 2.6. LFE5UM/LFE5UM5G-85 Clocking                                        | 20 |

| Figure 2.7. DCS Waveforms                                                      | 21 |

| Figure 2.8. Edge Clock Sources per Bank                                        | 22 |

| Figure 2.9. ECP5/ECP5-5G Clock Divider Sources                                 | 22 |

| Figure 2.10. DDRDLL Functional Diagram                                         |    |

| Figure 2.11. ECP5/ECP5-5G DLL Top Level View (For LFE-45 and LFE-85)           |    |

| Figure 2.12. Memory Core Reset                                                 |    |

| Figure 2.13. Comparison of General DSP and ECP5/ECP5-5G Approaches             | 27 |

| Figure 2.14. Simplified sysDSP Slice Block Diagram                             | 28 |

| Figure 2.15. Detailed sysDSP Slice Diagram                                     |    |

| Figure 2.16. Group of Four Programmable I/O Cells on Left/Right Sides          |    |

| Figure 2.17. Input Register Block for PIO on Top Side of the Device            |    |

| Figure 2.18. Input Register Block for PIO on Left and Right Side of the Device |    |

| Figure 2.19. Output Register Block on Top Side                                 |    |

| Figure 2.20. Output Register Block on Left and Right Sides                     |    |

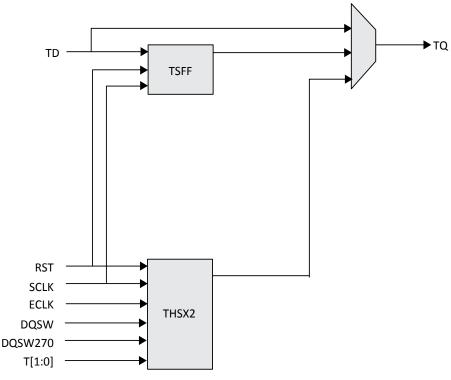

| Figure 2.21. Tristate Register Block on Top Side                               |    |

| Figure 2.22. Tristate Register Block on Left and Right Sides                   |    |

| Figure 2.23. DQS Grouping on the Left and Right Edges                          |    |

| Figure 2.24. DQS Control and Delay Block (DQSBUF)                              |    |

| Figure 2.25. ECP5/ECP5-5G Device Family Banks                                  |    |

| Figure 2.26. On-Chip Termination                                               |    |

| Figure 2.27. SERDES/PCS Duals (LFE5UM/LFE5UM5G-85)                             |    |

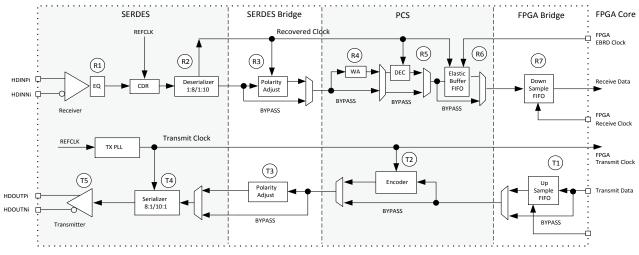

| Figure 2.28. Simplified Channel Block Diagram for SERDES/PCS Block             |    |

| Figure 3.1. LVDS25E Output Termination Example                                 |    |

| Figure 3.2. BLVDS25 Multi-point Output Example                                 |    |

| Figure 3.3. Differential LVPECL33                                              |    |

| Figure 3.4. MLVDS25 (Multipoint Low Voltage Differential Signaling)            |    |

| Figure 3.5. SLVS Interface                                                     |    |

| Figure 3.6. Receiver RX.CLK.Centered Waveforms                                 |    |

| Figure 3.7. Receiver RX.CLK.Aligned and DDR Memory Input Waveforms             |    |

| Figure 3.8. Transmit TX.CLK.Centered and DDR Memory Output Waveforms           |    |

| Figure 3.9. Transmit TX.CLK.Aligned Waveforms                                  |    |

| Figure 3.10. DDRX71 Video Timing Waveforms                                     |    |

| Figure 3.11. Receiver DDRX71 RX Waveforms                                      |    |

| Figure 3.12. Transmitter DDRX71_TX Waveforms                                   |    |

| Figure 3.13. Transmitter and Receiver Latency Block Diagram                    |    |

| Figure 3.14. SERDES External Reference Clock Waveforms                         |    |

| Figure 3.15. sysCONFIG Parallel Port Read Cycle                                |    |

| Figure 3.16. sysCONFIG Parallel Port Write Cycle                               |    |

| Figure 3.17. sysCONFIG Slave Serial Port Timing                                |    |

| Figure 3.18. Power-On-Reset (POR) Timing                                       |    |

| Figure 3.19. sysCONFIG Port Timing                                             |    |

| Figure 3.20. Configuration from PROGRAMN Timing                                |    |

| Figure 3.21. Wake-Up Timing                                                    |    |

| Figure 3.22. Master SPI Configuration Waveforms                                |    |

| Figure 3.23. JTAG Port Timing Waveforms                                        |    |

| Figure 3.24. Output Test Load, LVTTL and LVCMOS Standards                      |    |

| J ,                                                                            |    |

<sup>© 2014-2018</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Table 3.36. Receive and Jitter Tolerance                                |    |

|-------------------------------------------------------------------------|----|

| Table 3.37. Transmit                                                    |    |

| Table 3.38. Receive and Jitter Tolerance                                |    |

| Table 3.39. Transmit                                                    | 82 |

| Table 3.40. Receive                                                     | 82 |

| Table 3.41. Reference Clock                                             | 82 |

| Table 3.42. ECP5/ECP5-5G sysCONFIG Port Timing Specifications           | 83 |

| Table 3.43. JTAG Port Timing Specifications                             |    |

| Table 3.44. Test Fixture Required Components, Non-Terminated Interfaces |    |

|                                                                         |    |

### 2.2.2. Modes of Operation

Slices 0-2 have up to four potential modes of operation: Logic, Ripple, RAM and ROM. Slice 3 is not needed for RAM mode, it can be used in Logic, Ripple, or ROM modes.

#### Logic Mode

In this mode, the LUTs in each slice are configured as 4-input combinatorial lookup tables. A LUT4 can have 16 possible input combinations. Any four input logic functions can be generated by programming this lookup table. Since there are two LUT4s per slice, a LUT5 can be constructed within one slice. Larger look-up tables such as LUT6, LUT7 and LUT8 can be constructed by concatenating other slices. Note that LUT8 requires more than four slices.

#### **Ripple Mode**

Ripple mode supports the efficient implementation of small arithmetic functions. In ripple mode, the following functions can be implemented by each slice:

- x Addition 2-bit

- x Subtraction 2-bit

- x Add/Subtract 2-bit using dynamic control

- x Up counter 2-bit

- x Down counter 2-bit

- x Up/Down counter with asynchronous clear

- x Up/Down counter with preload (sync)

- x Ripple mode multiplier building block

- x Multiplier support

- x Comparator functions of A and B inputs

- x POE rššZ00⊊0E (µrŏ)}

- x v}rš∖µrõi}

- x o ¶ěyZn}v0E∖µně}

Ripple Mode includes an optional configuration that performs arithmetic using fast carry chain methods. In this configuration (also referred to as CCU2 mode) two additional signals, Carry Generate and Carry Propagate, are generated on a per slice basis to allow fast arithmetic functions to be constructed by concatenating Slices.

#### **RAM Mode**

In this mode, a 16x4-bit distributed single port RAM (SPR) can be constructed in one PFU using each LUT block in Slice 0 and Slice 1 as a 16 x 2-bit memory in each slice. Slice 2 is used to provide memory address and control signals. A 16 x 2-bit pseudo dual port RAM (PDPR) memory is created in one PFU by using one Slice as the read-write port and the other companion slice as the read-only port. The slice with the read-write port updates the SRAM data contents in both slices at the same write cycle.

ECP5/ECP5-5G devices support distributed memory initialization.

The Lattice design tools support the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2.3 lists the number of slices required to implement different distributed RAM primitives. For more information about using RAM in ECP5/ECP5-5G devices, refer to ECP5 and ECP5-5G Memory Usage Guide (TN1264).

#### Table 2.3. Number of Slices Required to Implement Distributed RAM

|                  | SPR 16 X 4 | PDPR 16 X 4 |

|------------------|------------|-------------|

| Number of slices | 3          | 6           |

|                  |            |             |

Note: SPR = Single Port RAM, PDPR = Pseudo Dual Port RAM

#### **ROM Mode**

ROM mode uses the LUT logic; hence, Slices 0 through 3 can be used in ROM mode. Preloading is accomplished through the programming interface during PFU configuration.

For more information, refer to ECP5 and ECP5-5G Memory Usage Guide (TN1264).

### DDRDLL

Every DDRDLL (master DLL block) can generate phase shift code representing the amount of delay in a delay block that corresponding to 90° phase of the reference clock input. The reference clock can be either from PLL, or input pin. This code is used in the DQSBUF block that controls a set of DQS pin groups to interface with DDR memory (slave DLL). There are two DDRDLLs that supply two sets of codes (for two different reference clock frequencies) to each side of the I/Os (at each of the corners). The DQSBUF uses this code to controls the DQS input of the DDR memory to 90° shift to clock DQs at the center of the data eye for DDR memory interface.

The code is also sent to another slave DLL, DLLDEL, that takes a clock input and generates a 90° shift clock output to drive the clocking structure. This is useful to interface edge-aligned Generic DDR, where 90° clocking needs to be created. Figure 2.10 shows DDRDLL functional diagram.

#### Figure 2.10. DDRDLL Functional Diagram

#### Table 2.5. DDRDLL Ports List

| Port Name   | Туре   | Description                                                                                                                                                 |

|-------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK         | Input  | Reference clock input to the DDRDLL. Should run at the same frequency as the clock to the delay code.                                                       |

| RST         | Input  | Reset Input to the DDRDLL.                                                                                                                                  |

| UDDCNTLN    | Input  | Update Control to update the delay code. The code is the DCNTL[7:0] outputs. These outputs are updated when the UDDCNTLN signal is LOW.                     |

| FREEZE      | Input  | FREEZE goes high and, without a glitch, turns off the DLL internal clock and the ring oscillator output clock. When FREEZE goes low, it turns them back on. |

| DDRDEL      | Output | The delay codes from the DDRDLL to be used in DQSBUF or DLLDEL.                                                                                             |

| LOCK        | Output | Lock output to indicate the DDRDLL has valid delay output.                                                                                                  |

| DCNTL [7:0] | Output | The delay codes from the DDRDLL available for the user IP.                                                                                                  |

There are four identical DDRDLLs, one in each of the four corners in LFE5-85 and LFE5-45 devices, and two DDRDLLs in both LFE5-25 & LFE5-12 devices in the upper two corners. Each DDRDLL can generate delay code based on the reference frequency. The slave DLL (DQSBUF and DLLDEL) use the code to delay the signal, to create the phase shifted signal used for either DDR memory, to create 90° shift clock. Figure 2.11 shows the DDRDLL and the slave DLLs on the top level view.

| Name    | Туре   | Description                                                         |

|---------|--------|---------------------------------------------------------------------|

| TD      | Input  | Tristate Input to Tristate SDR Register                             |

| RST     | Input  | Reset to the Tristate Block                                         |

| TD[1:0] | Input  | Tristate input to TSHX2 function                                    |

| SCLK    | Input  | Slow Speed System Clock                                             |

| ECLK    | Input  | High Speed Edge Clock                                               |

| DQSW    | Input  | Clock from DQS control Block used to generate DDR memory DQS output |

| DQSW270 | Input  | Clock from DQS control Block used to generate DDR memory DQ output  |

| TQ      | Output | Output of the Tristate block                                        |

### 2.13. DDR Memory Support

#### 2.13.1. DQS Grouping for DDR Memory

Certain PICs have additional circuitry to allow the implementation of high-speed source synchronous and DDR2, DDR3, LPDDR2 or LPDDR3 memory interfaces. The support varies by the edge of the device as detailed below.

The left and right sides of the PIC have fully functional elements supporting DDR2, DDR3, LPDDR2 or LPDDR3 memory interfaces. Every 16 PIOs on the left and right sides are grouped into one DQS group, as shown in Figure 2.23 on page 36. Within each DQS group, there are two pre-placed pins for DQS and DQS# signals. The rest of the pins in the DQS group can be used as DQ signals and DM signal. The number of pins in each DQS group bonded out is package dependent. DQS groups with less than 11 pins bonded out can only be used for LPDDR2/3 Command/ Address busses. In DQS groups with more than 11 pins bonded out, up to two pre-defined pins are assigned to be used as "virtual" VCCIO, by driving these pins to HIGH, with the user connecting these pins to VCCIO power supply. These connections create "soft" connections to V<sub>CCIO</sub> thru these output pins, and make better connections on VCCIO to help to reduce SSO noise. For details, refer to ECP5 and ECP5-5G High-Speed I/O Interface (TN1265).

|            | PIO A          | sysIO Buffer | Pad A (T)      |

|------------|----------------|--------------|----------------|

| •          | PIO B          | sysIO Buffer | Pad B (C)      |

| <b>↓</b>   | PIO C          | sysIO Buffer | Pad C          |

| <b>↓</b>   | PIO D          | sysIO Buffer | Pad D          |

| <b>↓</b>   | PIO A          | sysIO Buffer | Pad A (T)      |

| <b>↓</b>   | PIO B          | sysIO Buffer | Pad B (C)      |

| <b>↓</b>   | PIO C          | sysIO Buffer | Pad C          |

| <b>↓</b>   | PIO D          | sysIO Buffer | Pad D          |

|            | DQSBUF         | <br>Delay    |                |

| <b>↓</b>   | PIO A          | sysIO Buffer | Pad A (T)      |

| <b>↓</b>   | PIO B          | sysIO Buffer | Pad B (C)      |

| <b>↓</b>   | PIO C          | sysIO Buffer | Pad C          |

| <b>↓</b>   | PIO D          | sysIO Buffer | Pad D          |

| <b>↓</b> → | PIO A          | syslO Buffer | Pad A (T)      |

| <b>↓</b>   | PIO B          | sysIO Buffer | Pad B (C)      |

|            |                |              |                |

| <b>♦</b> → | PIO C          | sysIO Buffer | Pad C          |

| •          | PIO C<br>PIO D | sysIO Buffer | Pad C<br>Pad D |

Figure 2.23. DQS Grouping on the Left and Right Edges

#### 2.13.2. DLL Calibrated DQS Delay and Control Block (DQSBUF)

To support DDR memory interfaces (DDR2/3, LPDDR2/3), the DQS strobe signal from the memory must be used to capture the data (DQ) in the PIC registers during memory reads. This signal is output from the DDR memory device aligned to data transitions and must be time shifted before it can be used to capture data in the PIC. This time shifted is achieved by using DQSDEL programmable delay line in the DQS Delay Block (DQS read circuit). The DQSDEL is implemented as a slave delay line and works in conjunction with a master DDRDLL.

This block also includes slave delay line to generate delayed clocks used in the write side to generate DQ and DQS with correct phases within one DQS group. There is a third delay line inside this block used to provide write leveling feature for DDR write if needed.

Each of the read and write side delays can be dynamically shifted using margin control signals that can be controlled by the core logic.

FIFO Control Block shown in Figure 2.24 generates the Read and Write Pointers for the FIFO block inside the Input Register Block. These pointers are generated to control the DQS to ECLK domain crossing using the FIFO module.

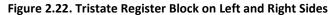

### 2.15. SERDES and Physical Coding Sublayer

LFE5UM/LFE5UM5G devices feature up to 4 channels of embedded SERDES/PCS arranged in dual-channel blocks at the bottom of the devices. Each channel supports up to 3.2 Gb/s (ECP5), or up to 5 Gb/s (ECP5-5G) data rate. Figure 2.27 shows the position of the dual blocks for the LFE5-85. Table 2.13 shows the location of available SERDES Duals for all devices. The LFE5UM/LFE5UM5G SERDES/PCS supports a range of popular serial protocols, including:

- x PCI Express Gen1 and Gen2 (2.5 Gb/s) on ECP5UM; Gen 1, Gen2 (2.5 Gb/s and 5 Gb/s) on ECP5-5G

- x Ethernet (XAUI, GbE t 1000 Base CS/SX/LX and SGMII)

- x SMPTE SDI (3G-SDI, HD-SDI, SD-SDI)

- X CPRI (E.6.LV: 614.4 Mb/s, E.12.LV: 1228.8 Mb/s, E.24.LV: 2457.6 Mb/s, E.30.LV: 3072 Mb/s), also E.48.LV2:4915 Mb/s in ECP5-5G

- x JESD204A/B t ADC and DAC converter interface: 312.5 Mb/s to 3.125 Gb/s (ECP5) / 5 Gb/s (ECP5-5G)

Each dual contains two dedicated SERDES for high speed, full duplex serial data transfer. Each dual also has a PCS block that interfaces to the SERDES channels and contains protocol specific digital logic to support the standards listed above. The PCS block also contains interface logic to the FPGA fabric. All PCS logic for dedicated protocol support can also be bypassed to allow raw 8-bit or 10-bit interfaces to the FPGA fabric.

Even though the SERDES/PCS blocks are arranged in duals, multiple baud rates can be supported within a dual with the use of dedicated, per channel /1, /2 and /11 rate dividers. Additionally, two duals can be arranged together to form x4 channel link.

ECP5UM devices and ECP5-5G devices are pin-to-pin compatible. But, the ECP5UM devices require 1.1 V on VCCA, VCCHRX and VCCHTX supplies. ECP5-5G devices require 1.2 V on these supplies. When designing either family device with migration in mind, these supplies need to be connected such that it is possible to adjust the voltage level on these supplies.

When a SERDES Dual in a 2-Dual device is not used, the power VCCA power supply for that Dual should be connected. It is advised to connect the VCCA of unused channel to core if the user knows he will not use the Dual at all, or it should be connected to a different regulated supply, if that Dual may be used in the future.

For an unused channel in a Dual, it is advised to connect the VCCHTX to VCCA, and user can leave VCCHRX unconnected.

For information on how to use the SERDES/PCS blocks to support specific protocols, as well on how to combine multiple protocols and baud rates within a device, refer to ECP5 and ECP5-5G SERDES/PCS Usage Guide (TN1261).

Figure 2.27. SERDES/PCS Duals (LFE5UM/LFE5UM5G-85)

| Standard                                       | Data Rate (Mb/s)                                           | Number of General/Link Width | Encoding Style |

|------------------------------------------------|------------------------------------------------------------|------------------------------|----------------|

| PCI Express 1.1 and 2.0                        | 2500                                                       | x1, x2, x4                   | 8b10b          |

| 2.02                                           | 5000 <sup>2</sup>                                          | x1, x2                       | 8b10b          |

| Gigabit Ethernet                               | 1250                                                       | x1                           | 8b10b          |

| COMU                                           | 1250                                                       | x1                           | 8b10b          |

| SGMII                                          | 2500                                                       | x1                           | 8b10b          |

| XAUI                                           | 3125                                                       | x4                           | 8b10b          |

| CPRI-1<br>CPRI-2<br>CPRI-3<br>CPRI-4<br>CPRI-5 | 614.4<br>1228.8<br>2457.6<br>3072.0<br>4915.2 <sup>2</sup> | x1                           | 8b10b          |

| SD-SDI (259M, 344M) <sup>1</sup>               | 270                                                        | x1                           | NRZI/Scrambled |

| HD-SDI (292M)                                  | 1483.5<br>1485                                             | x1                           | NRZI/Scrambled |

| 3G-SDI (424M)                                  | 2967<br>2970                                               | x1                           | NRZI/Scrambled |

|                                                | 5000                                                       | v                            | V              |

| JESD204A/B                                     | 3125                                                       | x1                           | 8b/10b         |

#### Notes:

1. For SD-SDI rate, the SERDES is bypassed and SERDES input signals are directly connected to the FPGA routing.

2. For ECP5-5G family devices only.

## 3. DC and Switching Characteristics

### 3.1. Absolute Maximum Ratings

#### Table 3.1. Absolute Maximum Ratings

| Symbol                                   | Parameter                              | Min  | Max  | Unit |

|------------------------------------------|----------------------------------------|------|------|------|

| V <sub>cc</sub>                          | Supply Voltage                         | t0.5 | 1.32 | V    |

| V <sub>CCA</sub>                         | Supply Voltage                         | t0.5 | 1.32 | V    |

| V <sub>CCAUX</sub> , V <sub>CCAUXA</sub> | Supply Voltage                         | t0.5 | 2.75 | V    |

| V <sub>CCIO</sub>                        | Supply Voltage                         | t0.5 | 3.63 | V    |

| V                                        | Input or I/O Transient Voltage Applied | t0.5 | 3.63 | V    |

| V <sub>CCHRX</sub> , V <sub>CCHTX</sub>  | SERDES RX/TX Buffer Supply Voltages    | t0.5 | 1.32 | V    |

| V                                        | Voltage Applied on SERDES Pins         | t0.5 | 1.80 | V    |

| T <sub>A</sub>                           | Storage Temperature (Ambient)          | t65  | 150  | °C   |

| Tj                                       | Junction Temperature                   | V    | +125 | °C   |

Notes:

Stress above those listed μv Œ šZ ^ • } o μš D Æ ] u μu Z š] v P • \_ u Ç μ • ‰ Œ u v vš u P š} operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

2. Compliance with the Lattice Thermal Management document is required.

3. All voltages referenced to GND.

### 3.2. Recommended Operating Conditions

#### **Table 3.2. Recommended Operating Conditions**

| Symbol                             | Parameter                                  |         | Min   | Max   | Unit |

|------------------------------------|--------------------------------------------|---------|-------|-------|------|

| N 2                                | Cone Supply Veltage                        | ECP5    | 1.045 | 1.155 | V    |

| V <sub>CC</sub> <sup>2</sup>       | Core Supply Voltage                        | ECP5-5G | 1.14  | 1.26  | V    |

| V <sub>CCAUX</sub> <sup>2, 4</sup> | Auxiliary Supply Voltage                   | v       | 2.375 | 2.625 | V    |

| V <sub>CCIO</sub> <sup>2, 3</sup>  | I/O Driver Supply Voltage                  | v       | 1.14  | 3.465 | V    |

| $V_{\text{REF}}^1$                 | Input Reference Voltage                    | v       | 0.5   | 1.0   | V    |

| t <sub>JCOM</sub>                  | Junction Temperature, Commercial Operation | v       | 0     | 85    | °C   |

| t <sub>JIND</sub>                  | Junction Temperature, Industrial Operation | V       | t40   | 100   | °C   |

| SERDES Externa                     | l Power Supply⁵                            |         |       |       |      |

| N                                  |                                            | ECP5UM  | 1.045 | 1.155 | V    |

| V <sub>CCA</sub>                   | SERDES Analog Power Supply                 | ECP5-5G | 1.164 | 1.236 | V    |

| V <sub>CCAUXA</sub>                | SERDES Auxiliary Supply Voltage            | v       | 2.374 | 2.625 | V    |

| N 6                                |                                            | ECP5UM  | 0.30  | 1.155 | V    |

| V <sub>CCHRX</sub> <sup>6</sup>    | SERDES Input Buffer Power Supply           | ECP5-5G | 0.30  | 1.26  | V    |

| N.                                 |                                            | ECP5UM  | 1.045 | 1.155 | V    |

| V <sub>CCHTX</sub>                 | SERDES Output Buffer Power Supply          | ECP5-5G | 1.14  | 1.26  | V    |

#### Notes:

1. For correct operation, all supplies except V<sub>REF</sub> must be held in their valid operation range. This is true independent of feature usage.

2. All supplies with same voltage, except SERDES Power Supplies, should be connected together.

- 3. See recommended voltages by I/O standard in Table 3.4 on page 48.

- 4. V<sub>CCAUX</sub> ramp rate must not exceed 30 mV/µs during power-up when transitioning between 0 V and 3 V.

- 5. Refer to ECP5 and ECP5-5G SERDES/PCS Usage Guide (TN1261) for information on board considerations for SERDES power supplies.

- 6. V<sub>CCHRX</sub> is used for Rx termination. It can be biased to Vcm if external AC coupling is used. This voltage needs to meet all the HDin input voltage level requirements specified in the Rx section of this Data Sheet.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### 3.7. Hot Socketing Requirements

#### **Table 3.6. Hot Socketing Requirements**

**#LATTICE**

| Description                                                                               | Min | Тур | Мах | Unit |

|-------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Input current per SERDES I/O pin when device is powered down and inputs driven.           |     | v   | 8   | mA   |

| Input current per HDIN pin when device power supply is off, inputs driven <sup>1, 2</sup> | v   | v   | 15  | mA   |

| Current per HDIN pin when device power ramps up, input driven <sup>3</sup>                |     | v   | 50  | mA   |

| Current per HDOUT pin when device power supply is off, outputs pulled up <sup>4</sup>     | v   | v   | 30  | mA   |

Notes:

1. Device is powered down with all supplies grounded, both HDINP and HDINN inputs driven by a CML driver with maximum allowed output V<sub>CCHTX</sub>, 8b/10b data, no external AC coupling.

2. Each P and N input must have less than the specified maximum input current during hot plug. For a device with 2 DCU, the total input current would be 15 mA \* 4 channels \* 2 input pins per channel = 120 mA.

- Device power supplies are ramping up (V<sub>CCA</sub> and V<sub>CCAUX</sub>), both HDINP and HDINN inputs are driven by a CML driver with maximum allowed output V<sub>CCHTX</sub>, 8b/10b data, internal AC coupling.

- 4. Device is powered down with all supplies grounded. Both HDOUTP and HDOUN outputs are pulled up to V<sub>CCHTX</sub> by the far end receiver termination of 50 Qsingle ended.

### 3.8. ESD Performance

Refer to the ECP5 and ECP5-5G Product Family Qualification Summary for complete qualification data, including ESD performance.

### 3.9. DC Electrical Characteristics

**Over Recommended Operating Conditions**

| Symbol                                                            | Parameter Condition                                              |                                                                                                                                                                     | Min | Тур | Max  | Unit |

|-------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| $I_{IL},I_{IH}^{1,4}$                                             | Input or I/O Low Leakage                                         | 0 dV <sub>IN</sub> dV <sub>CCIO</sub>                                                                                                                               | v   | v   | 10   | μA   |

| I <sub>IH</sub> <sup>1, 3</sup>                                   | Input or I/O High Leakage                                        | $V_{CCIO} < V_{IN} dV_{IH(MAX)}$                                                                                                                                    | v   | v   | 100  | μΑ   |

|                                                                   | I/O Active Pull-up Current,<br>sustaining logic HIGH state       | 0.7 V <sub>CCIO</sub> dV <sub>IN</sub> dV <sub>CCIO</sub>                                                                                                           | t30 | v   | v    | μA   |

| I/O Active Pull-up Current, pulling<br>down from logic HIGH state |                                                                  | 0 dV <sub>IN</sub> d0.7 V <sub>CCIO</sub>                                                                                                                           | v   | v   | t150 | μA   |

| IPD                                                               | I/O Active Pull-down Current,<br>sustaining logic LOW state      | 0 dV <sub>IN</sub> d V <sub>IL</sub> (MAX)                                                                                                                          | 30  | v   | v    | μA   |

| ΨD                                                                | I/O Active Pull-down Current,<br>pulling up from logic LOW state | 0 dV <sub>IN</sub> dV <sub>CCIO</sub>                                                                                                                               | v   | v   | 150  | μA   |

| C1                                                                | I/O Capacitance <sup>2</sup>                                     | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V}, \\ V_{CC} = 1.2 \text{ V}, V_{IO} = 0 \text{ to } V_{IH(MAX)}$               | v   | 5   | 8    | pf   |

| C2                                                                | Dedicated Input Capacitance <sup>2</sup>                         | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V}, \\ V_{CC} = 1.2 \text{ V}, V_{IO} = 0 \text{ to } V_{\text{IH}(\text{MAX})}$ | v   | 5   | 7    | pf   |

| V                                                                 | Hysteresis for Single-Ended                                      | V <sub>CCIO</sub> = 3.3 V                                                                                                                                           | v   | 300 | v    | mV   |

| V <sub>HYST</sub> Inputs                                          |                                                                  | V <sub>CCIO</sub> = 2.5 V                                                                                                                                           | v   | 250 | v    | mV   |

#### Notes:

1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tristated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

2. T<sub>A</sub> 25 °C, f = 1.0 MHz.

- 3. Applicable to general purpose I/Os in top and bottom banks.

- 4. When used as  $V_{REF}$ , maximum leakage= 25  $\mu$ A.

### 3.17. Maximum I/O Buffer Speed

Over recommended operating conditions.

#### Table 3.21. ECP5/ECP5-5G Maximum I/O Buffer Speed

| uffer Description               |                                                  | Max | Unit |

|---------------------------------|--------------------------------------------------|-----|------|

| Maximum Input Frequency         | ·                                                | ·   |      |

| LVDS25                          | LVDS, V <sub>CCIO</sub> = 2.5 V                  | 400 | MHz  |

| MLVDS25                         | MLVDS, Emulated, V <sub>CCIO</sub> = 2.5 V       | 400 | MHz  |

| BLVDS25                         | BLVDS, Emulated, V <sub>CCIO</sub> = 2.5 V       | 400 | MHz  |

| MIPI D-PHY (HS Mode)            | MIPI Video                                       | 400 | MHz  |

| SLVS                            | SLVS similar to MIPI                             | 400 | MHz  |

| Mini LVDS                       | Mini LVDS                                        | 400 | MHz  |

| LVPECL33                        | LVPECL, Emulated, V <sub>CCIO</sub> = 3.3 V      | 400 | MHz  |

| SSTL18 (all supported classes)  | SSTL_18 class I, II, V <sub>CCIO</sub> = 1.8 V   | 400 | MHz  |

| SSTL15 (all supported classes)  | SSTL_15 class I, II, V <sub>CCIO</sub> = 1.5 V   | 400 | MHz  |

| SSTL135 (all supported classes) | SSTL_135 class I, II, V <sub>CCIO</sub> = 1.35 V | 400 | MHz  |

| HSUL12 (all supported classes)  | HSUL_12 class I, II, V <sub>CCIO</sub> = 1.2 V   | 400 | MHz  |

| LVTTL33                         | LVTTL, V <sub>CCIO</sub> = 3.3 V                 | 200 | MHz  |

| LVCMOS33                        | LVCMOS, V <sub>CCIO</sub> = 3.3 V                | 200 | MHz  |

| LVCMOS25                        | LVCMOS, V <sub>CCIO</sub> = 2.5 V                | 200 | MHz  |

| LVCMOS18                        | LVCMOS, V <sub>CCIO</sub> = 1.8 V                | 200 | MHz  |

| LVCMOS15                        | LVCMOS 1.5, V <sub>CCIO</sub> = 1.5 V            | 200 | MHz  |

| LVCMOS12                        | LVCMOS 1.2, V <sub>CCIO</sub> = 1.2 V            | 200 | MHz  |

| Maximum Output Frequency        |                                                  |     |      |

| LVDS25E                         | LVDS, Emulated, V <sub>CCIO</sub> = 2.5 V        | 150 | MHz  |

| LVDS25                          | LVDS, V <sub>CCIO</sub> = 2.5 V                  | 400 | MHz  |

| MLVDS25                         | MLVDS, Emulated, V <sub>CCIO</sub> = 2.5 V       | 150 | MHz  |

| BLVDS25                         | BLVDS, Emulated, V <sub>CCIO</sub> = 2.5 V       | 150 | MHz  |

| LVPECL33                        | LVPECL, Emulated, V <sub>CCIO</sub> = 3.3 V      | 150 | MHz  |

| SSTL18 (all supported classes)  | SSTL_18 class I, II, V <sub>CCIO</sub> = 1.8 V   | 400 | MHz  |

| SSTL15 (all supported classes)  | SSTL_15 class I, II, V <sub>CCIO</sub> = 1.5 V   | 400 | MHz  |

| SSTL135 (all supported classes) | SSTL_135 class I, II, V <sub>CCIO</sub> = 1.35 V | 400 | MHz  |

| HSUL12 (all supported classes)  | HSUL12 class I, II, V <sub>CCI0</sub> = 1.2 V    | 400 | MHz  |

| LVTTL33                         | LVTTL, VCCIO = 3.3 V                             | 150 | MHz  |

| LVCMOS33 (For all drives)       | LVCMOS, 3.3 V                                    | 150 | MHz  |

| LVCMOS25 (For all drives)       | LVCMOS, 2.5 V                                    | 150 | MHz  |

| LVCMOS18 (For all drives)       | LVCMOS, 1.8 V                                    | 150 | MHz  |

| LVCMOS15 (For all drives)       | LVCMOS, 1.5 V                                    | 150 | MHz  |

| LVCMOS12 (For all drives)       | LVCMOS, 1.2 V                                    | 150 | MHz  |

Notes:

1. These maximum speeds are characterized but not tested on every device.

- 2. Maximum I/O speed for differential output standards emulated with resistors depends on the layout.

- 3. LVCMOS timing is measured with the load specified in Switching Test Conditions, Table 3.44 on page 90.

- 4. All speeds are measured at fast slew.

- 5. Actual system operation may vary depending on user logic implementation.

- 6. Maximum data rate equals 2 times the clock rate when utilizing DDR.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

1

1

v

Unit<sup>3</sup>

byte clk

word clk byte clk

byte clk UI + ps

UI + ps UI + ps

UI + ps

UI + ps

UI + ps

UI + ps

UI + ps

byte clk

byte clk

byte clk

byte clk

byte clk

word clk

### 3.21. SERDES/PCS Block Latency

Table 3.26 describes the latency of each functional block in the transmitter and receiver. Latency is given in parallel clock cycles. Figure 3.13 shows the location of each block.

| Table 3.   | 26. SERDES/PCS Latency Breakdown                |     |     |     |         |        |

|------------|-------------------------------------------------|-----|-----|-----|---------|--------|

| Item       | Description                                     | Min | Avg | Max | Fixed   | Bypass |

| Transm     | it Data Latency <sup>1</sup>                    |     |     |     | -       |        |

| <b>T</b> 1 | FPGA Bridge - Gearing disabled with same clocks | 3   | v   | 4   | v       | 1      |

| T1         | FPGA Bridge - Gearing enabled                   | 5   | v   | 7   | v       | v      |

| Т2         | 8b10b Encoder                                   | v   | v   | v   | 2       | 1      |

| Т3         | SERDES Bridge transmit                          | v   | v   | v   | 2       | 1      |

| T4         | Serializer: 8-bit mode                          | v   | v   | v   | 15 + '1 | v      |

| 14         | Serializer: 10-bit mode                         | v   | v   | v   | 18 + '1 | v      |

| TF         | Pre-emphasis ON                                 | v   | v   | v   | 1 + '2  | v      |

| Т5         | Pre-emphasis OFF                                | v   | v   | v   | 0 + '3  | v      |

| Receive    | e Data Latency <sup>2</sup>                     |     |     |     |         |        |

| D1         | Equalization ON                                 | v   | v   | v   | '1      | v      |

| R1         | Equalization OFF                                | v   | v   | v   | '2      | v      |

| <b>D</b> 2 | Deserializer: 8-bit mode                        | v   | v   | v   | 10 + '3 | v      |

| R2         | Deserializer: 10-bit mode                       | v   | v   | v   | 12 + '3 | v      |

| R3         | SERDES Bridge receive                           | v   | v   | v   | 2       | v      |

| R4         | Word alignment                                  | 3.1 | v   | 4   | v       | 1      |

| R5         | 8b10b decoder                                   | v   | v   | v   | 1       | 0      |

Notes:

R6

R7

1. '1 = t245 ps, '2 = +88 ps, '3 = +112 ps.

**Clock Tolerance Compensation**

FPGA Bridge - Gearing enabled

FPGA Bridge - Gearing disabled with same clocks

2. '1 = +118 ps, '2 = +132 ps, '3 = +700 ps.

3. byte clk = 8UIs (8-bit mode), or 10 UIs (10-bit mode); word clk = 16UIs (8-bit mode), or 20 UIs (10-bit mode).

7

4

7

15

v

v

23

5

9

v

v

٧

### 3.30. SMPTE SD/HD-SDI/3G-SDI (Serial Digital Interface) Electrical and Timing Characteristics

#### 3.30.1. AC and DC Characteristics

#### Table 3.39. Transmit

| Symbol                                  | Description                     | Test Conditions       | Min           | Тур | Max  | Unit |

|-----------------------------------------|---------------------------------|-----------------------|---------------|-----|------|------|

| BR <sub>SDO</sub>                       | Serial data rate                | v                     | 270           | V   | 2975 | Mb/s |

| T <sub>JALIGNMENT</sub> <sup>2</sup>    | Serial output jitter, alignment | 270 Mb/s <sup>6</sup> | v             | v   | 0.2  | UI   |

| T <sub>JALIGNMENT</sub> <sup>2</sup>    | Serial output jitter, alignment | 1485 Mb/s             | 1485 Mb/s v v |     | 0.2  | UI   |

| T <sub>JALIGNMENT</sub> <sup>1, 2</sup> | Serial output jitter, alignment | 2970 Mb/s             | v             | V   | 0.3  | UI   |

| T <sub>JTIMING</sub>                    | Serial output jitter, timing    | 270 Mb/s <sup>6</sup> | v             | v   | 0.2  | UI   |

| T <sub>JTIMING</sub>                    | Serial output jitter, timing    | 1485 Mb/s             | v             | V   | 1    | UI   |

| TJTIMING                                | Serial output jitter, timing    | 2970 Mb/s             | v             | v   | 2    | UI   |

Notes:

1. Timing jitter is measured in accordance with SMPTE serial data transmission standards.

- 2. Jitter is defined in accordance with SMPTE RP1 184-1996 as: jitter at an equipment output in the absence of input jitter.

- 3. All Tx jitter are measured at the output of an industry standard cable driver, with the Lattice SERDES device configured to  $\tilde{n} \wr Q$  output impedance connecting to the external cable driver with differential signaling.

- 4. The cable driver drives: RL=75 QAC-coupled at 270, 1485, or 2970 Mb/s.

- 5. All LFE5UM/LFE5UM5G devices are compliant with all SMPTE compliance tests, except 3G-SDI Level-A pathological compliance pattern test.

- 6. 270 Mb/s is supported with Rate Divider only.

#### Table 3.40. Receive

| Symbol            | Description            | Test Conditions | Min | Тур | Max  | Unit |

|-------------------|------------------------|-----------------|-----|-----|------|------|

| BR <sub>SDI</sub> | Serial input data rate | V               | 270 | V   | 2970 | Mb/s |

#### Table 3.41. Reference Clock

| Symbol            | Description                  | Description Test Conditions Min |    | Тур | Max   | Unit |

|-------------------|------------------------------|---------------------------------|----|-----|-------|------|

| F <sub>VCLK</sub> | Video output clock frequency | v                               | 54 | v   | 148.5 | MHz  |

| DCv               | Duty cycle, video clock      | v                               | 45 | 50  | 55    | %    |

**Note**: SD-SDI (270 Mb/s) is supported with Rate Divider only. For Single Rate: Reference Clock = 54 MHz and Rate Divider = /2. For Tri-Rate: Reference Clock = 148.5 MHz and Rate Divider = /11.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

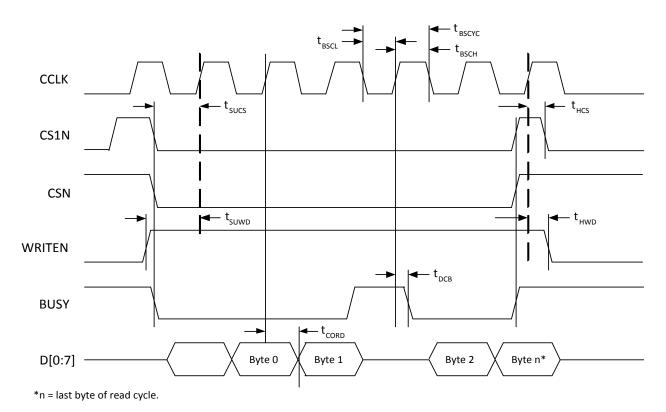

#### Table 3.42. ECP5/ECP5-5G sysCONFIG Port Timing Specifications (Continued)

| Symbol              | Parameter                        | Min | Max | Unit |     |  |  |

|---------------------|----------------------------------|-----|-----|------|-----|--|--|

| Slave Parallel      |                                  |     |     |      |     |  |  |

| f <sub>cclk</sub>   | CCLK input clock frequency       | v   | v   | 50   | MHz |  |  |

| t <sub>BSCH</sub>   | CCLK input clock pulsewidth HIGH | v   | 6   | v    | ns  |  |  |

| t <sub>BSCL</sub>   | CCLK input clock pulsewidth LOW  | v   | 6   | v    | ns  |  |  |

| t <sub>cord</sub>   | CCLK to DOUT for Read Data       | v   | v   | 12   | ns  |  |  |

| t <sub>sucbdi</sub> | Data Setup Time to CCLK          | v   | 1.5 | v    | ns  |  |  |

| t <sub>HCBDI</sub>  | Data Hold Time to CCLK           | v   | 1.5 | v    | ns  |  |  |

| t <sub>sucs</sub>   | CSN, CSN1 Setup Time to CCLK     | v   | 2.5 | v    | ns  |  |  |

| t <sub>HCS</sub>    | CSN, CSN1 Hold Time to CCLK      | v   | 1.5 | v    | ns  |  |  |

| t <sub>suwd</sub>   | WRITEN Setup Time to CCLK        | v   | 45  | v    | ns  |  |  |

| t <sub>HCWD</sub>   | WRITEN Hold Time to CCLK         | v   | 2   | v    | ns  |  |  |

| t <sub>DCB</sub>    | CCLK to BUSY Delay Time          | v   | v   | 12   | ns  |  |  |

Figure 3.15. sysCONFIG Parallel Port Read Cycle

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Part number          | Grade    | Package          | Pins | Temp.      | LUTs (K) | SERDES |

|----------------------|----------|------------------|------|------------|----------|--------|

| LFE5U-45F-8BG554C    | t8       | Lead free caBGA  | 554  | Commercial | 44       | No     |

| LFE5U-85F-6MG285C    | t6       | Lead free csfBGA | 285  | Commercial | 84       | No     |

| LFE5U-85F-7MG285C    | t7       | Lead free csfBGA | 285  | Commercial | 84       | No     |

| LFE5U-85F-8MG285C    | t8       | Lead free csfBGA | 285  | Commercial | 84       | No     |

| LFE5U-85F-6BG381C    | t6       | Lead free caBGA  | 381  | Commercial | 84       | No     |

| LFE5U-85F-7BG381C    | t7       | Lead free caBGA  | 381  | Commercial | 84       | No     |

| LFE5U-85F-8BG381C    | t8       | Lead free caBGA  | 381  | Commercial | 84       | No     |

| LFE5U-85F-6BG554C    | t6       | Lead free caBGA  | 554  | Commercial | 84       | No     |

| LFE5U-85F-7BG554C    | t7       | Lead free caBGA  | 554  | Commercial | 84       | No     |

| LFE5U-85F-8BG554C    | t8       | Lead free caBGA  | 554  | Commercial | 84       | No     |

| LFE5U-85F-6BG756C    | t6       | Lead free caBGA  | 756  | Commercial | 84       | No     |

| LFE5U-85F-7BG756C    | t7       | Lead free caBGA  | 756  | Commercial | 84       | No     |

| LFE5U-85F-8BG756C    | t8       | Lead free caBGA  | 756  | Commercial | 84       | No     |

| LFE5UM-25F-6MG285C   | t6       | Lead free csfBGA | 285  | Commercial | 24       | Yes    |

| LFE5UM-25F-7MG285C   | t7       | Lead free csfBGA | 285  | Commercial | 24       | Yes    |

| LFE5UM-25F-8MG285C   | t8       | Lead free csfBGA | 285  | Commercial | 24       | Yes    |

| LFE5UM-25F-6BG381C   | t6       | Lead free caBGA  | 381  | Commercial | 24       | Yes    |

| LFE5UM-25F-7BG381C   | t7       | Lead free caBGA  | 381  | Commercial | 24       | Yes    |

| LFE5UM-25F-8BG381C   | t8       | Lead free caBGA  | 381  | Commercial | 24       | Yes    |

| LFE5UM-45F-6MG285C   | t6       | Lead free csfBGA | 285  | Commercial | 44       | Yes    |

| LFE5UM-45F-7MG285C   | t7       | Lead free csfBGA | 285  | Commercial | 44       | Yes    |

| LFE5UM-45F-8MG285C   | t8       | Lead free csfBGA | 285  | Commercial | 44       | Yes    |

| LFE5UM-45F-6BG381C   | t6       | Lead free caBGA  | 381  | Commercial | 44       | Yes    |

| LFE5UM-45F-7BG381C   | t7       | Lead free caBGA  | 381  | Commercial | 44       | Yes    |

| LFE5UM-45F-8BG381C   | t8       | Lead free caBGA  | 381  | Commercial | 44       | Yes    |

| LFE5UM-45F-6BG554C   | t6       | Lead free caBGA  | 554  | Commercial | 44       | Yes    |

| LFE5UM-45F-7BG554C   | t7       | Lead free caBGA  | 554  | Commercial | 44       | Yes    |

| LFE5UM-45F-8BG554C   | t8       | Lead free caBGA  | 554  | Commercial | 44       | Yes    |

| LFE5UM-85F-6MG285C   | t6       | Lead free csfBGA | 285  | Commercial | 84       | Yes    |

| LFE5UM-85F-7MG285C   | t7       | Lead free csfBGA | 285  | Commercial | 84       | Yes    |

| LFE5UM-85F-8MG285C   | t8       | Lead free csfBGA | 285  | Commercial | 84       | Yes    |

| LFE5UM-85F-6BG381C   | t6       | Lead free caBGA  | 381  | Commercial | 84       | Yes    |

| LFE5UM-85F-7BG381C   | t7       | Lead free caBGA  | 381  | Commercial | 84       | Yes    |

| LFE5UM-85F-8BG381C   | t8       | Lead free caBGA  | 381  | Commercial | 84       | Yes    |

| LFE5UM-85F-6BG554C   | t6       | Lead free caBGA  | 554  | Commercial | 84       | Yes    |

| LFE5UM-85F-7BG554C   | t7       | Lead free caBGA  | 554  | Commercial | 84       | Yes    |

| LFE5UM-85F-8BG554C   | t8       | Lead free caBGA  | 554  | Commercial | 84       | Yes    |

| LFE5UM-85F-6BG756C   | t6       | Lead free caBGA  | 756  | Commercial | 84       | Yes    |

| LFE5UM-85F-7BG756C   | t7       | Lead free caBGA  | 756  | Commercial | 84       | Yes    |

| LFE5UM-85F-8BG756C   | t8       | Lead free caBGA  | 756  | Commercial | 84       | Yes    |

| LFE5UM5G-25F-8MG285C | t8<br>t0 | Lead free csfBGA | 285  | Commercial | 24       | Yes    |

| LFE5UM5G-25F-8BG381C | t8       | Lead free caBGA  | 381  | Commercial | 24       | Yes    |

| LFE5UM5G-45F-8MG285C | t8<br>t0 | Lead free csfBGA | 285  | Commercial | 44       | Yes    |

| LFE5UM5G-45F-8BG381C | t8       | Lead free caBGA  | 381  | Commercial | 44       | Yes    |

| LFE5UM5G-45F-8BG554C | t8       | Lead free caBGA  | 554  | Commercial | 44       | Yes    |

| LFE5UM5G-85F-8MG285C | t8       | Lead free csfBGA | 285  | Commercial | 84       | Yes    |

### **Supplemental Information**

### **For Further Information**

A variety of technical notes for the ECP5/ECP5-5G family are available.

- x High-Speed PCB Design Considerations (TN1033)

- x Transmission of High-Speed Serial Signals Over Common Cable Media (TN1066)

- x PCB Layout Recommendations for BGA Packages (TN1074)

- x Minimizing System Interruption During Configuration Using TransFR Technology (TN1087)

- x Electrical Recommendations for Lattice SERDES (FPGA-TN-02077)

- x LatticeECP3, ECP-5 and ECP5-5G Soft Error Detection (SED)/Correction (SEC) Usage Guide (TN1184)

- x Using TraceID (TN1207)

- x Sub-LVDS Signaling Using Lattice Devices (TN1210)

- x Advanced Security Encryption Key Programming Guide for ECP5, ECP5-5G, LatticeECP3, and LatticeECP2/MS Devices (TN1215)

- x LatticeECP3, LatticeECP2/M, ECP5 and ECP5-5G Dual Boot and Multiple Boot Feature (TN1216)

- x ECP5 and ECP5-5G sysCONFIG Usage Guide (TN1260)

- x ECP5 and ECP5-5G SERDES/PCS Usage Guide (TN1261)

- x ECP5 and ECP5-5G sysIO Usage Guide (TN1262)

- x ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263)

- x ECP5 and ECP5-5G Memory Usage Guide (TN1264)

- x ECP5 and ECP5-5G High-Speed I/O Interface (TN1265)

- x Power Consumption and Management for ECP5 and ECP5-5G Devices (TN1266)

- x ECP5 and ECP5-5G sysDSP Usage Guide (TN1267)

- x ECP5 and ECP5-5G Hardware Checklist (FPGA-TN-02038)

- x Solder Reflow Guide for Surface Mount Devices (FPGA-TN-02041)

- x ECP5 and ECP5-5G PCI Express Soft IP Ease of Use Guidelines (FPGA-TN-02045)

- x Programming External SPI Flash through JTAG for ECP5/ECP5-5G (FPGA-TN-02050)

- x Adding Scalable Power and Thermal Management to ECP5 Using L-ASC10 (AN6095)

For further information on interface standards refer to the following websites:

- x JEDEC Standards (LVTTL, LVCMOS, SSTL): www.jedec.org

- x PCI: www.pcisig.com

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

### (Continued)

| Date          | Version | Section                                                                        | Change Summary                                                                                                                                                                                                                                                                             |  |  |

|---------------|---------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| November 2015 | 1.5     | All                                                                            | Added ECP5-5G device family.                                                                                                                                                                                                                                                               |  |  |

|               |         |                                                                                | Changed document title to ECP5 and ECP5-5G Family Data Sheet.                                                                                                                                                                                                                              |  |  |

|               | 1.4     | General Description Updated Features section. Added support for eDP in RDR and |                                                                                                                                                                                                                                                                                            |  |  |

|               |         | Architecture                                                                   | Updated Overview section.<br>Revised Figure 2.1. Simplified Block Diagram, LFE5UM/LFE5UM5G-85<br>Device (Top Level). Modified Flexible sysIO description and Note.                                                                                                                         |  |  |

|               |         |                                                                                | Updated SERDES and Physical Coding Sublayer section.<br>x Changed E.24.V in CPRI protocol to E.24.LV.<br>x Z u } À ^í X í s_ (CE } u ‰ CE P CE ‰ Z } v µ v                                                                                                                                 |  |  |

|               |         | DC and Switching<br>Characteristics                                            | Updated Hot Socketing Requirements section. Revised V <sub>CCHTX</sub> in table notes 1 and 3. Indicated V <sub>CCHTX</sub> in table note 4.                                                                                                                                               |  |  |

|               |         |                                                                                | Updated SERDES High-Speed Data Transmitter section. Revised $\rm V_{\rm CCHTX}$ in table note 1.                                                                                                                                                                                           |  |  |

|               |         | Ordering Information                                                           | Updated ECP5/ECP5-5G Part Number Description section. Changed<br>^ > & $\tilde{n} & W' = \mu v  OE  A ] & u ] o C \\ \tilde{s} \\ \rangle & W \\ \tilde{n} & W' = \mu v  OE  A \\ \delta & U \\ \delta & \delta & \delta \\ \delta & \delta & \delta & \delta \\ \delta & \delta & \delta$ |  |  |

| August 2015   | 1.3     | General Description                                                            | Updated Features section.<br>X Removed SMPTE3G under Embedded SERDES.<br>X Added Single Event Upset (SEU) Mitigation Support.<br>Removed SMPTE protocol in fifth paragraph.                                                                                                                |  |  |

|               |         | Architecture                                                                   | General update.                                                                                                                                                                                                                                                                            |  |  |

|               |         | DC and Switching<br>Characteristics                                            | General update.                                                                                                                                                                                                                                                                            |  |  |

|               |         | Pinout Information                                                             | Updated Signal Descriptions section. Revised the descriptions of the<br>following signals:                                                                                                                                                                                                 |  |  |

|               |         | Supplemental<br>Information                                                    | Added TN1184 reference.                                                                                                                                                                                                                                                                    |  |  |

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

#### (Continued)

| Date        | Version | Section             | Change Summary                                                                                                                                                                                                                                                                                                     |

|-------------|---------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| August 2014 | 1.2     | All                 | Changed document status from Advance to Preliminary.                                                                                                                                                                                                                                                               |

|             |         | General Description | Updated Features section.                                                                                                                                                                                                                                                                                          |

|             |         |                     | x Deleted Serial RapidIO protocol under Embedded SERDES.                                                                                                                                                                                                                                                           |

|             |         |                     | x Corrected data rate under Pre-Engineered Source Synchronous                                                                                                                                                                                                                                                      |

|             |         |                     | Changed DD3. LPDDR3 to DDR2/3, LPDDR2/3.                                                                                                                                                                                                                                                                           |

|             |         |                     | Mentioned transmit de- u‰Z •]•ant@poEt- µCE•}CE•_X                                                                                                                                                                                                                                                                 |

|             |         | Architecture        | Updated Overview section.                                                                                                                                                                                                                                                                                          |

|             |         |                     | X Revised description of PFU blocks.                                                                                                                                                                                                                                                                               |

|             |         |                     | X Specified SRAM cell settings in describing the control of<br>SERDES/PCS duals.                                                                                                                                                                                                                                   |

|             |         |                     | Updated SERDES and Physical Coding Sublayer section.                                                                                                                                                                                                                                                               |

|             |         |                     | x Changed PCI Express 2.0 to PCI Express Gen1 and Gen2.                                                                                                                                                                                                                                                            |

|             |         |                     | x Deleted Serial RapidIO protocol.                                                                                                                                                                                                                                                                                 |

|             |         |                     | X Updated Table 2.13. LFE5UM/LFE5UM5G SERDES Standard<br>Support.                                                                                                                                                                                                                                                  |

|             |         |                     | Updated On-Chip Oscillator section.                                                                                                                                                                                                                                                                                |

|             |         |                     | x oš ^íïì±D0ņ̇́9 DK^_}•]ooš}CEX                                                                                                                                                                                                                                                                                    |

|             |         | DC and Switching    | <ul> <li>X Updated Table 2.16. Selectable Master Clock (MCLK) Frequencies<br/>during Configuration (Nominal)</li> </ul>                                                                                                                                                                                            |

|             |         |                     | Updated Absolute Maximum Ratings section. Added supply voltages                                                                                                                                                                                                                                                    |

|             |         | Characteristics     | V <sub>CCA</sub> and V <sub>CCAUXA</sub> .                                                                                                                                                                                                                                                                         |

|             |         |                     | Updated sysI/O Recommended Operating Conditions section. Revised HSULD12D VCCIO values and removed table note.                                                                                                                                                                                                     |

|             |         |                     | Updated sysI/O Single-Ended DC Electrical Characteristics section.<br>Revised some values for SSTL15 _I, SSTL15 _II, SSTL135_I, SSTL15_II,<br>and HSUL12.                                                                                                                                                          |

|             |         |                     | Updated External Switching Characteristics section. Changed parameters to $t_{SKEW\_PR}V_{CCA}$ and $t_{SKEW\_EDGE}$ and added LFE5-85 as device.                                                                                                                                                                  |

|             |         |                     | Updated ECP5 Family Timing Adders section. Added SSTL135_II buffer<br>type data. Removed LVCMOS33_20mA, LVCMOS25_20mA,<br>LVCMOS25_16mA, LVCMOS25D_16mA, and LVCMOS18_16mA buffer<br>types. Changed buffer type to LVCMOS12_4mA and LVCMOS12_8mA.<br>Updated Maximum I/O Buffer Speed section. Revised Max values. |

|             |         |                     | Updated sysCLOCK PLL Timing section. Revised $t_{DT}$ Min and Max values.<br>Revised $t_{OPJIT}$ Max value. Revised number of samples in table note 1.                                                                                                                                                             |

|             |         |                     | Updated SERDES High-Speed Data Transmitter section. Updated Table<br>3.24. Serial Output Timing and Levels and Table 3.25. Channel Output<br>Jitter.                                                                                                                                                               |

#### (Continued)

| Date        | Version | Section                             | Change Summary                                                                                                                                                                                                                               |

|-------------|---------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| August 2014 | 1.2     | DC and Switching<br>Characteristics | SERDES High-Speed Data Receiver section. Updated Table 3.26. Serial<br>Input Data Specifications, Table 3.28. Receiver Total Jitter Tolerance<br>Specification, and Table 3.29. External Reference Clock Specification<br>(refclkp/refclkn). |

|             |         |                                     | Modified section heading to XXAUI/CPRI LV E.30 Electrical and Timing<br>Characteristics. Updated Table 3.33 Transmit and Table 3.34. Receive<br>and Jitter Tolerance.                                                                        |

|             |         |                                     | Modified section heading to CPRI LV E.24 Electrical and Timing<br>Characteristics. Updated Table 3.35. Transmit and Table 3.36. Receive<br>and Jitter Tolerance.                                                                             |

|             |         |                                     | Modified section heading to Gigabit Ethernet/SGMII/CPRI LV E.12<br>Electrical and Timing Characteristics. Updated Table 3.37. Transmit and<br>Table 3.38. Receive and Jitter Tolerance.                                                      |

| June 2014   | 1.1     | Ordering Information                | Updated ECP5/ECP5-5G Part Number Description and Ordering Part Numbers sections.                                                                                                                                                             |

| March 2014  | 1.0     | All                                 | Initial release.                                                                                                                                                                                                                             |