# E. Lattice Semiconductor Corporation - LFE5UM-85F-8BG756C Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                        |

|--------------------------------|-------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 21000                                                                         |

| Number of Logic Elements/Cells | 84000                                                                         |

| Total RAM Bits                 | 3833856                                                                       |

| Number of I/O                  | 365                                                                           |

| Number of Gates                | -                                                                             |

| Voltage - Supply               | 1.045V ~ 1.155V                                                               |

| Mounting Type                  | Surface Mount                                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                               |

| Package / Case                 | 756-FBGA                                                                      |

| Supplier Device Package        | 756-CABGA (27x27)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe5um-85f-8bg756c |

|                                |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. General Description

The ECP5/ECP5-5G family of FPGA devices is optimized to deliver high performance features such as an enhanced DSP architecture, high speed SERDES (Serializer/Deserializer), and high speed source synchronous interfaces, in an economical FPGA fabric. This combination is achieved through advances in device architecture and the use of 40 nm technology making the devices suitable for high-volume, highspeed, and low-cost applications.

The ECP5/ECP5-5G device family covers look-up-table (LUT) capacity to 84K logic elements and supports up to 365 user I/Os. The ECP5/ECP5-5G device family also offers up to 156 18 x 18 multipliers and a wide range of parallel I/O standards.

The ECP5/ECP5-5G FPGA fabric is optimized high performance with low power and low cost in mind. The ECP5/ ECP5-5G devices utilize reconfigurable SRAM logic technology and provide popular building blocks such as LUT-based logic, distributed and embedded memory, Phase-Locked Loops (PLLs), Delay-Locked Loops (DLLs), pre-engineered source synchronous I/O support, enhanced sysDSP slices and advanced configuration support, including encryption and dual-boot capabilities.

The pre-engineered source synchronous logic implemented in the ECP5/ECP5-5G device family supports a broad range of interface standards including DDR2/3, LPDDR2/3, XGMII, and 7:1 LVDS.

The ECP5/ECP5-5G device family also features high speed SERDES with dedicated Physical Coding Sublayer (PCS) functions. High jitter tolerance and low transmit jitter allow the SERDES plus PCS blocks to be configured to support an array of popular data protocols including PCI Express, Ethernet (XAUI, GbE, and SGMII) and CPRI. Transmit De-emphasis with pre- and post-cursors, and Receive Equalization settings make the SERDES suitable for transmission and reception over various forms of media.

The ECP5/ECP5-5G devices also provide flexible, reliable and secure configuration options, such as dual-boot capability, bit-stream encryption, and TransFR field upgrade features.

ECP5-5G family devices have made some enhancement in the SERDES compared to ECP5UM devices. These enhancements increase the performance of the SERDES to up to 5 Gb/s data rate.

The ECP5-5G family devices are pin-to-pin compatible with the ECP5UM devices. These allows a migration path for users to port designs from ECP5UM to ECP5-5G devices to get higher performance. The Lattice Diamond<sup>™</sup> design software allows large complex designs to be efficiently implemented using the ECP5/ECP5-5G FPGA family. Synthesis library support for ECP5/ECP5-5G devices is available for popular logic synthesis tools. The Diamond tools use the synthesis tool output along with the constraints from its floor planning tools to place and route the design in the ECP5/ECP5-5G device. The tools extract the timing from the routing and back-annotate it into the design for timing verification.

Lattice provides many pre-engineered IP (Intellectual Property) modules for the ECP5/ECP5-5G family. By using these configurable soft core IPs as standardized blocks, designers are free to concentrate on the unique aspects of their design, increasing their productivity.

## 1.1. Features

- Higher Logic Density for Increased System Integration

- 12K to 84K LUTs

- 197 to 365 user programmable I/Os

- Embedded SERDES

- 270 Mb/s, up to 3.2 Gb/s, SERDES interface (ECP5)

- 270 Mb/s, up to 5.0 Gb/s, SERDES interface (ECP5-5G)

- Supports eDP in RDR (1.62 Gb/s) and HDR (2.7 Gb/s)

- Up to four channels per device: PCI Express, Ethernet (1GbE, SGMII, XAUI), and CPRI

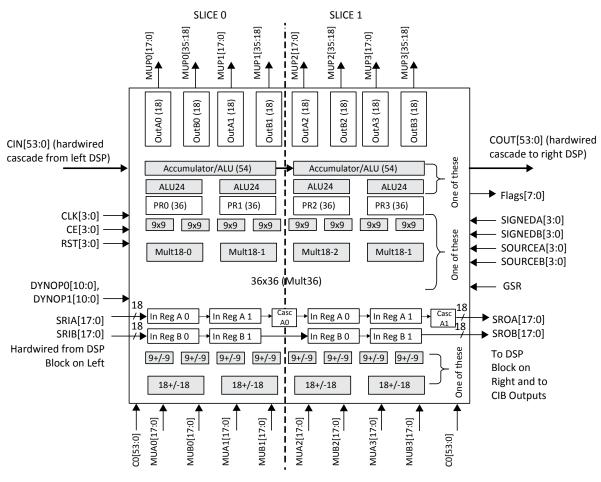

- sysDSP™

- Fully cascadable slice architecture

- 12 to 160 slices for high performance multiply and accumulate

- Powerful 54-bit ALU operations

- Time Division Multiplexing MAC Sharing

- Rounding and truncation

- Each slice supports

- Half 36 x 36, two 18 x 18 or four 9 x 9 multipliers

- Advanced 18 x 36 MAC and 18 x 18 Multiply-Multiply-Accumulate (MMAC) operations

- Flexible Memory Resources

- Up to 3.744 Mb sysMEM<sup>™</sup> Embedded Block RAM (EBR)

- 194K to 669K bits distributed RAM

- sysCLOCK Analog PLLs and DLLs

| Table 2.4 provides a description | of the signals in the PLL blocks. |

|----------------------------------|-----------------------------------|

|----------------------------------|-----------------------------------|

| Signal        | Туре   | Description                                                                     |

|---------------|--------|---------------------------------------------------------------------------------|

| CLKI          | Input  | Clock Input to PLL from external pin or routing                                 |

| CLKI2         | Input  | Muxed clock input to PLL                                                        |

| SEL           | Input  | Input Clock select, selecting from CLKI and CLKI2 inputs                        |

| CLKFB         | Input  | PLL Feedback Clock                                                              |

| PHASESEL[1:0] | Input  | Select which output to be adjusted on Phase by PHASEDIR, PHASESTEP, PHASELODREG |

| PHASEDIR      | Input  | Dynamic Phase adjustment direction.                                             |

| PHASESTEP     | Input  | Dynamic Phase adjustment step.                                                  |

| PHASELOADREG  | Input  | Load dynamic phase adjustment values into PLL.                                  |

| CLKOP         | Output | Primary PLL output clock (with phase shift adjustment)                          |

| CLKOS         | Output | Secondary PLL output clock (with phase shift adjust)                            |

| CLKOS2        | Output | Secondary PLL output clock2 (with phase shift adjust)                           |

| CLKOS3        | Output | Secondary PLL output clock3 (with phase shift adjust)                           |

| LOCK          | Output | PLL LOCK to CLKI, Asynchronous signal. Active high indicates PLL lock           |

| STDBY         | Input  | Standby signal to power down the PLL                                            |

| RST           | Input  | Resets the PLL                                                                  |

| ENCLKOP       | Input  | Enable PLL output CLKOP                                                         |

| ENCLKOS       | Input  | Enable PLL output CLKOS                                                         |

| ENCLKOS2      | Input  | Enable PLL output CLKOS2                                                        |

| ENCLKOS3      | Input  | Enable PLL output CLKOS3                                                        |

#### Table 2.4. PLL Blocks Signal Descriptions

For more details on the PLL you can refer to the ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263).

# 2.5. Clock Distribution Network

There are two main clock distribution networks for any member of the ECP5/ECP5-5G product family, namely Primary Clock (PCLK) and Edge Clock (ECLK). These clock networks have the clock sources come from many different sources, such as Clock Pins, PLL outputs, DLLDEL outputs, Clock divider outputs, SERDES/PCS clocks and some on chip generated clock signal. There are clock dividers (CLKDIV) blocks to provide the slower clock from these clock sources. ECP5/ECP5-5G also supports glitchless dynamic enable function (DCC) for the PCLK Clock to save dynamic power. There are also some logics to allow dynamic glitchless selection between two clocks for the PCLK network (DCS).

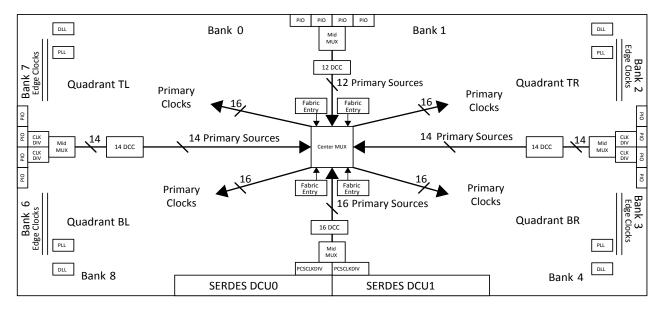

Overview of Clocking Network is shown in Figure 2.6 on page 20 for LFE5UM/LFE5UM5G-85 device.

Figure 2.6. LFE5UM/LFE5UM5G-85 Clocking

### 2.5.1. Primary Clocks

The ECP5/ECP5-5G device family provides low-skew, high fan-out clock distribution to all synchronous elements in the FPGA fabric through the Primary Clock Network.

The primary clock network is divided into four clocking quadrants: Top Left (TL), Bottom Left (BL), Top Right (TR), and Bottom Right (BR). Each of these quadrants has 16 clocks that can be distributed to the fabric in the quadrant.

The Lattice Diamond software can automatically route each clock to one of the four quadrants up to a maximum of 16 clocks per quadrant. The user can change how the clocks are routed by specifying a preference in the Lattice Diamond software to locate the clock to specific. The ECP5/ECP5-5G device provides the user with a maximum of 64 unique clock input sources that can be routed to the primary Clock network.

Primary clock sources are:

- Dedicated clock input pins

- PLL outputs

- CLKDIV outputs

- Internal FPGA fabric entries (with minimum general routing)

- SERDES/PCS/PCSDIV clocks

- OSC clock

These sources are routed to one of four clock switches called a Mid Mux. The outputs of the Mid MUX are routed to the center of the FPGA where another clock switch, called the Center MUX, is used to route the primary clock sources to primary clock distribution to the ECP5/ECP5-5G fabric. These routing muxes are shown in Figure 2.6. Since there is a maximum of 60 unique clock input sources to the clocking quadrants, there are potentially 64 unique clock domains that can be used in the ECP5/ECP5-5G Device. For more information about the primary clock tree and connections, refer to ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263).

#### 2.5.1.1. Dynamic Clock Control

The Dynamic Clock Control (DCC), Quadrant Clock enable/disable feature allows internal logic control of the quadrant primary clock network. When a clock network is disabled, the clock signal is static and not toggle. All the logic fed by that clock will not toggle, reducing the overall power consumption of the device. The disable function will not create glitch and increase the clock latency to the primary clock network.

This DCC controls the clock sources from the Primary CLOCK MIDMUX before they are fed to the Primary Center MUXs that drive the quadrant clock network. For more information about the DCC, refer to ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263).

- 5\*5 and larger size 2D blocks Semi internal DSP Slice support

- Flexible saturation and rounding options to satisfy a diverse set of applications situations

- Flexible cascading across DSP slices

- Minimizes fabric use for common DSP and ALU functions

- Enables implementation of FIR Filter or similar structures using dedicated sysDSP slice resources only

- Provides matching pipeline registers

- Can be configured to continue cascading from one row of sysDSP slices to another for longer cascade chains

- Flexible and Powerful Arithmetic Logic Unit (ALU) Supports:

- Dynamically selectable ALU OPCODE

- Ternary arithmetic (addition/subtraction of three inputs)

- Bit-wise two-input logic operations (AND, OR, NAND, NOR, XOR and XNOR)

- Eight flexible and programmable ALU flags that can be used for multiple pattern detection scenarios, such as, overflow, underflow and convergent rounding.

- Flexible cascading across slices to get larger functions

- RTL Synthesis friendly synchronous reset on all registers, while still supporting asynchronous reset for legacy users

- Dynamic MUX selection to allow Time Division Multiplexing (TDM) of resources for applications that require processor-like flexibility that enables different functions for each clock cycle

For most cases, as shown in Figure 2.14, the ECP5/ECP5-5G sysDSP slice is backwards-compatible with the LatticeECP2<sup>™</sup> and LatticeECP3<sup>™</sup> sysDSP block, such that, legacy applications can be targeted to the ECP5/ECP5-5G sysDSP slice. Figure 2.14 shows the diagram of sysDSP, and Figure 2.15 shows the detailed diagram.

Figure 2.14. Simplified sysDSP Slice Block Diagram

# 2.14. sysl/O Buffer

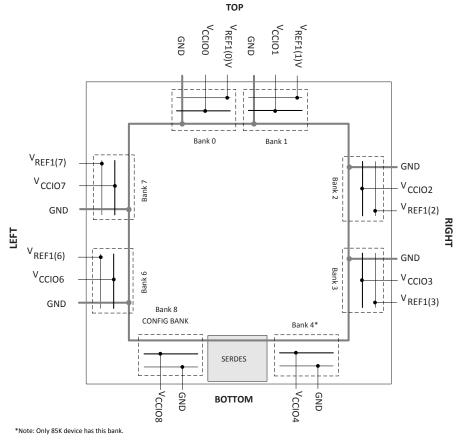

Each I/O is associated with a flexible buffer referred to as a sysI/O buffer. These buffers are arranged around the periphery of the device in groups referred to as banks. The sysI/O buffers allow users to implement the wide variety of standards that are found in today's systems including LVDS, HSUL, BLVDS, SSTL Class I and II, LVCMOS, LVTTL, LVPECL, and MIPI.

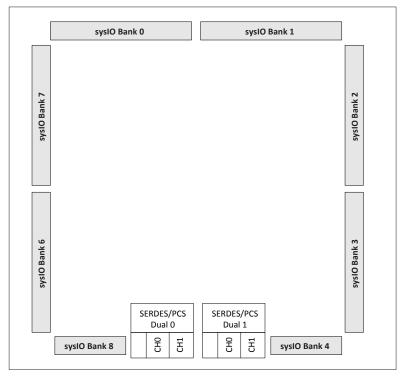

### 2.14.1. sysl/O Buffer Banks

ECP5/ECP5-5G devices have seven sysI/O buffer banks, two banks per side at Top, Left and Right, plus one at the bottom left side. The bottom left side bank (Bank 8) is a shared I/O bank. The I/Os in that bank contains both dedicated and shared I/O for sysConfig function. When a shared pin is not used for configuration, it is available as a user I/O. For LFE5-85 devices, there is an additional I/O bank (Bank 4) that is not available in other device in the family.

In ECP5/ECP5-5G devices, the Left and Right sides are tailored to support high performance interfaces, such as DDR2, DDR3, LPDDR2, LPDDR3 and other high speed source synchronous standards. The banks on the Left and Right sides of the devices feature LVDS input and output buffers, data-width gearing, and DQSBUF block to support DDR2/3 and LPDDR2/3 interfaces. The I/Os on the top and bottom banks do not have LVDS input and output buffer, and gearing logic, but can use LVCMOS to emulate most of differential output signaling.

Each sysIO bank has its own I/O supply voltage ( $V_{CCIO}$ ). In addition, the banks on the Left and Right sides of the device, have voltage reference input (shared I/O pin), VREF1 per bank, which allow it to be completely independent of each other. The  $V_{REF}$  voltage is used to set the threshold for the referenced input buffers, such as SSTL. Figure 2.25 shows the seven banks and their associated supplies.

In ECP5/ECP5-5G devices, single-ended output buffers and ratioed input buffers (LVTTL, and LVCMOS) are powered using  $V_{CCIO}$ . LVTTL, LVCMOS33, LVCMOS25 and LVCMOS12 can also be set as fixed threshold inputs independent of  $V_{CCIO}$ .

Figure 2.27. SERDES/PCS Duals (LFE5UM/LFE5UM5G-85)

| Standard                                       | Data Rate (Mb/s)                                           | Number of General/Link Width | Encoding Style |

|------------------------------------------------|------------------------------------------------------------|------------------------------|----------------|

| PCI Express 1.1 and 2.0                        | 2500                                                       | x1, x2, x4                   | 8b10b          |

| 2.02                                           | 5000 <sup>2</sup>                                          | x1, x2                       | 8b10b          |

| Gigabit Ethernet                               | 1250                                                       | x1                           | 8b10b          |

| COMU                                           | 1250                                                       | x1                           | 8b10b          |

| SGMII                                          | 2500                                                       | x1                           | 8b10b          |

| XAUI                                           | 3125                                                       | x4                           | 8b10b          |

| CPRI-1<br>CPRI-2<br>CPRI-3<br>CPRI-4<br>CPRI-5 | 614.4<br>1228.8<br>2457.6<br>3072.0<br>4915.2 <sup>2</sup> | x1                           | 8b10b          |

| SD-SDI (259M, 344M) 1                          | 270                                                        | x1                           | NRZI/Scrambled |

| HD-SDI (292M)                                  | 1483.5<br>1485                                             | x1                           | NRZI/Scrambled |

| 3G-SDI (424M)                                  | 2967<br>2970                                               | x1                           | NRZI/Scrambled |

|                                                | 5000                                                       | _                            | _              |

| JESD204A/B                                     | 3125                                                       | x1                           | 8b/10b         |

#### Notes:

1. For SD-SDI rate, the SERDES is bypassed and SERDES input signals are directly connected to the FPGA routing.

2. For ECP5-5G family devices only.

| Package    | LFE5UM/LFE5UM5G-25 | LFE5UM/LFE5UM5G-45 | LFE5UM/LFE5UM5G-85 |

|------------|--------------------|--------------------|--------------------|

| 285 csfBGA | 1                  | 1                  | 1                  |

| 381 caBGA  | 1                  | 2                  | 2                  |

| 554 caBGA  | -                  | 2                  | 2                  |

| 756 caBGA  | -                  | -                  | 2                  |

#### Table 2.14. Available SERDES Duals per LFE5UM/LFE5UM5G Devices

### 2.15.1. SERDES Block

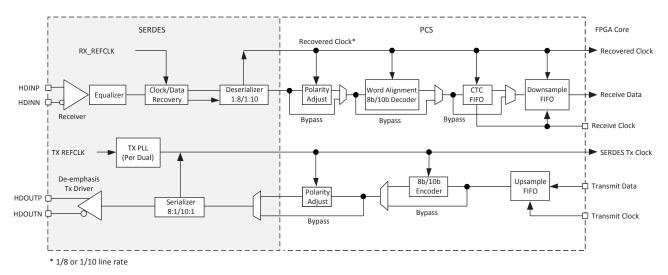

A SERDES receiver channel may receive the serial differential data stream, equalize the signal, perform Clock and Data Recovery (CDR) and de-serialize the data stream before passing the 8- or 10-bit data to the PCS logic. The SERDES transmitter channel may receive the parallel 8- or 10-bit data, serialize the data and transmit the serial bit stream through the differential drivers. Figure 2.28 shows a single-channel SERDES/PCS block. Each SERDES channel provides a recovered clock and a SERDES transmit clock to the PCS block and to the FPGA core logic.

Each transmit channel, receiver channel, and SERDES PLL shares the same power supply (VCCA). The output and input buffers of each channel have their own independent power supplies (VCCHTX and VCCHRX).

Figure 2.28. Simplified Channel Block Diagram for SERDES/PCS Block

### 2.15.2. PCS

As shown in Figure 2.28, the PCS receives the parallel digital data from the deserializer and selects the polarity, performs word alignment, decodes (8b/10b), provides Clock Tolerance Compensation and transfers the clock domain from the recovered clock to the FPGA clock via the Down Sample FIFO.

For the transmit channel, the PCS block receives the parallel data from the FPGA core, encodes it with 8b/10b, selects the polarity and passes the 8/10 bit data to the transmit SERDES channel.

The PCS also provides bypass modes that allow a direct 8-bit or 10-bit interface from the SERDES to the FPGA logic. The PCS interface to the FPGA can also be programmed to run at 1/2 speed for a 16-bit or 20-bit interface to the FPGA logic. Some of the enhancements in LFE5UM/LFE5UM5G SERDES/PCS include:

- Higher clock/channel granularity: Dual channel architecture provides more clock resource per channel.

- Enhanced Tx de-emphasis: Programmable pre- and post-cursors improves Tx output signaling

- Bit-slip function in PCS: Improves logic needed to perform Word Alignment function

Refer to ECP5 and ECP5-5G SERDES/PCS Usage Guide (TN1261) for more information.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# 3.7. Hot Socketing Requirements

#### **Table 3.6. Hot Socketing Requirements**

| Description                                                                               | Min | Тур | Max | Unit |

|-------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Input current per SERDES I/O pin when device is powered down and inputs driven.           | _   | _   | 8   | mA   |

| Input current per HDIN pin when device power supply is off, inputs driven <sup>1, 2</sup> | _   | _   | 15  | mA   |

| Current per HDIN pin when device power ramps up, input driven <sup>3</sup>                | _   | _   | 50  | mA   |

| Current per HDOUT pin when device power supply is off, outputs pulled up <sup>4</sup>     | —   | —   | 30  | mA   |

Notes:

1. Device is powered down with all supplies grounded, both HDINP and HDINN inputs driven by a CML driver with maximum allowed output V<sub>CCHTX</sub>, 8b/10b data, no external AC coupling.

2. Each P and N input must have less than the specified maximum input current during hot plug. For a device with 2 DCU, the total input current would be 15 mA \* 4 channels \* 2 input pins per channel = 120 mA.

- Device power supplies are ramping up (V<sub>CCA</sub> and V<sub>CCAUX</sub>), both HDINP and HDINN inputs are driven by a CML driver with maximum allowed output V<sub>CCHTX</sub>, 8b/10b data, internal AC coupling.

- 4. Device is powered down with all supplies grounded. Both HDOUTP and HDOUN outputs are pulled up to  $V_{CCHTX}$  by the far end receiver termination of 50  $\Omega$  single ended.

## 3.8. ESD Performance

Refer to the ECP5 and ECP5-5G Product Family Qualification Summary for complete qualification data, including ESD performance.

# 3.9. DC Electrical Characteristics

**Over Recommended Operating Conditions**

| Symbol                                            | Parameter                                                        | Condition                                                                                                                                             | Min | Тур | Max  | Unit |

|---------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| I <sub>IL</sub> , I <sub>IH</sub> <sup>1, 4</sup> | Input or I/O Low Leakage                                         | $0 \leq V_{\text{IN}} \leq V_{\text{CCIO}}$                                                                                                           | _   | —   | 10   | μA   |

| I <sub>IH</sub> <sup>1, 3</sup>                   | Input or I/O High Leakage                                        | $V_{CCIO} < V_{IN} \leq V_{IH(MAX)}$                                                                                                                  | —   | —   | 100  | μA   |

| I                                                 | I/O Active Pull-up Current,<br>sustaining logic HIGH state       | $0.7 \: V_{CCIO} \! \leq \! V_{IN} \! \leq \! V_{CCIO}$                                                                                               | -30 | _   | _    | μA   |

| I <sub>PU</sub>                                   | I/O Active Pull-up Current, pulling down from logic HIGH state   | $0 \leq V_{\text{IN}} \leq 0.7 \; V_{\text{CCIO}}$                                                                                                    |     | _   | -150 | μA   |

| IPD                                               | I/O Active Pull-down Current,<br>sustaining logic LOW state      | $0 \le V_{IN} \le V_{IL}$ (MAX)                                                                                                                       | 30  | —   | —    | μA   |

| IDD                                               | I/O Active Pull-down Current,<br>pulling up from logic LOW state | $0 \leq V_{IN} \leq V_{CCIO}$                                                                                                                         | _   | —   | 150  | μA   |

| C1                                                | I/O Capacitance <sup>2</sup>                                     | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V}, \\ V_{CC} = 1.2 \text{ V}, V_{IO} = 0 \text{ to } V_{IH(MAX)}$ | _   | 5   | 8    | pf   |

| C2                                                | Dedicated Input Capacitance <sup>2</sup>                         | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V}, \\ V_{CC} = 1.2 \text{ V}, V_{IO} = 0 \text{ to } V_{IH(MAX)}$ | _   | 5   | 7    | pf   |

| V                                                 | Hysteresis for Single-Ended                                      | V <sub>CCIO</sub> = 3.3 V                                                                                                                             | -   | 300 | _    | mV   |

| V <sub>HYST</sub>                                 | Inputs                                                           | V <sub>CCIO</sub> = 2.5 V                                                                                                                             | _   | 250 | _    | mV   |

#### **Table 3.7. DC Electrical Characteristics**

Notes:

1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tristated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

2. T<sub>A</sub> 25 °C, f = 1.0 MHz.

- 3. Applicable to general purpose I/Os in top and bottom banks.

- 4. When used as  $V_{REF}$ , maximum leakage= 25  $\mu$ A.

### 3.14.4. LVDS25E

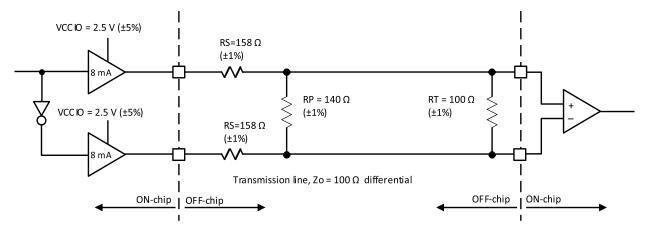

The top and bottom sides of ECP5/ECP5-5G devices support LVDS outputs via emulated complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The scheme shown in Figure 3.1 is one possible solution for point-to-point signals.

Figure 3.1. LVDS25E Output Termination Example

#### Table 3.14. LVDS25E DC Conditions

| Parameter         | Description                    | Typical | Unit |

|-------------------|--------------------------------|---------|------|

| V <sub>CCIO</sub> | Output Driver Supply (±5%)     | 2.50    | V    |

| Z <sub>OUT</sub>  | Driver Impedance               | 20      | Ω    |

| Rs                | Driver Series Resistor (±1%)   | 158     | Ω    |

| R <sub>P</sub>    | Driver Parallel Resistor (±1%) | 140     | Ω    |

| R <sub>T</sub>    | Receiver Termination (±1%)     | 100     | Ω    |

| V <sub>OH</sub>   | Output High Voltage            | 1.43    | V    |

| V <sub>OL</sub>   | Output Low Voltage             | 1.07    | V    |

| V <sub>OD</sub>   | Output Differential Voltage    | 0.35    | V    |

| V <sub>CM</sub>   | Output Common Mode Voltage     | 1.25    | V    |

| ZBACK             | Back Impedance                 | 100.5   | Ω    |

| I <sub>DC</sub>   | DC Output Current              | 6.03    | mA   |

Note: For input buffer, see LVDS Table 3.13 on page 55.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

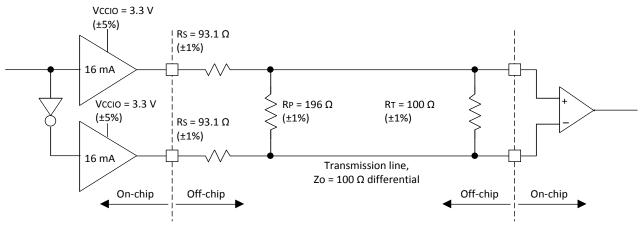

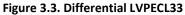

### 3.14.6. LVPECL33

The ECP5/ECP5-5G devices support the differential LVPECL standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The LVPECL input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3.3 is one possible solution for point-to-point signals.

Over recommended operating conditions.

| Parameter         | Description                    | Typical | Unit |

|-------------------|--------------------------------|---------|------|

| V <sub>CCIO</sub> | Output Driver Supply (±5%)     | 3.30    | V    |

| Z <sub>OUT</sub>  | Driver Impedance               | 10      | Ω    |

| Rs                | Driver Series Resistor (±1%)   | 93      | Ω    |

| R <sub>P</sub>    | Driver Parallel Resistor (±1%) | 196     | Ω    |

| R <sub>T</sub>    | Receiver Termination (±1%)     | 100     | Ω    |

| V <sub>OH</sub>   | Output High Voltage            | 2.05    | V    |

| V <sub>OL</sub>   | Output Low Voltage             | 1.25    | V    |

| V <sub>OD</sub>   | Output Differential Voltage    | 0.80    | V    |

| V <sub>CM</sub>   | Output Common Mode Voltage     | 1.65    | V    |

| ZBACK             | Back Impedance                 | 100.5   | Ω    |

| I <sub>DC</sub>   | DC Output Current              | 12.11   | mA   |

#### Table 3.16. LVPECL33 DC Conditions

Note: For input buffer, see LVDS Table 3.13 on page 55.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

| Damamatar                                | Description                                                      | Device         |          | -8        | -         | -7       | -          | -6         | Unit             |

|------------------------------------------|------------------------------------------------------------------|----------------|----------|-----------|-----------|----------|------------|------------|------------------|

| Parameter                                | Description                                                      | Device         | Min      | Max       | Min       | Max      | Min        | Max        |                  |

| t <sub>h_delpll</sub>                    | Clock to Data Hold - PIO Input<br>Register with Data Input Delay | All Devices    | 0        | -         | 0         | -        | 0          | -          | ns               |

| Generic DDR Input                        |                                                                  |                |          |           |           |          |            |            |                  |

| Generic DDRX1 Inp                        | uts With Clock and Data Centere                                  | d at Pin (GDDI | RX1_RX.S | CLK.Cen   | tered) Us | ing PCLk | Clock In   | put - Fig  | ure 3.6          |

| t <sub>SU_GDDRX1_centered</sub>          | Data Setup Before CLK Input                                      | All Devices    | 0.52     | -         | 0.52      | -        | 0.52       | -          | ns               |

| $t_{HD_GDDRX1_centered}$                 | Data Hold After CLK Input                                        | All Devices    | 0.52     | _         | 0.52      | _        | 0.52       | _          | ns               |

| $f_{DATA\_GDDRX1\_centered}$             | GDDRX1 Data Rate                                                 | All Devices    | _        | 500       | —         | 500      | —          | 500        | Mb/s             |

| $f_{MAX\_GDDRX1\_centered}$              | GDDRX1 CLK Frequency (SCLK)                                      | All Devices    | _        | 250       | —         | 250      | _          | 250        | MHz              |

| Generic DDRX1 Inp                        | uts With Clock and Data Aligned                                  | at Pin (GDDR)  | (1_RX.SC | LK.Aligne | ed) Using | PCLK Cl  | ock Input  | t - Figure | 3.7              |

| $t_{SU\_GDDRX1\_aligned}$                | Data Setup from CLK Input                                        | All Devices    | -        | -0.55     | -         | -0.55    | -          | -0.55      | ns +<br>1/2 UI   |

| $t_{HD\_GDDRX1\_aligned}$                | Data Hold from CLK Input                                         | All Devices    | 0.55     | -         | 0.55      | -        | 0.55       | _          | ns +<br>1/2 U    |

| $f_{DATA_GDDRX1_aligned}$                | GDDRX1 Data Rate                                                 | All Devices    | —        | 500       | —         | 500      | —          | 500        | Mb/s             |

| $f_{MAX_GDDRX1_aligned}$                 | GDDRX1 CLK Frequency (SCLK)                                      | All Devices    | _        | 250       | —         | 250      | —          | 250        | MHz              |

| Generic DDRX2 Inp                        | uts With Clock and Data Centere                                  | d at Pin (GDDI | RX2_RX.E | CLK.Cen   | tered) Us | ing PCLK | Clock In   | put, Left  | and              |

| Right sides Only - F                     |                                                                  | T              |          |           |           | 1        | 1          |            |                  |

| $t_{SU_GDDRX2_centered}$                 | Data Setup before CLK Input                                      | All Devices    | 0.321    | —         | 0.403     | _        | 0.471      | _          | ns               |

| $t_{HD\_GDDRX2\_centered}$               | Data Hold after CLK Input                                        | All Devices    | 0.321    | _         | 0.403     | _        | 0.471      | _          | ns               |

| $f_{DATA\_GDDRX2\_centered}$             | GDDRX2 Data Rate                                                 | All Devices    | —        | 800       | —         | 700      | —          | 624        | Mb/s             |

| $f_{MAX\_GDDRX2\_centered}$              | GDDRX2 CLK Frequency (ECLK)                                      | All Devices    | -        | 400       | -         | 350      | -          | 312        | MHz              |

| Generic DDRX2 Inp<br>sides Only - Figure | uts With Clock and Data Aligned 3.7                              | at Pin (GDDR)  | (2_RX.EC | LK.Aligne | ed) Using | PCLK Cl  | ock Input  | t, Left an | d Right          |

| $t_{su\_GDDRX2\_aligned}$                | Data Setup from CLK Input                                        | All Devices    | -        | -0.344    | —         | -0.42    | -          | -0.495     | ns + 1/2<br>UI   |

| $t_{HD}_{GDDRX2}_{aligned}$              | Data Hold from CLK Input                                         | All Devices    | 0.344    | —         | 0.42      | _        | 0.495      | —          | ns + 1/2<br>UI   |

| $f_{DATA\_GDDRX2\_aligned}$              | GDDRX2 Data Rate                                                 | All Devices    | —        | 800       | —         | 700      | _          | 624        | Mb/s             |

| $f_{MAX\_GDDRX2\_aligned}$               | GDDRX2 CLK Frequency                                             | All Devices    |          | 400       | —         | 350      | _          | 312        | MHz              |

| Video DDRX71 Inpu<br>Figure 3.11         | its With Clock and Data Aligned a                                | at Pin (GDDRX  | 71_RX.E0 | CLK) Usin | g PLL Clo | ck Input | , Left and | l Right si | des Only         |

| t <sub>su_lvds71_i</sub>                 | Data Setup from CLK Input<br>(bit i)                             | All Devices    | _        | -0.271    | _         | -0.39    | _          | -0.41      | ns+(1/2+<br>* UI |

| thd_lvds71_i                             | Data Hold from CLK Input<br>(bit i)                              | All Devices    | 0.271    | _         | 0.39      | -        | 0.41       | _          | ns+(1/2+<br>* UI |

| f <sub>DATA_LVDS71</sub>                 | DDR71 Data Rate                                                  | All Devices    | 1        | 756       | —         | 620      | -          | 525        | Mb/s             |

| f <sub>MAX_LVDS71</sub>                  | DDR71 CLK Frequency (ECLK)                                       | All Devices    |          | 378       | _         | 310      | _          | 262.5      | MHz              |

#### Table 3.22. ECP5/ECP5-5G External Switching Characteristics (Continued)

#### Table 3.22. ECP5/ECP5-5G External Switching Characteristics (Continued)

|                                                                                                                               | ECP5-5G External Switching Cr            |                 | -8 -7 -6   |           |            |            | <u>,</u>   |            |                  |

|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------|------------|-----------|------------|------------|------------|------------|------------------|

| Parameter                                                                                                                     | Description                              | Device          | Min        | -o<br>Max | Min        | Max        | Min        | -o<br>Max  | Unit             |

| Generic DDR Outp                                                                                                              | ut                                       |                 |            |           |            |            |            |            |                  |

| •                                                                                                                             | tputs With Clock and Data Cente          | red at Pin (GD  | DRX1_TX    | .SCLK.Ce  | ntered) l  | Jsing PCL  | K Clock Ir | nput - Fig | ure 3.6          |

| $t_{\text{DVB}\_\text{GDDRX1}\_\text{centered}}$                                                                              | Data Output Valid before CLK<br>Output   | All Devices     | -0.67      | _         | -0.67      | -          | -0.67      | _          | ns +<br>1/2 UI   |

| $t_{\text{DVA}_{GDDRX1}_{centered}}$                                                                                          | Data Output Valid after CLK<br>Output    | All Devices     | -0.67      | _         | -0.67      | _          | -0.67      | _          | ns +<br>1/2 UI   |

| f <sub>DATA_GDDRX1_centered</sub>                                                                                             | GDDRX1 Data Rate                         | All Devices     | _          | 500       | —          | 500        | _          | 500        | Mb/s             |

| f <sub>MAX_GDDRX1_centered</sub>                                                                                              | GDDRX1 CLK Frequency (SCLK)              | All Devices     | _          | 250       | _          | 250        | _          | 250        | MHz              |

| Generic DDRX1 Ou                                                                                                              | tputs With Clock and Data Aligne         | ed at Pin (GDDI | RX1_TX.9   | CLK.Alig  | ned) Usin  | g PCLK C   | lock Inpu  | t - Figure | 3.9              |

| $t_{DIB\_GDDRX1\_aligned}$                                                                                                    | Data Output Invalid before<br>CLK Output | All Devices     | -0.3       | _         | -0.3       | _          | -0.3       | _          | ns               |

| $t_{\text{DIA}_{GDDRX1}_{aligned}}$                                                                                           | Data Output Invalid after CLK<br>Output  | All Devices     | _          | 0.3       | —          | 0.3        | -          | 0.3        | ns               |

| $f_{DATA\_GDDRX1\_aligned}$                                                                                                   | GDDRX1 Data Rate                         | All Devices     | _          | 500       | —          | 500        | —          | 500        | Mb/s             |

| $f_{MAX\_GDDRX1\_aligned}$                                                                                                    | GDDRX1 CLK Frequency (SCLK)              | All Devices     | _          | 250       | —          | 250        | —          | 250        | MHz              |

| Generic DDRX2 Ou                                                                                                              | tputs With Clock and Data Cente          | red at Pin (GD  | DRX2_TX    | .ECLK.Ce  | ntered) l  | Jsing PCL  | K Clock Iı | nput, Left | and              |

| Right sides Only -                                                                                                            | igure 3.8                                |                 |            |           |            | 1          | 1          |            | 1                |

| $t_{\text{DVB}_{GDDRX2}_{centered}}$                                                                                          | Data Output Valid Before CLK<br>Output   | All Devices     | -<br>0.442 | —         | -0.56      | _          | –<br>0.676 | —          | ns +<br>1/2 UI   |

| $t_{\text{DVA}_{GDDRX2}_{centered}}$                                                                                          | Data Output Valid After CLK<br>Output    | All Devices     | _          | 0.442     | _          | 0.56       | _          | 0.676      | ns +<br>1/2 UI   |

| $f_{\text{DATA}\_\text{GDDRX2}\_\text{centered}}$                                                                             | GDDRX2 Data Rate                         | All Devices     | —          | 800       | —          | 700        | —          | 624        | Mb/s             |

| $f_{MAX\_GDDRX2\_centered}$                                                                                                   | GDDRX2 CLK Frequency (ECLK)              | All Devices     | —          | 400       | —          | 350        | —          | 312        | MHz              |

| Generic DDRX2 Ou<br>sides Only - Figure                                                                                       | tputs With Clock and Data Aligne         | ed at Pin (GDDI | RX2_TX.E   | CLK.Alig  | ned) Usin  | g PCLK C   | lock Inpu  | t, Left an | d Right          |

| t <sub>DIB_GDDRX2_aligned</sub>                                                                                               | Data Output Invalid before<br>CLK Output | All Devices     | -0.16      | _         | -0.18      | -          | -0.2       | _          | ns               |

| $t_{\text{DIA}\_\text{GDDRX2}\_\text{aligned}}$                                                                               | Data Output Invalid after CLK<br>Output  | All Devices     | _          | 0.16      | _          | 0.18       | _          | 0.2        | ns               |

| $f_{DATA\_GDDRX2\_aligned}$                                                                                                   | GDDRX2 Data Rate                         | All Devices     | _          | 800       | —          | 700        | _          | 624        | Mb/s             |

| $f_{MAX\_GDDRX2\_aligned}$                                                                                                    | GDDRX2 CLK Frequency (ECLK)              | All Devices     | _          | 400       | —          | 350        | _          | 312        | MHz              |

| Video DDRX71 Out                                                                                                              | puts With Clock and Data Aligne          | d at Pin (GDDR  | х71_тх.    | ECLK) Usi | ing PLL Cl | ock Inpu   | t, Left an | d Right si | des Only         |

| - Figure 3.12                                                                                                                 |                                          |                 |            |           |            | 1          | 1          |            |                  |

| t <sub>dib_lvds71_i</sub>                                                                                                     | Data Output Invalid before<br>CLK Output | All Devices     | -0.16      | -         | -0.18      | _          | -0.2       | _          | ns +<br>(i) * UI |

| t <sub>dia_lvds71_i</sub>                                                                                                     | Data Output Invalid after CLK<br>Output  | All Devices     | _          | 0.16      | —          | 0.18       | _          | 0.2        | ns +<br>(i) * UI |

| f <sub>data_lvds71</sub>                                                                                                      | DDR71 Data Rate                          | All Devices     | —          | 756       | _          | 620        | —          | 525        | Mb/s             |

| f <sub>MAX_LVDS71</sub>                                                                                                       | DDR71 CLK Frequency (ECLK)               | All Devices     | _          | 378       | _          | 310        | —          | 262.5      | MHz              |

| Memory Interface                                                                                                              |                                          |                 |            |           |            |            |            |            |                  |

| DDR2/DDR3/DDR3                                                                                                                | IL/LPDDR2/LPDDR3 READ (DQ In             | put Data are A  | ligned to  | DQS)      |            |            |            |            |                  |

| t <sub>DVBDQ_DDR2</sub><br>t <sub>DVBDQ_DDR3</sub><br>t <sub>DVBDQ_DDR3L</sub><br>t <sub>DVBDQ_LPDDR2</sub>                   | Data Output Valid before DQS<br>Input    | All Devices     | _          | -0.26     | _          | –<br>0.317 | _          | –<br>0.374 | ns + 1/2<br>UI   |

| tovbdo_lpddr3<br>tovado_ddr2<br>tovado_ddr3<br>tovado_ddr3<br>tovado_lddr3<br>tovado_lpddr2<br>tovado_lpddr2<br>tovado_lpddr3 | Data Output Valid after DQS<br>Input     | All Devices     | 0.26       |           | 0.317      | _          | 0.374      |            | ns + 1/2<br>UI   |

#### Table 3.22. ECP5/ECP5-5G External Switching Characteristics (Continued)

| Demonstern                                                                                                                              | Description                            | Device      | -      | -8    | -    | -7    |      | -6    |      | -6 |  |

|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------|--------|-------|------|-------|------|-------|------|----|--|

| Parameter                                                                                                                               | Description                            | Device      | Min Mi |       | Min  | Max   | Min  | Max   | Unit |    |  |

| f <sub>data_ddr2</sub><br>f <sub>data_ddr3</sub><br>f <sub>data_ddr3</sub><br>f <sub>data_lpddr2</sub><br>f <sub>data_lpddr3</sub>      | DDR Memory Data Rate                   | All Devices | Ι      | 800   | _    | 700   | _    | 624   | Mb/s |    |  |

| fmax_ddr2<br>fmax_ddr3<br>fmax_ddr3l<br>fmax_lpddr2<br>fmax_lpddr3                                                                      | DDR Memory CLK<br>Frequency (ECLK)     | All Devices | Ι      | 400   | _    | 350   | _    | 312   | MHz  |    |  |

| DDR2/DDR3/DDR3L/LPDDR2/LPDDR3 WRITE (DQ Output Data are Centered to DQS)                                                                |                                        |             |        |       |      |       |      |       |      |    |  |

| t <sub>dqvbs_ddr2</sub><br>t <sub>dqvbs_ddr3</sub><br>t <sub>dqvbs_ddr3</sub><br>t <sub>dqvbs_lpddr2</sub><br>t <sub>dqvbs_lpddr3</sub> | Data Output Valid before<br>DQS Output | All Devices | _      | -0.25 | _    | -0.25 | _    | -0.25 | UI   |    |  |

| tdqvas_ddr2<br>tdqvas_ddr3<br>tdqvas_ddr3l<br>tdqvas_lpddr2<br>tdqvas_lpddr2<br>tdqvas_lpddr3                                           | Data Output Valid after DQS<br>Output  | All Devices | 0.25   | _     | 0.25 | _     | 0.25 | _     | UI   |    |  |

| fdata_ddr2<br>fdata_ddr3<br>fdata_ddr3l<br>fdata_lpddr2<br>fdata_lpddr3                                                                 | DDR Memory Data Rate                   | All Devices | _      | 800   | _    | 700   | _    | 624   | Mb/s |    |  |

| f <sub>MAX_DDR2</sub><br>f <sub>MAX_DDR3</sub><br>f <sub>MAX_DDR3L</sub><br>f <sub>MAX_LPDDR2</sub><br>f <sub>MAX_LPDDR3</sub>          | DDR Memory CLK<br>Frequency (ECLK)     | All Devices | _      | 400   | _    | 350   | _    | 312   | MHz  |    |  |

Notes:

1. Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from the Diamond software.

General I/O timing numbers are based on LVCMOS 2.5, 12 mA, Fast Slew Rate, 0pf load. Generic DDR timing are numbers based on LVDS I/O. DDR2 timing numbers are based on SSTL18. DDR3 timing numbers are based on SSTL15. LPDDR2 and LPDDR3 timing numbers are based on HSUL12.

- 3. Uses LVDS I/O standard for measurements.

- 4. Maximum clock frequencies are tested under best case conditions. System performance may vary upon the user environment.

- 5. All numbers are generated with the Diamond software.

FPGA-DS-02012-1.9

# 3.25.2. PCIe (5 Gb/s) – Preliminary AC and DC Characteristics

Over recommended operating conditions.

#### Table 3.31. PCIe (5 Gb/s)

| Symbol                            | Description                                                 | Test Conditions              | Min    | Тур | Max    | Unit       |

|-----------------------------------|-------------------------------------------------------------|------------------------------|--------|-----|--------|------------|

| Transmit <sup>1</sup>             |                                                             |                              |        |     |        |            |

| UI                                | Unit Interval                                               | —                            | 199.94 | 200 | 200.06 | ps         |

| B <sub>WTX-PKG-PLL2</sub>         | Tx PLL bandwidth corresponding to<br>PKGTX-PLL2             | _                            | 5      | -   | 16     | MHz        |

| P <sub>KGTX-PLL2</sub>            | Tx PLL Peaking                                              | —                            | -      | —   | 1      | dB         |

| V <sub>TX-DIFF-PP</sub>           | Differential p-p Tx voltage swing                           | —                            | 0.8    | _   | 1.2    | V, p-p     |

| V <sub>TX-DIFF-PP-LOW</sub>       | Low power differential p-p Tx voltage swing                 | _                            | 0.4    | _   | 1.2    | V, p-p     |

| V <sub>TX-DE-RATIO-3.5dB</sub>    | Tx de-emphasis level ratio at 3.5dB                         | —                            | 3      | —   | 4      | dB         |

| V <sub>TX-DE-RATIO-6dB</sub>      | Tx de-emphasis level ratio at 6dB                           | —                            | 5.5    | —   | 6.5    | dB         |

| T <sub>MIN-PULSE</sub>            | Instantaneous lone pulse width                              | _                            |        | —   | _      | UI         |

| T <sub>TX-RISE-FALL</sub>         | Transmitter rise and fall time                              | —                            |        | —   | _      | UI         |

| T <sub>TX-EYE</sub>               | Transmitter Eye, including all jitter sources               | _                            | 0.75   | _   | _      | UI         |

| T <sub>TX-DJ</sub>                | Tx deterministic jitter > 1.5 MHz                           | _                            | _      | —   | 0.15   | UI         |

| T <sub>TX-RJ</sub>                | Tx RMS jitter < 1.5 MHz                                     | _                            | _      | _   | 3      | ps,<br>RMS |

| T <sub>RF-MISMATCH</sub>          | Tx rise/fall time mismatch                                  | —                            | _      | —   |        | UI         |

| R <sub>LTX-DIFF</sub>             | Tx Differential Return Loss, including                      |                              | 10     | _   | _      | dB         |

| 'LIX-DIFF                         | package and silicon                                         | 1.25 GHz < freq<br>< 2.5 GHz | 8      | _   | _      | dB         |

| R <sub>LTX-CM</sub>               | Tx Common Mode Return Loss, including package and silicon   | 50 MHz < freq <<br>2.5 GHz   | 6      | _   | _      | dB         |

| Z <sub>TX-DIFF-DC</sub>           | DC differential Impedance                                   | _                            | -      | _   | 120    | Ω          |

| V <sub>TX-CM-AC-PP</sub>          | Tx AC peak common mode voltage, peak-peak                   | -                            | -      | -   |        | mV,<br>p-p |

| I <sub>TX-SHORT</sub>             | Transmitter short-circuit current                           | —                            | _      | —   | 90     | mA         |

| V <sub>TX-DC-CM</sub>             | Transmitter DC common-mode voltage                          | _                            | 0      | -   | 1.2    | V          |

| V <sub>TX-IDLE-DIFF-DC</sub>      | Electrical Idle Output DC voltage                           | —                            | 0      | —   | 5      | mV         |

| V <sub>TX-IDLE-DIFF-AC-p</sub>    | Electrical Idle Differential Output<br>peak voltage         | -                            | _      | -   |        | mV         |

| V <sub>TX-RCV-DETECT</sub>        | Voltage change allowed during<br>Receiver Detect            | _                            | _      | -   | 600    | mV         |

| T <sub>TX-IDLE-MIN</sub>          | Min. time in Electrical Idle                                | —                            | 20     | —   | _      | ns         |

| T <sub>TX-IDLE-SET-TO-IDLE</sub>  | Max. time from El Order Set to valid<br>Electrical Idle     | _                            | _      | _   | 8      | ns         |

| T <sub>TX-IDLE-TO-DIFF-DATA</sub> | Max. time from Electrical Idle to valid differential output | _                            | _      | _   | 8      | ns         |

| L <sub>TX-SKEW</sub>              | Lane-to-lane output skew                                    | _                            | _      | _   |        | ps         |

# 3.31. sysCONFIG Port Timing Specifications

Over recommended operating conditions.

#### Table 3.42. ECP5/ECP5-5G sysCONFIG Port Timing Specifications

| Symbol                      | Parameter                                                                                                                                |                          | Min | Max | Unit |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----|-----|------|

| POR, Confi                  | guration Initialization, and Wakeup                                                                                                      | I                        | 1   | 1   | 1    |

| t <sub>ICFG</sub>           | Time from the Application of $V_{CC, V}$ V <sub>CCAUX</sub> or V <sub>CCI08</sub><br>(whichever is the last) to the rising edge of INITN | -                        | _   | 33  | ms   |

| t <sub>VMC</sub>            | Time from $t_{ICFG}$ to the valid Master CCLK                                                                                            | _                        | _   | 5   | us   |

| t <sub>cz</sub>             | CCLK from Active to High-Z                                                                                                               | _                        | _   | 300 | ns   |

| Master CCI                  | LK                                                                                                                                       | T                        | 1   | 1   | 1    |

| f <sub>MCLK</sub>           | Frequency                                                                                                                                | All selected frequencies | -20 | 20  | %    |

| t <sub>MCLK-DC</sub>        | Duty Cycle                                                                                                                               | All selected frequencies | 40  | 60  | %    |

| All Configu                 | ration Modes                                                                                                                             |                          |     |     |      |

| t <sub>PRGM</sub>           | PROGRAMN LOW pulse accepted                                                                                                              | _                        | 110 | _   | ns   |

| t <sub>PRGMRJ</sub>         | PROGRAMN LOW pulse rejected                                                                                                              | _                        | _   | 50  | ns   |

| t <sub>INITL</sub>          | INITN LOW time                                                                                                                           | _                        | _   | 55  | ns   |

| t <sub>dppint</sub>         | PROGRAMN LOW to INITN LOW                                                                                                                | _                        | _   | 70  | ns   |

| <b>t</b> <sub>DPPDONE</sub> | PROGRAMN LOW to DONE LOW                                                                                                                 | _                        | _   | 80  | ns   |

| t <sub>IODISS</sub>         | PROGRAMN LOW to I/O Disabled                                                                                                             | _                        | _   | 150 | ns   |

| Slave SPI                   |                                                                                                                                          | T                        | 1   |     | 1    |

| f <sub>CCLK</sub>           | CCLK input clock frequency                                                                                                               | _                        | _   | 60  | MHz  |

| t <sub>CCLKH</sub>          | CCLK input clock pulsewidth HIGH                                                                                                         | _                        | 6   | _   | ns   |

| t <sub>cclkl</sub>          | CCLK input clock pulsewidth LOW                                                                                                          | _                        | 6   | _   | ns   |

| t <sub>stsu</sub>           | CCLK setup time                                                                                                                          | _                        | 1   | _   | ns   |

| t <sub>sth</sub>            | CCLK hold time                                                                                                                           | _                        | 1   | _   | ns   |

| t <sub>sтсо</sub>           | CCLK falling edge to valid output                                                                                                        | _                        | _   | 10  | ns   |

| t <sub>stoz</sub>           | CCLK falling edge to valid disable                                                                                                       | _                        | _   | 10  | ns   |

| t <sub>stov</sub>           | CCLK falling edge to valid enable                                                                                                        | _                        | _   | 10  | ns   |

| t <sub>scs</sub>            | Chip Select HIGH time                                                                                                                    | _                        | 25  | _   | ns   |

| t <sub>scss</sub>           | Chip Select setup time                                                                                                                   | _                        | 3   | _   | ns   |

| t <sub>scsн</sub>           | Chip Select hold time                                                                                                                    | _                        | 3   | _   | ns   |

| Master SPI                  |                                                                                                                                          | ,                        | ,   |     |      |

| f <sub>CCLK</sub>           | Max selected CCLK output frequency                                                                                                       | _                        | _   | 62  | MHz  |

| t <sub>cclкн</sub>          | CCLK output clock pulse width HIGH                                                                                                       | _                        | 3.5 | _   | ns   |

| t <sub>CCLKL</sub>          | CCLK output clock pulse width LOW                                                                                                        | _                        | 3.5 | _   | ns   |

| t <sub>sтsu</sub>           | CCLK setup time                                                                                                                          | _                        | 5   | _   | ns   |

| t <sub>sтн</sub>            | CCLK hold time                                                                                                                           | _                        | 1   | _   | ns   |

| t <sub>CSSPI</sub>          | INITN HIGH to Chip Select LOW                                                                                                            | _                        | 100 | 200 | ns   |

| t <sub>CFGX</sub>           | INITN HIGH to first CCLK edge                                                                                                            | _                        | _   | 150 | ns   |

| Slave Seria                 | l l                                                                                                                                      |                          |     |     | 1    |

| f <sub>CCLK</sub>           | CCLK input clock frequency                                                                                                               | _                        | _   | 66  | MHz  |

| t <sub>sscн</sub>           | CCLK input clock pulse width HIGH                                                                                                        | _                        | 5   | _   | ns   |

| t <sub>SSCL</sub>           | CCLK input clock pulse width LOW                                                                                                         | _                        | 5   | _   | ns   |

| t <sub>suscdi</sub>         | CCLK setup time                                                                                                                          | _                        | 0.5 | _   | ns   |

| t <sub>HSCDI</sub>          | CCLK hold time                                                                                                                           | _                        | 1.5 | _   | ns   |

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

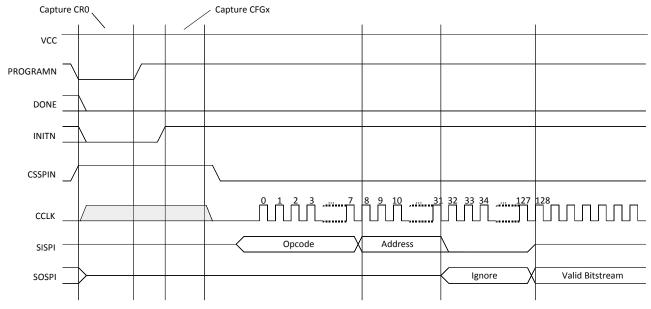

Figure 3.22. Master SPI Configuration Waveforms

# 3.32. JTAG Port Timing Specifications

Over recommended operating conditions.

#### Table 3.43. JTAG Port Timing Specifications

| Symbol                      | Parameter                                                          | Min | Max | Units |

|-----------------------------|--------------------------------------------------------------------|-----|-----|-------|

| f <sub>MAX</sub>            | TCK clock frequency                                                | -   | 25  | MHz   |

| t <sub>втсрн</sub>          | TCK [BSCAN] clock pulse width high                                 | 20  | —   | ns    |

| t <sub>btcpl</sub>          | TCK [BSCAN] clock pulse width low                                  | 20  | —   | ns    |

| t <sub>BTS</sub>            | TCK [BSCAN] setup time                                             | 10  | —   | ns    |

| t <sub>BTH</sub>            | TCK [BSCAN] hold time                                              | 8   | —   | ns    |

| t <sub>BTRF</sub>           | TCK [BSCAN] rise/fall time                                         | 50  | —   | mV/ns |

| t <sub>BTCO</sub>           | TAP controller falling edge of clock to valid output               | -   | 10  | ns    |

| t <sub>BTCODIS</sub>        | TAP controller falling edge of clock to valid disable              | —   | 10  | ns    |

| t <sub>btcoen</sub>         | TAP controller falling edge of clock to valid enable               | -   | 10  | ns    |

| t <sub>BTCRS</sub>          | BSCAN test capture register setup time                             | 8   | —   | ns    |

| t <sub>btcrh</sub>          | BSCAN test capture register hold time                              | 25  | —   | ns    |

| t <sub>BUTCO</sub>          | BSCAN test update register, falling edge of clock to valid output  | -   | 25  | ns    |

| t <sub>BTUODIS</sub>        | BSCAN test update register, falling edge of clock to valid disable | -   | 25  | ns    |

| <b>t</b> <sub>BTUPOEN</sub> | BSCAN test update register, falling edge of clock to valid enable  | -   | 25  | ns    |

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

# 4.2. PICs and DDR Data (DQ) Pins Associated with the DDR Strobe (DQS) Pin

| PICs Associated with DQS Strobe | PIO within PIC                              | DDR Strobe (DQS) and Data (DQ) Pins |  |  |  |  |  |  |  |

|---------------------------------|---------------------------------------------|-------------------------------------|--|--|--|--|--|--|--|

| F                               | For Left and Right Edges of the Device Only |                                     |  |  |  |  |  |  |  |

|                                 | А                                           | DQ                                  |  |  |  |  |  |  |  |

|                                 | В                                           | DQ                                  |  |  |  |  |  |  |  |

| P[L/R] [n-6]                    | С                                           | DQ                                  |  |  |  |  |  |  |  |

|                                 | D                                           | DQ                                  |  |  |  |  |  |  |  |

|                                 | А                                           | DQ                                  |  |  |  |  |  |  |  |

|                                 | В                                           | DQ                                  |  |  |  |  |  |  |  |

| P[L/R] [n-3]                    | С                                           | DQ                                  |  |  |  |  |  |  |  |

|                                 | D                                           | DQ                                  |  |  |  |  |  |  |  |

|                                 | А                                           | DQS (P)                             |  |  |  |  |  |  |  |

|                                 | В                                           | DQS (N)                             |  |  |  |  |  |  |  |

| P[L/R] [n]                      | С                                           | DQ                                  |  |  |  |  |  |  |  |

|                                 | D                                           | DQ                                  |  |  |  |  |  |  |  |

|                                 | А                                           | DQ                                  |  |  |  |  |  |  |  |

|                                 | В                                           | DQ                                  |  |  |  |  |  |  |  |

| P[L/R] [n+3]                    | С                                           | DQ                                  |  |  |  |  |  |  |  |

|                                 | D                                           | DQ                                  |  |  |  |  |  |  |  |

**Note**: "n" is a row PIC number.

# 4.3. **Pin Information Summary**

### 4.3.1. **LFE5UM/LFE5UM5G**

| Pin Information Summary     |                             | 5UM/<br>M5G-25 | LFE5UN       | 1/LFE5U       | M5G-45      | LFE5UM/LFE5UM5G-85 |               |             |              |              |

|-----------------------------|-----------------------------|----------------|--------------|---------------|-------------|--------------------|---------------|-------------|--------------|--------------|

| Pin Type                    |                             | 285<br>csfBG   | 381<br>caBGA | 285<br>csfBGA | 381<br>caBG | 554<br>caBGA       | 285<br>csfBGA | 381<br>caBG | 554<br>caBGA | 756<br>caBGA |

|                             | Bank 0                      | 6              | 24           | 6             | 27          | 32                 | 6             | 27          | 32           | 56           |

|                             | Bank 1                      | 6              | 32           | 6             | 33          | 40                 | 6             | 33          | 40           | 48           |

|                             | Bank 2                      | 21             | 32           | 21            | 32          | 32                 | 21            | 34          | 32           | 48           |

| General Purpose             | Bank 3                      | 28             | 32           | 28            | 33          | 48                 | 28            | 33          | 48           | 64           |

| Inputs/Outputs per Bank     | Bank 4                      | 0              | 0            | 0             | 0           | 0                  | 0             | 0           | 14           | 24           |

|                             | Bank 6                      | 26             | 32           | 26            | 33          | 48                 | 26            | 33          | 48           | 64           |

|                             | Bank 7                      | 18             | 32           | 18            | 32          | 32                 | 18            | 32          | 32           | 48           |

|                             | Bank 8                      | 13             | 13           | 13            | 13          | 13                 | 13            | 13          | 13           | 13           |

| Total Single-Ended User I/O | Total Single-Ended User I/O |                | 197          | 118           | 203         | 245                | 118           | 205         | 259          | 365          |

| VCC                         | VCC                         |                | 20           | 13            | 20          | 24                 | 13            | 20          | 24           | 36           |

| VCCAUX (Core)               |                             | 3              | 4            | 3             | 4           | 9                  | 3             | 4           | 9            | 8            |

|                             | Bank O                      | 1              | 2            | 1             | 2           | 3                  | 1             | 2           | 3            | 4            |

|                             | Bank 1                      | 1              | 2            | 1             | 2           | 3                  | 1             | 2           | 3            | 4            |

|                             | Bank 2                      | 2              | 3            | 2             | 3           | 4                  | 2             | 3           | 4            | 4            |

| VICEIO                      | Bank 3                      | 2              | 3            | 2             | 3           | 3                  | 2             | 3           | 3            | 4            |

| VCCIO                       | Bank 4                      | 0              | 0            | 0             | 0           | 0                  | 0             | 0           | 2            | 2            |

|                             | Bank 6                      | 2              | 3            | 2             | 3           | 4                  | 2             | 3           | 4            | 4            |

|                             | Bank 7                      | 2              | 3            | 2             | 3           | 3                  | 2             | 3           | 3            | 4            |

|                             | Bank 8                      | 2              | 2            | 2             | 2           | 2                  | 2             | 2           | 2            | 2            |

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Pin Information Summary          |          |              | 5UM/<br>M5G-25 | LFE5UN        | //LFE5U     | M5G-45       | LF            | E5UM/LF     | 5UM/LFE5UM5G-85 |              |  |  |

|----------------------------------|----------|--------------|----------------|---------------|-------------|--------------|---------------|-------------|-----------------|--------------|--|--|

| Pin Type                         |          | 285<br>csfBG | 381<br>caBGA   | 285<br>csfBGA | 381<br>caBG | 554<br>caBGA | 285<br>csfBGA | 381<br>caBG | 554<br>caBGA    | 756<br>caBGA |  |  |

| ТАР                              |          | 4            | 4              | 4             | 4           | 4            | 4             | 4           | 4               | 4            |  |  |

| Miscellaneous Dedicated Pins     |          | 7            | 7              | 7             | 7           | 7            | 7             | 7           | 7               | 7            |  |  |

| GND                              |          | 83           | 59             | 83            | 59          | 113          | 83            | 59          | 113             | 166          |  |  |

| NC                               |          | 1            | 8              | 1             | 2           | 33           | 1             | 0           | 17              | 29           |  |  |

| Reserved                         |          | 0            | 2              | 0             | 2           | 4            | 0             | 2           | 4               | 4            |  |  |