# E. Flattice Semiconductor Corporation - <u>LFE5UM5G-45F-8BG381I Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                          |

|--------------------------------|---------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 11000                                                                           |

| Number of Logic Elements/Cells | 44000                                                                           |

| Total RAM Bits                 | 1990656                                                                         |

| Number of I/O                  | 203                                                                             |

| Number of Gates                | -                                                                               |

| Voltage - Supply               | 1.045V ~ 1.155V                                                                 |

| Mounting Type                  | Surface Mount                                                                   |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                              |

| Package / Case                 | 381-FBGA                                                                        |

| Supplier Device Package        | 381-CABGA (17x17)                                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe5um5g-45f-8bg381i |

|                                |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Figures

| Figure 2.1. Simplified Block Diagram, LFE5UM/LFE5UM5G-85 Device (Top Level)    | 13 |

|--------------------------------------------------------------------------------|----|

| Figure 2.2. PFU Diagram                                                        | 14 |

| Figure 2.3. Slice Diagram                                                      | 15 |

| Figure 2.4. Connectivity Supporting LUT5, LUT6, LUT7, and LUT8                 | 16 |

| Figure 2.5. General Purpose PLL Diagram                                        | 18 |

| Figure 2.6. LFE5UM/LFE5UM5G-85 Clocking                                        | 20 |

| Figure 2.7. DCS Waveforms                                                      | 21 |

| Figure 2.8. Edge Clock Sources per Bank                                        | 22 |

| Figure 2.9. ECP5/ECP5-5G Clock Divider Sources                                 | 22 |

| Figure 2.10. DDRDLL Functional Diagram                                         |    |

| Figure 2.11. ECP5/ECP5-5G DLL Top Level View (For LFE-45 and LFE-85)           |    |

| Figure 2.12. Memory Core Reset                                                 |    |

| Figure 2.13. Comparison of General DSP and ECP5/ECP5-5G Approaches             | 27 |

| Figure 2.14. Simplified sysDSP Slice Block Diagram                             | 28 |

| Figure 2.15. Detailed sysDSP Slice Diagram                                     |    |

| Figure 2.16. Group of Four Programmable I/O Cells on Left/Right Sides          |    |

| Figure 2.17. Input Register Block for PIO on Top Side of the Device            |    |

| Figure 2.18. Input Register Block for PIO on Left and Right Side of the Device |    |

| Figure 2.19. Output Register Block on Top Side                                 |    |

| Figure 2.20. Output Register Block on Left and Right Sides                     |    |

| Figure 2.21. Tristate Register Block on Top Side                               |    |

| Figure 2.22. Tristate Register Block on Left and Right Sides                   |    |

| Figure 2.23. DQS Grouping on the Left and Right Edges                          |    |

| Figure 2.24. DQS Control and Delay Block (DQSBUF)                              |    |

| Figure 2.25. ECP5/ECP5-5G Device Family Banks                                  |    |

| Figure 2.26. On-Chip Termination                                               |    |

| Figure 2.27. SERDES/PCS Duals (LFE5UM/LFE5UM5G-85)                             |    |

| Figure 2.28. Simplified Channel Block Diagram for SERDES/PCS Block             |    |

| Figure 3.1. LVDS25E Output Termination Example                                 |    |

| Figure 3.2. BLVDS25 Multi-point Output Example                                 |    |

| Figure 3.3. Differential LVPECL33                                              |    |

| Figure 3.4. MLVDS25 (Multipoint Low Voltage Differential Signaling)            |    |

| Figure 3.5. SLVS Interface                                                     |    |

| Figure 3.6. Receiver RX.CLK.Centered Waveforms                                 |    |

| Figure 3.7. Receiver RX.CLK.Aligned and DDR Memory Input Waveforms             |    |

| Figure 3.8. Transmit TX.CLK.Centered and DDR Memory Output Waveforms           |    |

| Figure 3.9. Transmit TX.CLK.Aligned Waveforms                                  |    |

| Figure 3.10. DDRX71 Video Timing Waveforms                                     |    |

| Figure 3.11. Receiver DDRX71 RX Waveforms                                      |    |

| Figure 3.12. Transmitter DDRX71_TX Waveforms                                   |    |

| Figure 3.13. Transmitter and Receiver Latency Block Diagram                    |    |

| Figure 3.14. SERDES External Reference Clock Waveforms                         |    |

| Figure 3.15. sysCONFIG Parallel Port Read Cycle                                |    |

| Figure 3.16. sysCONFIG Parallel Port Write Cycle                               |    |

| Figure 3.17. sysCONFIG Slave Serial Port Timing                                |    |

| Figure 3.18. Power-On-Reset (POR) Timing                                       |    |

| Figure 3.19. sysCONFIG Port Timing                                             |    |

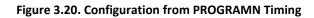

| Figure 3.20. Configuration from PROGRAMN Timing                                |    |

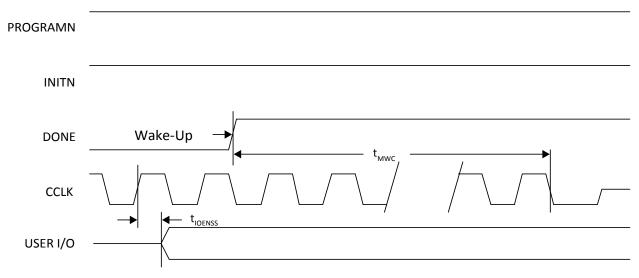

| Figure 3.21. Wake-Up Timing                                                    |    |

| Figure 3.22. Master SPI Configuration Waveforms                                |    |

| Figure 3.23. JTAG Port Timing Waveforms                                        |    |

| Figure 3.24. Output Test Load, LVTTL and LVCMOS Standards                      |    |

| J ,                                                                            |    |

<sup>© 2014-2018</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

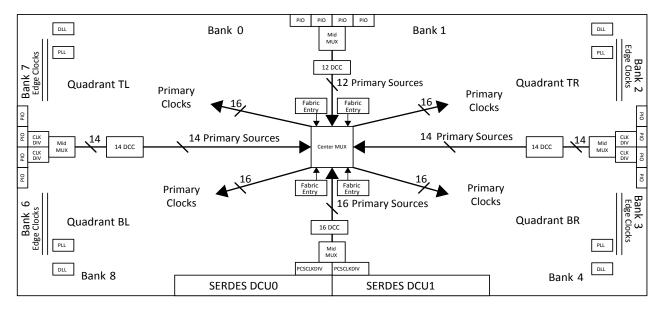

Figure 2.6. LFE5UM/LFE5UM5G-85 Clocking

## 2.5.1. Primary Clocks

The ECP5/ECP5-5G device family provides low-skew, high fan-out clock distribution to all synchronous elements in the FPGA fabric through the Primary Clock Network.

The primary clock network is divided into four clocking quadrants: Top Left (TL), Bottom Left (BL), Top Right (TR), and Bottom Right (BR). Each of these quadrants has 16 clocks that can be distributed to the fabric in the quadrant.

The Lattice Diamond software can automatically route each clock to one of the four quadrants up to a maximum of 16 clocks per quadrant. The user can change how the clocks are routed by specifying a preference in the Lattice Diamond software to locate the clock to specific. The ECP5/ECP5-5G device provides the user with a maximum of 64 unique clock input sources that can be routed to the primary Clock network.

Primary clock sources are:

- Dedicated clock input pins

- PLL outputs

- CLKDIV outputs

- Internal FPGA fabric entries (with minimum general routing)

- SERDES/PCS/PCSDIV clocks

- OSC clock

These sources are routed to one of four clock switches called a Mid Mux. The outputs of the Mid MUX are routed to the center of the FPGA where another clock switch, called the Center MUX, is used to route the primary clock sources to primary clock distribution to the ECP5/ECP5-5G fabric. These routing muxes are shown in Figure 2.6. Since there is a maximum of 60 unique clock input sources to the clocking quadrants, there are potentially 64 unique clock domains that can be used in the ECP5/ECP5-5G Device. For more information about the primary clock tree and connections, refer to ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263).

#### 2.5.1.1. Dynamic Clock Control

The Dynamic Clock Control (DCC), Quadrant Clock enable/disable feature allows internal logic control of the quadrant primary clock network. When a clock network is disabled, the clock signal is static and not toggle. All the logic fed by that clock will not toggle, reducing the overall power consumption of the device. The disable function will not create glitch and increase the clock latency to the primary clock network.

This DCC controls the clock sources from the Primary CLOCK MIDMUX before they are fed to the Primary Center MUXs that drive the quadrant clock network. For more information about the DCC, refer to ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263).

\*For 7:1 LVDS interface only. It is required to use PIO pair pins PIOA/B.

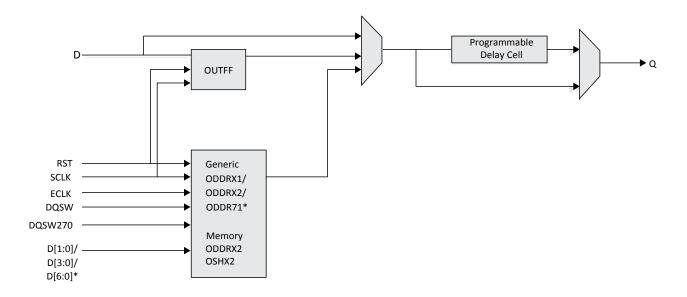

#### Figure 2.20. Output Register Block on Left and Right Sides

| Name                  | Туре   | Description                                                         |

|-----------------------|--------|---------------------------------------------------------------------|

| Q                     | Output | High Speed Data Output                                              |

| D                     | Input  | Data from core to output SDR register                               |

| D[1:0]/D[3:0]/ D[6:0] | Input  | Low Speed Data from device core to output DDR register              |

| RST                   | Input  | Reset to the Output Block                                           |

| SCLK                  | Input  | Slow Speed System Clock                                             |

| ECLK                  | Input  | High Speed Edge Clock                                               |

| DQSW                  | Input  | Clock from DQS control Block used to generate DDR memory DQS output |

| DQSW270               | Input  | Clock from DQS control Block used to generate DDR memory DQ output  |

#### Table 2.9. Output Block Port Description

## 2.12. Tristate Register Block

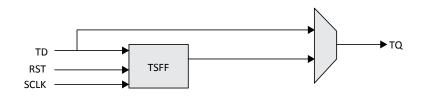

The tristate register block registers tristate control signals from the core of the device before they are passed to the sysIO buffers. The block contains a register for SDR operation. In SDR, TD input feeds one of the flip-flops that then feeds the output. In DDR operation used mainly for DDR memory interface can be implemented on the left and right sides of the device. Here two inputs feed the tristate registers clocked by both ECLK and SCLK.

Figure 2.21 and Figure 2.22 show the Tristate Register Block functions on the device. For detailed description of the tristate register block modes and usage, refer to ECP5 and ECP5-5G High-Speed I/O Interface (TN1265).

Figure 2.21. Tristate Register Block on Top Side

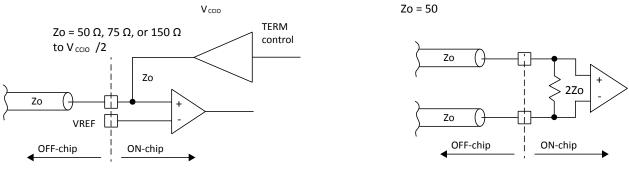

### 2.14.4. On-Chip Programmable Termination

The ECP5/ECP5-5G devices support a variety of programmable on-chip terminations options, including:

- Dynamically switchable Single-Ended Termination with programmable resistor values of 50  $\Omega$ , 75  $\Omega$ , or 150  $\Omega$ .

- Common mode termination of 100 Ω for differential inputs.

Parallel Single-Ended Input

Differential Input

Figure 2.26. On-Chip Termination

See Table 2.12 for termination options for input modes.

| IO_TYPE         | Terminate to V <sub>CCIO</sub> /2* | Differential Termination Resistor* |

|-----------------|------------------------------------|------------------------------------|

| LVDS25          | _                                  | 100                                |

| BLVDS25         | —                                  | 100                                |

| MLVDS           | —                                  | 100                                |

| LVPECL33        | —                                  | 100                                |

| subLVDS         | —                                  | 100                                |

| SLVS            | _                                  | 100                                |

| HSUL12          | 50, 75, 150                        | —                                  |

| HSUL12D         | —                                  | 100                                |

| SSTL135_I / II  | 50, 75, 150                        | —                                  |

| SSTL135D_I / II | —                                  | 100                                |

| SSTL15_I / II   | 50, 75, 150                        | -                                  |

| SSTL15D_I / II  | —                                  | 100                                |

| SSTL18_I / II   | 50, 75, 150                        | -                                  |

| SSTL18D_I / II  | _                                  | 100                                |

\*Notes:

TERMINATE to  $V_{CCIO}/2$  (Single-Ended) and DIFFRENTIAL TERMINATION RESISTOR when turned on can only have one setting per bank. Only left and right banks have this feature.

Use of TERMINATE to  $V_{CCIO}/2$  and DIFFRENTIAL TERMINATION RESISTOR are mutually exclusive in an I/O bank. On-chip termination tolerance ±20%.

Refer to ECP5 and ECP5-5G sysIO Usage Guide (TN1262) for on-chip termination usage and value ranges.

### 2.14.5. Hot Socketing

ECP5/ECP5-5G devices have been carefully designed to ensure predictable behavior during power-up and power-down. During power-up and power-down sequences, the I/Os remain in tristate until the power supply voltage is high enough to ensure reliable operation. In addition, leakage into I/O pins is controlled within specified limits. See the Hot Socketing Specifications section on page 48.

#### Table 3.20. Register-to-Register Performance

| Function                                                                        | –8 Timing | Unit |

|---------------------------------------------------------------------------------|-----------|------|

| Basic Functions                                                                 | ' '       |      |

| 16-Bit Decoder                                                                  | 441       | MHz  |

| 32-Bit Decoder                                                                  | 441       | MHz  |

| 64-Bit Decoder                                                                  | 332       | MHz  |

| 4:1 Mux                                                                         | 441       | MHz  |

| 8:1 Mux                                                                         | 441       | MHz  |

| 16:1 Mux                                                                        | 441       | MHz  |

| 32:1 Mux                                                                        | 441       | MHz  |

| 8-Bit Adder                                                                     | 441       | MHz  |

| 16-Bit Adder                                                                    | 441       | MHz  |

| 64-Bit Adder                                                                    | 441       | MHz  |

| 16-Bit Counter                                                                  | 384       | MHz  |

| 32-Bit Counter                                                                  | 317       | MHz  |

| 64-Bit Counter                                                                  | 263       | MHz  |

| 64-Bit Accumulator                                                              | 288       | MHz  |

| Embedded Memory Functions                                                       |           |      |

| 1024x18 True-Dual Port RAM (Write Through or Normal), with EBR Output Registers | 272       | MHz  |

| 1024x18 True-Dual Port RAM (Read-Before-Write), with EBR Output Registers       | 214       | MHz  |

| Distributed Memory Functions                                                    | '         |      |

| 16 x 2 Pseudo-Dual Port or 16 x 4 Single Port RAM (One PFU)                     | 441       | MHz  |

| 16 x 4 Pseudo-Dual Port (Two PFUs)                                              | 441       | MHz  |

| DSP Functions                                                                   | · · ·     |      |

| 9 x 9 Multiplier (All Registers)                                                | 225       | MHz  |

| 18 x 18 Multiplier (All Registers)                                              | 225       | MHz  |

| 36 x 36 Multiplier (All Registers)                                              | 225       | MHz  |

| 18 x 18 Multiply-Add/Sub (All Registers)                                        | 225       | MHz  |

| 18 x 18 Multiply/Accumulate (Input and Output Registers)                        | 225       | MHz  |

Notes:

1. These functions were generated using Lattice Diamond design software tool. Exact performance may vary with the device and the design software tool version. The design software tool uses internal parameters that have been characterized but are not tested on every device.

2. Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from Lattice Diamond design software tool.

## 3.16. Derating Timing Tables

Logic timing provided in the following sections of this data sheet and the Diamond design tools are worst case numbers in the operating range. Actual delays at nominal temperature and voltage for best case process, can be much better than the values given in the tables. The Diamond design tool can provide logic timing numbers at a particular temperature and voltage.

| Damamatar                                | Description                                                      | Destas         |          | -8        |           | -7       | -          | -6         | L lusit          |

|------------------------------------------|------------------------------------------------------------------|----------------|----------|-----------|-----------|----------|------------|------------|------------------|

| Parameter                                | Description                                                      | Device         | Min      | Max       | Min       | Max      | Min        |            | Unit             |

| t <sub>h_delpll</sub>                    | Clock to Data Hold - PIO Input<br>Register with Data Input Delay | All Devices    | 0        | -         | 0         | -        | 0          | -          | ns               |

| Generic DDR Input                        |                                                                  |                |          |           |           |          |            |            |                  |

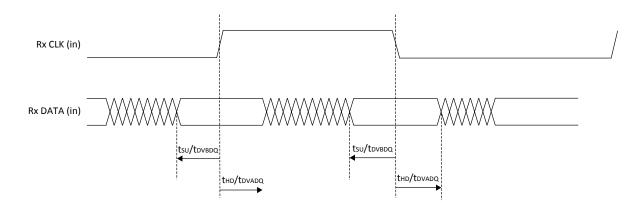

| Generic DDRX1 Inp                        | uts With Clock and Data Centere                                  | d at Pin (GDDI | RX1_RX.S | CLK.Cen   | tered) Us | ing PCLk | Clock In   | put - Fig  | ure 3.6          |

| t <sub>SU_GDDRX1_centered</sub>          | Data Setup Before CLK Input                                      | All Devices    | 0.52     | -         | 0.52      | -        | 0.52       | -          | ns               |

| $t_{HD_GDDRX1_centered}$                 | Data Hold After CLK Input                                        | All Devices    | 0.52     | _         | 0.52      | _        | 0.52       | _          | ns               |

| $f_{DATA\_GDDRX1\_centered}$             | GDDRX1 Data Rate                                                 | All Devices    | _        | 500       | —         | 500      | —          | 500        | Mb/s             |

| $f_{MAX\_GDDRX1\_centered}$              | GDDRX1 CLK Frequency (SCLK)                                      | All Devices    | _        | 250       | —         | 250      | _          | 250        | MHz              |

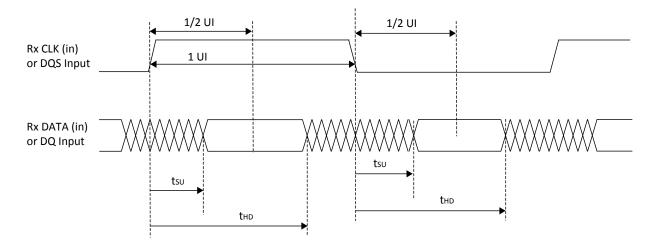

| Generic DDRX1 Inp                        | uts With Clock and Data Aligned                                  | at Pin (GDDR)  | (1_RX.SC | LK.Aligne | ed) Using | PCLK Cl  | ock Input  | t - Figure | 3.7              |

| $t_{SU\_GDDRX1\_aligned}$                | Data Setup from CLK Input                                        | All Devices    | -        | -0.55     | -         | -0.55    | -          | -0.55      | ns +<br>1/2 UI   |

| $t_{HD\_GDDRX1\_aligned}$                | Data Hold from CLK Input                                         | All Devices    | 0.55     | -         | 0.55      | -        | 0.55       | _          | ns +<br>1/2 U    |

| $f_{DATA_GDDRX1_aligned}$                | GDDRX1 Data Rate                                                 | All Devices    | —        | 500       | —         | 500      | —          | 500        | Mb/s             |

| $f_{MAX\_GDDRX1\_aligned}$               | GDDRX1 CLK Frequency (SCLK)                                      | All Devices    | _        | 250       | —         | 250      | —          | 250        | MHz              |

| Generic DDRX2 Inp                        | uts With Clock and Data Centere                                  | d at Pin (GDDI | RX2_RX.E | CLK.Cen   | tered) Us | ing PCLK | Clock In   | put, Left  | and              |

| Right sides Only - F                     |                                                                  | T              |          |           |           | 1        | 1          |            |                  |

| $t_{SU_GDDRX2_centered}$                 | Data Setup before CLK Input                                      | All Devices    | 0.321    | —         | 0.403     | _        | 0.471      | _          | ns               |

| $t_{HD\_GDDRX2\_centered}$               | Data Hold after CLK Input                                        | All Devices    | 0.321    | _         | 0.403     | _        | 0.471      | _          | ns               |

| $f_{DATA\_GDDRX2\_centered}$             | GDDRX2 Data Rate                                                 | All Devices    | —        | 800       | —         | 700      | —          | 624        | Mb/s             |

| $f_{MAX\_GDDRX2\_centered}$              | GDDRX2 CLK Frequency (ECLK)                                      | All Devices    | -        | 400       | -         | 350      | -          | -          | MHz              |

| Generic DDRX2 Inp<br>sides Only - Figure | uts With Clock and Data Aligned 3.7                              | at Pin (GDDR)  | (2_RX.EC | LK.Aligne | ed) Using | PCLK Cl  | ock Input  | t, Left an | d Right          |

| $t_{SU\_GDDRX2\_aligned}$                | Data Setup from CLK Input                                        | All Devices    | -        | -0.344    | —         | -0.42    | -          | -0.495     | ns + 1/2<br>UI   |

| $t_{HD}_{GDDRX2}_{aligned}$              | Data Hold from CLK Input                                         | All Devices    | 0.344    | —         | 0.42      | _        | 0.495      | —          | ns + 1/2<br>UI   |

| $f_{DATA\_GDDRX2\_aligned}$              | GDDRX2 Data Rate                                                 | All Devices    | —        | 800       | —         | 700      | _          | 624        | Mb/s             |

| $f_{MAX\_GDDRX2\_aligned}$               | GDDRX2 CLK Frequency                                             | All Devices    |          | 400       | —         | 350      | _          | 312        | MHz              |

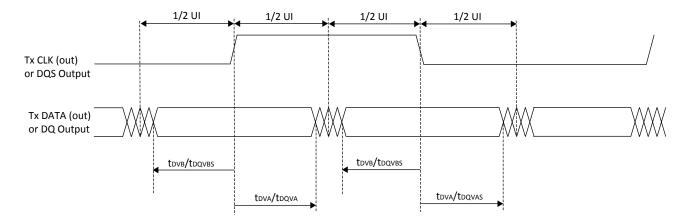

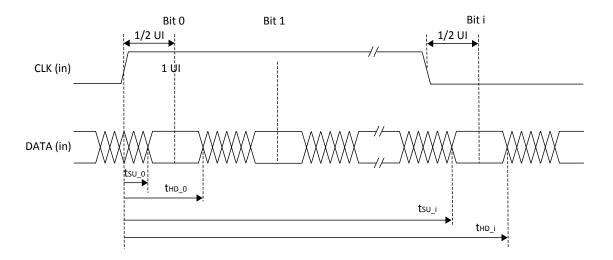

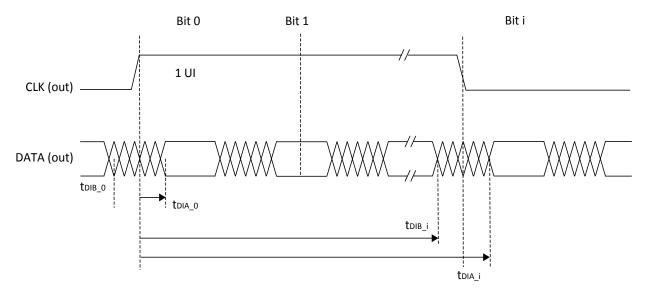

| Video DDRX71 Inpu<br>Figure 3.11         | its With Clock and Data Aligned a                                | at Pin (GDDRX  | 71_RX.E0 | CLK) Usin | g PLL Clo | ck Input | , Left and | l Right si | des Only         |

| t <sub>su_lvds71_i</sub>                 | Data Setup from CLK Input<br>(bit i)                             | All Devices    | _        | -0.271    | _         | -0.39    | _          | -0.41      | ns+(1/2+<br>* UI |

| thd_lvds71_i                             | Data Hold from CLK Input<br>(bit i)                              | All Devices    | 0.271    | _         | 0.39      | -        | 0.41       | _          | ns+(1/2+<br>* UI |

| f <sub>DATA_LVDS71</sub>                 | DDR71 Data Rate                                                  | All Devices    | 1        | 756       | —         | 620      | -          | 525        | Mb/s             |

| f <sub>MAX_LVDS71</sub>                  | DDR71 CLK Frequency (ECLK)                                       | All Devices    |          | 378       | _         | 310      | _          | 262.5      | MHz              |

#### Table 3.22. ECP5/ECP5-5G External Switching Characteristics (Continued)

| Demonstern                                                                                                                              | Description                            | Davies        | -         | -8         | -7   |       | -6   |       | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------|-----------|------------|------|-------|------|-------|------|

| Parameter                                                                                                                               | Description                            | Device        | Min       | Max        | Min  | Max   | Min  | Max   | Unit |

| f <sub>data_ddr2</sub><br>f <sub>data_ddr3</sub><br>f <sub>data_ddr3</sub><br>f <sub>data_lpddr2</sub><br>f <sub>data_lpddr3</sub>      | DDR Memory Data Rate                   | All Devices   | Ι         | 800        | _    | 700   | _    | 624   | Mb/s |

| fmax_ddr2<br>fmax_ddr3<br>fmax_ddr3l<br>fmax_lpddr2<br>fmax_lpddr3                                                                      | DDR Memory CLK<br>Frequency (ECLK)     | All Devices   | Ι         | 400        | _    | 350   | _    | 312   | MHz  |

| DDR2/DDR3/DDR                                                                                                                           | 3L/LPDDR2/LPDDR3 WRITE (DO             | Q Output Data | are Cente | ered to DC | QS)  |       |      |       |      |

| t <sub>dqvbs_ddr2</sub><br>t <sub>dqvbs_ddr3</sub><br>t <sub>dqvbs_ddr3</sub><br>t <sub>dqvbs_lpddr2</sub><br>t <sub>dqvbs_lpddr3</sub> | Data Output Valid before<br>DQS Output | All Devices   | _         | -0.25      | _    | -0.25 | _    | -0.25 | UI   |

| tdqvas_ddr2<br>tdqvas_ddr3<br>tdqvas_ddr3l<br>tdqvas_lpddr2<br>tdqvas_lpddr2<br>tdqvas_lpddr3                                           | Data Output Valid after DQS<br>Output  | All Devices   | 0.25      | _          | 0.25 | _     | 0.25 | _     | UI   |

| fdata_ddr2<br>fdata_ddr3<br>fdata_ddr3l<br>fdata_lpddr2<br>fdata_lpddr3                                                                 | DDR Memory Data Rate                   | All Devices   | _         | 800        | _    | 700   | _    | 624   | Mb/s |

| f <sub>MAX_DDR2</sub><br>f <sub>MAX_DDR3</sub><br>f <sub>MAX_DDR3L</sub><br>f <sub>MAX_LPDDR2</sub><br>f <sub>MAX_LPDDR3</sub>          | DDR Memory CLK<br>Frequency (ECLK)     | All Devices   | _         | 400        | _    | 350   | _    | 312   | MHz  |

Notes:

1. Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from the Diamond software.

General I/O timing numbers are based on LVCMOS 2.5, 12 mA, Fast Slew Rate, 0pf load. Generic DDR timing are numbers based on LVDS I/O. DDR2 timing numbers are based on SSTL18. DDR3 timing numbers are based on SSTL15. LPDDR2 and LPDDR3 timing numbers are based on HSUL12.

- 3. Uses LVDS I/O standard for measurements.

- 4. Maximum clock frequencies are tested under best case conditions. System performance may vary upon the user environment.

- 5. All numbers are generated with the Diamond software.

FPGA-DS-02012-1.9

Figure 3.6. Receiver RX.CLK.Centered Waveforms

Figure 3.7. Receiver RX.CLK.Aligned and DDR Memory Input Waveforms

Figure 3.8. Transmit TX.CLK.Centered and DDR Memory Output Waveforms

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Figure 3.11. Receiver DDRX71\_RX Waveforms

Figure 3.12. Transmitter DDRX71\_TX Waveforms

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

## 3.22. SERDES High-Speed Data Receiver

#### Table 3.27. Serial Input Data Specifications

| Symbol                  | Description                                                     | Min  | Тур       | Max                                | Unit    |

|-------------------------|-----------------------------------------------------------------|------|-----------|------------------------------------|---------|

| V <sub>RX-DIFF-S</sub>  | Differential input sensitivity                                  | 150  | -         | 1760                               | mV, p-p |

| V <sub>RX-IN</sub>      | Input levels                                                    | 0    | -         | V <sub>CCA</sub> +0.5 <sup>2</sup> | V       |

| V <sub>RX-CM-DCCM</sub> | Input common mode range (internal DC coupled mode)              | 0.6  | _         | V <sub>CCA</sub>                   | V       |

| V <sub>RX-CM-ACCM</sub> | Input common mode range (internal AC coupled mode) <sup>2</sup> | 0.1  | _         | V <sub>CCA</sub> +0.2              | V       |

| T <sub>RX-RELOCK</sub>  | SCDR re-lock time <sup>1</sup>                                  | _    | 1000      | _                                  | Bits    |

| Z <sub>RX-TERM</sub>    | Input termination 50/75 $\Omega$ /High Z                        | -20% | 50/75/5 K | +20%                               | Ω       |

| RL <sub>RX-RL</sub>     | Return loss (without package)                                   | —    | _         | -10                                | dB      |

Notes:

1. This is the typical number of bit times to re-lock to a new phase or frequency within ±300 ppm, assuming 8b10b encoded data.

2. Up to 1.655 for ECP5, and 1.76 for ECP5-5G.

## 3.23. Input Data Jitter Tolerance

A receiver's ability to tolerate incoming signal jitter is very dependent on jitter type. High speed serial interface standards have recognized the dependency on jitter type and have specifications to indicate tolerance levels for different jitter types as they relate to specific protocols. Sinusoidal jitter is considered to be a worst case jitter type.

| Description   | Frequency  | Condition               | Min | Тур | Max  | Unit            |

|---------------|------------|-------------------------|-----|-----|------|-----------------|

| Deterministic |            | 400 mV differential eye | —   | —   | TBD  | UI, p-p         |

| Random        | 5 Gb/s     | 400 mV differential eye | —   | —   | TBD  | UI <i>,</i> p-p |

| Total         |            | 400 mV differential eye | —   | —   | TBD  | UI, p-p         |

| Deterministic |            | 400 mV differential eye | —   | _   | 0.37 | UI <i>,</i> p-p |

| Random        | 3.125 Gb/s | 400 mV differential eye | —   | —   | 0.18 | UI <i>,</i> p-p |

| Total         |            | 400 mV differential eye | —   | _   | 0.65 | UI <i>,</i> p-p |

| Deterministic |            | 400 mV differential eye | —   | —   | 0.37 | UI <i>,</i> p-p |

| Random        | 2.5 Gb/s   | 400 mV differential eye | —   | —   | 0.18 | UI <i>,</i> p-p |

| Total         |            | 400 mV differential eye | —   | —   | 0.65 | UI <i>,</i> p-p |

| Deterministic |            | 400 mV differential eye | —   | —   | 0.37 | UI <i>,</i> p-p |

| Random        | 1.25 Gb/s  | 400 mV differential eye | —   | _   | 0.18 | UI <i>,</i> p-p |

| Total         |            | 400 mV differential eye | _   | _   | 0.65 | UI, p-p         |

#### Table 3.28. Receiver Total Jitter Tolerance Specification

Notes:

1. Jitter tolerance measurements are done with protocol compliance tests: 3.125 Gb/s - XAUI Standard, 2.5 Gb/s - PCIe Standard, 1.25 Gb/s - SGMII Standard.

2. For ECP5-5G family devices only.

## 3.25. PCI Express Electrical and Timing Characteristics

## 3.25.1. PCIe (2.5 Gb/s) AC and DC Characteristics

Over recommended operating conditions.

#### Table 3.30. PCIe (2.5 Gb/s)

| Symbol                                       | Description                                                          | Test Conditions                                        | Min               | Тур  | Max                | Unit |

|----------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------|-------------------|------|--------------------|------|

| Transmit <sup>1</sup>                        | - · · · · · · · · · · · · · · · · · · ·                              |                                                        |                   |      | 1                  |      |

| UI                                           | Unit interval                                                        | —                                                      | 399.88            | 400  | 400.12             | ps   |

| V <sub>TX-DIFF_P-P</sub>                     | Differential peak-to-peak output                                     | —                                                      | 0.8               | 1.0  | 1.2                | V    |

| V <sub>TX-DE-RATIO</sub>                     | De-emphasis differential output voltage ratio                        | _                                                      | -3                | -3.5 | -4                 | dB   |

| V <sub>TX-CM-AC_P</sub>                      | RMS AC peak common-mode output voltage                               | -                                                      | _                 | _    | 20                 | mV   |

| V <sub>TX-RCV-DETECT</sub>                   | Amount of voltage change allowed during receiver detection           | -                                                      | _                 | _    | 600                | mV   |

| V <sub>TX-CM-DC</sub>                        | Tx DC common mode voltage                                            | —                                                      | 0                 |      | V <sub>CCHTX</sub> | V    |

| I <sub>TX-SHORT</sub>                        | Output short circuit current                                         | V <sub>TX-D+</sub> =0.0 V<br>V <sub>TX-D-</sub> =0.0 V | _                 |      | 90                 | mA   |

| Z <sub>TX-DIFF-DC</sub>                      | Differential output impedance                                        | —                                                      | 80                | 100  | 120                | Ω    |

| RL <sub>TX-DIFF</sub>                        | Differential return loss                                             | —                                                      | 10                |      | _                  | dB   |

| RL <sub>TX-CM</sub>                          | Common mode return loss                                              | —                                                      | 6.0               | -    | —                  | dB   |

| T <sub>TX-RISE</sub>                         | Tx output rise time                                                  | 20% to 80%                                             | 0.125             | —    | -                  | UI   |

| T <sub>TX-FALL</sub>                         | Tx output fall time                                                  | 20% to 80%                                             | 0.125             |      | -                  | UI   |

| L <sub>TX-SKEW</sub>                         | Lane-to-lane static output skew for all lanes in port/link           | -                                                      | -                 | -    | 1.3                | ns   |

| T <sub>TX-EYE</sub>                          | Transmitter eye width                                                | —                                                      | 0.75              | -    | _                  | UI   |

| T <sub>TX-EYE-MEDIAN-TO-MAX-</sub><br>JITTER | Maximum time between jitter median and maximum deviation from median | _                                                      | _                 | _    | 0.125              | UI   |

| Receive <sup>1, 2</sup>                      |                                                                      |                                                        |                   |      |                    |      |

| UI                                           | Unit Interval                                                        | _                                                      | 399.88            | 400  | 400.12             | ps   |

| V <sub>RX-DIFF_P-P</sub>                     | Differential peak-to-peak input voltage                              | -                                                      | 0.34 <sup>3</sup> | _    | 1.2                | v    |

| V <sub>RX-IDLE-DET-DIFF_P-P</sub>            | Idle detect threshold voltage                                        | _                                                      | 65                | _    | 340 <sup>3</sup>   | mV   |

| V <sub>RX-CM-AC_P</sub>                      | RMS AC peak common-mode input voltage                                | _                                                      | _                 | _    | 150                | mV   |

| Z <sub>RX-DIFF-DC</sub>                      | DC differential input impedance                                      | _                                                      | 80                | 100  | 120                | Ω    |

| Z <sub>RX-DC</sub>                           | DC input impedance                                                   | _                                                      | 40                | 50   | 60                 | Ω    |

| Z <sub>RX-HIGH-IMP-DC</sub>                  | Power-down DC input impedance                                        | _                                                      | 200K              | _    | _                  | Ω    |

| RL <sub>RX-DIFF</sub>                        | Differential return loss                                             | _                                                      | 10                | _    | _                  | dB   |

| RL <sub>RX-CM</sub>                          | Common mode return loss                                              | _                                                      | 6.0               | _    | _                  | dB   |

#### Notes:

- 1. Values are measured at 2.5 Gb/s.

- 2. Measured with external AC-coupling on the receiver.

- 3. Not in compliance with PCI Express 1.1 standard.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## 3.25.2. PCIe (5 Gb/s) – Preliminary AC and DC Characteristics

Over recommended operating conditions.

#### Table 3.31. PCIe (5 Gb/s)

| Symbol                            | Description                                                 | Test Conditions              | Min    | Тур | Max    | Unit       |

|-----------------------------------|-------------------------------------------------------------|------------------------------|--------|-----|--------|------------|

| Transmit <sup>1</sup>             |                                                             |                              |        |     |        |            |

| UI                                | Unit Interval                                               | —                            | 199.94 | 200 | 200.06 | ps         |

| B <sub>WTX-PKG-PLL2</sub>         | Tx PLL bandwidth corresponding to<br>PKGTX-PLL2             | _                            | 5      | -   | 16     | MHz        |

| P <sub>KGTX-PLL2</sub>            | Tx PLL Peaking                                              | _                            | _      | _   | 1      | dB         |

| V <sub>TX-DIFF-PP</sub>           | Differential p-p Tx voltage swing                           | —                            | 0.8    | —   | 1.2    | V, p-p     |

| V <sub>TX-DIFF-PP-LOW</sub>       | Low power differential p-p Tx voltage swing                 | _                            | 0.4    | -   | 1.2    | V, p-p     |

| V <sub>TX-DE-RATIO-3.5dB</sub>    | Tx de-emphasis level ratio at 3.5dB                         | —                            | 3      | —   | 4      | dB         |

| V <sub>TX-DE-RATIO-6dB</sub>      | Tx de-emphasis level ratio at 6dB                           | —                            | 5.5    | —   | 6.5    | dB         |

| T <sub>MIN-PULSE</sub>            | Instantaneous lone pulse width                              | _                            |        | —   | _      | UI         |

| T <sub>TX-RISE-FALL</sub>         | Transmitter rise and fall time                              | _                            |        | —   | _      | UI         |

| T <sub>TX-EYE</sub>               | Transmitter Eye, including all jitter sources               | _                            | 0.75   | _   | _      | UI         |

| T <sub>TX-DJ</sub>                | Tx deterministic jitter > 1.5 MHz                           | —                            | -      | —   | 0.15   | UI         |

| T <sub>TX-RJ</sub>                | Tx RMS jitter < 1.5 MHz                                     | —                            | Ι      | -   | 3      | ps,<br>RMS |

| T <sub>RF-MISMATCH</sub>          | Tx rise/fall time mismatch                                  | _                            | _      | _   |        | UI         |

| R <sub>LTX-DIFF</sub>             | Tx Differential Return Loss, including                      | 50 MHz < freq <<br>1.25 GHz  | 10     | _   | _      | dB         |

| ''LIX-DIFF                        | package and silicon                                         | 1.25 GHz < freq<br>< 2.5 GHz | 8      | _   | _      | dB         |

| R <sub>LTX-CM</sub>               | Tx Common Mode Return Loss, including package and silicon   | 50 MHz < freq <<br>2.5 GHz   | 6      | _   | _      | dB         |

| Z <sub>TX-DIFF-DC</sub>           | DC differential Impedance                                   | _                            | _      | _   | 120    | Ω          |

| V <sub>TX-CM-AC-PP</sub>          | Tx AC peak common mode voltage, peak-peak                   | -                            | -      | -   |        | mV,<br>p-p |

| I <sub>TX-SHORT</sub>             | Transmitter short-circuit current                           | —                            | -      | —   | 90     | mA         |

| V <sub>TX-DC-CM</sub>             | Transmitter DC common-mode voltage                          | _                            | 0      | -   | 1.2    | V          |

| V <sub>TX-IDLE-DIFF-DC</sub>      | Electrical Idle Output DC voltage                           | —                            | 0      | —   | 5      | mV         |

| V <sub>TX-IDLE-DIFF-AC-p</sub>    | Electrical Idle Differential Output<br>peak voltage         | _                            | -      | -   |        | mV         |

| V <sub>TX-RCV-DETECT</sub>        | Voltage change allowed during<br>Receiver Detect            | -                            | -      | -   | 600    | mV         |

| T <sub>TX-IDLE-MIN</sub>          | Min. time in Electrical Idle                                | —                            | 20     | _   | _      | ns         |

| T <sub>TX-IDLE-SET-TO-IDLE</sub>  | Max. time from El Order Set to valid<br>Electrical Idle     | _                            | _      | -   | 8      | ns         |

| T <sub>TX-IDLE-TO-DIFF-DATA</sub> | Max. time from Electrical Idle to valid differential output | _                            | _      | _   | 8      | ns         |

| L <sub>TX-SKEW</sub>              | Lane-to-lane output skew                                    | _                            | _      | _   |        | ps         |

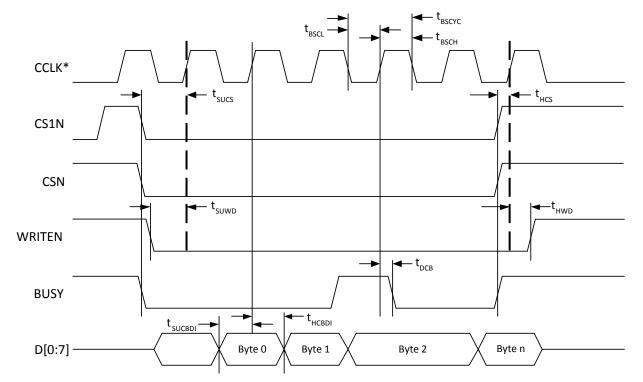

\*In Master Parallel Mode the FPGA provides CCLK (MCLK). In Slave Parallel Mode the external device provides CCLK.

Figure 3.16. sysCONFIG Parallel Port Write Cycle

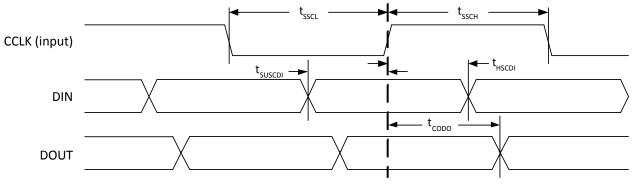

Figure 3.17. sysCONFIG Slave Serial Port Timing

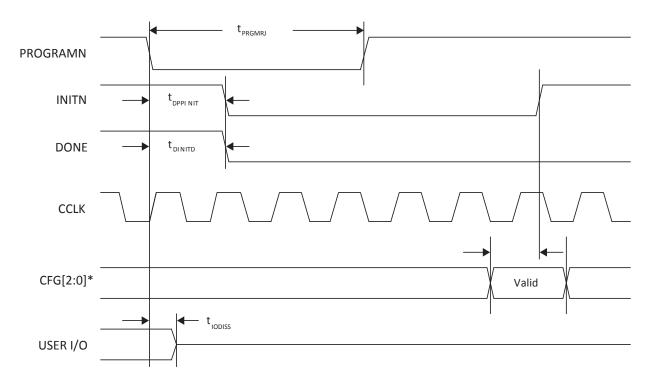

\*The CFG pins are normally static (hardwired).

## 4. Pinout Information

## 4.1. Signal Descriptions

| Signal Name                     | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|---------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| General Purpose                 |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| P[L/R] [Group Number]_[A/B/C/D] | ı/o | <ul> <li>[L/R] indicates the L (Left), or R (Right) edge of the device. [Group Number] indicates the PIO [A/B/C/D] group.</li> <li>[A/B/C/D] indicates the PIO within the PIC to which the pad is connected.</li> <li>Some of these user-programmable pins are shared with special function pins. These pins, when not used as special purpose pins, can be programmed as I/Os for user logic. During configuration the user-programmable I/Os are tristated with an internal pull-down resistor enabled. If any pin is not used (or not bonded to a package pin), it is tristated and default to have pull-down enabled after configuration.</li> <li>PIO A and B are grouped as a pair, and PIO C and D are group as a pair. Each pair supports true LVDS differential input buffer. Only PIO A and B pair supports true LVDS differential output buffer.</li> <li>Each A/B and C/D pair supports programmable on/off differential input termination of 100 Ω.</li> </ul> |  |

| P[T/B][Group Number]_[A/B]      | 1/0 | <ul> <li>[T/B] indicates the T (top) or B (bottom) edge of the device. [Group Number] indicates the PIO [A/B] group.</li> <li>[A/B] indicates the PIO within the PIC to which the pad is connected. Some of these user-programmable pins are shared with sysConfig pins. These pins, when not used as configuration pins, can be programmed as I/Os for user logic. Duri</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| GSRN                            | 1   | Global RESET signal (active low). Any I/O pin can be GSRN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| NC                              | _   | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| RESERVED                        | _   | This pin is reserved and should not be connected to anything on the board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| GND                             | _   | Ground. Dedicated pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| V <sub>cc</sub>                 | -   | Power supply pins for core logic. Dedicated pins. V <sub>CC</sub> = 1.1 V (ECP5), 1.2 V (ECP5UM5G)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| V <sub>CCAUX</sub>              | _   | Auxiliary power supply pin. This dedicated pin powers all the differential and referenced input buffers. $V_{CCAUX} = 2.5 V.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| V <sub>CCIOx</sub>              | _   | Dedicated power supply pins for I/O bank x. $V_{\text{CCIO8}}$ is used for configuration and JTAG.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| VREF1_x                         | _   | Reference supply pins for I/O bank x. Pre-determined shared pin in each bank are assigned as VREF1 input. When not used, they may be used as I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| PLL, DLL and Clock Functions    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| [LOC][_GPLL[T, C]_IN            | I   | General Purpose PLL (GPLL) input pads: [LOC] = ULC, LLC, URC and LRC, T = true and C = complement. These pins are shared I/O pins. When not configured as GPLL input pads, they can be used as general purpose I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| GR_PCLK[Bank][num]              | I   | General Routing Signals in Banks 0, 1, 2, 3, 4, 6 and 7. There are two in each bank ([num] = 0, 1). Refer to ECP5 sysClock PLL/DLL Design and Usage Guide (TN1263). These pins are shared I/O pins. When not configured as GR pins, they can be used as general purpose I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| PCLK[T/C][Bank]_[num]           | I/O | General Purpose Primary CLK pads: [T/C] = True/Complement, [Bank] = (0, 1, 2, 3, 6 and 7). There are two in each bank ([num] = 0, 1). These are shared I/ O pins. When not configured as PCLK pins, they can be used as general purpose I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

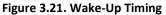

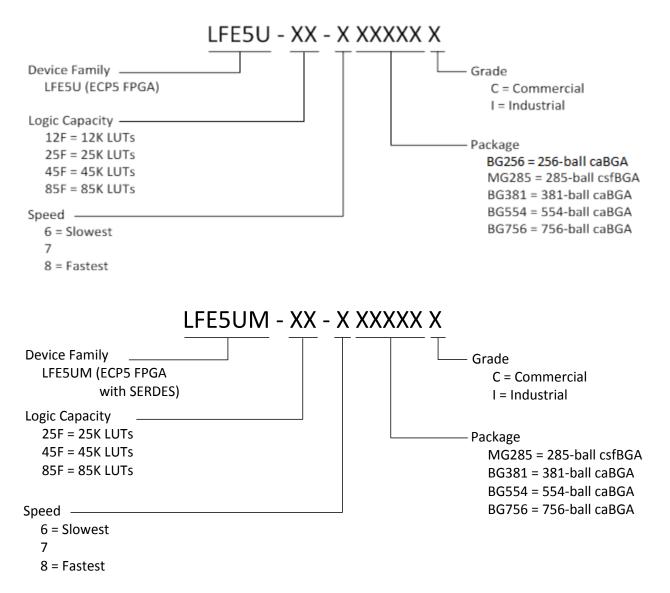

## 5. Ordering Information

## 5.1. ECP5/ECP5-5G Part Number Description

| Part number          | Grade | Package         | Pins | Temp.      | LUTs (K) | SERDES |

|----------------------|-------|-----------------|------|------------|----------|--------|

| LFE5UM5G-85F-8BG381C | -8    | Lead free caBGA | 381  | Commercial | 84       | Yes    |

| LFE5UM5G-85F-8BG554C | -8    | Lead free caBGA | 554  | Commercial | 84       | Yes    |

| LFE5UM5G-85F-8BG756C | -8    | Lead free caBGA | 756  | Commercial | 84       | Yes    |

### 5.2.2. Industrial

| Part number       | Grade | Package          | Pins | Temp.      | LUTs (K) | SERDES |

|-------------------|-------|------------------|------|------------|----------|--------|

| LFE5U-12F-6BG256I | -6    | Lead free caBGA  | 256  | Industrial | 12       | No     |

| LFE5U-12F-7BG256I | -7    | Lead free caBGA  | 256  | Industrial | 12       | No     |

| LFE5U-12F-8BG256I | -8    | Lead free caBGA  | 256  | Industrial | 12       | No     |

| LFE5U-12F-6MG285I | -6    | Lead free csfBGA | 285  | Industrial | 12       | No     |

| LFE5U-12F-7MG285I | -7    | Lead free csfBGA | 285  | Industrial | 12       | No     |

| LFE5U-12F-8MG285I | -8    | Lead free csfBGA | 285  | Industrial | 12       | No     |

| LFE5U-12F-6BG381I | -6    | Lead free caBGA  | 381  | Industrial | 12       | No     |

| LFE5U-12F-7BG381I | -7    | Lead free caBGA  | 381  | Industrial | 12       | No     |

| LFE5U-12F-8BG381I | -8    | Lead free caBGA  | 381  | Industrial | 12       | No     |

| LFE5U-25F-6BG256I | -6    | Lead free caBGA  | 256  | Industrial | 24       | No     |

| LFE5U-25F-7BG256I | -7    | Lead free caBGA  | 256  | Industrial | 24       | No     |

| LFE5U-25F-8BG256I | -8    | Lead free caBGA  | 256  | Industrial | 24       | No     |

| LFE5U-25F-6MG285I | -6    | Lead free csfBGA | 285  | Industrial | 24       | No     |

| LFE5U-25F-7MG285I | -7    | Lead free csfBGA | 285  | Industrial | 24       | No     |

| LFE5U-25F-8MG285I | -8    | Lead free csfBGA | 285  | Industrial | 24       | No     |

| LFE5U-25F-6BG381I | -6    | Lead free caBGA  | 381  | Industrial | 24       | No     |

| LFE5U-25F-7BG381I | -7    | Lead free caBGA  | 381  | Industrial | 24       | No     |

| LFE5U-25F-8BG381I | -8    | Lead free caBGA  | 381  | Industrial | 24       | No     |

| LFE5U-45F-6BG256I | -6    | Lead free caBGA  | 256  | Industrial | 44       | No     |

| LFE5U-45F-7BG256I | -7    | Lead free caBGA  | 256  | Industrial | 44       | No     |

| LFE5U-45F-8BG256I | -8    | Lead free caBGA  | 256  | Industrial | 44       | No     |

| LFE5U-45F-6MG285I | -6    | Lead free csfBGA | 285  | Industrial | 44       | No     |

| LFE5U-45F-7MG285I | -7    | Lead free csfBGA | 285  | Industrial | 44       | No     |

| LFE5U-45F-8MG285I | -8    | Lead free csfBGA | 285  | Industrial | 44       | No     |

| LFE5U-45F-6BG381I | -6    | Lead free caBGA  | 381  | Industrial | 44       | No     |

| LFE5U-45F-7BG381I | -7    | Lead free caBGA  | 381  | Industrial | 44       | No     |

| LFE5U-45F-8BG381I | -8    | Lead free caBGA  | 381  | Industrial | 44       | No     |

| LFE5U-45F-6BG554I | -6    | Lead free caBGA  | 554  | Industrial | 44       | No     |

| LFE5U-45F-7BG554I | -7    | Lead free caBGA  | 554  | Industrial | 44       | No     |

| LFE5U-45F-8BG554I | -8    | Lead free caBGA  | 554  | Industrial | 44       | No     |

| LFE5U-85F-6MG285I | -6    | Lead free csfBGA | 285  | Industrial | 84       | No     |

| LFE5U-85F-7MG285I | -7    | Lead free csfBGA | 285  | Industrial | 84       | No     |

| LFE5U-85F-8MG285I | -8    | Lead free csfBGA | 285  | Industrial | 84       | No     |

| LFE5U-85F-6BG381I | -6    | Lead free caBGA  | 381  | Industrial | 84       | No     |

| LFE5U-85F-7BG381I | -7    | Lead free caBGA  | 381  | Industrial | 84       | No     |

| LFE5U-85F-8BG381I | -8    | Lead free caBGA  | 381  | Industrial | 84       | No     |

| LFE5U-85F-6BG554I | -6    | Lead free caBGA  | 554  | Industrial | 84       | No     |

| LFE5U-85F-7BG554I | -7    | Lead free caBGA  | 554  | Industrial | 84       | No     |

| LFE5U-85F-8BG554I | -8    | Lead free caBGA  | 554  | Industrial | 84       | No     |

## **Revision History**

| Date           | Version | Section                     | Change Summary                                                                                                                |

|----------------|---------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| March 2018 1.9 | 1.9     | All                         | Updated formatting and page referencing.                                                                                      |

|                |         | General Description         | Updated Table 1.1. ECP5 and ECP5-5G Family Selection Guide. Added caBGA256 package in LFE5U-45.                               |

|                |         | Architecture                | Added a row for SGMII in Table 2.13. LFE5UM/LFE5UM5G SERDES<br>Standard Support. Updated footnote #1.                         |

|                |         | DC and Switching            | Updated Table 3.2. Recommended Operating Conditions.                                                                          |

|                |         | Characteristics             | Added 2 rows and updated values in Table 3.7. DC Electrical Characteristics.                                                  |

|                |         |                             | Updated Table 3.8. ECP5/ECP5-5G Supply Current (Standby).                                                                     |

|                |         |                             | Updated Table 3.11. sysl/O Recommended Operating Conditions.                                                                  |

|                |         |                             | Updated Table 3.12. Single-Ended DC Characteristics.                                                                          |

|                |         |                             | Updated Table 3.13. LVDS.                                                                                                     |

|                |         |                             | Updated Table 3.14. LVDS25E DC Conditions.                                                                                    |

|                |         |                             | Updated Table 3.21. ECP5/ECP5-5G Maximum I/O Buffer Speed.                                                                    |

|                |         |                             | Updated Table 3.28. Receiver Total Jitter Tolerance Specification.                                                            |

|                |         |                             | Updated header name of section 3.28 CPRI LV E.24/SGMII(2.5Gbps)<br>Electrical and Timing Characteristics.                     |

|                |         |                             | Updated header name of section 3.29 Gigabit<br>Ethernet/SGMII(1.25Gbps)/CPRI LV E.12 Electrical and Timing<br>Characteristics |

|                |         | Pinout Information          | Updated table in section 4.3.2 LFE5U.                                                                                         |

|                |         | Ordering Information        | Added table rows in 5.2.1 Commercial.                                                                                         |

|                |         |                             | Added table rows in 5.2.2 Industrial.                                                                                         |

|                |         | Supplemental<br>Information | Updated For Further Information section.                                                                                      |

| November 2017  | 1.8     | General Description         | Updated Table 1.1. ECP5 and ECP5-5G Family Selection Guide. Added caBGA256 package in LFE5U-12 and LFE5U-25.                  |

## (Continued)

| Date              | Version | Section                             | Change Summary                                                                                                                        |

|-------------------|---------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| November 2015 1.5 | 1.5 All |                                     | Added ECP5-5G device family.                                                                                                          |

|                   |         |                                     | Changed document title to ECP5 and ECP5-5G Family Data Sheet.                                                                         |

|                   | 1.4     | General Description                 | Updated Features section. Added support for eDP in RDR and HDR.                                                                       |

|                   |         | Architecture                        | Updated Overview section.                                                                                                             |

|                   |         |                                     | Revised Figure 2.1. Simplified Block Diagram, LFE5UM/LFE5UM5G-85<br>Device (Top Level). Modified Flexible sysIO description and Note. |

|                   |         |                                     | Updated SERDES and Physical Coding Sublayer section.                                                                                  |

|                   |         |                                     | Changed E.24.V in CPRI protocol to E.24.LV.                                                                                           |

|                   |         |                                     | • Removed "1.1 V" from paragraph on unused Dual.                                                                                      |

|                   |         | DC and Switching                    | Updated Hot Socketing Requirements section. Revised $V_{CCHTX}$ in table                                                              |

|                   |         | Characteristics                     | notes 1 and 3. Indicated V <sub>CCHTX</sub> in table note 4.                                                                          |

|                   |         |                                     | Updated SERDES High-Speed Data Transmitter section. Revised $V_{CCHTX}$                                                               |

|                   |         | in table note 1.                    |                                                                                                                                       |

|                   |         | Ordering Information                | Updated ECP5/ECP5-5G Part Number Description section. Changed<br>"LFE5 FPGA" under Device Family to "ECP5 FPGA".                      |

| August 2015       | 1.3     | General Description                 | Updated Features section.                                                                                                             |

|                   |         |                                     | Removed SMPTE3G under Embedded SERDES.                                                                                                |

|                   |         |                                     | Added Single Event Upset (SEU) Mitigation Support.                                                                                    |

|                   |         |                                     | Removed SMPTE protocol in fifth paragraph.                                                                                            |

|                   |         | Architecture                        | General update.                                                                                                                       |

|                   |         | DC and Switching<br>Characteristics | General update.                                                                                                                       |

|                   |         | Pinout Information                  | Updated Signal Descriptions section. Revised the descriptions of the following signals:                                               |

|                   |         |                                     | • P[L/R] [Group Number]_[A/B/C/D]                                                                                                     |

|                   |         |                                     | • P[T/B][Group Number]_[A/B]                                                                                                          |

|                   |         |                                     | D4/IO4 (Previously named D4/MOSI2/IO4)                                                                                                |

|                   |         |                                     | D5/IO5 (Previously named D5/MISO/IO5)                                                                                                 |

|                   |         |                                     | <ul> <li>VCCHRX_D[dual_num]CH[chan_num]</li> </ul>                                                                                    |

|                   | ļ       |                                     | VCCHTX_D[dual_num]CH[chan_num]                                                                                                        |

|                   |         | Supplemental<br>Information         | Added TN1184 reference.                                                                                                               |