# E. Flattice Semiconductor Corporation - <u>LFE5UM5G-85F-8BG381I Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                          |

|--------------------------------|---------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 21000                                                                           |

| Number of Logic Elements/Cells | 84000                                                                           |

| Total RAM Bits                 | 3833856                                                                         |

| Number of I/O                  | 205                                                                             |

| Number of Gates                | -                                                                               |

| Voltage - Supply               | 1.045V ~ 1.155V                                                                 |

| Mounting Type                  | Surface Mount                                                                   |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                              |

| Package / Case                 | 381-FBGA                                                                        |

| Supplier Device Package        | 381-CABGA (17x17)                                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe5um5g-85f-8bg381i |

|                                |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Figures

| Figure 2.1. Simplified Block Diagram, LFE5UM/LFE5UM5G-85 Device (Top Level)    | 13 |

|--------------------------------------------------------------------------------|----|

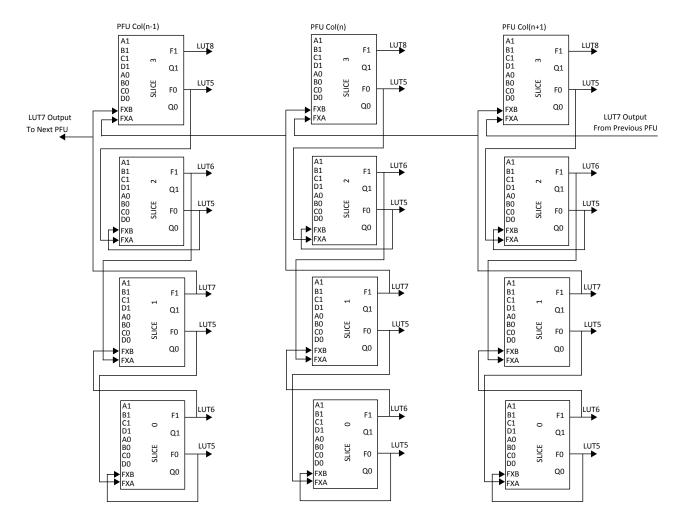

| Figure 2.2. PFU Diagram                                                        | 14 |

| Figure 2.3. Slice Diagram                                                      | 15 |

| Figure 2.4. Connectivity Supporting LUT5, LUT6, LUT7, and LUT8                 | 16 |

| Figure 2.5. General Purpose PLL Diagram                                        | 18 |

| Figure 2.6. LFE5UM/LFE5UM5G-85 Clocking                                        | 20 |

| Figure 2.7. DCS Waveforms                                                      | 21 |

| Figure 2.8. Edge Clock Sources per Bank                                        | 22 |

| Figure 2.9. ECP5/ECP5-5G Clock Divider Sources                                 | 22 |

| Figure 2.10. DDRDLL Functional Diagram                                         |    |

| Figure 2.11. ECP5/ECP5-5G DLL Top Level View (For LFE-45 and LFE-85)           |    |

| Figure 2.12. Memory Core Reset                                                 |    |

| Figure 2.13. Comparison of General DSP and ECP5/ECP5-5G Approaches             | 27 |

| Figure 2.14. Simplified sysDSP Slice Block Diagram                             | 28 |

| Figure 2.15. Detailed sysDSP Slice Diagram                                     |    |

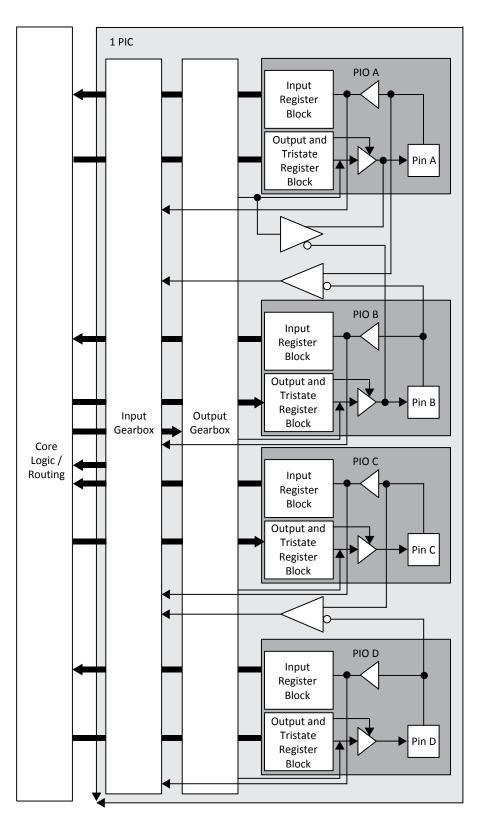

| Figure 2.16. Group of Four Programmable I/O Cells on Left/Right Sides          |    |

| Figure 2.17. Input Register Block for PIO on Top Side of the Device            |    |

| Figure 2.18. Input Register Block for PIO on Left and Right Side of the Device |    |

| Figure 2.19. Output Register Block on Top Side                                 |    |

| Figure 2.20. Output Register Block on Left and Right Sides                     |    |

| Figure 2.21. Tristate Register Block on Top Side                               |    |

| Figure 2.22. Tristate Register Block on Left and Right Sides                   |    |

| Figure 2.23. DQS Grouping on the Left and Right Edges                          |    |

| Figure 2.24. DQS Control and Delay Block (DQSBUF)                              |    |

| Figure 2.25. ECP5/ECP5-5G Device Family Banks                                  |    |

| Figure 2.26. On-Chip Termination                                               |    |

| Figure 2.27. SERDES/PCS Duals (LFE5UM/LFE5UM5G-85)                             |    |

| Figure 2.28. Simplified Channel Block Diagram for SERDES/PCS Block             |    |

| Figure 3.1. LVDS25E Output Termination Example                                 |    |

| Figure 3.2. BLVDS25 Multi-point Output Example                                 |    |

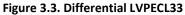

| Figure 3.3. Differential LVPECL33                                              |    |

| Figure 3.4. MLVDS25 (Multipoint Low Voltage Differential Signaling)            |    |

| Figure 3.5. SLVS Interface                                                     |    |

| Figure 3.6. Receiver RX.CLK.Centered Waveforms                                 |    |

| Figure 3.7. Receiver RX.CLK.Aligned and DDR Memory Input Waveforms             |    |

| Figure 3.8. Transmit TX.CLK.Centered and DDR Memory Output Waveforms           |    |

| Figure 3.9. Transmit TX.CLK.Aligned Waveforms                                  |    |

| Figure 3.10. DDRX71 Video Timing Waveforms                                     |    |

| Figure 3.11. Receiver DDRX71 RX Waveforms                                      |    |

| Figure 3.12. Transmitter DDRX71_TX Waveforms                                   |    |

| Figure 3.13. Transmitter and Receiver Latency Block Diagram                    |    |

| Figure 3.14. SERDES External Reference Clock Waveforms                         |    |

| Figure 3.15. sysCONFIG Parallel Port Read Cycle                                |    |

| Figure 3.16. sysCONFIG Parallel Port Write Cycle                               |    |

| Figure 3.17. sysCONFIG Slave Serial Port Timing                                |    |

| Figure 3.18. Power-On-Reset (POR) Timing                                       |    |

| Figure 3.19. sysCONFIG Port Timing                                             |    |

| Figure 3.20. Configuration from PROGRAMN Timing                                |    |

| Figure 3.21. Wake-Up Timing                                                    |    |

| Figure 3.22. Master SPI Configuration Waveforms                                |    |

| Figure 3.23. JTAG Port Timing Waveforms                                        |    |

| Figure 3.24. Output Test Load, LVTTL and LVCMOS Standards                      |    |

| J ,                                                                            |    |

<sup>© 2014-2018</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Table 3.36. Receive and Jitter Tolerance                                |    |

|-------------------------------------------------------------------------|----|

| Table 3.37. Transmit                                                    |    |

| Table 3.38. Receive and Jitter Tolerance                                |    |

| Table 3.39. Transmit                                                    | 82 |

| Table 3.40. Receive                                                     | 82 |

| Table 3.41. Reference Clock                                             | 82 |

| Table 3.42. ECP5/ECP5-5G sysCONFIG Port Timing Specifications           | 83 |

| Table 3.43. JTAG Port Timing Specifications                             |    |

| Table 3.44. Test Fixture Required Components, Non-Terminated Interfaces |    |

|                                                                         |    |

## Acronyms in This Document

A list of acronyms used in this document.

| ALUArithmetic Logic UnitBGABall Grid ArrayCDRClock and Data RecoveryCRCCycle Redundancy CodeDCCDynamic Clock ControlDCSDynamic Clock SelectDDRDouble Data RateDLLDelay-Locked LoopsDSPDigital Signal ProcessingEBREmbedded Block RAMECLKEdge ClockFFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Transistor-Transistor LogicLVTLLow Voltage Transistor-Transistor LogicLVTLPripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSERDESSerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access PortTDMTime D | Acronym | Definition                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------------------------|

| CDRClock and Data RecoveryCRCCycle Redundancy CodeDCCDynamic Clock ControlDCSDynamic Clock SelectDDRDouble Data RateDLLDelay-Locked LoopsDSPDigital Signal ProcessingEBREmbedded Block RAMECLKEdge ClockFFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Transistor-Transistor LogicLVTLLow Voltage Positive Emitter Coupled LogicLVTLLow Voltage Transistor-Transistor LogicLVTLPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                       | ALU     | Arithmetic Logic Unit                               |

| CRCCycle Redundancy CodeDCCDynamic Clock ControlDCSDynamic Clock SelectDDRDouble Data RateDLLDelay-Locked LoopsDSPDigital Signal ProcessingEBREmbedded Block RAMECLKEdge ClockFFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                               | BGA     | Ball Grid Array                                     |

| DCCDynamic Clock ControlDCSDynamic Clock SelectDDRDouble Data RateDLLDelay-Locked LoopsDSPDigital Signal ProcessingEBREmbedded Block RAMECLKEdge ClockFFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                       | CDR     | Clock and Data Recovery                             |

| DCSDynamic Clock SelectDDRDouble Data RateDLLDelay-Locked LoopsDSPDigital Signal ProcessingEBREmbedded Block RAMECLKEdge ClockFFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICSeralizer/DeserializerSERDESSerializer/DeserializerSELUSingle Event UpsetSERDESSerializer/DeserializerSELUSingle Port RAMSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                               | CRC     | Cycle Redundancy Code                               |

| DDRDouble Data RateDLLDelay-Locked LoopsDSPDigital Signal ProcessingEBREmbedded Block RAMECLKEdge ClockFFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICSERDES Client InterfaceSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                            | DCC     | Dynamic Clock Control                               |

| DLLDelay-Locked LoopsDSPDigital Signal ProcessingEBREmbedded Block RAMECLKEdge ClockFFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICSERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                         | DCS     | Dynamic Clock Select                                |

| DSPDigital Signal ProcessingEBREmbedded Block RAMECLKEdge ClockFFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICSERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                             | DDR     | Double Data Rate                                    |

| EBREmbedded Block RAMECLKEdge ClockFFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable Functional UnitPICSERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                          | DLL     | Delay-Locked Loops                                  |

| ECLKEdge ClockFFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTLLow Voltage Transistor-Transistor LogicLVTTLLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                              | DSP     | Digital Signal Processing                           |

| FFTFast Fourier TransformsFIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                             | EBR     | Embedded Block RAM                                  |

| FIFOFirst In First OutFIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable Functional UnitPICSERDES Client InterfaceSCISERDES Client InterfaceSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                          | ECLK    | Edge Clock                                          |

| FIRFinite Impulse ResponseLVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable Functional UnitPICSERDES Client InterfaceSCISERDES Client InterfaceSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                | FFT     | Fast Fourier Transforms                             |

| LVCMOSLow-Voltage Complementary Metal Oxide SemiconductorLVDSLow-Voltage Differential SignalingLVPECLLow Voltage Positive Emitter Coupled LogicLVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                    | FIFO    | First In First Out                                  |

| LVDSLow-Voltage Differential SignalingLVPECLLow-Voltage Positive Emitter Coupled LogicLVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FIR     | Finite Impulse Response                             |

| LVPECLLow Voltage Positive Emitter Coupled LogicLVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LVCMOS  | Low-Voltage Complementary Metal Oxide Semiconductor |

| LVTTLLow Voltage Transistor-Transistor LogicLUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LVDS    | Low-Voltage Differential Signaling                  |

| LUTLook Up TableMLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LVPECL  | Low Voltage Positive Emitter Coupled Logic          |

| MLVDSMultipoint Low-Voltage Differential SignalingPCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LVTTL   | Low Voltage Transistor-Transistor Logic             |

| PCIPeripheral Component InterconnectPCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LUT     | Look Up Table                                       |

| PCSPhysical Coding SublayerPCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MLVDS   | Multipoint Low-Voltage Differential Signaling       |

| PCLKPrimary ClockPDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PCI     | Peripheral Component Interconnect                   |

| PDPRPseudo Dual Port RAMPFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PCS     | Physical Coding Sublayer                            |

| PFUProgrammable Functional UnitPICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PCLK    | Primary Clock                                       |

| PICProgrammable I/O CellsPLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PDPR    | Pseudo Dual Port RAM                                |

| PLLPhase-Locked LoopsPORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PFU     | Programmable Functional Unit                        |

| PORPower On ResetSCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PIC     | Programmable I/O Cells                              |

| SCISERDES Client InterfaceSERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PLL     | Phase-Locked Loops                                  |

| SERDESSerializer/DeserializerSEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | POR     | Power On Reset                                      |

| SEUSingle Event UpsetSLVSScalable Low-Voltage SignalingSPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SCI     | SERDES Client Interface                             |

| SLVS       Scalable Low-Voltage Signaling         SPI       Serial Peripheral Interface         SPR       Single Port RAM         SRAM       Static Random-Access Memory         TAP       Test Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SERDES  | Serializer/Deserializer                             |

| SPISerial Peripheral InterfaceSPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SEU     | Single Event Upset                                  |

| SPRSingle Port RAMSRAMStatic Random-Access MemoryTAPTest Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SLVS    | Scalable Low-Voltage Signaling                      |

| SRAM     Static Random-Access Memory       TAP     Test Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SPI     | Serial Peripheral Interface                         |

| TAP Test Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SPR     | Single Port RAM                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SRAM    | Static Random-Access Memory                         |

| TDM Time Division Multiplexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ТАР     | Test Access Port                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TDM     | Time Division Multiplexing                          |

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Figure 2.4. Connectivity Supporting LUT5, LUT6, LUT | 7, and LUT8 |

|-----------------------------------------------------|-------------|

|-----------------------------------------------------|-------------|

| Table | 2.2. | Slice | Signal | Descriptions |

|-------|------|-------|--------|--------------|

|-------|------|-------|--------|--------------|

| Function | Туре               | Signal Names   | Description                                                      |

|----------|--------------------|----------------|------------------------------------------------------------------|

| Input    | Data signal        | A0, B0, C0, D0 | Inputs to LUT4                                                   |

| Input    | Data signal        | A1, B1, C1, D1 | Inputs to LUT4                                                   |

| Input    | Multi-purpose      | M0             | Multipurpose Input                                               |

| Input    | Multi-purpose      | M1             | Multipurpose Input                                               |

| Input    | Control signal     | CE             | Clock Enable                                                     |

| Input    | Control signal     | LSR            | Local Set/Reset                                                  |

| Input    | Control signal     | CLK            | System Clock                                                     |

| Input    | Inter-PFU signal   | FCI            | Fast Carry-in <sup>1</sup>                                       |

| Input    | Inter-slice signal | FXA            | Intermediate signal to generate LUT6, LUT7 and LUT8 <sup>2</sup> |

| Input    | Inter-slice signal | FXB            | Intermediate signal to generate LUT6, LUT7 and LUT8 <sup>2</sup> |

| Output   | Data signals       | F0, F1         | LUT4 output register bypass signals                              |

| Output   | Data signals       | Q0, Q1         | Register outputs                                                 |

| Output   | Inter-PFU signal   | FCO            | Fast carry chain output <sup>1</sup>                             |

Notes:

2. Requires two adjacent PFUs.

<sup>1.</sup> See Figure 2.3 on page 15 for connection details.

## 2.11. **PIO**

The PIO contains three blocks: an input register block, output register block, and tristate register block. These blocks contain registers for operating in a variety of modes along with the necessary clock and selection logic.

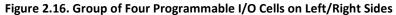

#### 2.11.1. Input Register Block

The input register blocks for the PIOs on all edges contain delay elements and registers that can be used to condition high-speed interface signals before they are passed to the device core. In addition, the input register blocks for the PIOs on the left and right edges include built-in FIFO logic to interface to DDR and LPDDR memory.

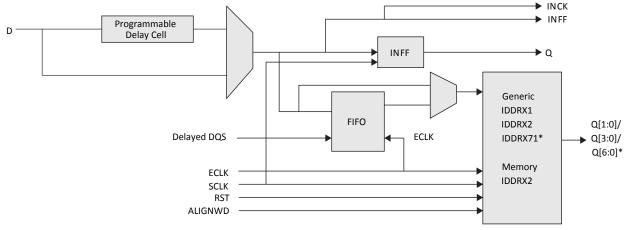

The Input register block on the right and left sides includes gearing logic and registers to implement IDDRX1 and IDDRX2 functions. With two PICs sharing the DDR register path, it can also implement IDDRX71 function used for 7:1 LVDS interfaces. It uses three sets of registers to shift, update, and transfer to implement gearing and the clock domain transfer. The first stage registers samples the high-speed input data by the high-speed edge clock on its rising and falling edges. The second stage registers perform data alignment based on the control signals. The third stage pipeline registers pass the data to the device core synchronized to the low-speed system clock. The top side of the device supports IDDRX1 gearing function. For more information on gearing function, refer to ECP5 and ECP5-5G High-Speed I/O Interface (TN1265).

Figure 2.17 shows the input register block for the PIOs on the top edge.

Figure 2.17. Input Register Block for PIO on Top Side of the Device

Figure 2.18 shows the input register block for the PIOs located on the left and right edges.

\*For 7:1 LVDS interface only. It is required to use PIO pair pins (PIOA/B or PIOC/D).

#### Figure 2.18. Input Register Block for PIO on Left and Right Side of the Device

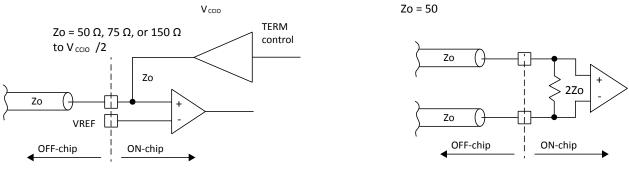

#### 2.14.4. On-Chip Programmable Termination

The ECP5/ECP5-5G devices support a variety of programmable on-chip terminations options, including:

- Dynamically switchable Single-Ended Termination with programmable resistor values of 50  $\Omega$ , 75  $\Omega$ , or 150  $\Omega$ .

- Common mode termination of 100 Ω for differential inputs.

Parallel Single-Ended Input

Differential Input

Figure 2.26. On-Chip Termination

See Table 2.12 for termination options for input modes.

| IO_TYPE         | Terminate to V <sub>CCIO</sub> /2* | Differential Termination Resistor* |

|-----------------|------------------------------------|------------------------------------|

| LVDS25          | _                                  | 100                                |

| BLVDS25         | —                                  | 100                                |

| MLVDS           | —                                  | 100                                |

| LVPECL33        | —                                  | 100                                |

| subLVDS         | —                                  | 100                                |

| SLVS            | _                                  | 100                                |

| HSUL12          | 50, 75, 150                        | —                                  |

| HSUL12D         | —                                  | 100                                |

| SSTL135_I / II  | 50, 75, 150                        | —                                  |

| SSTL135D_I / II | —                                  | 100                                |

| SSTL15_I / II   | 50, 75, 150                        | -                                  |

| SSTL15D_I / II  | —                                  | 100                                |

| SSTL18_I / II   | 50, 75, 150                        | -                                  |

| SSTL18D_I / II  | _                                  | 100                                |

\*Notes:

TERMINATE to  $V_{CCIO}/2$  (Single-Ended) and DIFFRENTIAL TERMINATION RESISTOR when turned on can only have one setting per bank. Only left and right banks have this feature.

Use of TERMINATE to  $V_{CCIO}/2$  and DIFFRENTIAL TERMINATION RESISTOR are mutually exclusive in an I/O bank. On-chip termination tolerance ±20%.

Refer to ECP5 and ECP5-5G sysIO Usage Guide (TN1262) for on-chip termination usage and value ranges.

#### 2.14.5. Hot Socketing

ECP5/ECP5-5G devices have been carefully designed to ensure predictable behavior during power-up and power-down. During power-up and power-down sequences, the I/Os remain in tristate until the power supply voltage is high enough to ensure reliable operation. In addition, leakage into I/O pins is controlled within specified limits. See the Hot Socketing Specifications section on page 48.

## 2.15. SERDES and Physical Coding Sublayer

LFE5UM/LFE5UM5G devices feature up to 4 channels of embedded SERDES/PCS arranged in dual-channel blocks at the bottom of the devices. Each channel supports up to 3.2 Gb/s (ECP5), or up to 5 Gb/s (ECP5-5G) data rate. Figure 2.27 shows the position of the dual blocks for the LFE5-85. Table 2.13 shows the location of available SERDES Duals for all devices. The LFE5UM/LFE5UM5G SERDES/PCS supports a range of popular serial protocols, including:

- PCI Express Gen1 and Gen2 (2.5 Gb/s) on ECP5UM; Gen 1, Gen2 (2.5 Gb/s and 5 Gb/s) on ECP5-5G

- Ethernet (XAUI, GbE 1000 Base CS/SX/LX and SGMII)

- SMPTE SDI (3G-SDI, HD-SDI, SD-SDI)

- CPRI (E.6.LV: 614.4 Mb/s, E.12.LV: 1228.8 Mb/s, E.24.LV: 2457.6 Mb/s, E.30.LV: 3072 Mb/s), also E.48.LV2:4915 Mb/s in ECP5-5G

- JESD204A/B ADC and DAC converter interface: 312.5 Mb/s to 3.125 Gb/s (ECP5) / 5 Gb/s (ECP5-5G)

Each dual contains two dedicated SERDES for high speed, full duplex serial data transfer. Each dual also has a PCS block that interfaces to the SERDES channels and contains protocol specific digital logic to support the standards listed above. The PCS block also contains interface logic to the FPGA fabric. All PCS logic for dedicated protocol support can also be bypassed to allow raw 8-bit or 10-bit interfaces to the FPGA fabric.

Even though the SERDES/PCS blocks are arranged in duals, multiple baud rates can be supported within a dual with the use of dedicated, per channel /1, /2 and /11 rate dividers. Additionally, two duals can be arranged together to form x4 channel link.

ECP5UM devices and ECP5-5G devices are pin-to-pin compatible. But, the ECP5UM devices require 1.1 V on VCCA, VCCHRX and VCCHTX supplies. ECP5-5G devices require 1.2 V on these supplies. When designing either family device with migration in mind, these supplies need to be connected such that it is possible to adjust the voltage level on these supplies.

When a SERDES Dual in a 2-Dual device is not used, the power VCCA power supply for that Dual should be connected. It is advised to connect the VCCA of unused channel to core if the user knows he will not use the Dual at all, or it should be connected to a different regulated supply, if that Dual may be used in the future.

For an unused channel in a Dual, it is advised to connect the VCCHTX to VCCA, and user can leave VCCHRX unconnected.

For information on how to use the SERDES/PCS blocks to support specific protocols, as well on how to combine multiple protocols and baud rates within a device, refer to ECP5 and ECP5-5G SERDES/PCS Usage Guide (TN1261).

## 3.7. Hot Socketing Requirements

#### **Table 3.6. Hot Socketing Requirements**

| Description                                                                               | Min | Тур | Max | Unit |

|-------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Input current per SERDES I/O pin when device is powered down and inputs driven.           | _   | _   | 8   | mA   |

| Input current per HDIN pin when device power supply is off, inputs driven <sup>1, 2</sup> | _   | _   | 15  | mA   |

| Current per HDIN pin when device power ramps up, input driven <sup>3</sup>                | _   | _   | 50  | mA   |

| Current per HDOUT pin when device power supply is off, outputs pulled up <sup>4</sup>     | —   | —   | 30  | mA   |

Notes:

1. Device is powered down with all supplies grounded, both HDINP and HDINN inputs driven by a CML driver with maximum allowed output V<sub>CCHTX</sub>, 8b/10b data, no external AC coupling.

2. Each P and N input must have less than the specified maximum input current during hot plug. For a device with 2 DCU, the total input current would be 15 mA \* 4 channels \* 2 input pins per channel = 120 mA.

- Device power supplies are ramping up (V<sub>CCA</sub> and V<sub>CCAUX</sub>), both HDINP and HDINN inputs are driven by a CML driver with maximum allowed output V<sub>CCHTX</sub>, 8b/10b data, internal AC coupling.

- 4. Device is powered down with all supplies grounded. Both HDOUTP and HDOUN outputs are pulled up to  $V_{CCHTX}$  by the far end receiver termination of 50  $\Omega$  single ended.

## 3.8. ESD Performance

Refer to the ECP5 and ECP5-5G Product Family Qualification Summary for complete qualification data, including ESD performance.

## 3.9. DC Electrical Characteristics

**Over Recommended Operating Conditions**

| Symbol                                            | Parameter                                                        | Condition                                                                                                                                             | Min | Тур | Max  | Unit |

|---------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| I <sub>IL</sub> , I <sub>IH</sub> <sup>1, 4</sup> | Input or I/O Low Leakage                                         | $0 \leq V_{\text{IN}} \leq V_{\text{CCIO}}$                                                                                                           | _   | —   | 10   | μA   |

| I <sub>IH</sub> <sup>1, 3</sup>                   | Input or I/O High Leakage                                        | $V_{CCIO} < V_{IN} \leq V_{IH(MAX)}$                                                                                                                  | —   | —   | 100  | μA   |

| I                                                 | I/O Active Pull-up Current,<br>sustaining logic HIGH state       | $0.7 \: V_{CCIO} \! \leq \! V_{IN} \! \leq \! V_{CCIO}$                                                                                               | -30 | _   | _    | μA   |

| I <sub>PU</sub>                                   | I/O Active Pull-up Current, pulling down from logic HIGH state   | $0 \leq V_{\text{IN}} \leq 0.7 \; V_{\text{CCIO}}$                                                                                                    |     | _   | -150 | μA   |

| 1                                                 | I/O Active Pull-down Current,<br>sustaining logic LOW state      | $0 \le V_{IN} \le V_{IL}$ (MAX)                                                                                                                       | 30  | —   | —    | μA   |

| I <sub>PD</sub>                                   | I/O Active Pull-down Current,<br>pulling up from logic LOW state | $0 \leq V_{IN} \leq V_{CCIO}$                                                                                                                         | —   | —   | 150  | μA   |

| C1                                                | I/O Capacitance <sup>2</sup>                                     | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V}, \\ V_{CC} = 1.2 \text{ V}, V_{IO} = 0 \text{ to } V_{IH(MAX)}$ | _   | 5   | 8    | pf   |

| C2                                                | Dedicated Input Capacitance <sup>2</sup>                         | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V}, \\ V_{CC} = 1.2 \text{ V}, V_{IO} = 0 \text{ to } V_{IH(MAX)}$ | _   | 5   | 7    | pf   |

| V                                                 | Hysteresis for Single-Ended                                      | V <sub>CCIO</sub> = 3.3 V                                                                                                                             | -   | 300 | _    | mV   |

| V <sub>HYST</sub>                                 | Inputs                                                           | V <sub>CCIO</sub> = 2.5 V                                                                                                                             | _   | 250 | _    | mV   |

#### **Table 3.7. DC Electrical Characteristics**

Notes:

1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tristated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

2. T<sub>A</sub> 25 °C, f = 1.0 MHz.

- 3. Applicable to general purpose I/Os in top and bottom banks.

- 4. When used as  $V_{REF}$ , maximum leakage= 25  $\mu$ A.

## 3.14. sysl/O Differential Electrical Characteristics

#### 3.14.1. LVDS

Over recommended operating conditions.

#### Table 3.13. LVDS

| Parameter                        | Description                                                | Test Conditions                                              | Min   | Тур  | Max   | Unit |

|----------------------------------|------------------------------------------------------------|--------------------------------------------------------------|-------|------|-------|------|

| $V_{\text{INP}}, V_{\text{INM}}$ | Input Voltage                                              | -                                                            | 0     | _    | 2.4   | V    |

| V <sub>CM</sub>                  | Input Common Mode Voltage                                  | Half the sum of the two Inputs                               | 0.05  | —    | 2.35  | V    |

| V <sub>THD</sub>                 | Differential Input Threshold                               | Difference between the two Inputs                            | ±100  | _    | _     | mV   |

| I <sub>IN</sub>                  | Input Current                                              | Power On or Power Off                                        | -     | —    | ±10   | μΑ   |

| V <sub>OH</sub>                  | Output High Voltage for $V_{\text{OP}}$ or $V_{\text{OM}}$ | R <sub>T</sub> = 100 Ω                                       | -     | 1.38 | 1.60  | V    |

| V <sub>OL</sub>                  | Output Low Voltage for $V_{OP}$ or $V_{OM}$                | R <sub>T</sub> = 100 Ω                                       | 0.9 V | 1.03 | _     | V    |

| V <sub>OD</sub>                  | Output Voltage Differential                                | (V <sub>OP</sub> - V <sub>OM</sub> ), R <sub>T</sub> = 100 Ω | 250   | 350  | 450   | mV   |

| $\Delta V_{\text{OD}}$           | Change in $V_{\text{OD}}$ Between High and Low             | _                                                            | _     | _    | 50    | mV   |

| V <sub>OS</sub>                  | Output Voltage Offset                                      | $(V_{OP} + V_{OM})/2, R_T = 100 \Omega$                      | 1.125 | 1.25 | 1.375 | V    |

| $\Delta V_{OS}$                  | Change in Vos Between H and L                              | —                                                            | -     | _    | 50    | mV   |

| I <sub>SAB</sub>                 | Output Short Circuit Current                               | V <sub>OD</sub> = 0 V Driver outputs shorted to each other   | _     | _    | 12    | mA   |

**Note**: On the left and right sides of the device, this specification is valid only for  $V_{CCIO} = 2.5$  V or 3.3 V.

### 3.14.2. **SSTLD**

All differential SSTL outputs are implemented as a pair of complementary single-ended outputs. All allowable single-ended output classes (class I and class II) are supported in this mode.

#### 3.14.3. LVCMOS33D

All I/O banks support emulated differential I/O using the LVCMOS33D I/O type. This option, along with the external resistor network, provides the system designer the flexibility to place differential outputs on an I/O bank with 3.3 V  $V_{CCIO}$ . The default drive current for LVCMOS33D output is 12 mA with the option to change the device strength to 4 mA, 8 mA, 12 mA or 16 mA. Follow the LVCMOS33 specifications for the DC characteristics of the LVCMOS33D.

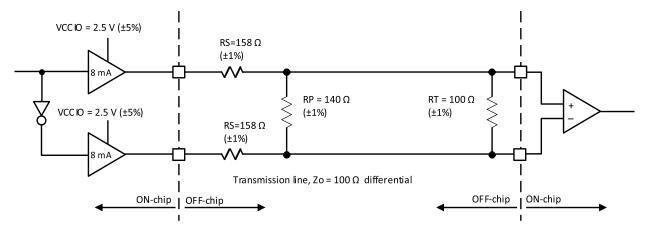

### 3.14.4. LVDS25E

The top and bottom sides of ECP5/ECP5-5G devices support LVDS outputs via emulated complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The scheme shown in Figure 3.1 is one possible solution for point-to-point signals.

Figure 3.1. LVDS25E Output Termination Example

#### Table 3.14. LVDS25E DC Conditions

| Parameter         | Description                    | Typical | Unit |

|-------------------|--------------------------------|---------|------|

| V <sub>CCIO</sub> | Output Driver Supply (±5%)     | 2.50    | V    |

| Z <sub>OUT</sub>  | Driver Impedance               | 20      | Ω    |

| Rs                | Driver Series Resistor (±1%)   | 158     | Ω    |

| R <sub>P</sub>    | Driver Parallel Resistor (±1%) | 140     | Ω    |

| R <sub>T</sub>    | Receiver Termination (±1%)     | 100     | Ω    |

| V <sub>OH</sub>   | Output High Voltage            | 1.43    | V    |

| V <sub>OL</sub>   | Output Low Voltage             | 1.07    | V    |

| V <sub>OD</sub>   | Output Differential Voltage    | 0.35    | V    |

| V <sub>CM</sub>   | Output Common Mode Voltage     | 1.25    | V    |

| ZBACK             | Back Impedance                 | 100.5   | Ω    |

| I <sub>DC</sub>   | DC Output Current              | 6.03    | mA   |

Note: For input buffer, see LVDS Table 3.13 on page 55.

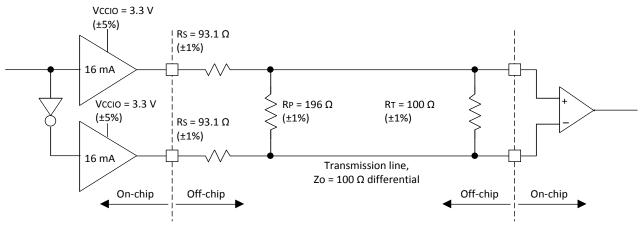

## 3.14.6. LVPECL33

The ECP5/ECP5-5G devices support the differential LVPECL standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The LVPECL input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3.3 is one possible solution for point-to-point signals.

Over recommended operating conditions.

| Parameter         | Description                    | Typical | Unit |

|-------------------|--------------------------------|---------|------|

| V <sub>CCIO</sub> | Output Driver Supply (±5%)     | 3.30    | V    |

| Z <sub>OUT</sub>  | Driver Impedance               | 10      | Ω    |

| Rs                | Driver Series Resistor (±1%)   | 93      | Ω    |

| R <sub>P</sub>    | Driver Parallel Resistor (±1%) | 196     | Ω    |

| R <sub>T</sub>    | Receiver Termination (±1%)     | 100     | Ω    |

| V <sub>OH</sub>   | Output High Voltage            | 2.05    | V    |

| V <sub>OL</sub>   | Output Low Voltage             | 1.25    | V    |

| V <sub>OD</sub>   | Output Differential Voltage    | 0.80    | V    |

| V <sub>CM</sub>   | Output Common Mode Voltage     | 1.65    | V    |

| ZBACK             | Back Impedance                 | 100.5   | Ω    |

| I <sub>DC</sub>   | DC Output Current              | 12.11   | mA   |

#### Table 3.16. LVPECL33 DC Conditions

Note: For input buffer, see LVDS Table 3.13 on page 55.

### 3.14.8. SLVS

Scalable Low-Voltage Signaling (SLVS) is based on a point-to-point signaling method defined in the JEDEC JESD8-13 (SLVS-400) standard. This standard evolved from the traditional LVDS standard and relies on the advantage of its use of smaller voltage swings and a lower common-mode voltage. The 200 mV (400 mV p-p) SLVS swing contributes to a reduction in power.

The ECP5/ECP5-5G devices can receive differential input up to 800 Mb/s with its LVDS input buffer. This LVDS input buffer is used to meet the SLVS input standard specified by the JEDEC standard. The SLVS output parameters are compared to ECP5/ECP5-5G LVDS input parameters, as listed in Table 3.18.

#### Table 3.18. Input to SLVS

| Parameter                  | ECP5/ECP5-5G LVDS Input | SLVS Output | Unit |

|----------------------------|-------------------------|-------------|------|

| Vcm (min)                  | 50                      | 150         | mV   |

| Vcm (max)                  | 2350                    | 250         | mV   |

| Differential Voltage (min) | 100                     | 140         | mV   |

| Differential Voltage (max) | -                       | 270         | mV   |

ECP5/ECP5-5G does not support SLVS output. However, SLVS output can be created using ECP5/ECP5-5G LVDS outputs by level shift to meet the low Vcm/Vod levels required by SLVS. Figure 3.5 shows how the LVDS output can be shifted external to meet SLVS levels.

Figure 3.5. SLVS Interface

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## 3.25. PCI Express Electrical and Timing Characteristics

### 3.25.1. PCIe (2.5 Gb/s) AC and DC Characteristics

Over recommended operating conditions.

#### Table 3.30. PCIe (2.5 Gb/s)

| Symbol                                       | Description                                                          | Test Conditions                                        | Min               | Тур  | Max                | Unit |  |  |

|----------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------|-------------------|------|--------------------|------|--|--|

| Transmit <sup>1</sup>                        |                                                                      |                                                        |                   |      |                    |      |  |  |

| UI                                           | Unit interval                                                        | -                                                      | 399.88            | 400  | 400.12             | ps   |  |  |

| V <sub>TX-DIFF_P-P</sub>                     | Differential peak-to-peak output                                     | -                                                      | 0.8               | 1.0  | 1.2                | V    |  |  |

| V <sub>TX-DE-RATIO</sub>                     | De-emphasis differential output voltage ratio                        | _                                                      | -3                | -3.5 | -4                 | dB   |  |  |

| V <sub>TX-CM-AC_P</sub>                      | RMS AC peak common-mode output voltage                               | -                                                      | -                 | _    | 20                 | mV   |  |  |

| V <sub>TX-RCV-DETECT</sub>                   | Amount of voltage change allowed during receiver detection           | _                                                      | _                 | _    | 600                | mV   |  |  |

| V <sub>TX-CM-DC</sub>                        | Tx DC common mode voltage                                            | _                                                      | 0                 | _    | V <sub>CCHTX</sub> | V    |  |  |

| I <sub>TX-SHORT</sub>                        | Output short circuit current                                         | V <sub>TX-D+</sub> =0.0 V<br>V <sub>TX-D-</sub> =0.0 V | _                 | _    | 90                 | mA   |  |  |