Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                                 |

|--------------------------------|---------------------------------------------------------------------------------|

| Product Status                 | Active                                                                          |

| Number of LABs/CLBs            | 21000                                                                           |

| Number of Logic Elements/Cells | 84000                                                                           |

| Total RAM Bits                 | 3833856                                                                         |

| Number of I/O                  | 118                                                                             |

| Number of Gates                | -                                                                               |

| Voltage - Supply               | 1.045V ~ 1.155V                                                                 |

| Mounting Type                  | Surface Mount                                                                   |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                                 |

| Package / Case                 | 285-LFBGA, CSPBGA                                                               |

| Supplier Device Package        | 285-CSFBGA (10x10)                                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe5um5g-85f-8mg285c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Contents**

| 40 | cronyms in Th | nis Document                                        | 9  |

|----|---------------|-----------------------------------------------------|----|

| L. | General D     | Description                                         | 10 |

|    |               | tures                                               |    |

| 2. | Architect     | ıre                                                 | 12 |

|    | 2.1. Ove      | rview                                               | 12 |

|    | 2.2. PFU      | Blocks                                              | 13 |

|    | 2.2.1. S      | lice                                                | 14 |

|    |               | Nodes of Operation                                  |    |

|    |               | ting                                                |    |

|    |               | cking Structure                                     |    |

|    |               | ysCLOCK PLL                                         |    |

|    |               | ck Distribution Network                             |    |

|    | 2.5.1. P      | rimary Clocks                                       | 20 |

|    | 2.5.2. E      | dge Clock                                           | 21 |

|    | 2.6. Cloc     | ck Dividers                                         | 22 |

|    | 2.7. DDF      | RDLL                                                | 23 |

|    | 2.8. sysN     | MEM Memory                                          | 24 |

|    | 2.8.1. s      | ysMEM Memory Block                                  | 24 |

|    | 2.8.2. B      | bus Size Matching                                   | 25 |

|    | 2.8.3. R      | AM Initialization and ROM Operation                 | 25 |

|    | 2.8.4. N      | Nemory Cascading                                    | 25 |

|    | 2.8.5. S      | ingle, Dual and Pseudo-Dual Port Modes              | 25 |

|    | 2.8.6. N      | Nemory Core Reset                                   | 26 |

|    | 2.9. sys[     | DSP™ Slice                                          | 26 |

|    | 2.9.1. s      | ysDSP Slice Approach Compared to General DSP        | 26 |

|    | 2.9.2. s      | ysDSP Slice Architecture Features                   | 27 |

|    | 2.10. Prog    | grammable I/O Cells                                 | 30 |

|    | 2.11. PIO     |                                                     | 32 |

|    | 2.11.1.       | Input Register Block                                | 32 |

|    | 2.11.2.       | Output Register Block                               | 33 |

|    | 2.12. Tris    | tate Register Block                                 | 34 |

|    | 2.13. DDF     | R Memory Support                                    | 35 |

|    | 2.13.1.       | DQS Grouping for DDR Memory                         |    |

|    | 2.13.2.       | DLL Calibrated DQS Delay and Control Block (DQSBUF) |    |

|    | 2.14. sysl    | /O Buffer                                           |    |

|    | 2.14.1.       | sysI/O Buffer Banks                                 |    |

|    | 2.14.2.       | Typical sysI/O I/O Behavior during Power-up         |    |

|    | 2.14.3.       | Supported sysI/O Standards                          |    |

|    | 2.14.4.       | On-Chip Programmable Termination                    |    |

|    | 2.14.5.       | Hot Socketing                                       |    |

|    |               | DES and Physical Coding Sublayer                    |    |

|    | 2.15.1.       | SERDES Block                                        |    |

|    | 2.15.2.       | PCS                                                 |    |

|    | 2.15.3.       | SERDES Client Interface Bus                         |    |

|    |               | ible Dual SERDES Architecture                       |    |

|    |               | E 1149.1-Compliant Boundary Scan Testability        |    |

|    |               | ice Configuration                                   |    |

|    | 2.18.1.       | Enhanced Configuration Options                      |    |

|    | 2.18.2.       | Single Event Upset (SEU) Support                    |    |

|    | 2.18.3.       | On-Chip Oscillator                                  |    |

|    |               | sity Shifting                                       |    |

| 3. | DC and Sv     | vitching Characteristics                            | 47 |

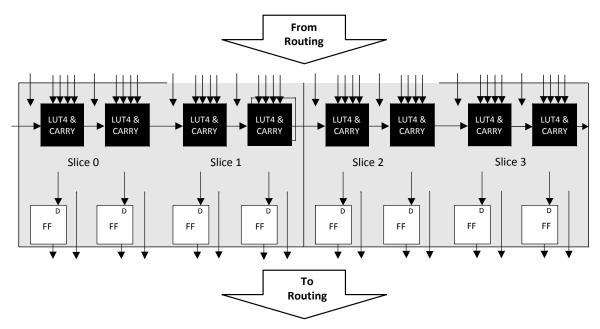

Figure 2.2. PFU Diagram

#### 2.2.1. Slice

Each slice contains two LUT4s feeding two registers. In Distributed SRAM mode, Slice 0 through Slice 2 are configured as distributed memory, and Slice 3 is used as Logic or ROM. Table 2.1 shows the capability of the slices along with the operation modes they enable. In addition, each PFU contains logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7 and LUT8. There is control logic to perform set/reset functions (programmable as synchronous/ asynchronous), clock select, chip-select and wider RAM/ROM functions.

Table 2.1. Resources and Modes Available per Slice

| Slice   | PFU (Used in Distributed SRAM)             |       | PFU (Not used as Distributed SRAM) |                    |

|---------|--------------------------------------------|-------|------------------------------------|--------------------|

| Siice   | Resources                                  | Modes | Resources                          | Modes              |

| Slice 0 | 2 LUT4s and 2 Registers                    | RAM   | 2 LUT4s and 2 Registers            | Logic, Ripple, ROM |

| Slice 1 | 2 LUT4s and 2 Registers                    | RAM   | 2 LUT4s and 2 Registers            | Logic, Ripple, ROM |

| Slice 2 | 2 LUT4s and 2 Registers                    | RAM   | 2 LUT4s and 2 Registers            | Logic, Ripple, ROM |

| Slice 3 | 2 LUT4s and 2 Registers Logic, Ripple, ROM |       | 2 LUT4s and 2 Registers            | Logic, Ripple, ROM |

Figure 2.3 shows an overview of the internal logic of the slice. The registers in the slice can be configured for positive/negative and edge triggered or level sensitive clocks.

Each slice has 14 input signals, 13 signals from routing and one from the carry-chain (from the adjacent slice or PFU). There are five outputs, four to routing and one to carry-chain (to the adjacent PFU). There are two inter slice/PFU output signals that are used to support wider LUT functions, such as LUT6, LUT7 and LUT8. Table 2.2 and Figure 2.3 list the signals associated with all the slices. Figure 2.4 on page 16 shows the connectivity of the inter-slice/PFU signals that support LUT5, LUT6, LUT7 and LUT8.

### 2.2.2. Modes of Operation

Slices 0-2 have up to four potential modes of operation: Logic, Ripple, RAM and ROM. Slice 3 is not needed for RAM mode, it can be used in Logic, Ripple, or ROM modes.

#### **Logic Mode**

In this mode, the LUTs in each slice are configured as 4-input combinatorial lookup tables. A LUT4 can have 16 possible input combinations. Any four input logic functions can be generated by programming this lookup table. Since there are two LUT4s per slice, a LUT5 can be constructed within one slice. Larger look-up tables such as LUT6, LUT7 and LUT8 can be constructed by concatenating other slices. Note that LUT8 requires more than four slices.

#### **Ripple Mode**

Ripple mode supports the efficient implementation of small arithmetic functions. In ripple mode, the following functions can be implemented by each slice:

- Addition 2-bit

- Subtraction 2-bit

- Add/Subtract 2-bit using dynamic control

- Up counter 2-bit

- Down counter 2-bit

- Up/Down counter with asynchronous clear

- Up/Down counter with preload (sync)

- Ripple mode multiplier building block

- Multiplier support

- Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Ripple Mode includes an optional configuration that performs arithmetic using fast carry chain methods. In this configuration (also referred to as CCU2 mode) two additional signals, Carry Generate and Carry Propagate, are generated on a per slice basis to allow fast arithmetic functions to be constructed by concatenating Slices.

#### **RAM Mode**

In this mode, a 16x4-bit distributed single port RAM (SPR) can be constructed in one PFU using each LUT block in Slice 0 and Slice 1 as a 16 x 2-bit memory in each slice. Slice 2 is used to provide memory address and control signals. A 16 x 2-bit pseudo dual port RAM (PDPR) memory is created in one PFU by using one Slice as the read-write port and the other companion slice as the read-only port. The slice with the read-write port updates the SRAM data contents in both slices at the same write cycle.

ECP5/ECP5-5G devices support distributed memory initialization.

The Lattice design tools support the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2.3 lists the number of slices required to implement different distributed RAM primitives. For more information about using RAM in ECP5/ECP5-5G devices, refer to ECP5 and ECP5-5G Memory Usage Guide (TN1264).

Table 2.3. Number of Slices Required to Implement Distributed RAM

|                                                          | SPR 16 X 4 | PDPR 16 X 4 |  |  |  |  |  |

|----------------------------------------------------------|------------|-------------|--|--|--|--|--|

| Number of slices                                         | 3          | 6           |  |  |  |  |  |

| Note: SPR = Single Port RAM, PDPR = Pseudo Dual Port RAM |            |             |  |  |  |  |  |

# ROM Mode

ROM mode uses the LUT logic; hence, Slices 0 through 3 can be used in ROM mode. Preloading is accomplished through the programming interface during PFU configuration.

For more information, refer to ECP5 and ECP5-5G Memory Usage Guide (TN1264).

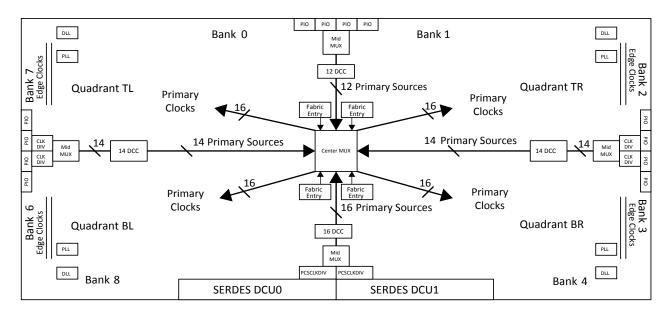

Figure 2.6. LFE5UM/LFE5UM5G-85 Clocking

### 2.5.1. Primary Clocks

The ECP5/ECP5-5G device family provides low-skew, high fan-out clock distribution to all synchronous elements in the FPGA fabric through the Primary Clock Network.

The primary clock network is divided into four clocking quadrants: Top Left (TL), Bottom Left (BL), Top Right (TR), and Bottom Right (BR). Each of these quadrants has 16 clocks that can be distributed to the fabric in the quadrant.

The Lattice Diamond software can automatically route each clock to one of the four quadrants up to a maximum of 16 clocks per quadrant. The user can change how the clocks are routed by specifying a preference in the Lattice Diamond software to locate the clock to specific. The ECP5/ECP5-5G device provides the user with a maximum of 64 unique clock input sources that can be routed to the primary Clock network.

Primary clock sources are:

- Dedicated clock input pins

- PLL outputs

- CLKDIV outputs

- Internal FPGA fabric entries (with minimum general routing)

- SERDES/PCS/PCSDIV clocks

- OSC clock

These sources are routed to one of four clock switches called a Mid Mux. The outputs of the Mid MUX are routed to the center of the FPGA where another clock switch, called the Center MUX, is used to route the primary clock sources to primary clock distribution to the ECP5/ECP5-5G fabric. These routing muxes are shown in Figure 2.6. Since there is a maximum of 60 unique clock input sources to the clocking quadrants, there are potentially 64 unique clock domains that can be used in the ECP5/ECP5-5G Device. For more information about the primary clock tree and connections, refer to ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263).

#### 2.5.1.1. Dynamic Clock Control

The Dynamic Clock Control (DCC), Quadrant Clock enable/disable feature allows internal logic control of the quadrant primary clock network. When a clock network is disabled, the clock signal is static and not toggle. All the logic fed by that clock will not toggle, reducing the overall power consumption of the device. The disable function will not create glitch and increase the clock latency to the primary clock network.

This DCC controls the clock sources from the Primary CLOCK MIDMUX before they are fed to the Primary Center MUXs that drive the quadrant clock network. For more information about the DCC, refer to ECP5 and ECP5-5G sysClock PLL/DLL Design and Usage Guide (TN1263).

- 5\*5 and larger size 2D blocks Semi internal DSP Slice support

- Flexible saturation and rounding options to satisfy a diverse set of applications situations

- Flexible cascading across DSP slices

- Minimizes fabric use for common DSP and ALU functions

- Enables implementation of FIR Filter or similar structures using dedicated sysDSP slice resources only

- Provides matching pipeline registers

- Can be configured to continue cascading from one row of sysDSP slices to another for longer cascade chains

- Flexible and Powerful Arithmetic Logic Unit (ALU) Supports:

- Dynamically selectable ALU OPCODE

- Ternary arithmetic (addition/subtraction of three inputs)

- Bit-wise two-input logic operations (AND, OR, NAND, NOR, XOR and XNOR)

- Eight flexible and programmable ALU flags that can be used for multiple pattern detection scenarios, such as, overflow, underflow and convergent rounding.

- Flexible cascading across slices to get larger functions

- RTL Synthesis friendly synchronous reset on all registers, while still supporting asynchronous reset for legacy users

- Dynamic MUX selection to allow Time Division Multiplexing (TDM) of resources for applications that require processor-like flexibility that enables different functions for each clock cycle

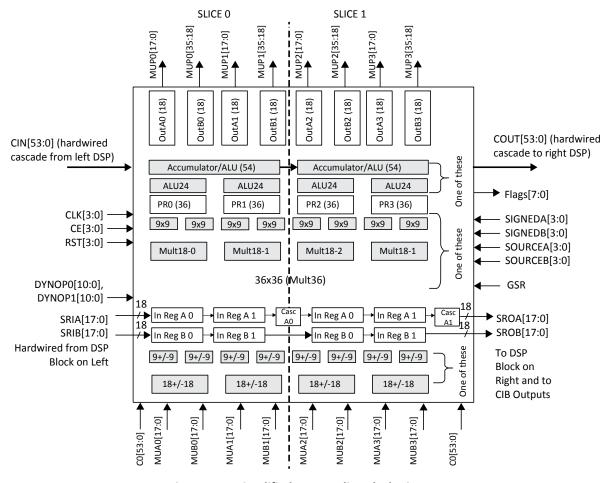

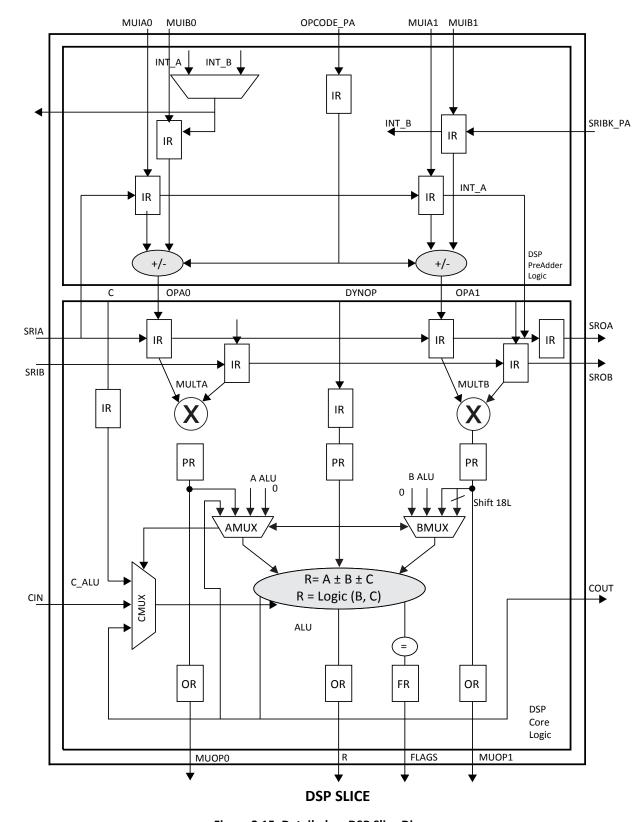

For most cases, as shown in Figure 2.14, the ECP5/ECP5-5G sysDSP slice is backwards-compatible with the LatticeECP2™ and LatticeECP3™ sysDSP block, such that, legacy applications can be targeted to the ECP5/ ECP5-5G sysDSP slice. Figure 2.14 shows the diagram of sysDSP, and Figure 2.15 shows the detailed diagram.

Figure 2.14. Simplified sysDSP Slice Block Diagram

Figure 2.15. Detailed sysDSP Slice Diagram

### 2.11. PIO

The PIO contains three blocks: an input register block, output register block, and tristate register block. These blocks contain registers for operating in a variety of modes along with the necessary clock and selection logic.

### 2.11.1. Input Register Block

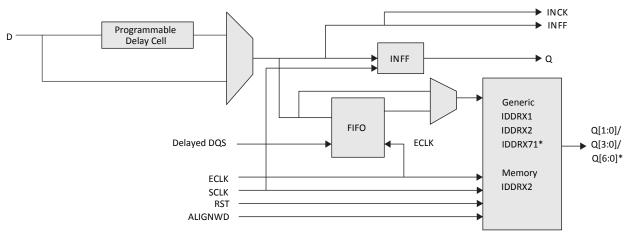

The input register blocks for the PIOs on all edges contain delay elements and registers that can be used to condition high-speed interface signals before they are passed to the device core. In addition, the input register blocks for the PIOs on the left and right edges include built-in FIFO logic to interface to DDR and LPDDR memory.

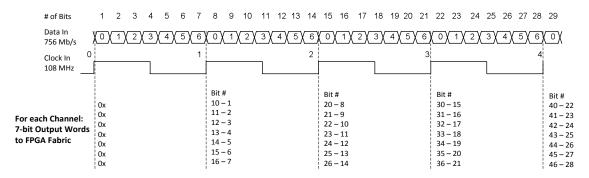

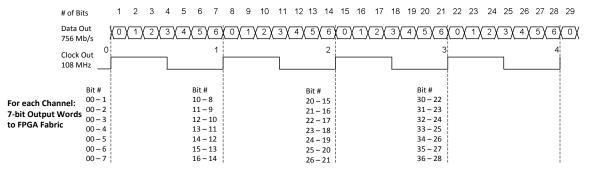

The Input register block on the right and left sides includes gearing logic and registers to implement IDDRX1 and IDDRX2 functions. With two PICs sharing the DDR register path, it can also implement IDDRX71 function used for 7:1 LVDS interfaces. It uses three sets of registers to shift, update, and transfer to implement gearing and the clock domain transfer. The first stage registers samples the high-speed input data by the high-speed edge clock on its rising and falling edges. The second stage registers perform data alignment based on the control signals. The third stage pipeline registers pass the data to the device core synchronized to the low-speed system clock. The top side of the device supports IDDRX1 gearing function. For more information on gearing function, refer to ECP5 and ECP5-5G High-Speed I/O Interface (TN1265).

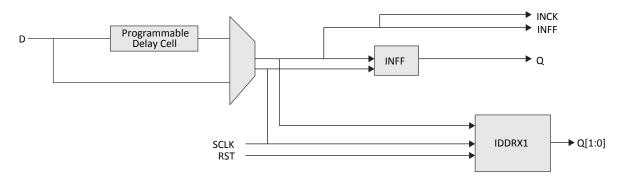

Figure 2.17 shows the input register block for the PIOs on the top edge.

Figure 2.17. Input Register Block for PIO on Top Side of the Device

Figure 2.18 shows the input register block for the PIOs located on the left and right edges.

<sup>\*</sup>For 7:1 LVDS interface only. It is required to use PIO pair pins (PIOA/B or PIOC/D).

Figure 2.18. Input Register Block for PIO on Left and Right Side of the Device

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

32

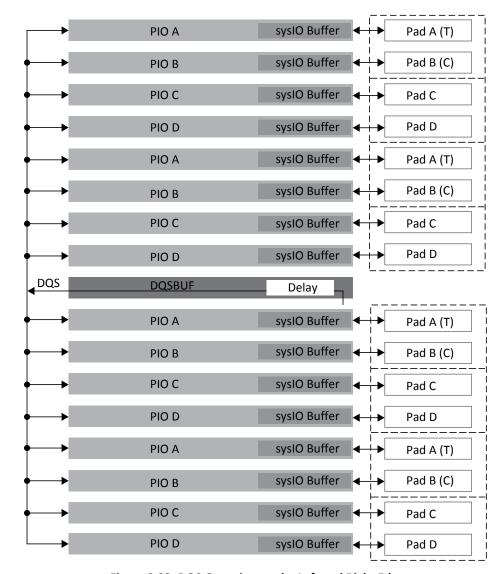

Figure 2.23. DQS Grouping on the Left and Right Edges

### 2.13.2. DLL Calibrated DQS Delay and Control Block (DQSBUF)

To support DDR memory interfaces (DDR2/3, LPDDR2/3), the DQS strobe signal from the memory must be used to capture the data (DQ) in the PIC registers during memory reads. This signal is output from the DDR memory device aligned to data transitions and must be time shifted before it can be used to capture data in the PIC. This time shifted is achieved by using DQSDEL programmable delay line in the DQS Delay Block (DQS read circuit). The DQSDEL is implemented as a slave delay line and works in conjunction with a master DDRDLL.

This block also includes slave delay line to generate delayed clocks used in the write side to generate DQ and DQS with correct phases within one DQS group. There is a third delay line inside this block used to provide write leveling feature for DDR write if needed.

Each of the read and write side delays can be dynamically shifted using margin control signals that can be controlled by the core logic.

FIFO Control Block shown in Figure 2.24 generates the Read and Write Pointers for the FIFO block inside the Input Register Block. These pointers are generated to control the DQS to ECLK domain crossing using the FIFO module.

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### 2.14. sysI/O Buffer

Each I/O is associated with a flexible buffer referred to as a sysI/O buffer. These buffers are arranged around the periphery of the device in groups referred to as banks. The sysI/O buffers allow users to implement the wide variety of standards that are found in today's systems including LVDS, HSUL, BLVDS, SSTL Class I and II, LVCMOS, LVTTL, LVPECL, and MIPI.

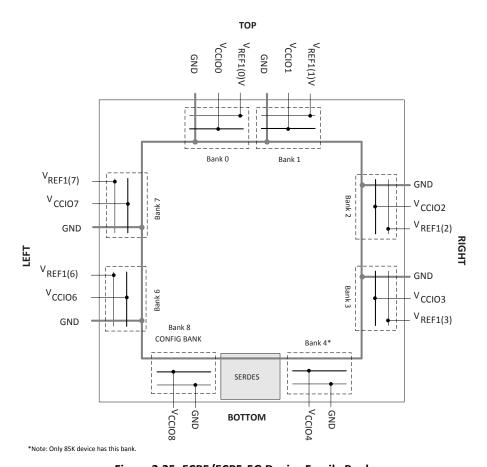

### 2.14.1. sysI/O Buffer Banks

ECP5/ECP5-5G devices have seven sysI/O buffer banks, two banks per side at Top, Left and Right, plus one at the bottom left side. The bottom left side bank (Bank 8) is a shared I/O bank. The I/Os in that bank contains both dedicated and shared I/O for sysConfig function. When a shared pin is not used for configuration, it is available as a user I/O. For LFE5-85 devices, there is an additional I/O bank (Bank 4) that is not available in other device in the family.

In ECP5/ECP5-5G devices, the Left and Right sides are tailored to support high performance interfaces, such as DDR2, DDR3, LPDDR2, LPDDR3 and other high speed source synchronous standards. The banks on the Left and Right sides of the devices feature LVDS input and output buffers, data-width gearing, and DQSBUF block to support DDR2/3 and LPDDR2/3 interfaces. The I/Os on the top and bottom banks do not have LVDS input and output buffer, and gearing logic, but can use LVCMOS to emulate most of differential output signaling.

Each sysIO bank has its own I/O supply voltage ( $V_{CCIO}$ ). In addition, the banks on the Left and Right sides of the device, have voltage reference input (shared I/O pin), VREF1 per bank, which allow it to be completely independent of each other. The  $V_{REF}$  voltage is used to set the threshold for the referenced input buffers, such as SSTL. Figure 2.25 shows the seven banks and their associated supplies.

In ECP5/ECP5-5G devices, single-ended output buffers and ratioed input buffers (LVTTL, and LVCMOS) are powered using  $V_{\text{CCIO}}$ . LVTTL, LVCMOS33, LVCMOS25 and LVCMOS12 can also be set as fixed threshold inputs independent of  $V_{\text{CCIO}}$ .

Figure 2.25. ECP5/ECP5-5G Device Family Banks

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

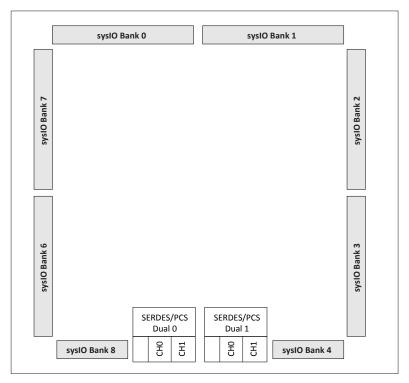

Figure 2.27. SERDES/PCS Duals (LFE5UM/LFE5UM5G-85)

Table 2.13. LFE5UM/LFE5UM5G SERDES Standard Support

| Standard                                       | Data Rate (Mb/s)                                           | Number of General/Link Width | Encoding Style |

|------------------------------------------------|------------------------------------------------------------|------------------------------|----------------|

| PCI Express 1.1 and 2.0                        | 2500                                                       | x1, x2, x4                   | 8b10b          |

| 2.02                                           | 5000 <sup>2</sup>                                          | x1, x2                       | 8b10b          |

| Gigabit Ethernet                               | 1250                                                       | x1                           | 8b10b          |

| CCAAII                                         | 1250                                                       | x1                           | 8b10b          |

| SGMII                                          | 2500                                                       | x1                           | 8b10b          |

| XAUI                                           | 3125                                                       | x4                           | 8b10b          |

| CPRI-1<br>CPRI-2<br>CPRI-3<br>CPRI-4<br>CPRI-5 | 614.4<br>1228.8<br>2457.6<br>3072.0<br>4915.2 <sup>2</sup> | x1                           | 8b10b          |

| SD-SDI (259M, 344M) <sup>1</sup>               | 270                                                        | x1                           | NRZI/Scrambled |

| HD-SDI (292M)                                  | 1483.5<br>1485                                             | x1                           | NRZI/Scrambled |

| 3G-SDI (424M)                                  | 2967<br>2970                                               | x1                           | NRZI/Scrambled |

|                                                | 5000                                                       | _                            | _              |

| JESD204A/B                                     | 3125                                                       | x1                           | 8b/10b         |

### Notes:

- 1. For SD-SDI rate, the SERDES is bypassed and SERDES input signals are directly connected to the FPGA routing.

- 2. For ECP5-5G family devices only.

#### 2.15.3. SERDES Client Interface Bus

The SERDES Client Interface (SCI) is an IP interface that allows the user to change the configuration thru this interface. This is useful when the user needs to fine-tune some settings, such as input and output buffer that need to be optimized based on the channel characteristics. It is a simple register configuration interface that allows SERDES/PCS configuration without power cycling the device.

The Diamond design tools support all modes of the PCS. Most modes are dedicated to applications associated with a specific industry standard data protocol. Other more general purpose modes allow users to define their own operation. With these tools, the user can define the mode for each dual in a design.

Popular standards such as 10 Gb Ethernet, x4 PCI Express and 4x Serial RapidIO can be implemented using IP (available through Lattice), with two duals (Four SERDES channels and PCS) and some additional logic from the core.

The LFE5UM/LFE5UM5G devices support a wide range of protocols. Within the same dual, the LFE5UM/ LFE5UM5G devices support mixed protocols with semi-independent clocking as long as the required clock frequencies are integer x1, x2, or x11 multiples of each other. Table 2.15 lists the allowable combination of primary and secondary protocol combinations.

### 2.16. Flexible Dual SERDES Architecture

The LFE5UM/LFE5UM5G SERDES architecture is a dual channel-based architecture. For most SERDES settings and standards, the whole dual (consisting of two SERDES channels) is treated as a unit. This helps in silicon area savings, better utilization, higher granularity on clock/SERDES channel and overall lower cost.

However, for some specific standards, the LFE5UM/LFE5UM5G dual-channel architecture provides flexibility; more than one standard can be supported within the same dual.

Table 2.15 lists the standards that can be mixed and matched within the same dual. In general, the SERDES standards whose nominal data rates are either the same or a defined subset of each other, can be supported within the same dual. The two Protocol columns of the table define the different combinations of protocols that can be implemented together within a Dual.

| Protocol        |      | Protocol          |

|-----------------|------|-------------------|

| PCI Express 1.1 | with | SGMII             |

| PCI Express 1.1 | with | Gigabit Ethernet  |

| CPRI-3          | with | CPRI-2 and CPRI-1 |

| 3G-SDI          | with | HD-SDI and SD-SDI |

There are some restrictions to be aware of when using spread spectrum clocking. When a dual shares a PCI Express x1 channel with a non-PCI Express channel, ensure that the reference clock for the dual is compatible with all protocols within the dual. For example, a PCI Express spread spectrum reference clock is not compatible with most Gigabit Ethernet applications because of tight CTC ppm requirements.

While the LFE5UM/LFE5UM5G architecture will allow the mixing of a PCI Express channel and a Gigabit Ethernet, or SGMII channel within the same dual, using a PCI Express spread spectrum clocking as the transmit reference clock will cause a violation of the Gigabit Ethernet, and SGMII transmit jitter specifications.

For further information on SERDES, refer to ECP5 and ECP5-5G SERDES/PCS Usage Guide (TN1261).

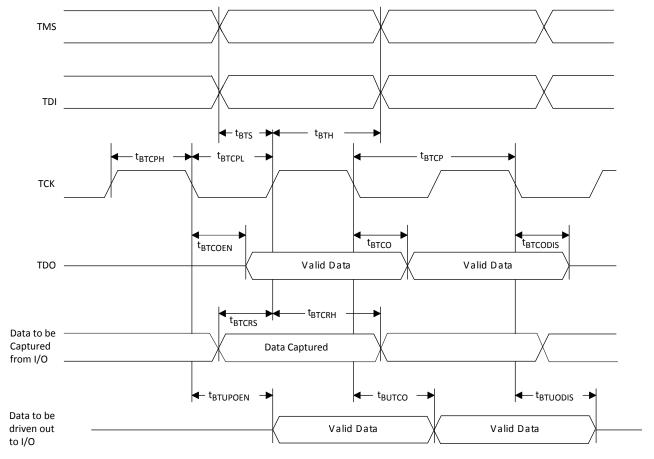

# 2.17. IEEE 1149.1-Compliant Boundary Scan Testability

All ECP5/ECP5-5G devices have boundary scan cells that are accessed through an IEEE 1149.1 compliant Test Access Port (TAP). This allows functional testing of the circuit board on which the device is mounted through a serial scan path that can access all critical logic nodes. Internal registers are linked internally, allowing test data to be shifted in and loaded directly onto test nodes, or test data to be captured and shifted out for verification. The test access port consists of dedicated I/Os: TDI, TDO, TCK and TMS. The test access port uses VCCIO8 for power supply.

For more information, refer to ECP5 and ECP5-5G sysCONFIG Usage Guide (TN1260).

44

### 3.7. Hot Socketing Requirements

#### **Table 3.6. Hot Socketing Requirements**

| Description                                                                               | Min | Тур | Max | Unit |

|-------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Input current per SERDES I/O pin when device is powered down and inputs driven.           | -   | ı   | 8   | mA   |

| Input current per HDIN pin when device power supply is off, inputs driven <sup>1, 2</sup> | _   | -   | 15  | mA   |

| Current per HDIN pin when device power ramps up, input driven <sup>3</sup>                |     | -   | 50  | mA   |

| Current per HDOUT pin when device power supply is off, outputs pulled up <sup>4</sup>     | _   | _   | 30  | mA   |

#### Notes:

- Device is powered down with all supplies grounded, both HDINP and HDINN inputs driven by a CML driver with maximum allowed output V<sub>CCHTX</sub>, 8b/10b data, no external AC coupling.

- 2. Each P and N input must have less than the specified maximum input current during hot plug. For a device with 2 DCU, the total input current would be 15 mA \* 4 channels \* 2 input pins per channel = 120 mA.

- Device power supplies are ramping up (V<sub>CCA</sub> and V<sub>CCAUX</sub>), both HDINP and HDINN inputs are driven by a CML driver with maximum allowed output V<sub>CCHTX</sub>, 8b/10b data, internal AC coupling.

- 4. Device is powered down with all supplies grounded. Both HDOUTP and HDOUN outputs are pulled up to  $V_{CCHTX}$  by the far end receiver termination of 50  $\Omega$  single ended.

### 3.8. ESD Performance

Refer to the ECP5 and ECP5-5G Product Family Qualification Summary for complete qualification data, including ESD performance.

### 3.9. DC Electrical Characteristics

**Over Recommended Operating Conditions**

**Table 3.7. DC Electrical Characteristics**

| Symbol                                            | Parameter                                                        | Condition                                                                                                                                               | Min | Тур | Max  | Unit |

|---------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| I <sub>IL</sub> , I <sub>IH</sub> <sup>1, 4</sup> | Input or I/O Low Leakage                                         | $0 \le V_{IN} \le V_{CCIO}$                                                                                                                             | _   | _   | 10   | μΑ   |

| I <sub>IH</sub> 1,3                               | Input or I/O High Leakage                                        | $V_{CCIO} < V_{IN} \le V_{IH(MAX)}$                                                                                                                     | _   | _   | 100  | μΑ   |

| 1                                                 | I/O Active Pull-up Current,<br>sustaining logic HIGH state       | $0.7 V_{CCIO} \le V_{IN} \le V_{CCIO}$                                                                                                                  | -30 | _   | ı    | μΑ   |

| I <sub>PU</sub>                                   | I/O Active Pull-up Current, pulling down from logic HIGH state   | $0 \le V_{IN} \le 0.7 \ V_{CCIO}$                                                                                                                       | _   | _   | -150 | μΑ   |

| I <sub>PD</sub>                                   | I/O Active Pull-down Current,<br>sustaining logic LOW state      | $0 \le V_{IN} \le V_{IL} (MAX)$                                                                                                                         | 30  | _   | -    | μΑ   |

| IPD                                               | I/O Active Pull-down Current,<br>pulling up from logic LOW state | $0 \le V_{IN} \le V_{CCIO}$                                                                                                                             | _   | _   | 150  | μΑ   |

| C1                                                | I/O Capacitance <sup>2</sup>                                     | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V}, \\ V_{CC} = 1.2 \text{ V}, V_{IO} = 0 \text{ to } V_{IH(MAX)}$   | _   | 5   | 8    | pf   |

| C2                                                | Dedicated Input Capacitance <sup>2</sup>                         | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V},$<br>$V_{CC} = 1.2 \text{ V}, V_{IO} = 0 \text{ to } V_{IH(MAX)}$ | _   | 5   | 7    | pf   |

| W                                                 | Hysteresis for Single-Ended                                      | V <sub>CCIO</sub> = 3.3 V                                                                                                                               | _   | 300 |      | mV   |

| V <sub>HYST</sub>                                 | Inputs                                                           | V <sub>CCIO</sub> = 2.5 V                                                                                                                               | _   | 250 | _    | mV   |

#### Notes:

- 1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tristated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

- 2. T<sub>Δ</sub> 25 °C, f = 1.0 MHz.

- 3. Applicable to general purpose I/Os in top and bottom banks.

- 4. When used as  $V_{REF}$ , maximum leakage= 25  $\mu$ A.

# 3.15. Typical Building Block Function Performance

#### Table 3.19. Pin-to-Pin Performance

| Function        | -8 Timing | Unit |

|-----------------|-----------|------|

| Basic Functions | ,         | ·    |

| 16-Bit Decoder  | 5.06      | ns   |

| 32-Bit Decoder  | 6.08      | ns   |

| 64-Bit Decoder  | 5.06      | ns   |

| 4:1 Mux         | 4.45      | ns   |

| 8:1 Mux         | 4.63      | ns   |

| 16:1 Mux        | 4.81      | ns   |

| 32:1 Mux        | 4.85      | ns   |

#### Notes:

- 1. I/Os are configured with LVCMOS25 with V<sub>CCIO</sub>=2.5, 12 mA drive.

- These functions were generated using Lattice Diamond design software tool. Exact performance may vary with the device and the design software tool version. The design software tool uses internal parameters that have been characterized but are not tested on every device.

- 3. Commercial timing numbers are shown. Industrial numbers are typically slower and can be extracted from Lattice Diamond design software tool.

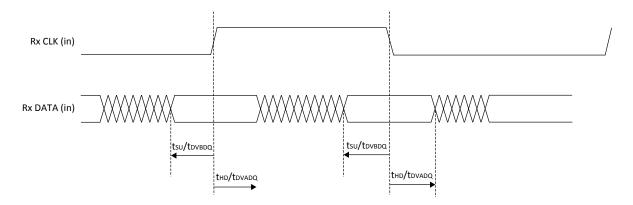

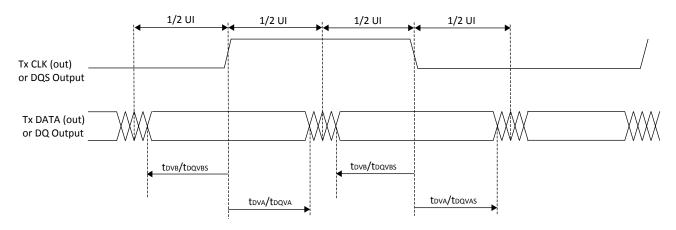

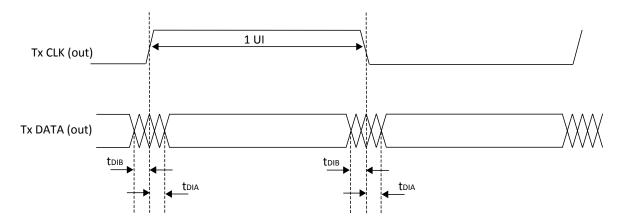

Figure 3.6. Receiver RX.CLK.Centered Waveforms

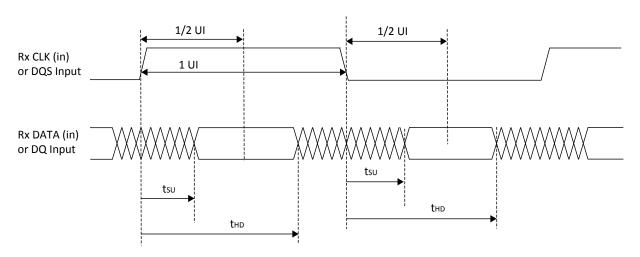

Figure 3.7. Receiver RX.CLK.Aligned and DDR Memory Input Waveforms

Figure 3.8. Transmit TX.CLK.Centered and DDR Memory Output Waveforms

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Figure 3.9. Transmit TX.CLK.Aligned Waveforms

#### Receiver - Shown for one LVDS Channel

#### Transmitter - Shown for one LVDS Channel

Figure 3.10. DDRX71 Video Timing Waveforms

### 3.24. SERDES External Reference Clock

The external reference clock selection and its interface are a critical part of system applications for this product. Table 3.29 specifies reference clock requirements, over the full range of operating conditions.

Table 3.29. External Reference Clock Specification (refclkp/refclkn)

| Symbol                        | Description                                     | Min   | Тур     | Max                       | Unit                    |

|-------------------------------|-------------------------------------------------|-------|---------|---------------------------|-------------------------|

| F <sub>REF</sub>              | Frequency range                                 | 50    | _       | 320                       | MHz                     |

| F <sub>REF-PPM</sub>          | Frequency tolerance <sup>1</sup>                | -1000 | _       | 1000                      | ppm                     |

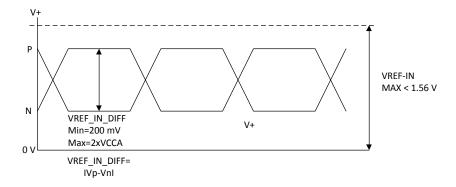

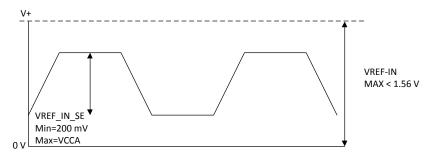

| V <sub>REF-IN-SE</sub>        | Input swing, single-ended clock <sup>2, 4</sup> | 200   | _       | V <sub>CCAUXA</sub>       | mV, p-p                 |

| V <sub>REF-IN-DIFF</sub>      | Input swing, differential clock                 | 200   | _       | 2*V <sub>CCAUXA</sub>     | mV, p-p<br>differential |

| $V_{REF-IN}$                  | Input levels                                    | 0     | _       | V <sub>CCAUXA</sub> + 0.4 | V                       |

| D <sub>REF</sub>              | Duty cycle <sup>3</sup>                         | 40    | _       | 60                        | %                       |

| T <sub>REF-R</sub>            | Rise time (20% to 80%)                          | 200   | 500     | 1000                      | ps                      |

| T <sub>REF-F</sub>            | Fall time (80% to 20%)                          | 200   | 500     | 1000                      | ps                      |

| Z <sub>REF-IN-TERM-DIFF</sub> | Differential input termination                  | -30%  | 100/HiZ | +30%                      | Ω                       |

| C <sub>REF-IN-CAP</sub>       | Input capacitance                               | _     | _       | 7                         | pF                      |

#### Notes:

- Depending on the application, the PLL\_LOL\_SET and CDR\_LOL\_SET control registers may be adjusted for other tolerance values as described in ECP5 and ECP5-5G SERDES/PCS Usage Guide (TN1261).

- 2. The signal swing for a single-ended input clock must be as large as the p-p differential swing of a differential input clock to get the same gain at the input receiver. With single-ended clock, a reference voltage needs to be externally connected to CLKREFN pin, and the input voltage needs to be swung around this reference voltage.

- 3. Measured at 50% amplitude.

- Single-ended clocking is achieved by applying a reference voltage V<sub>REF</sub> on REFCLKN input, with the clock applied to REFCLKP input pin. V<sub>REF</sub> should be set to mid-point of the REFCLKP voltage swing.

Figure 3.14. SERDES External Reference Clock Waveforms

FPGA-DS-02012-1.9 75

© 2014-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

# 3.25.2. PCIe (5 Gb/s) - Preliminary AC and DC Characteristics

Over recommended operating conditions.

Table 3.31. PCIe (5 Gb/s)

| Symbol                            | Description                                                 | Test Conditions              | Min    | Тур | Max    | Unit       |

|-----------------------------------|-------------------------------------------------------------|------------------------------|--------|-----|--------|------------|

| Transmit <sup>1</sup>             |                                                             |                              |        |     |        | •          |

| UI                                | Unit Interval                                               | _                            | 199.94 | 200 | 200.06 | ps         |

| B <sub>WTX-PKG-PLL2</sub>         | Tx PLL bandwidth corresponding to PKGTX-PLL2                | _                            | 5      | _   | 16     | MHz        |

| P <sub>KGTX-PLL2</sub>            | Tx PLL Peaking                                              | _                            | _      | _   | 1      | dB         |

| V <sub>TX-DIFF-PP</sub>           | Differential p-p Tx voltage swing                           | _                            | 0.8    | _   | 1.2    | V, p-p     |

| V <sub>TX-DIFF-PP-LOW</sub>       | Low power differential p-p Tx voltage swing                 | _                            | 0.4    | _   | 1.2    | V, p-p     |

| V <sub>TX-DE-RATIO-3.5dB</sub>    | Tx de-emphasis level ratio at 3.5dB                         | _                            | 3      | _   | 4      | dB         |

| V <sub>TX-DE-RATIO-6dB</sub>      | Tx de-emphasis level ratio at 6dB                           | _                            | 5.5    | _   | 6.5    | dB         |

| T <sub>MIN-PULSE</sub>            | Instantaneous lone pulse width                              | _                            |        | _   | _      | UI         |

| T <sub>TX-RISE-FALL</sub>         | Transmitter rise and fall time                              | _                            |        | _   | _      | UI         |

| T <sub>TX-EYE</sub>               | Transmitter Eye, including all jitter sources               | _                            | 0.75   | _   | _      | UI         |

| T <sub>TX-DJ</sub>                | Tx deterministic jitter > 1.5 MHz                           | _                            | -      | _   | 0.15   | UI         |

| T <sub>TX-RJ</sub>                | Tx RMS jitter < 1.5 MHz                                     | _                            | _      | _   | 3      | ps,<br>RMS |

| T <sub>RF-MISMATCH</sub>          | Tx rise/fall time mismatch                                  | _                            | _      | _   |        | UI         |

| R <sub>LTX-DIFF</sub>             | Tx Differential Return Loss, including                      | 50 MHz < freq <<br>1.25 GHz  | 10     | _   | _      | dB         |

| 'LIX-DIFF                         | package and silicon                                         | 1.25 GHz < freq<br>< 2.5 GHz | 8      | _   | _      | dB         |

| R <sub>LTX-CM</sub>               | Tx Common Mode Return Loss, including package and silicon   | 50 MHz < freq <<br>2.5 GHz   | 6      | _   | _      | dB         |

| Z <sub>TX-DIFF-DC</sub>           | DC differential Impedance                                   | _                            | _      | _   | 120    | Ω          |

| V <sub>TX-CM-AC-PP</sub>          | Tx AC peak common mode voltage, peak-peak                   | _                            | _      | _   |        | mV,<br>p-p |

| I <sub>TX-SHORT</sub>             | Transmitter short-circuit current                           | _                            | _      | _   | 90     | mA         |

| V <sub>TX-DC-CM</sub>             | Transmitter DC common-mode voltage                          | _                            | 0      | _   | 1.2    | ٧          |

| V <sub>TX-IDLE-DIFF-DC</sub>      | Electrical Idle Output DC voltage                           | _                            | 0      | _   | 5      | mV         |

| V <sub>TX-IDLE-DIFF-AC-p</sub>    | Electrical Idle Differential Output peak voltage            | _                            | _      | _   |        | mV         |

| V <sub>TX-RCV-DETECT</sub>        | Voltage change allowed during<br>Receiver Detect            | _                            | _      | _   | 600    | mV         |

| T <sub>TX-IDLE-MIN</sub>          | Min. time in Electrical Idle                                | _                            | 20     | _   | _      | ns         |

| T <sub>TX-IDLE-SET-TO-IDLE</sub>  | Max. time from El Order Set to valid<br>Electrical Idle     | _                            | _      | _   | 8      | ns         |

| T <sub>TX-IDLE-TO-DIFF-DATA</sub> | Max. time from Electrical Idle to valid differential output | _                            | _      | _   | 8      | ns         |

| L <sub>TX-SKEW</sub>              | Lane-to-lane output skew                                    | _                            | _      | _   |        | ps         |

# 3.26. CPRI LV2 E.48 Electrical and Timing Characteristics - Preliminary

Table 3.32. CPRI LV2 E.48 Electrical and Timing Characteristics

| Symbol                      | Description                                                      | Test Conditions                    | Min    | Тур    | Max                             | Unit        |

|-----------------------------|------------------------------------------------------------------|------------------------------------|--------|--------|---------------------------------|-------------|

| Transmit                    | 1                                                                |                                    | ll.    |        |                                 |             |

| UI                          | Unit Interval                                                    | _                                  | 203.43 | 203.45 | 203.47                          | ps          |

| T <sub>DCD</sub>            | Duty Cycle Distortion                                            | _                                  | _      | _      | 0.05                            | UI          |

| J <sub>UBHPJ</sub>          | Uncorrelated Bounded High<br>Probability Jitter                  | _                                  | _      | _      | 0.15                            | UI          |

| J <sub>TOTAL</sub>          | Total Jitter                                                     | _                                  | _      | _      | 0.3                             | UI          |

| Z <sub>RX-DIFF-DC</sub>     | DC differential Impedance                                        | _                                  | 80     | _      | 120                             | Ω           |

| T <sub>SKEW</sub>           | Skew between differential signals                                | _                                  | _      | _      | 9                               | ps          |

| R <sub>LTX-DIFF</sub>       | Tx Differential Return Loss (S22), including package and silicon | 100 MHz < freq<br>< 3.6864 GHz     | _      | _      | -8                              | dB          |

|                             |                                                                  | 3.6864 GHz < freq<br>< 4.9152 GHz  | -      | _      | -8 + 16.6 *log<br>(freq/3.6864) | dB          |

| R <sub>LTX-CM</sub>         | Tx Common Mode Return Loss, including package and silicon        | 100 MHz < freq<br>< 3.6864 GHz 6 — |        | _      | _                               | dB          |

| I <sub>TX-SHORT</sub>       | Transmitter short-circuit current                                | _                                  | _      | _      | 100                             | mA          |

| T <sub>RISE_FALL-DIFF</sub> | Differential Rise and Fall Time                                  | _                                  |        | _      | _                               | ps          |

| L <sub>TX-SKEW</sub>        | Lane-to-lane output skew                                         | _                                  | _      | _      |                                 | ps          |

| Receive                     |                                                                  |                                    |        | •      |                                 |             |

| UI                          | Unit Interval                                                    | _                                  | 203.43 | 203.45 | 203.47                          | ps          |

| V <sub>RX-DIFF-PP</sub>     | Differential Rx peak-peak voltage                                | _                                  | _      | _      | 1.2                             | V, p-p      |

| V <sub>RX-EYE_Y1_Y2</sub>   | Receiver eye opening mask, Y1 and Y2                             | _                                  | 62.5   | _      | 375                             | mV,<br>diff |

| V <sub>RX-EYE_X1</sub>      | Receiver eye opening mask, X1                                    | _                                  | _      | _      | 0.3                             | UI          |

| T <sub>RX-TJ</sub>          | Receiver total jitter tolerance (not including sinusoidal)       | _                                  | _      | _      | 0.6                             | UI          |

| R <sub>LRX-DIFF</sub>       | Receiver differential Return Loss, package plus silicon          | 100 MHz < freq<br>< 3.6864 GHz     | _      | _      | -8                              | dB          |

|                             |                                                                  | 3.6864 GHz < freq<br>< 4.9152 GHz  | _      | _      | -8 + 16.6 *log<br>(freq/3.6864) | dB          |

| R <sub>LRX-CM</sub>         | Receiver common mode Return<br>Loss, package plus silicon        | _                                  | 6      | _      | _                               | dB          |

| Z <sub>RX-DIFF-DC</sub>     | Receiver DC differential impedance                               | _                                  | 80     | 100    | 120                             | Ω           |

**Note**: Data is measured with PRBS7 data pattern, not with PRBS-31 pattern.

Figure 3.23. JTAG Port Timing Waveforms

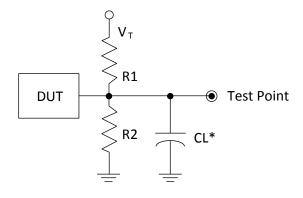

# 3.33. Switching Test Conditions

Figure 3.24 shows the output test load that is used for AC testing. The specific values for resistance, capacitance, voltage, and other test conditions are listed in Table 3.44.

\*CL Includes Test Fixture and Probe Capacitance

Figure 3.24. Output Test Load, LVTTL and LVCMOS Standards

### (Continued)

| Date          | Version | Section                             | Change Summary                                                                                                                     |  |  |

|---------------|---------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|

| November 2015 | 1.5     | All                                 | Added ECP5-5G device family.                                                                                                       |  |  |

|               |         |                                     | Changed document title to ECP5 and ECP5-5G Family Data Sheet.                                                                      |  |  |

|               | 1.4     | General Description                 | Updated Features section. Added support for eDP in RDR and HDR.                                                                    |  |  |

|               |         | Architecture                        | Updated Overview section.                                                                                                          |  |  |

|               |         |                                     | Revised Figure 2.1. Simplified Block Diagram, LFE5UM/LFE5UM5G-85 Device (Top Level). Modified Flexible sysIO description and Note. |  |  |

|               |         |                                     | Updated SERDES and Physical Coding Sublayer section.                                                                               |  |  |

|               |         |                                     | Changed E.24.V in CPRI protocol to E.24.LV.                                                                                        |  |  |

|               |         |                                     | Removed "1.1 V" from paragraph on unused Dual.                                                                                     |  |  |

|               |         | DC and Switching                    | Updated Hot Socketing Requirements section. Revised V <sub>CCHTX</sub> in table                                                    |  |  |

|               |         | Characteristics                     | notes 1 and 3. Indicated V <sub>CCHTX</sub> in table note 4.                                                                       |  |  |

|               |         |                                     | Updated SERDES High-Speed Data Transmitter section. Revised V <sub>CCHTX</sub>                                                     |  |  |

|               | ļ       |                                     | in table note 1.                                                                                                                   |  |  |

|               |         | Ordering Information                | Updated ECP5/ECP5-5G Part Number Description section. Changed "LFE5 FPGA" under Device Family to "ECP5 FPGA".                      |  |  |

| August 2015   | 1.3     | General Description                 | Updated Features section.                                                                                                          |  |  |

|               |         |                                     | Removed SMPTE3G under Embedded SERDES.                                                                                             |  |  |

|               |         |                                     | Added Single Event Upset (SEU) Mitigation Support.                                                                                 |  |  |

|               |         |                                     | Removed SMPTE protocol in fifth paragraph.                                                                                         |  |  |

|               |         | Architecture                        | General update.                                                                                                                    |  |  |

|               |         | DC and Switching<br>Characteristics | General update.                                                                                                                    |  |  |

|               |         | Pinout Information                  | Updated Signal Descriptions section. Revised the descriptions of the following signals:                                            |  |  |

|               |         |                                     | P[L/R] [Group Number]_[A/B/C/D]                                                                                                    |  |  |

|               |         |                                     | P[T/B][Group Number]_[A/B]                                                                                                         |  |  |

|               |         |                                     | D4/IO4 (Previously named D4/MOSI2/IO4)                                                                                             |  |  |

|               |         |                                     | D5/IO5 (Previously named D5/MISO/IO5)                                                                                              |  |  |

|               |         |                                     | VCCHRX_D[dual_num]CH[chan_num]                                                                                                     |  |  |

|               |         |                                     | VCCHTX_D[dual_num]CH[chan_num]                                                                                                     |  |  |

|               |         | Supplemental<br>Information         | Added TN1184 reference.                                                                                                            |  |  |