# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | 56800EX                                                               |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 100MHz                                                                |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                            |

| Peripherals                | Brown-out Detect/Reset, DMA, LVD, POR, PWM, WDT                       |

| Number of I/O              | 68                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 24K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b, 10x16b; D/A 1x12b                                         |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 80-LQFP                                                               |

| Supplier Device Package    | 80-FQFP (12x12)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc56f84766vlk |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Up to 16 KW FlexNVM, which can be used as additional program or data flash memory

- Up to 1 KW FlexRAM, which can be configured as enhanced EEPROM (used in conjunction with FlexNVM) or used as additional RAM

# 1.5 Interrupt Controller

- Five interrupt priority levels

- Three user programmable priority levels for each interrupt source: level 0, 1, 2

- Unmaskable level 3 interrupts include: illegal instruction, hardware stack overflow, misaligned data access, SWI3 instruction

- Maskable level 3 interrupts include: EOnCE step counter, EOnCE breakpoint unit, EOnCE trace buffer

- Lowest-priority software interrupt: level LP

- Support for nested interrupt: higher priority level interrupt request can interrupt lower priority interrupt subroutine

- Masking of interrupt priority level managed by the 56800EX core

- Two programmable fast interrupts that can be assigned to any interrupt source

- Notification to System Integration Module (SIM) to restart clock when in wait and stop states

- Ability to relocate interrupt vector table

# 1.6 Peripheral highlights

# 1.6.1 Enhanced Flex Pulse Width Modulator (eFlexPWM)

- PWM module contains four identical submodules with up to three outputs per submodule

- 16 bits of resolution for center, edge aligned, and asymmetrical PWMs

- PWMA with NanoEdge high resolution

- Fractional delay for enhanced resolution of the PWM period and edge placement

- Arbitrary PWM edge placement

- 312 ps PWM frequency and duty-cycle resolution when NanoEdge functionality is enabled

- PWMB with supporting accumulative fractional clock calculation

- Accumulative fractional clock calculation improves the resolution of the PWM period and edge placement

- Arbitrary PWM edge placement

- Equivalent to 312 ps PWM frequency and duty-cycle resolution on average

# 1.6.6 Quad Timer

- Four 16-bit up/down counters with programmable prescaler for each counter

- Operation modes: edge count, gated count, signed count, capture, compare, PWM, signal shot, single pulse, pulse string, cascaded, quadrature decode

- Programmable input filter

- Counting start can be synchronized across counters

# 1.6.7 Queued Serial Communications Interface (QSCI) Modules

- Operating clock up to two times CPU operating frequency

- Four-word-deep FIFOs available on both transmit and receive buffers

- Standard mark/space non-return-to-zero (NRZ) format

- 13-bit integer and 3-bit fractional baud rate selection

- Full-duplex or single-wire operation

- Programmable 8-bit or 9-bit data format

- Error detection capability

- Two receiver wakeup methods:

- Idle line

- Address mark

- 1/16 bit-time noise detection

# 1.6.8 Queued Serial Peripheral Interface (QSPI) Modules

- Maximum 25 Mbps baud rate

- Selectable baud rate clock sources for low baud rate communication

- Baud rate as low as Baudrate\_Freq\_in / 8192

- Full-duplex operation

- Master and slave modes

- Double-buffered operation with separate transmit and receive registers

- Four-word-deep FIFOs available on transmit and receive buffers

- Programmable length transmissions (2 bits to 16 bits)

- Programmable transmit and receive shift order (MSB as first bit transmitted)

### 1.6.9 Inter-Integrated Circuit (I2C)/System Management Bus (SMBus) Modules

- Compatible with I2C bus standard

- Support for System Management Bus (SMBus) specification, version 2

- Multi-master operation

- General call recognition

- 10-bit address extension

- Start/Repeat and Stop indication flags

- Support for dual slave addresses or configuration of a range of slave addresses

- Programmable glitch input filter

### 1.6.10 Flex Controller Area Network (FlexCAN) Module

- Clock source from PLL or XOSC/CLKIN

- Implementation of the CAN protocol Version 2.0 A/B

- Standard and extended data frames

- 0-to-8 bytes data length

- Programmable bit rate up to 1 Mbps

- Support for remote frames

- Sixteen Message Buffers, each configurable as receive or transmit, all supporting standard and extended messages

- Individual Rx Mask Registers per Message Buffer

- Internal timer for time-stamping of received and transmitted messages

- Listen-only mode capability

- Programmable loopback mode supporting self-test operation

- Programmable transmission priority scheme: lowest ID, lowest buffer number, or highest priority

- Global network time, synchronized by a specific message

- Low power modes, with programmable wakeup on bus activity

# 1.6.11 Computer Operating Properly (COP) Watchdog

- Programmable timeout period

- Support for operation in all power modes: run mode, wait mode, stop mode

- Causes loss of reference reset 128 cycles after loss of reference clock to the PLL is detected

- Selectable reference clock source in support of EN60730 and IEC61508

- Selectable clock sources:

- External crystal oscillator/external clock source

- On-chip low-power 32 kHz oscillator

- System bus (IPBus up to 100 MHz)

- 8 MHz / 400 kHz ROSC

- Support for interrupt triggered when the counter reaches the timeout value

Terminology and guidelines

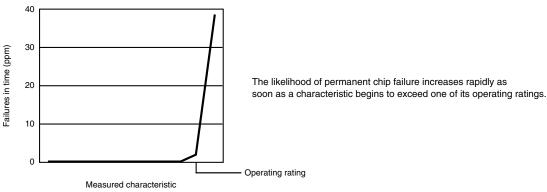

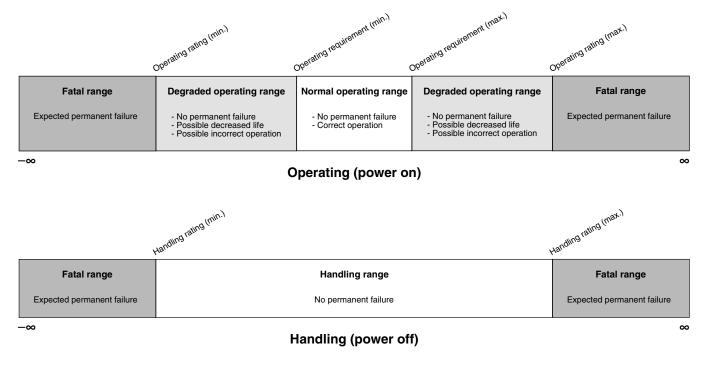

# 5.5 Result of exceeding a rating

# 5.6 Relationship between ratings and operating requirements

# 5.7 Guidelines for ratings and operating requirements

Follow these guidelines for ratings and operating requirements:

- Never exceed any of the chip's ratings.

- During normal operation, don't exceed any of the chip's operating requirements.

- If you must exceed an operating requirement at times other than during normal operation (for example, during power sequencing), limit the duration as much as possible.

# 5.8 Definition: Typical value

A *typical value* is a specified value for a technical characteristic that:

- Lies within the range of values specified by the operating behavior

- Given the typical manufacturing process, is representative of that characteristic during operation when you meet the typical-value conditions or other specified conditions

Typical values are provided as design guidelines and are neither tested nor guaranteed.

# 5.8.1 Example 1

This is an example of an operating behavior that includes a typical value:

| Symbol | Description                                    | Min. | Тур. | Max. | Unit |

|--------|------------------------------------------------|------|------|------|------|

|        | Digital I/O weak<br>pullup/pulldown<br>current | 10   | 70   | 130  | μΑ   |

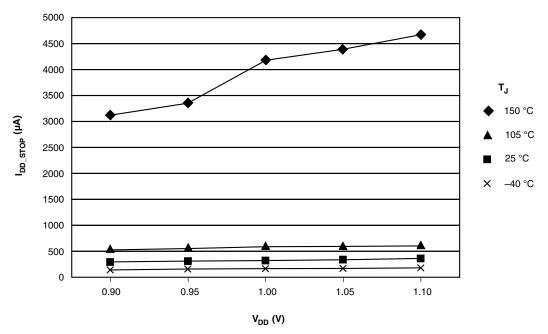

### 5.8.2 Example 2

This is an example of a chart that shows typical values for various voltage and temperature conditions:

# 6.3 ESD handling ratings

Although damage from electrostatic discharge (ESD) is much less common on these devices than on early CMOS circuits, use normal handling precautions to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

All ESD testing is in conformity with AEC-Q100 Stress Test Qualification. During the device qualification ESD stresses were performed for the human body model (HBM), the machine model (MM), and the charge device model (CDM).

All latch-up testing is in conformity with AEC-Q100 Stress Test Qualification.

A device is defined as a failure if after exposure to ESD pulses the device no longer meets the device specification. Complete DC parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

| Characteristic <sup>1</sup>                      | Min   | Max   | Unit |

|--------------------------------------------------|-------|-------|------|

| ESD for Human Body Model (HBM)                   | -2000 | +2000 | V    |

| ESD for Machine Model (MM)                       | -200  | +200  | V    |

| ESD for Charge Device Model (CDM)                | -500  | +500  | V    |

| Latch-up current at TA= 85°C (I <sub>LAT</sub> ) | -100  | +100  | mA   |

Table 3. ESD/Latch-up Protection

1. Parameter is achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted.

# 6.4 Voltage and current operating ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table 4 may affect device reliability or cause permanent damage to the device.

|                                                        | -                  |                    |      | -   |      |

|--------------------------------------------------------|--------------------|--------------------|------|-----|------|

| Characteristic                                         | Symbol             | Notes <sup>1</sup> | Min  | Max | Unit |

| Supply Voltage Range                                   | V <sub>DD</sub>    |                    | -0.3 | 4.0 | V    |

| Analog Supply Voltage Range                            | V <sub>DDA</sub>   |                    | -0.3 | 4.0 | V    |

| ADC High Voltage Reference                             | V <sub>REFHx</sub> |                    | -0.3 | 4.0 | V    |

| Voltage difference V <sub>DD</sub> to V <sub>DDA</sub> | ΔV <sub>DD</sub>   |                    | -0.3 | 0.3 | V    |

| Voltage difference V <sub>SS</sub> to V <sub>SSA</sub> | $\Delta V_{SS}$    |                    | -0.3 | 0.3 | V    |

Table continues on the next page...

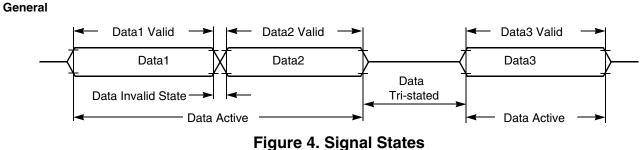

Figure 4. Signal States

# 7.3 Nonswitching electrical specifications

## 7.3.1 Voltage and current operating requirements

This section includes information about recommended operating conditions.

Recommended  $V_{DD}$  ramp rate is between 1 ms and 200 ms.

NOTE

| Table 5. | Recommended Operating Conditions ( $V_{REFLx} = 0 V$ , $V_{SSA} = 0 V$ , |

|----------|--------------------------------------------------------------------------|

|          | $V_{SS} = 0 V$ )                                                         |

| Characteristic                                                       | Symbol                             | Notes <sup>1</sup> | Min                   | Тур | Max                   | Unit |

|----------------------------------------------------------------------|------------------------------------|--------------------|-----------------------|-----|-----------------------|------|

| Supply voltage <sup>2</sup>                                          | V <sub>DD</sub> , V <sub>DDA</sub> |                    | 2.7                   | 3.3 | 3.6                   | V    |

| ADC (Cyclic) Reference Voltage High                                  | V <sub>REFHA</sub>                 |                    | 3.0                   |     | V <sub>DDA</sub>      | V    |

|                                                                      | V <sub>REFHB</sub>                 |                    |                       |     |                       |      |

| ADC (SAR) Reference Voltage High                                     | V <sub>REFHC</sub>                 |                    | 2.0                   |     | V <sub>DDA</sub>      | V    |

| Voltage difference V <sub>DD</sub> to V <sub>DDA</sub>               | ΔVDD                               |                    | -0.1                  | 0   | 0.1                   | V    |

| Voltage difference V <sub>SS</sub> to V <sub>SSA</sub>               | ΔVSS                               |                    | -0.1                  | 0   | 0.1                   | V    |

| Input Voltage High (digital inputs)                                  | V <sub>IH</sub>                    | Pin Group 1        | 0.7 x V <sub>DD</sub> |     | 5.5                   | V    |

| RESET Voltage High                                                   | V <sub>IH_RESET</sub>              | Pin Group 2        | 0.7 x V <sub>DD</sub> | _   | V <sub>DD</sub>       | V    |

| Input Voltage Low (digital inputs)                                   | VIL                                | Pin Groups 1, 2    |                       |     | $0.35 \times V_{DD}$  | V    |

| Oscillator Input Voltage High                                        | VIHOSC                             | Pin Group 4        | 2.0                   |     | V <sub>DD</sub> + 0.3 | V    |

| XTAL driven by an external clock source                              |                                    |                    |                       |     |                       |      |

| Oscillator Input Voltage Low                                         | VILOSC                             | Pin Group 4        | -0.3                  |     | 0.8                   | V    |

| Output Source Current High (at V <sub>OH</sub> min.) <sup>3, 4</sup> | I <sub>ОН</sub>                    |                    |                       |     |                       |      |

| Programmed for low drive strength                                    |                                    | Pin Group 1        | _                     |     | -2                    | mA   |

| Programmed for high drive strength                                   |                                    | Pin Group 1        | _                     |     | -9                    |      |

| Output Source Current Low (at V <sub>OL</sub> max.) <sup>3, 4</sup>  | I <sub>OL</sub>                    |                    |                       |     |                       |      |

| Programmed for low drive strength                                    |                                    | Pin Groups 1, 2    | —                     |     | 2                     | mA   |

| Programmed for high drive strength                                   |                                    | Pin Groups 1, 2    | —                     |     | 9                     |      |

#### 1. Default Mode

• Pin Group 1: GPIO, TDI, TDO, TMS, TCK

Pin Group 2: RESET

| Characteristic                                      | Symbol             | Notes <sup>1</sup> | Min                                     | Тур | Max                                     | Unit | Test Conditions                                                |

|-----------------------------------------------------|--------------------|--------------------|-----------------------------------------|-----|-----------------------------------------|------|----------------------------------------------------------------|

| Comparator Input Current<br>Low                     | I <sub>ILC</sub>   | Pin Group 3        | _                                       | 0   | +/- 2                                   | μA   | $V_{IN} = 0V$                                                  |

| Oscillator Input Current<br>Low                     | I <sub>ILOSC</sub> | Pin Group 3        | _                                       | 0   | +/- 2                                   | μA   | V <sub>IN</sub> = 0V                                           |

| DAC Output Voltage<br>Range                         | V <sub>DAC</sub>   | Pin Group 5        | Typically<br>V <sub>SSA</sub> +<br>40mV | —   | Typically<br>V <sub>DDA</sub> -<br>40mV | V    | $R_{LD} = 3 \text{ k}\Omega \parallel C_{LD} = 400 \text{ pf}$ |

| Output Current <sup>1</sup><br>High Impedance State | I <sub>OZ</sub>    | Pin Groups<br>1, 2 | _                                       | 0   | +/- 1                                   | μA   | —                                                              |

| Schmitt Trigger Input<br>Hysteresis                 | V <sub>HYS</sub>   | Pin Groups<br>1, 2 | 0.06 x V <sub>DD</sub>                  | —   | —                                       | V    | _                                                              |

#### 1. Default Mode

- Pin Group 1: GPIO, TDI, TDO, TMS, TCK

- Pin Group 2: RESET

- Pin Group 3: ADC and Comparator Analog Inputs

- Pin Group 4: XTAL, EXTAL

- Pin Group 5: DAC

### 7.3.4 Power mode transition operating behaviors

Parameters listed are guaranteed by design.

#### NOTE

All address and data buses described here are internal.

#### Table 8. Reset, Stop, Wait, and Interrupt Timing

| Characteristic                                                              | Symbol           | Typical Min                    | Typical<br>Max | Unit | See<br>Figure |

|-----------------------------------------------------------------------------|------------------|--------------------------------|----------------|------|---------------|

| Minimum RESET Assertion Duration                                            | t <sub>RA</sub>  | 16 <sup>1</sup>                | —              | ns   | _             |

| RESET deassertion to First Address Fetch                                    | t <sub>RDA</sub> | 865 x T <sub>OSC</sub> + 8 x T |                | ns   | _             |

| Delay from Interrupt Assertion to Fetch of first instruction (exiting Stop) | t <sub>IF</sub>  | 361.3                          | 570.9          | ns   | _             |

1. If the RESET pin filter is enabled by setting the RST\_FLT bit in the SIM\_CTRL register to 1, the minimum pulse assertion must be greater than 21 ns.

#### NOTE

In the Table 8, T = system clock cycle and  $T_{OSC}$  = oscillator clock cycle. For an operating frequency of 100 MHz, T = 10 ns. At 4 MHz (used coming out of reset and stop modes), T = 250 ns.

# 8 Peripheral operating requirements and behaviors

# 8.1 Core modules

## 8.1.1 JTAG Timing

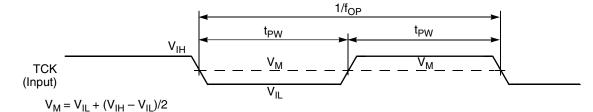

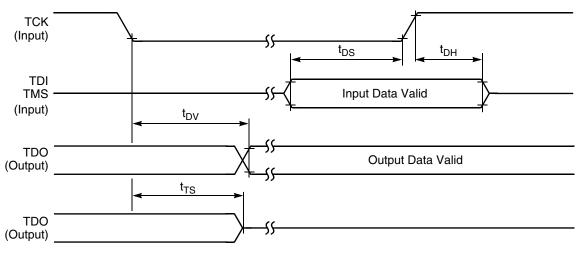

| Characteristic             | Symbol          | Min | Мах        | Unit | See<br>Figure |

|----------------------------|-----------------|-----|------------|------|---------------|

| TCK frequency of operation | f <sub>OP</sub> | DC  | SYS_CLK/16 | MHz  | Figure 5      |

| TCK clock pulse width      | t <sub>PW</sub> | 50  | _          | ns   | Figure 5      |

| TMS, TDI data set-up time  | t <sub>DS</sub> | 5   |            | ns   | Figure 6      |

| TMS, TDI data hold time    | t <sub>DH</sub> | 5   |            | ns   | Figure 6      |

| TCK low to TDO data valid  | t <sub>DV</sub> |     | 30         | ns   | Figure 6      |

| TCK low to TDO tri-state   | t <sub>TS</sub> |     | 30         | ns   | Figure 6      |

#### Table 14. JTAG Timing

#### Figure 5. Test Clock Input Timing Diagram

| Symbol                    | Description                              | Min. | Тур. | Max. | Unit | Notes |

|---------------------------|------------------------------------------|------|------|------|------|-------|

| t <sub>hversscr</sub>     | Sector Erase high-voltage time           | —    | 13   | 113  | ms   | 1     |

| t <sub>hversblk32k</sub>  | Erase Block high-voltage time for 32 KB  | —    | 52   | 452  | ms   | 1     |

| t <sub>hversblk256k</sub> | Erase Block high-voltage time for 256 KB |      | 104  | 904  | ms   | 1     |

Table 21. NVM program/erase timing specifications (continued)

1. Maximum time based on expectations at cycling end-of-life.

#### 8.4.1.2 Flash timing specifications — commands Table 22. Flash command timing specifications

| Symbol                  | Description                                           | Min. | Тур. | Max. | Unit | Notes |

|-------------------------|-------------------------------------------------------|------|------|------|------|-------|

|                         | Read 1s Block execution time                          |      |      |      |      |       |

| t <sub>rd1blk32k</sub>  | • 32 KB data flash                                    | _    | _    | 0.5  | ms   |       |

| t <sub>rd1blk256k</sub> | 256 KB program flash                                  | _    | _    | 1.7  | ms   |       |

| t <sub>rd1sec1k</sub>   | Read 1s Section execution time (data flash sector)    | -    | -    | 60   | μs   | 1     |

| t <sub>rd1sec2k</sub>   | Read 1s Section execution time (program flash sector) | -    | _    | 60   | μs   | 1     |

| t <sub>pgmchk</sub>     | Program Check execution time                          | _    | -    | 45   | μs   | 1     |

| t <sub>rdrsrc</sub>     | Read Resource execution time                          | _    | —    | 30   | μs   | 1     |

| t <sub>pgm4</sub>       | Program Longword execution time                       | _    | 65   | 145  | μs   |       |

|                         | Erase Flash Block execution time                      |      |      |      |      | 2     |

| t <sub>ersblk32k</sub>  | · 32 KB data flash                                    |      | 55   | 465  | ms   |       |

| t <sub>ersblk256k</sub> | 256 KB program flash                                  | -    | 122  | 985  | ms   |       |

| t <sub>ersscr</sub>     | Erase Flash Sector execution time                     |      | 14   | 114  | ms   | 2     |

|                         | Program Section execution time                        |      |      |      |      |       |

| t <sub>pgmsec512p</sub> | • 512 B program flash                                 | _    | 2.4  | _    | ms   |       |

| t <sub>pgmsec512d</sub> | • 512 B data flash                                    | _    | 4.7  | _    | ms   |       |

| t <sub>pgmsec1kp</sub>  | <ul> <li>1 KB program flash</li> </ul>                | _    | 4.7  | _    | ms   |       |

| t <sub>pgmsec1kd</sub>  | • 1 KB data flash                                     | _    | 9.3  | _    | ms   |       |

| t <sub>rd1all</sub>     | Read 1s All Blocks execution time                     |      |      | 1.8  | ms   |       |

| t <sub>rdonce</sub>     | Read Once execution time                              | _    | —    | 25   | μs   | 1     |

| t <sub>pgmonce</sub>    | Program Once execution time                           | _    | 65   | —    | μs   |       |

| t <sub>ersall</sub>     | Erase All Blocks execution time                       | _    | 175  | 1500 | ms   | 2     |

| t <sub>vfykey</sub>     | Verify Backdoor Access Key execution time             | _    | —    | 30   | μs   | 1     |

|                         | Program Partition for EEPROM execution time           |      |      |      |      |       |

| t <sub>pgmpart32k</sub> | • 32 KB FlexNVM                                       | -    | 70   | _    | ms   |       |

Table continues on the next page...

#### 8.4.1.4 Reliability specifications Table 24. NVM reliability specifications

| Symbol                   | Description                                             | Min.     | Typ. <sup>1</sup> | Max. | Unit   | Notes |

|--------------------------|---------------------------------------------------------|----------|-------------------|------|--------|-------|

|                          | Program                                                 | n Flash  |                   |      |        |       |

| t <sub>nvmretp10k</sub>  | Data retention after up to 10 K cycles                  | 5        | 50                | _    | years  |       |

| t <sub>nvmretp1k</sub>   | Data retention after up to 1 K cycles                   | 20       | 100               | —    | years  |       |

| n <sub>nvmcycp</sub>     | Cycling endurance                                       | 10 K     | 50 K              | —    | cycles | 2     |

|                          | Data                                                    | Flash    | •                 |      |        |       |

| t <sub>nvmretd10k</sub>  | Data retention after up to 10 K cycles                  | 5        | 50                | _    | years  |       |

| t <sub>nvmretd1k</sub>   | Data retention after up to 1 K cycles                   | 20       | 100               | _    | years  |       |

| n <sub>nvmcycd</sub>     | mcycd Cycling endurance                                 |          | 50 K              | _    | cycles | 2     |

|                          | FlexRAM as                                              | s EEPROM |                   |      |        |       |

| t <sub>nvmretee100</sub> | 100 Data retention up to 100% of write endurance        |          | 50                | _    | years  |       |

| t <sub>nvmretee10</sub>  | Data retention up to 10% of write endurance             | 20       | 100               | _    | years  |       |

|                          | Write endurance                                         |          |                   |      |        | 3     |

| n <sub>nvmwree16</sub>   | <ul> <li>EEPROM backup to FlexRAM ratio = 16</li> </ul> | 35 K     | 175 K             | _    | writes |       |

| n <sub>nvmwree128</sub>  | • EEPROM backup to FlexRAM ratio = 128                  |          | 1.6 M             | _    | writes |       |

| n <sub>nvmwree512</sub>  | • EEPROM backup to FlexRAM ratio = 512                  |          | 6.4 M             | _    | writes |       |

| n <sub>nvmwree4k</sub>   | • EEPROM backup to FlexRAM ratio = 4096                 |          | 50 M              | _    | writes |       |

| n <sub>nvmwree8k</sub>   | EEPROM backup to FlexRAM ratio = 8192                   | 20 M     | 100 M             | _    | writes |       |

Typical data retention values are based on measured response accelerated at high temperature and derated to a constant 25°C use profile. Engineering Bulletin EB618 does not apply to this technology. Typical endurance defined in Engineering Bulletin EB619.

2. Cycling endurance represents number of program/erase cycles at -40°C  $\leq$  T<sub>i</sub>  $\leq$  125°C.

3. Write endurance represents the number of writes to each FlexRAM location at -40°C ≤Tj ≤ 125°C influenced by the cycling endurance of the FlexNVM (same value as data flash) and the allocated EEPROM backup. Minimum and typical values assume all byte-writes to FlexRAM.

# 8.5 Analog

### 8.5.1 12-bit Cyclic Analog-to-Digital Converter (ADC) Parameters Table 25. 12-bit ADC Electrical Specifications

| Characteristic                    | Symbol              | Min               | Тур | Max               | Unit |

|-----------------------------------|---------------------|-------------------|-----|-------------------|------|

| Recommended Operating Conditions  |                     |                   |     |                   |      |

| Supply Voltage <sup>1</sup>       | V <sub>DDA</sub>    | 2.7               | 3.3 | 3.6               | V    |

| Vrefh Supply Voltage <sup>2</sup> | Vrefhx              | 3.0               |     | V <sub>DDA</sub>  | V    |

| ADC Conversion Clock <sup>3</sup> | f <sub>ADCCLK</sub> | 0.6               |     | 20                | MHz  |

| Conversion Range                  | R <sub>AD</sub>     | V <sub>REFL</sub> |     | V <sub>REFH</sub> | V    |

Table continues on the next page...

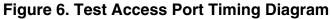

- 7. Input data is 1 kHz sine wave. ADC conversion clock <12MHz.

- 8. System Clock = 4 MHz, ADC Clock = 2 MHz, AVG = Max, Long Sampling = Max

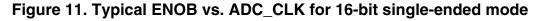

Typical ADC 16-bit Single-Ended ENOB vs ADC Clock 100Hz, 90% FS Sine Input

### 8.5.3 12-bit Digital-to-Analog Converter (DAC) Parameters Table 28. DAC Parameters

| Parameter                           | Conditions/Comments                                             | Symbol            | Min | Тур     | Max     | Unit             |

|-------------------------------------|-----------------------------------------------------------------|-------------------|-----|---------|---------|------------------|

|                                     | DC Speci                                                        | ifications        |     |         |         |                  |

| Resolution                          |                                                                 |                   | 12  | 12      | 12      | bits             |

| Settling time <sup>1</sup>          | At output load                                                  |                   | —   | 1       |         | μs               |

|                                     | RLD = 3 kΩ                                                      |                   |     |         |         |                  |

|                                     | CLD = 400 pf                                                    |                   |     |         |         |                  |

| Power-up time                       | Time from release of PWRDWN signal until DACOUT signal is valid | t <sub>DAPU</sub> | _   | -       | 11      | μs               |

|                                     | Accu                                                            | iracy             |     |         |         |                  |

| Integral non-linearity <sup>2</sup> | Range of input digital words:                                   | INL               | —   | +/- 3   | +/- 4   | LSB <sup>3</sup> |

|                                     | 410 to 3891 (\$19A - \$F33)                                     |                   |     |         |         |                  |

|                                     | 5% to 95% of full range                                         |                   |     |         |         |                  |

| Differential non-                   | Range of input digital words:                                   | DNL               |     | +/- 0.8 | +/- 0.9 | LSB <sup>3</sup> |

| linearity <sup>2</sup>              | 410 to 3891 (\$19A - \$F33)                                     |                   |     |         |         |                  |

|                                     | 5% to 95% of full range                                         |                   |     |         |         |                  |

Table continues on the next page ...

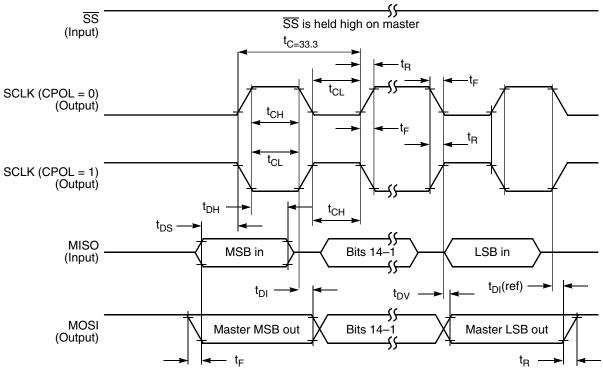

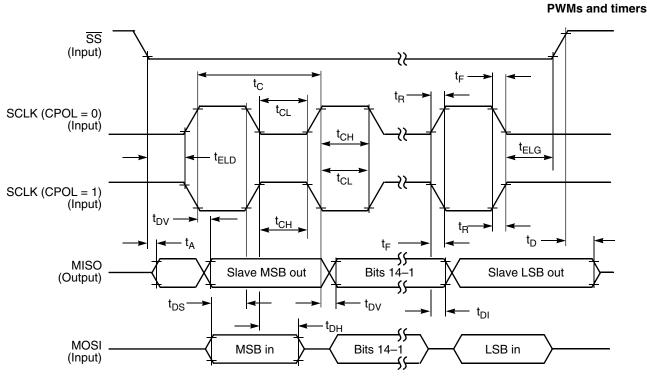

**PWMs and timers**

| Characteristic                                       | Symbol           | Min  | Max | Unit | See Figure |

|------------------------------------------------------|------------------|------|-----|------|------------|

| Enable lead time                                     | t <sub>ELD</sub> |      |     |      | Figure 18  |

| Master                                               |                  | —    | _   | ns   |            |

| Slave                                                |                  | 17.5 | _   | ns   |            |

| Enable lag time                                      | t <sub>ELG</sub> |      |     |      | Figure 18  |

| Master                                               |                  | —    | _   | ns   |            |

| Slave                                                |                  | 17.5 | _   | ns   |            |

| Clock (SCK) high time                                | t <sub>CH</sub>  |      |     |      | Figure 15  |

| Master                                               |                  | 16.6 | _   | ns   | Figure 16  |

| Slave                                                |                  | 16.6 | _   | ns   | Figure 17  |

|                                                      |                  |      |     |      | Figure 18  |

| Clock (SCK) low time                                 | t <sub>CL</sub>  |      |     |      | Figure 18  |

| Master                                               |                  | 16.6 | -   | ns   |            |

| Slave                                                |                  | 16.6 | _   | ns   |            |

| Data set-up time required for inputs                 | t <sub>DS</sub>  |      |     |      | Figure 15  |

| Master                                               |                  | 16.5 | _   | ns   | Figure 16  |

| Slave                                                |                  | 1    | _   | ns   | Figure 17  |

|                                                      |                  |      |     |      | Figure 18  |

| Data hold time required for inputs                   | t <sub>DH</sub>  |      |     |      | Figure 15  |

| Master                                               |                  | 1    | _   | ns   | Figure 16  |

| Slave                                                |                  | 3    | _   | ns   | Figure 17  |

|                                                      |                  |      |     |      | Figure 18  |

| Access time (time to data active                     | t <sub>A</sub>   |      |     |      | Figure 18  |

| from high-impedance state)                           |                  | 5    | _   | ns   |            |

| Slave                                                |                  |      |     |      |            |

| Disable time (hold time to high-<br>impedance state) | t <sub>D</sub>   |      |     |      | Figure 18  |

| Slave                                                |                  | 5    | _   | ns   |            |

| Data valid for outputs                               | t <sub>DV</sub>  |      |     |      | Figure 15  |

| Master                                               | vu               | _    | 5   | ns   | Figure 16  |

| Slave (after enable edge)                            |                  | _    | 15  | ns   | Figure 17  |

| Slave (aller shable bage)                            |                  |      |     |      | Figure 18  |

| Data invalid                                         | t <sub>DI</sub>  |      |     |      | Figure 15  |

| Master                                               | וטי              | 0    |     | ns   | Figure 16  |

| Slave                                                |                  | 0    | _   | ns   | Figure 17  |

|                                                      |                  | 5    |     |      | Figure 18  |

### Table 32. SPI Timing (continued)

Table continues on the next page ...

| Characteristic | Symbol         | Min | Max | Unit | See Figure |

|----------------|----------------|-----|-----|------|------------|

| Rise time      | t <sub>R</sub> |     |     |      | Figure 15  |

| Master         |                | —   | 1   | ns   | Figure 16  |

| Slave          |                | —   | 1   | ns   | Figure 17  |

|                |                |     |     |      | Figure 18  |

| Fall time      | t <sub>F</sub> |     |     |      | Figure 15  |

| Master         |                | —   | 1   | ns   | Figure 16  |

| Slave          |                | —   | 1   | ns   | Figure 17  |

|                |                |     |     |      | Figure 18  |

Table 32.

SPI Timing (continued)

Figure 18. SPI Slave Timing (CPHA = 1)

### 8.7.2 Queued Serial Communication Interface (SCI) Timing

Parameters listed are guaranteed by design.

| Characteristic                                                                              | Symbol                   | Min        | Max                    | Unit                          | See Figure |

|---------------------------------------------------------------------------------------------|--------------------------|------------|------------------------|-------------------------------|------------|

| Baud rate <sup>1</sup> BF                                                                   |                          |            | (f <sub>MAX</sub> /16) | Mbps                          | —          |

| RXD pulse width                                                                             | RXD <sub>PW</sub>        | 0.965/BR   | 1.04/BR                | ns                            | Figure 19  |

| TXD pulse width                                                                             | TXD <sub>PW</sub>        | 0.965/BR   | 1.04/BR                | ns                            | Figure 20  |

|                                                                                             | LIN                      | Slave Mode |                        |                               |            |

| Deviation of slave node clock from nominal clock rate before synchronization                | F <sub>TOL_UNSYNCH</sub> | -14        | 14                     | %                             | _          |

| Deviation of slave node clock relative to<br>the master node clock after<br>synchronization | F <sub>TOL_SYNCH</sub>   | -2         | 2                      | %                             | _          |

| Minimum break character length                                                              | T <sub>BREAK</sub>       | 13         | _                      | Master<br>node bit<br>periods | _          |

|                                                                                             |                          | 11         | _                      | Slave node<br>bit periods     | _          |

1. f<sub>MAX</sub> is the frequency of operation of the SCI clock in MHz, which can be selected as the bus clock (max. 200 MHz depending on part number) or 2x bus clock (max. 200 MHz) for the devices.

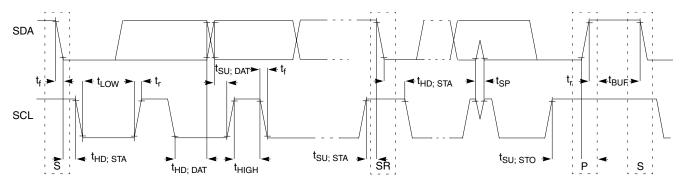

| Characteristic                                                       | Symbol                | Standa  | Standard Mode |                                    | Mode    | Unit |

|----------------------------------------------------------------------|-----------------------|---------|---------------|------------------------------------|---------|------|

|                                                                      |                       | Minimum | Maximum       | Minimum                            | Maximum |      |

| Fall time of SDA and SCL signals                                     | t <sub>f</sub>        | —       | 300           | 20 +0.1C <sub>b</sub> <sup>5</sup> | 300     | ns   |

| Set-up time for STOP condition                                       | t <sub>SU</sub> ; STO | 4       |               | 0.6                                |         | μs   |

| Bus free time between STOP and<br>START condition                    | t <sub>BUF</sub>      | 4.7     | _             | 1.3                                | _       | μs   |

| Pulse width of spikes that must be<br>suppressed by the input filter | t <sub>SP</sub>       | N/A     | N/A           | 0                                  | 50      | ns   |

Table 35. I<sup>2</sup>C Timing (continued)

- 1. The master mode I<sup>2</sup>C deasserts ACK of an address byte simultaneously with the falling edge of SCL. If no slaves acknowledge this address byte, a negative hold time can result, depending on the edge rates of the SDA and SCL lines.

- The maximum tHD; DAT must be met only if the device does not stretch the LOW period (tLOW) of the SCL signal.

- 3. Input signal Slew = 10ns and Output Load = 50pf

- 4. Set-up time in slave-transmitter mode is 1 IPBus clock period, if the TX FIFO is empty.

- 5. A Fast mode I<sup>2</sup>C bus device can be used in a Standard mode I2C bus system, but the requirement t<sub>SU; DAT</sub> ≥ 250 ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line t<sub>rmax</sub> + t<sub>SU; DAT</sub> = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification) before the SCL line is released.

- 6.  $C_b$  = total capacitance of the one bus line in pF.

Figure 22. Timing Definition for Fast and Standard Mode Devices on the I<sup>2</sup>C Bus

### 9 Design Considerations

### 9.1 Thermal Design Considerations

An estimation of the chip junction temperature, TJ, can be obtained from the equation:

$T_J = T_A + (R_{\Theta JA} \times P_D)$

Where,

$T_A$  = Ambient temperature for the package (°C)

$R_{\Theta JA}$  = Junction-to-ambient thermal resistance (°C/W)

$P_D$  = Power dissipation in the package (W)

Pinout

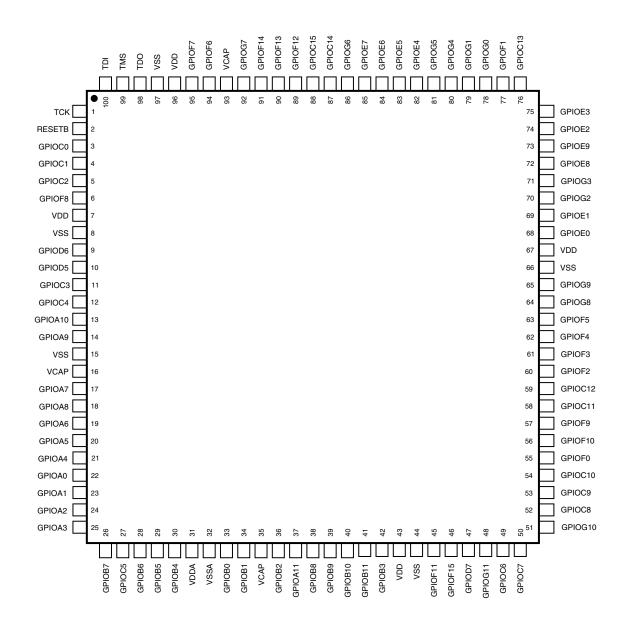

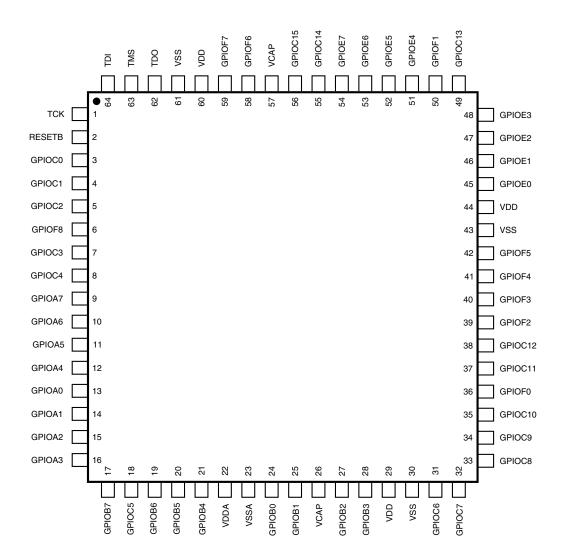

# 11.2 Pinout diagrams

The following diagrams show pinouts for the packages. For each pin, the diagrams show the default function. However, many signals may be multiplexed onto a single pin.

Figure 23. 100-pin LQFP

#### Figure 25. 64-pin LQFP

NOTE

The RESETB pin is a 3.3 V pin only.

# **12 Product Documentation**

The documents listed in Table 36 are required for a complete description and proper design with the device. Documentation is available from local Freescale distributors, Freescale Semiconductor sales offices, or online at http://www.freescale.com.

| Торіс                                    | Description                                                                                                                       | Document Number  |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------|

| DSP56800E/DSP56800EX<br>Reference Manual | Detailed description of the 56800EX family architecture, 32-bit digital signal controller core processor, and the instruction set | DSP56800ERM      |

| MC56F847xx Reference Manual              | Detailed functional description and programming model                                                                             | MC56F847XXRM     |

| Serial Bootloader User Guide             | Detailed description of the Serial Bootloader in the DSC family of devices                                                        |                  |

| MC56F847xx Data Sheet                    | Electrical and timing specifications, pin descriptions, and package information (this document)                                   | MC56F847XX       |

| MC56F84xxx Errata                        | Details any chip issues that might be present                                                                                     | MC56F84XXX_0N27E |

Table 36. Device Documentation

# **13 Revision History**

The following table summarizes changes to this document since the release of the previous version.

| Rev. | Date    | Substantial Changes                                                                                                                                                            |

|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3    | 08/2012 | In various locations: Clarified that the RESETB pin is a 3.3 V pin only                                                                                                        |

|      |         | MC56F844x/5x/7x Product Family: Clarified that DAC table row applies to 12-bit DAC                                                                                             |

|      |         | Voltage and current operating ratings: Added rows for RESET input voltage range and RESET output voltage range                                                                 |

|      |         | Voltage and current operating requirements: Added row for RESET voltage high, and added new final footnote                                                                     |

|      |         | Voltage and current operating behaviors: For Digital Input Current High, created separate sub-rows for Pin Groups 1 and 2                                                      |

|      |         | Power mode transition operating behaviors: Updated row for RESET deassertion to First Address Fetch                                                                            |

|      |         | Power consumption operating behaviors: Replaced all TBD values, and updated Typical at 3.3 V $I_{\text{DDA}}$ value for WAIT mode                                              |

|      |         | EMC radiated emissions operating behaviors: Removed this section                                                                                                               |

|      |         | Thermal attributes: Updated values for 100 LQFP                                                                                                                                |

|      |         | JTAG Timing: Changed divider value of Max for TCK frequency of operation                                                                                                       |

|      |         | Relaxation Oscillator Timing: Replaced all TBDs, and removed Standby Mode specification for 8 MHz Frequency Variation                                                          |

|      |         | Peripheral operating requirements and behaviors: Updated Flash timing specifications and added Flash high voltage current behaviors                                            |

|      |         | 16-bit ADC electrical characteristics: Updated DNL information about Max value for 16-bit modes and 12-bit modes, and updated INL information about Max value for 16-bit modes |

|      |         | Signal Multiplexing and Pin Assignments: Added note about GPIOC1, added JTAG signals to table and diagrams, and changed "SCK" signal names to "SCLK"                           |

### Table 37. Revision History