Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

|                            |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1.5K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 13x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4510t-i-ml |

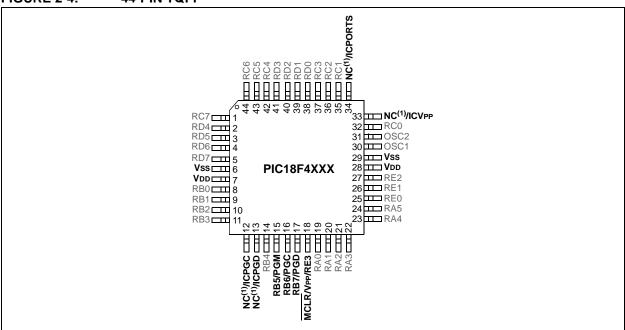

The following devices are included in 44-pin TQFP parts:

- PIC18F4221

- PIC18F4321

- PIC18F4410

- PIC18F4420

- PIC18F4423

- PIC18F4450

- PIC18F4455

- PIC18F4458PIC18F4480

- PIC18F4510

- PIC18F4520

- PIC18F4515

- PIC18F4523

- PIC18F4525

- PIC18F4550

- PIC18F4553

- PIC18F4580

- 1 10 101 1000

- PIC18F4585PIC18F4610

- PIC18F4620

- PIC18F4680

- PIC18F4682

- PIC18F4685

#### FIGURE 2-4: 44-PIN TQFP

Note 1: These pins are NC (No Connect) for all devices listed above with the exception of the PIC18F4450, PIC18F4455, PIC18F4458 and the PIC18F4553 devices (see Section 2.8 "Dedicated ICSP/ICD Port (44-Pin TQFP Only)" for more information on programming these pins in these devices).

For PIC18F2685/4685 devices, the code memory space extends from 0000h to 017FFFh (96 Kbytes) in five 16-Kbyte blocks. For PIC18F2682/4682 devices, the code memory space extends from 0000h to 0013FFFh (80 Kbytes) in four 16-Kbyte blocks. Addresses, 0000h through 0FFFh, however, define a "Boot Block" region that is treated separately from Block 0. All of these blocks define code protection boundaries within the code memory space.

The size of the Boot Block in PIC18F2685/4685 and PIC18F2682/4682 devices can be configured as 1, 2 or 4K words (see Figure 2-7). This is done through the BBSIZ<2:1> bits in the Configuration register, CONFIG4L. It is important to note that increasing the size of the Boot Block decreases the size of Block 0.

TABLE 2-3: IMPLEMENTATION OF CODE MEMORY

| Device     | Code Memory Size (Bytes) |

|------------|--------------------------|

| PIC18F2682 | 000000h 012EEEh (90K)    |

| PIC18F4682 | 000000h-013FFFh (80K)    |

| PIC18F2685 | 000000h 017EEEh (06K)    |

| PIC18F4685 | 000000h-017FFFh (96K)    |

TABLE 2-4: IMPLEMENTATION OF CODE MEMORY

| Device     | Code Memory Size (Bytes) |

|------------|--------------------------|

| PIC18F2455 |                          |

| PIC18F2458 | 000000h 005FFFh (24K)    |

| PIC18F4455 | 000000h-005FFFh (24K)    |

| PIC18F4458 |                          |

| PIC18F2510 |                          |

| PIC18F2520 |                          |

| PIC18F2523 |                          |

| PIC18F2550 |                          |

| PIC18F2553 | 000000h 007FFFh (20K)    |

| PIC18F4510 | 000000h-007FFFh (32K)    |

| PIC18F4520 |                          |

| PIC18F4523 |                          |

| PIC18F4550 |                          |

| PIC18F4553 |                          |

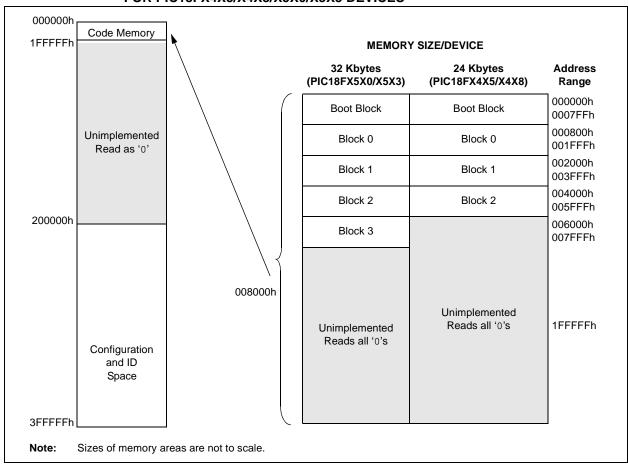

FIGURE 2-8: MEMORY MAP AND THE CODE MEMORY SPACE FOR PIC18FX4X5/X4X8/X5X0/X5X3 DEVICES

For PIC18FX4X0/X4X3 devices, the code memory space extends from 000000h to 003FFh (16 Kbytes) in two 8-Kbyte blocks. Addresses, 000000h through 0003FFh, however, define a "Boot Block" region that is treated separately from Block 0. All of these blocks define code protection boundaries within the code memory space.

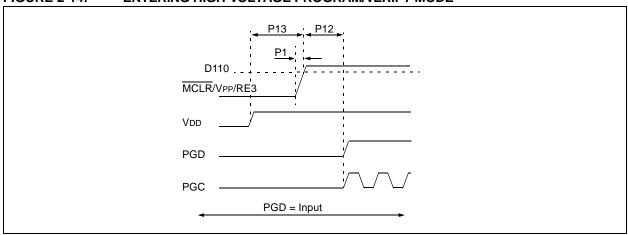

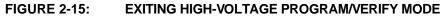

### 2.5 Entering and Exiting High-Voltage ICSP Program/Verify Mode

As shown in Figure 2-14, the High-Voltage ICSP Program/Verify mode is entered by holding PGC and PGD low and then raising MCLR/VPP/RE3 to VIHH (high voltage). Once in this mode, the code memory, data EEPROM (selected devices only, see **Section 3.3 "Data EEPROM Programming"**), ID locations and Configuration bits can be accessed and programmed in serial fashion. Figure 2-15 shows the exit sequence.

The sequence that enters the device into the Program/Verify mode places all unused I/Os in the high-impedance state.

FIGURE 2-14: ENTERING HIGH-VOLTAGE PROGRAM/VERIFY MODE

#### 2.7 Serial Program/Verify Operation

The PGC pin is used as a clock input pin and the PGD pin is used for entering command bits and data input/output during serial operation. Commands and data are transmitted on the rising edge of PGC, latched on the falling edge of PGC and are Least Significant bit (LSb) first.

#### 2.7.1 4-BIT COMMANDS

All instructions are 20 bits, consisting of a leading 4-bit command followed by a 16-bit operand, which depends on the type of command being executed. To input a command, PGC is cycled four times. The commands needed for programming and verification are shown in Table 2-8.

Depending on the 4-bit command, the 16-bit operand represents 16 bits of input data or 8 bits of input data and 8 bits of output data.

Throughout this specification, commands and data are presented as illustrated in Table 2-9. The 4-bit command is shown Most Significant bit (MSb) first. The command operand, or "Data Payload", is shown as <MSB><LSB>. Figure 2-18 demonstrates how to serially present a 20-bit command/operand to the device.

#### 2.7.2 CORE INSTRUCTION

The core instruction passes a 16-bit instruction to the CPU core for execution. This is needed to set up registers as appropriate for use with other commands.

TABLE 2-8: COMMANDS FOR PROGRAMMING

| Description                                            | 4-Bit Command |

|--------------------------------------------------------|---------------|

| Core Instruction (Shift in16-bit instruction)          | 0000          |

| Shift Out TABLAT Register                              | 0010          |

| Table Read                                             | 1000          |

| Table Read, Post-Increment                             | 1001          |

| Table Read, Post-Decrement                             | 1010          |

| Table Read, Pre-Increment                              | 1011          |

| Table Write                                            | 1100          |

| Table Write, Post-Increment by 2                       | 1101          |

| Table Write, Start Programming,<br>Post-Increment by 2 | 1110          |

| Table Write, Start Programming                         | 1111          |

### TABLE 2-9: SAMPLE COMMAND SEQUENCE

| 4-Bit Command | Data Payload | Core Instruction    |

|---------------|--------------|---------------------|

| 1101          | 3C 40        | Table Write,        |

|               |              | post-increment by 2 |

### 2.8 Dedicated ICSP/ICD Port (44-Pin TQFP Only)

The PIC18F4455/4458/4550/4553 44-pin TQFP devices are designed to support an alternate programming input: the dedicated ICSP/ICD port. The primary purpose of this port is to provide an alternate In-Circuit Debugging (ICD) option and free the pins (RB6, RB7 and  $\overline{MCLR}$ ) that would normally be used for debugging the application. In conjunction with ICD capability, however, the dedicated ICSP/ICD port also provides an alternate port for ICSP.

Setting the ICPRT Configuration bit enables the dedicated ICSP/ICD port. The dedicated ICSP/ICD port functions the same as the default ICSP/ICD port; however, alternate pins are used instead of the default pins. Table 2-10 identifies the functionally equivalent pins for ICSP purposes:

The dedicated ICSP/ICD port is an alternate port. Thus, ICSP is still available through the default port even though the ICPRT Configuration bit is set. When the VIH is seen on the MCLR/VPP/RE3 pin prior to applying VIH to the ICRST/ICVPP pin, then the state of the ICRST/ICVPP pin is ignored. Likewise, when the VIH is seen on ICRST/ICVPP prior to applying VIH to MCLR/VPP/RE3, then the state of the MCLR/VPP/RE3 pin is ignored.

**Note:** The ICPRT Configuration bit can only be programmed through the default ICSP port. Chip Erase functions through the dedicated ICSP/ICD port do not affect this bit.

When the ICPRT Configuration bit is set (dedicated ICSP/ICD port enabled), the NC/ICPORTS pin must be tied to either VDD or VSS.

The ICPRT Configuration bit must be maintained clear for all 28-pin and 40-pin devices; otherwise, unexpected operation may occur.

TABLE 2-10: ICSP™ EQUIVALENT PINS

| Pin Name     | During Programming |          |                |                    |

|--------------|--------------------|----------|----------------|--------------------|

| Pili Name    | Pin Name           | Pin Type | Dedicated Pins | Pin Description    |

| MCLR/Vpp/RE3 | VPP                | Р        | NC/ICRST/ICVPP | Programming Enable |

| RB6          | PGC                | I        | NC/ICCK/ICPGC  | Serial Clock       |

| RB7          | PGD                | I/O      | NC/ICDT/ICPGD  | Serial Data        |

**Legend:** I = Input, O = Output, P = Power

#### 3.0 DEVICE PROGRAMMING

Programming includes the ability to erase or write the various memory regions within the device.

In all cases, except high-voltage ICSP Bulk Erase, the EECON1 register must be configured in order to operate on a particular memory region.

When using the EECON1 register to act on code memory, the EEPGD bit must be set (EECON1<7> = 1) and the CFGS bit must be cleared (EECON1<6> = 0). The WREN bit must be set (EECON1<2> = 1) to enable writes of any sort (e.g., erases) and this must be done prior to initiating a write sequence. The FREE bit must be set (EECON1<4> = 1) in order to erase the program space being pointed to by the Table Pointer. The erase or write sequence is initiated by setting the WR bit (EECON1<1> = 1). It is strongly recommended that the WREN bit only be set immediately prior to a program erase.

#### 3.1 ICSP Erase

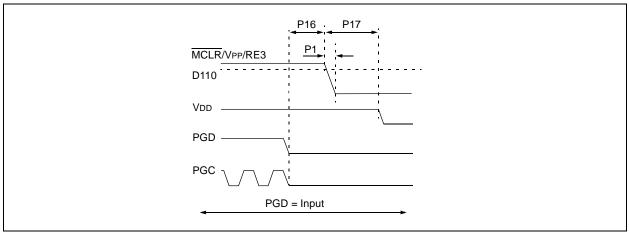

#### 3.1.1 HIGH-VOLTAGE ICSP BULK ERASE

Erasing code or data EEPROM is accomplished by configuring two Bulk Erase Control registers located at 3C0004h and 3C0005h. Code memory may be erased, portions at a time, or the user may erase the entire device in one action. Bulk Erase operations will also clear any code-protect settings associated with the memory block being erased. Erase options are detailed in Table 3-1. If data EEPROM is code-protected (CPD = 0), the user must request an erase of data EEPROM (e.g., 0084h as shown in Table 3-1).

TABLE 3-1: BULK ERASE OPTIONS

| Description                      | Data<br>(3C0005h:3C0004h) |

|----------------------------------|---------------------------|

| Chip Erase                       | 3F8Fh                     |

| Erase Data EEPROM <sup>(1)</sup> | 0084h                     |

| Erase Boot Block                 | 0081h                     |

| Erase Configuration Bits         | 0082h                     |

| Erase Code EEPROM Block 0        | 0180h                     |

| Erase Code EEPROM Block 1        | 0280h                     |

| Erase Code EEPROM Block 2        | 0480h                     |

| Erase Code EEPROM Block 3        | 0880h                     |

| Erase Code EEPROM Block 4        | 1080h                     |

| Erase Code EEPROM Block 5        | 2080h                     |

Note 1: Selected devices only, see Section 3.3 "Data EEPROM Programming".

The actual Bulk Erase function is a self-timed operation. Once the erase has started (falling edge of the 4th PGC after the NOP command), serial execution will cease until the erase completes (Parameter P11). During this time, PGC may continue to toggle but PGD must be held low.

The code sequence to erase the entire device is shown in Table and the flowchart is shown in Figure 3-1.

Note: A Bulk Erase is the only way to reprogram code-protect bits from an ON state to an OFF state.

TABLE 3-2: BULK ERASE COMMAND SEQUENCE

| 4-Bit Command | Data Payload | Core Instruction                               |

|---------------|--------------|------------------------------------------------|

| 0000          | 0E 3C        | MOVLW 3Ch                                      |

| 0000          | 6E F8        | MOVWF TBLPTRU                                  |

| 0000          | 0E 00        | MOVLW 00h                                      |

| 0000          | 6E F7        | MOVWF TBLPTRH                                  |

| 0000          | 0E 05        | MOVLW 05h                                      |

| 0000          | 6E F6        | MOVWF TBLPTRL                                  |

| 1100          | 3F 3F        | Write 3F3Fh to 3C0005h                         |

| 0000          | 0E 3C        | MOVLW 3Ch                                      |

| 0000          | 6E F8        | MOVWF TBLPTRU                                  |

| 0000          | 0E 00        | MOVLW 00h                                      |

| 0000          | 6E F7        | MOVWF TBLPTRH                                  |

| 0000          | 0E 04        | MOVLW 04h                                      |

| 0000          | 6E F6        | MOVWF TBLPTRL                                  |

| 1100          | 8F 8F        | Write 8F8Fh TO 3C0004h to erase entire device. |

|               |              | NOP                                            |

|               |              | Hold PGD low until erase completes.            |

| 0000          | 00 00        |                                                |

| 0000          | 00 00        |                                                |

FIGURE 3-1: BULK ERASE FLOW

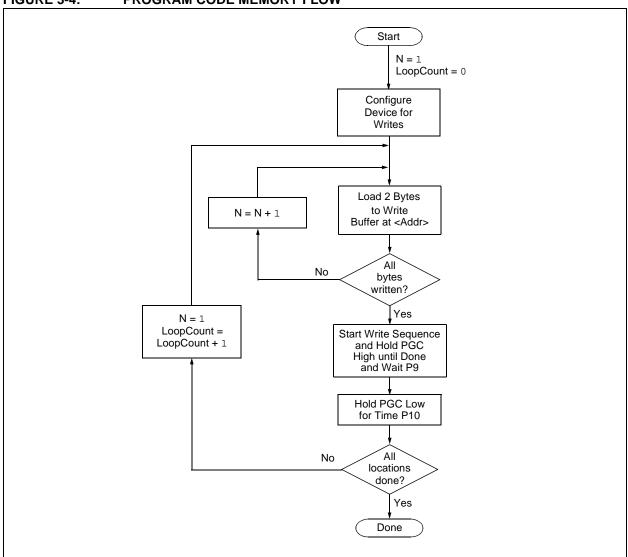

FIGURE 3-4: PROGRAM CODE MEMORY FLOW

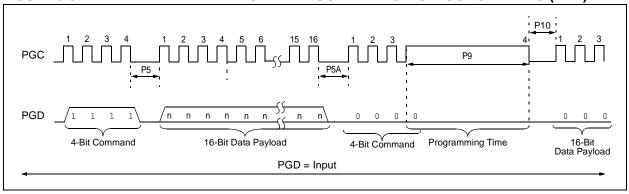

FIGURE 3-5: TABLE WRITE AND START PROGRAMMING INSTRUCTION TIMING (1111)

TABLE 3-7: PROGRAMMING DATA MEMORY

| 4-Bit<br>Command             | Data Payload                                      | Core Instruction                                                   |

|------------------------------|---------------------------------------------------|--------------------------------------------------------------------|

| Step 1: Direct acc           | ess to data EEPROM.                               |                                                                    |

| 0000                         | 9E A6<br>9C A6                                    | BCF EECON1, EEPGD<br>BCF EECON1, CFGS                              |

| Step 2: Set the da           | ata EEPROM Address Pointe                         | er.                                                                |

| 0000<br>0000<br>0000<br>0000 | 0E <addr> 6E A9 0E <addrh> 6E AA</addrh></addr>   | MOVLW <addr> MOVWF EEADR MOVLW <addrh> MOVWF EEADRH</addrh></addr> |

| Step 3: Load the             | data to be written.                               |                                                                    |

| 0000<br>0000                 | OE <data><br/>6E A8</data>                        | MOVLW <data> MOVWF EEDATA</data>                                   |

| Step 4: Enable me            | emory writes.                                     |                                                                    |

| 0000                         | 84 A6                                             | BSF EECON1, WREN                                                   |

| Step 5: Initiate wri         | ite.                                              |                                                                    |

| 0000                         | 82 A6                                             | BSF EECON1, WR                                                     |

| Step 6: Poll WR b            | it, repeat until the bit is clear                 | 1                                                                  |

| 0000<br>0000<br>0000<br>0010 | 50 A6<br>6E F5<br>00 00<br><msb><lsb></lsb></msb> | MOVF EECON1, W, 0 MOVWF TABLAT NOP Shift out data(1)               |

| Step 7: Hold PGC             | low for time P10.                                 |                                                                    |

| Step 8: Disable w            | rites.                                            |                                                                    |

| 0000                         | 94 A6                                             | BCF EECON1, WREN                                                   |

| Repeat Steps 2 th            | rough 8 to write more data.                       |                                                                    |

Note 1: See Figure 4-4 for details on shift out data timing.

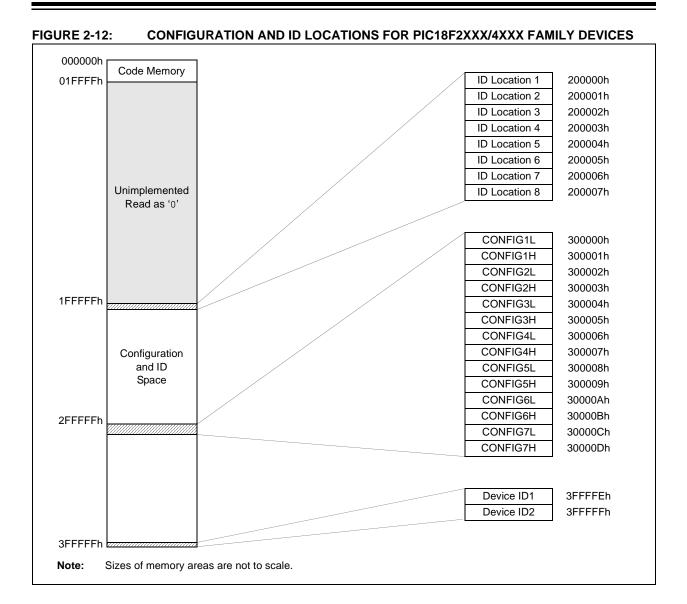

### 3.4 ID Location Programming

The ID locations are programmed much like the code memory. The ID registers are mapped in addresses, 200000h through 200007h. These locations read out normally even after code protection.

Note: The user only needs to fill the first 8 bytes of the write buffer in order to write the ID locations.

Table 3-8 demonstrates the code sequence required to write the ID locations.

In order to modify the ID locations, refer to the methodology described in **Section 3.2.1 "Modifying Code Memory"**. As with code memory, the ID locations must be erased before being modified.

TABLE 3-8: WRITE ID SEQUENCE

| 4-Bit<br>Command                                     | Data Payload                                                                 | Core Instruction                                                                                                                                                                         |

|------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Step 1: Direct acc                                   | ess to code memory and en                                                    | nable writes.                                                                                                                                                                            |

| 0000                                                 | 8E A6<br>9C A6                                                               | BSF EECON1, EEPGD<br>BCF EECON1, CFGS                                                                                                                                                    |

| Step 2: Load write                                   | buffer with 8 bytes and writ                                                 | te.                                                                                                                                                                                      |

| 0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>1101 | 0E 20<br>6E F8<br>0E 00<br>6E F7<br>0E 00<br>6E F6<br><msb><lsb></lsb></msb> | MOVLW 20h MOVWF TBLPTRU MOVLW 00h MOVWF TBLPTRH MOVLW 00h MOVWF TBLPTRL Write 2 bytes and post-increment address by 2.                                                                   |

| 1101<br>1101<br>1111<br>0000                         | <msb><lsb> <msb><lsb> <msb><lsb> 00 00</lsb></msb></lsb></msb></lsb></msb>   | Write 2 bytes and post-increment address by 2. Write 2 bytes and post-increment address by 2. Write 2 bytes and start programming. NOP - hold PGC high for time P9 and low for time P10. |

#### 3.5 Boot Block Programming

The code sequence detailed in Table 3-5 should be used, except that the address used in "Step 2" will be in the range of 000000h to 0007FFh.

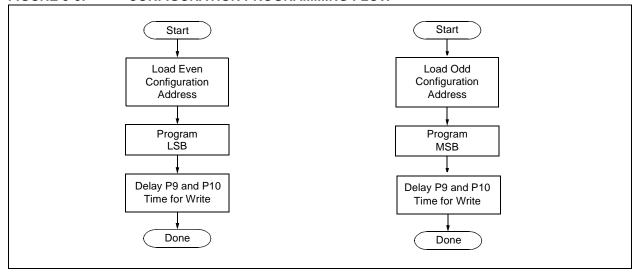

#### 3.6 Configuration Bits Programming

Unlike code memory, the Configuration bits are programmed a byte at a time. The Table Write, Begin Programming 4-bit command ('1111') is used, but only eight bits of the following 16-bit payload will be written. The LSB of the payload will be written to even addresses and the MSB will be written to odd addresses. The code sequence to program two consecutive configuration locations is shown in Table 3-9.

**Note:** The address must be explicitly written for each byte programmed. The addresses can not be incremented in this mode.

TABLE 3-9: SET ADDRESS POINTER TO CONFIGURATION LOCATION

| 4-Bit<br>Command  | Data Payload                      | Core Instruction                                          |

|-------------------|-----------------------------------|-----------------------------------------------------------|

| Step 1: Enable wr | ites and direct access to cor     | nfiguration memory.                                       |

| 0000              | 8E A6<br>8C A6                    | BSF EECON1, EEPGD BSF EECON1, CFGS                        |

|                   |                                   | e to be written. Write even/odd addresses. <sup>(1)</sup> |

| 0000              | 0E 30                             | MOVLW 30h                                                 |

| 0000              | 6E F8                             | MOVWF TBLPTRU                                             |

| 0000              | 0E 00                             | MOVLW 00h                                                 |

| 0000              | 6E F7                             | MOVWF TBLPRTH                                             |

| 0000              | 0E 00                             | MOVLW 00h                                                 |

| 0000              | 6E F6                             | MOVWF TBLPTRL                                             |

| 1111              | <msb ignored=""><lsb></lsb></msb> | Load 2 bytes and start programming.                       |

| 0000              | 00 00                             | NOP - hold PGC high for time P9 and low for time P10.     |

| 0000              | 0E 01                             | MOVLW 01h                                                 |

| 0000              | 6E F6                             | MOVWF TBLPTRL                                             |

| 1111              | <msb><lsb ignored=""></lsb></msb> | Load 2 bytes and start programming.                       |

| 0000              | 00 00                             | NOP - hold PGC high for time P9 and low for time P10.     |

Note 1: Enabling the write protection of Configuration bits (WRTC = 0 in CONFIG6H) will prevent further writing of the Configuration bits. Always write all the Configuration bits before enabling the write protection for Configuration bits.

### FIGURE 3-8: CONFIGURATION PROGRAMMING FLOW

TABLE 5-2: DEVICE ID VALUES

| Device -   | Device ID Value |                          |  |

|------------|-----------------|--------------------------|--|

| Device     | DEVID2          | DEVID1                   |  |

| PIC18F2221 | 21h             | 011x xxxx                |  |

| PIC18F2321 | 21h             | 001x xxxx                |  |

| PIC18F2410 | 11h             | 011x xxxx                |  |

| PIC18F2420 | 11h             | 010x xxxx <sup>(1)</sup> |  |

| PIC18F2423 | 11h             | 010x xxxx <sup>(2)</sup> |  |

| PIC18F2450 | 24h             | 001x xxxx                |  |

| PIC18F2455 | 12h             | 011x xxxx                |  |

| PIC18F2458 | 2Ah             | 011x xxxx                |  |

| PIC18F2480 | 1Ah             | 111x xxxx                |  |

| PIC18F2510 | 11h             | 001x xxxx                |  |

| PIC18F2515 | 0Ch             | 111x xxxx                |  |

| PIC18F2520 | 11h             | 000x xxxx(1)             |  |

| PIC18F2523 | 11h             | 000x xxxx <sup>(2)</sup> |  |

| PIC18F2525 | 0Ch             | 110x xxxx                |  |

| PIC18F2550 | 12h             | 010x xxxx                |  |

| PIC18F2553 | 2Ah             | 010x xxxx                |  |

| PIC18F2580 | 1Ah             | 110x xxxx                |  |

| PIC18F2585 | 0Eh             | 111x xxxx                |  |

| PIC18F2610 | 0Ch             | 101x xxxx                |  |

| PIC18F2620 | 0Ch             | 100x xxxx                |  |

| PIC18F2680 | 0Eh             | 110x xxxx                |  |

| PIC18F2682 | 27h             | 000x xxxx                |  |

| PIC18F2685 | 27h             | 001x xxxx                |  |

| PIC18F4221 | 21h             | 010x xxxx                |  |

| PIC18F4321 | 21h             | 000x xxxx                |  |

| PIC18F4410 | 10h             | 111x xxxx                |  |

| PIC18F4420 | 10h             | 110x xxxx(1)             |  |

| PIC18F4423 | 10h             | 110x xxxx <sup>(2)</sup> |  |

| PIC18F4450 | 24h             | 000x xxxx                |  |

| PIC18F4455 | 12h             | 001x xxxx                |  |

| PIC18F4458 | 2Ah             | 001x xxxx                |  |

| PIC18F4480 | 1Ah             | 101x xxxx                |  |

| PIC18F4510 | 10h             | 101x xxxx                |  |

| PIC18F4515 | 0Ch             | 011x xxxx                |  |

| PIC18F4520 | 10h             | 100x xxxx <sup>(1)</sup> |  |

| PIC18F4523 | 10h             | 100x xxxx <sup>(2)</sup> |  |

| PIC18F4525 | 0Ch             | 010x xxxx                |  |

| PIC18F4550 | 12h             | 000x xxxx                |  |

| PIC18F4553 | 2Ah             | 000x xxxx                |  |

| PIC18F4580 | 1Ah             | 100x xxxx                |  |

**Legend:** The 'x's in DEVID1 contain the device revision code.

**Note 1:** DEVID1 bit 4 is used to determine the device type (REV4 = 0).

**2:** DEVID1 bit 4 is used to determine the device type (REV4 = 1).

| Bit Name    | Configuration Words | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLLDIV<2:0> | CONFIG1L            | Oscillator Selection bits<br>(PIC18F2455/2550/4455/4550, PIC18F2458/2553/4458/4553 and<br>PIC18F2450/4450 devices only)                                                                                                                                                                                                                                                                                                                                             |

|             |                     | Divider must be selected to provide a 4 MHz input into the 96 MHz PLL:  111 = Oscillator divided by 12 (48 MHz input)  110 = Oscillator divided by 10 (40 MHz input)  101 = Oscillator divided by 6 (24 MHz input)  100 = Oscillator divided by 5 (20 MHz input)  011 = Oscillator divided by 4 (16 MHz input)  010 = Oscillator divided by 3 (12 MHz input)  001 = Oscillator divided by 2 (8 MHz input)  000 = No divide - oscillator used directly (4 MHz input) |

| VREGEN      | CONFIG2L            | USB Voltage Regulator Enable bit (PIC18F2455/2550/4455/4550, PIC18F2458/2553/4458/4553 and PIC18F2450/4450 devices only)  1 = USB voltage regulator is enabled 0 = USB voltage regulator is disabled                                                                                                                                                                                                                                                                |

| BORV<1:0>   | CONFIG2L            | Brown-out Reset Voltage bits  11 = VBOR is set to 2.0V  10 = VBOR is set to 2.7V  01 = VBOR is set to 4.2V  00 = VBOR is set to 4.5V                                                                                                                                                                                                                                                                                                                                |

| BOREN<1:0>  | CONFIG2L            | Brown-out Reset Enable bits  11 = Brown-out Reset is enabled in hardware only (SBOREN is disabled)  10 = Brown-out Reset is enabled in hardware only and disabled in Sleep mode SBOREN is disabled)  01 = Brown-out Reset is enabled and controlled by software (SBOREN is enabled)  00 = Brown-out Reset is disabled in hardware and software                                                                                                                      |

| PWRTEN      | CONFIG2L            | Power-up Timer Enable bit  1 = PWRT is disabled  0 = PWRT is enabled                                                                                                                                                                                                                                                                                                                                                                                                |

| WDPS<3:0>   | CONFIG2H            | Watchdog Timer Postscaler Select bits  1111 = 1:32,768  1110 = 1:16,384  1101 = 1:8,192  1100 = 1:4,096  1011 = 1:2,048  1010 = 1:512  1000 = 1:256  0111 = 1:128  0110 = 1:64  0101 = 1:32  0100 = 1:16  0011 = 1:8  0010 = 1:4  0001 = 1:2  0000 = 1:1                                                                                                                                                                                                            |

**Note 1:** The BBSIZ bits, BBSIZ<1:0> and BBSIZ<2:1> bits, cannot be changed once any of the following code-protect bits are enabled: CPB or CP0, WRTB or WRT0, EBTRB or EBTR0.

<sup>2:</sup> Not available in PIC18FXX8X and PIC18F2450/4450 devices.

| Bit Name                  | Configuration Words | Description                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|---------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| WDTEN                     | CONFIG2H            | Watchdog Timer Enable bit  1 = WDT is enabled  0 = WDT is disabled (control is placed on the SWDTEN bit)                                                                                                                |  |  |  |  |  |  |  |

| MCLRE                     | CONFIG3H            | MCLR Pin Enable bit  1 = MCLR pin is enabled, RE3 input pin is disabled  0 = RE3 input pin is enabled, MCLR pin is disabled                                                                                             |  |  |  |  |  |  |  |

| LPT1OSC                   | CONFIG3H            | Low-Power Timer1 Oscillator Enable bit  1 = Timer1 is configured for low-power operation  0 = Timer1 is configured for high-power operation                                                                             |  |  |  |  |  |  |  |

| PBADEN                    | CONFIG3H            | PORTB A/D Enable bit  1 = PORTB A/D<4:0> pins are configured as analog input channels on Reset  0 = PORTB A/D<4:0> pins are configured as digital I/O on Reset                                                          |  |  |  |  |  |  |  |

| PBADEN                    | CONFIG3H            | PORTB A/D Enable bit (PIC18FXX8X devices only)  1 = PORTB A/D<4:0> and PORTB A/D<1:0> pins are configured as analog input channels on Reset  0 = PORTB A/D<4:0> pins are configured as digital I/O on Reset             |  |  |  |  |  |  |  |

| CCP2MX                    | CONFIG3H            | CCP2 MUX bit  1 = CCP2 input/output is multiplexed with RC1 <sup>(2)</sup> 0 = CCP2 input/output is multiplexed with RB3                                                                                                |  |  |  |  |  |  |  |

| DEBUG                     | CONFIG4L            | Background Debugger Enable bit  1 = Background debugger is disabled, RB6 and RB7 are configured as general purpose I/O pins  0 = Background debugger is enabled, RB6 and RB7 are dedicated to In-Circuit Debug          |  |  |  |  |  |  |  |

| XINST                     | CONFIG4L            | Extended Instruction Set Enable bit  1 = Instruction set extension and Indexed Addressing mode are enabled  0 = Instruction set extension and Indexed Addressing mode are disabled  (Legacy mode)                       |  |  |  |  |  |  |  |

| ICPRT                     | CONFIG4L            | Dedicated In-Circuit (ICD/ICSP <sup>TM</sup> ) Port Enable bit (PIC18F2455/2550/4455/4550, PIC18F2458/2553/4458/4553 and PIC18F2450/4450 devices only)  1 = ICPORT is enabled 0 = ICPORT is disabled                    |  |  |  |  |  |  |  |

| BBSIZ<1:0> <sup>(1)</sup> | CONFIG4L            | Boot Block Size Select bits (PIC18F2585/2680/4585/4680 devices only)  11 = 4K words (8 Kbytes) Boot Block  10 = 4K words (8 Kbytes) Boot Block  01 = 2K words (4 Kbytes) Boot Block  00 = 1K word (2 Kbytes) Boot Block |  |  |  |  |  |  |  |

| BBSIZ<2:1> <sup>(1)</sup> | CONFIG4L            | Boot Block Size Select bits (PIC18F2682/2685/4582/4685 devices only)  11 = 4K words (8 Kbytes) Boot Block  10 = 4K words (8 Kbytes) Boot Block  01 = 2K words (4 Kbytes) Boot Block  00 = 1K word (2 Kbytes) Boot Block |  |  |  |  |  |  |  |

**Note 1:** The BBSIZ bits, BBSIZ<1:0> and BBSIZ<2:1> bits, cannot be changed once any of the following code-protect bits are enabled: CPB or CP0, WRTB or WRT0, EBTRB or EBTR0.

<sup>2:</sup> Not available in PIC18FXX8X and PIC18F2450/4450 devices.

| x 5 code memory area) F4685 devices only) rotected cted x 4 code memory area) PIC18F4682/4685 devices only) rotected cted x 3 code memory area) rotected cted cted cted cted |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cted  4 code memory area)  PIC18F4682/4685 devices only)  rotected  cted  3 code memory area)  rotected                                                                      |

| PIC18F4682/4685 devices only) rotected cted c 3 code memory area) rotected                                                                                                   |

| cted  c 3 code memory area) rotected                                                                                                                                         |

| rotected                                                                                                                                                                     |

|                                                                                                                                                                              |

| cted                                                                                                                                                                         |

|                                                                                                                                                                              |

| c 2 code memory area)                                                                                                                                                        |

| rotected<br>cted                                                                                                                                                             |

| c 1 code memory area)                                                                                                                                                        |

| rotected<br>cted                                                                                                                                                             |

| c 0 code memory area)                                                                                                                                                        |

| rotected                                                                                                                                                                     |

| cted                                                                                                                                                                         |

| EEPROM)                                                                                                                                                                      |

| t write-protected<br>ite-protected                                                                                                                                           |

| Block memory area)                                                                                                                                                           |

| re-protected                                                                                                                                                                 |

| rotected                                                                                                                                                                     |

| iguration registers)                                                                                                                                                         |

| rs are not write-protected                                                                                                                                                   |

| rs are write-protected                                                                                                                                                       |

| (Block 5 code memory area)<br>F4685 devices only)                                                                                                                            |

| red from Table Reads executed in other blocks                                                                                                                                |

| rom Table Reads executed in other blocks                                                                                                                                     |

| (Block 4 code memory area) PIC18F4682/4685 devices only)                                                                                                                     |

| red from Table Reads executed in other blocks                                                                                                                                |

| rom Table Reads executed in other blocks                                                                                                                                     |

| (Block 3 code memory area)                                                                                                                                                   |

| ed from Table Reads executed in other blocks                                                                                                                                 |

| from Table Reads executed in other blocks                                                                                                                                    |

| (Block 2 code memory area) red from Table Reads executed in other blocks                                                                                                     |

| from Table Reads executed in other blocks                                                                                                                                    |

| (Block 1 code memory area)                                                                                                                                                   |

| red from Table Reads executed in other blocks from Table Reads executed in other blocks                                                                                      |

|                                                                                                                                                                              |

**Note 1:** The BBSIZ bits, BBSIZ<1:0> and BBSIZ<2:1> bits, cannot be changed once any of the following code-protect bits are enabled: CPB or CP0, WRTB or WRT0, EBTRB or EBTR0.

<sup>2:</sup> Not available in PIC18FXX8X and PIC18F2450/4450 devices.

| Bit Name  | Configuration Words | Description                                                                                                                                                                  |

|-----------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EBTR0     | CONFIG7L            | Table Read Protection bit (Block 0 code memory area)                                                                                                                         |

|           |                     | <ul> <li>1 = Block 0 is not protected from Table Reads executed in other blocks</li> <li>0 = Block 0 is protected from Table Reads executed in other blocks</li> </ul>       |

| EBTRB     | CONFIG7H            | Table Read Protection bit (Boot Block memory area)                                                                                                                           |

|           |                     | <ul> <li>1 = Boot Block is not protected from Table Reads executed in other blocks</li> <li>0 = Boot Block is protected from Table Reads executed in other blocks</li> </ul> |

| DEV<10:3> | DEVID2              | Device ID bits                                                                                                                                                               |

|           |                     | These bits are used with the DEV<2:0> bits in the DEVID1 register to identify part number.                                                                                   |

| DEV<2:0>  | DEVID1              | Device ID bits                                                                                                                                                               |

|           |                     | These bits are used with the DEV<10:3> bits in the DEVID2 register to identify part number.                                                                                  |

| REV<4:0>  | DEVID1              | Revision ID bits                                                                                                                                                             |

|           |                     | These bits are used to indicate the revision of the device. The REV4 bit is sometimes used to fully specify the device type.                                                 |

**Note 1:** The BBSIZ bits, BBSIZ<1:0> and BBSIZ<2:1> bits, cannot be changed once any of the following code-protect bits are enabled: CPB or CP0, WRTB or WRT0, EBTRB or EBTR0.

<sup>2:</sup> Not available in PIC18FXX8X and PIC18F2450/4450 devices.

TABLE 5-4: DEVICE BLOCK LOCATIONS AND SIZES (CONTINUED)

|             | Memory          |        |               |               | End     | ing Addr | Size (Bytes) |         |         |               |         |                     |                 |

|-------------|-----------------|--------|---------------|---------------|---------|----------|--------------|---------|---------|---------------|---------|---------------------|-----------------|

| Device      | Size<br>(Bytes) | Pins   | Boot<br>Block | Block 0       | Block 1 | Block 2  | Block 3      | Block 4 | Block 5 | Boot<br>Block | Block 0 | Remaining<br>Blocks | Device<br>Total |

| PIC18F4455  | 24K             | 40     | 0007FF        | 001FFF        | 003FFF  | 005FFF   | _            | _       | _       | 2048          | 6144    | 16384               | 24576           |

| PIC18F4458  | 24K             | 40     | 0007FF        | 001FFF        | 003FFF  | 005FFF   | _            | _       | _       | 2048          | 6144    | 16384               | 24576           |

| PIC18F4480  | 16K             | 40     | 0007FF        | 001FFF        | 003FFF  |          |              | _       |         | 2048          | 6144    | 8192                | 16384           |

| PIC 18F4480 | ION             |        | 000FFF        |               |         |          | _            |         | _       | 4096          | 4096    |                     | 16384           |

| PIC18F4510  | 32K             | 40     | 0007FF        | 001FFF        | 003FFF  | 005FFF   | 007FFF       | _       | _       | 2048          | 6144    | 24576               | 32768           |

| PIC18F4515  | 48K             | 40     | 0007FF        | 003FFF        | 007FFF  | 00BFFF   | _            | _       | _       | 2048          | 14336   | 32768               | 49152           |

| PIC18F4520  | 32K             | 40     | 0007FF        | 001FFF        | 003FFF  | 005FFF   | 007FFF       | _       | _       | 2048          | 14336   | 16384               | 32768           |

| PIC18F4523  | 32K             | 40     | 0007FF        | 001FFF        | 003FFF  | 005FFF   | 007FFF       | _       | _       | 2048          | 14336   | 16384               | 32768           |

| PIC18F4525  | 48K             | 40     | 0007FF        | 003FFF        | 007FFF  | 00BFFF   | _            | _       | _       | 2048          | 14336   | 32768               | 49152           |

| PIC18F4550  | 32K             | 40     | 0007FF        | 001FFF        | 003FFF  | 005FFF   | 007FFF       | _       | _       | 2048          | 6144    | 24576               | 32768           |

| PIC18F4553  | 32K             | 40     | 0007FF        | 001FFF        | 003FFF  | 005FFF   | 007FFF       | _       | _       | 2048          | 6144    | 24576               | 32768           |

| DIO40E4500  | 32K             | 40     | 0007FF        | 001FFF        | 003FFF  | 005FFF   | 007FFF       | _       | _       | 2048          | 6144    | 24576               | 32768           |

| PIC18F4580  |                 |        | 000FFF        |               |         |          |              |         |         | 4096          | 4096    |                     |                 |

|             | 48K             | 48K 40 | 0007FF        | 003FFF        | 007FFF  | 00BFFF   | FFF —        | _       |         | 2048          | 14336   | 32768               | 49152           |

| PIC18F4585  |                 |        | 000FFF        |               |         |          |              |         |         | 4096          | 12288   |                     |                 |

|             |                 |        | 001FFF        |               |         |          |              |         |         | 8192          | 8192    |                     |                 |

| PIC18F4610  | 64K             | 40     | 0007FF        | 003FFF        | 007FFF  | 00BFFF   | 00FFFF       | _       | _       | 2048          | 14336   | 49152               | 65536           |

| PIC18F4620  | 64K             | 40     | 0007FF        | 003FFF        | 007FFF  | 00BFFF   | 00FFFF       | _       | _       | 2048          | 14336   | 49152               | 65536           |

|             | 64K             | 64K 40 | 0007FF        |               |         |          | 00FFFF       | _       | _       | 2048          | 14336   | 49152               | 65536           |

| PIC18F4680  |                 |        | 000FFF        | 003FFF        | 007FFF  | 00BFFF   |              |         |         | 4096          | 12288   |                     |                 |

|             |                 |        | 001FFF        |               |         |          |              |         |         | 8192          | 8192    |                     |                 |

| PIC18F4682  |                 |        | 0007FF        |               | 007FFF  |          |              | 013FFF  | _       | 2048          | 14336   | 65536               | 81920           |

|             | 80K             | 40     | 000FFF        | 003FFF        |         | 00BFFF   | 00FFFF       |         |         | 4096          | 12288   |                     |                 |

|             |                 |        | 001FFF        |               |         |          |              |         |         | 8192          | 8192    |                     |                 |

|             | 96K             |        | 0007FF        |               |         |          |              |         | 017FFF  | 2048          | 14336   | 81920               | 98304           |

| PIC18F4685  |                 | 44     | 000FFF        | F 003FFF 007F | 007FFF  | F 00BFFF | 00FFFF       | 013FFF  |         | 4096          | 12288   |                     |                 |

|             |                 |        | 001FFF        |               |         |          |              |         |         | 8192          | 8192    |                     |                 |

**Legend:** — = unimplemented.

TABLE 5-5: CONFIGURATION WORD MASKS FOR COMPUTING CHECKSUMS

| TABLE 5-5: | CONFIGURATION WORD MASKS FOR COMPUTING CHECKSUMS  Configuration Word (CONFIGXX) |                   |    |    |    |    |    |    |    |    |    |    |    |    |

|------------|---------------------------------------------------------------------------------|-------------------|----|----|----|----|----|----|----|----|----|----|----|----|

|            | 1L                                                                              | 1H                | 2L | 2H | 3L | 3H | 4L | 4H | 5L | 5H | 6L | 6H | 7L | 7H |

| Device     |                                                                                 | Address (30000xh) |    |    |    |    |    |    |    |    |    |    |    |    |

|            | 0h                                                                              | 1h                | 2h | 3h | 4h | 5h | 6h | 7h | 8h | 9h | Ah | Bh | Ch | Dh |

| PIC18F2221 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | F5 | 00 | 03 | CO | 03 | E0 | 03 | 40 |

| PIC18F2321 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | F5 | 00 | 03 | CO | 03 | E0 | 03 | 40 |

| PIC18F2410 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | C5 | 00 | 03 | C0 | 03 | E0 | 03 | 40 |

| PIC18F2420 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | C5 | 00 | 03 | C0 | 03 | E0 | 03 | 40 |

| PIC18F2423 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | C5 | 00 | 03 | C0 | 03 | E0 | 03 | 40 |

| PIC18F2450 | 3F                                                                              | CF                | 3F | 1F | 00 | 86 | ED | 00 | 03 | 40 | 03 | 60 | 03 | 40 |

| PIC18F2455 | 3F                                                                              | CF                | 3F | 1F | 00 | 87 | E5 | 00 | 07 | C0 | 07 | E0 | 07 | 40 |

| PIC18F2458 | 3F                                                                              | CF                | 3F | 1F | 00 | 87 | E5 | 00 | 07 | C0 | 07 | E0 | 07 | 40 |

| PIC18F2480 | 00                                                                              | CF                | 1F | 1F | 00 | 86 | D5 | 00 | 03 | C0 | 03 | E0 | 03 | 40 |

| PIC18F2510 | 00                                                                              | 1F                | 1F | 1F | 00 | 87 | C5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F2515 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | C5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F2520 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | C5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F2523 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | C5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F2525 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | C5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F2550 | 3F                                                                              | CF                | 3F | 1F | 00 | 87 | E5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F2553 | 3F                                                                              | CF                | 3F | 1F | 00 | 87 | E5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F2580 | 00                                                                              | CF                | 1F | 1F | 00 | 86 | D5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F2585 | 00                                                                              | CF                | 1F | 1F | 00 | 86 | C5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F2610 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | C5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F2620 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | C5 | 00 | 0F | CO | 0F | E0 | 0F | 40 |

| PIC18F2680 | 00                                                                              | CF                | 1F | 1F | 00 | 86 | C5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F2682 | 00                                                                              | CF                | 1F | 1F | 00 | 86 | C5 | 00 | 3F | C0 | 3F | E0 | 3F | 40 |

| PIC18F2685 | 00                                                                              | CF                | 1F | 1F | 00 | 86 | C5 | 00 | 3F | C0 | 3F | E0 | 3F | 40 |

| PIC18F4221 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | F5 | 00 | 03 | C0 | 03 | E0 | 03 | 40 |

| PIC18F4321 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | F5 | 00 | 03 | C0 | 03 | E0 | 03 | 40 |

| PIC18F4410 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | C5 | 00 | 03 | C0 | 03 | E0 | 03 | 40 |

| PIC18F4420 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | C5 | 00 | 03 | C0 | 03 | E0 | 03 | 40 |

| PIC18F4423 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | C5 | 00 | 03 | C0 | 03 | E0 | 03 | 40 |

| PIC18F4450 | 3F                                                                              | CF                | 3F | 1F | 00 | 86 | ED | 00 | 03 | 40 | 03 | 60 | 03 | 40 |

| PIC18F4455 | 3F                                                                              | CF                | 3F | 1F | 00 | 87 | E5 | 00 | 07 | C0 | 07 | E0 | 07 | 40 |

| PIC18F4458 | 3F                                                                              | CF                | 3F | 1F | 00 | 87 | E5 | 00 | 07 | C0 | 07 | E0 | 07 | 40 |

| PIC18F4480 | 00                                                                              | CF                | 1F | 1F | 00 | 86 | D5 | 00 | 03 | C0 | 03 | E0 | 03 | 40 |

| PIC18F4510 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | C5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F4515 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | C5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F4520 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | C5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F4523 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | C5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F4525 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | C5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F4550 | 3F                                                                              | CF                | 3F | 1F | 00 | 87 | E5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F4553 | 3F                                                                              | CF                | 3F | 1F | 00 | 87 | E5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F4580 | 00                                                                              | CF                | 1F | 1F | 00 | 86 | D5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F4585 | 00                                                                              | CF                | 1F | 1F | 00 | 86 | C5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F4610 | 00                                                                              | CF                | 1F | 1F | 00 | 87 | C5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

**Legend:** Shaded cells are unimplemented.