Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 768 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 13x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4410t-i-pt |

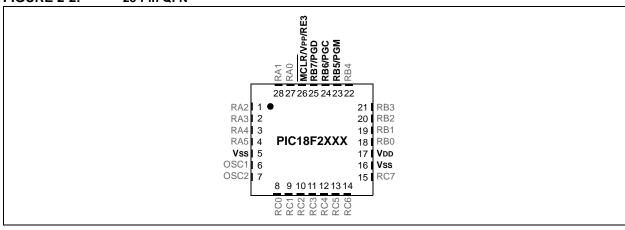

The following devices are included in 28-pin QFN parts:

- PIC18F2221

- PIC18F2423

- PIC18F2510

- PIC18F2580

- PIC18F2321

- PIC18F2450

- PIC18F2520

- PIC18F2682

- PIC18F2410 • PIC18F2420

- PIC18F2480

- PIC18F2523

- PIC18F2685

#### **FIGURE 2-2:** 28-Pin QFN

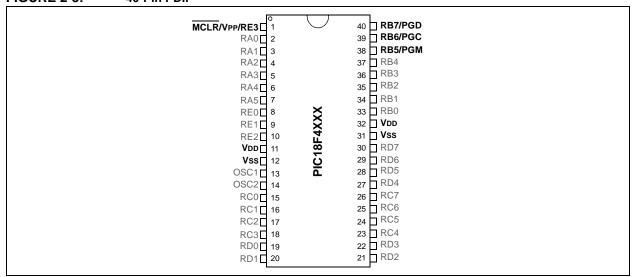

The following devices are included in 40-pin PDIP parts:

- PIC18F4221

- PIC18F4455

- PIC18F4523

- PIC18F4610

- PIC18F4321

- PIC18F4458

- PIC18F4525

- PIC18F4410

- PIC18F4480

- PIC18F4620

- PIC18F4550

- PIC18F4420

- PIC18F4510

- PIC18F4553

- PIC18F4680

- PIC18F4423

- PIC18F4515

- PIC18F4580

- PIC18F4682 PIC18F4685

- PIC18F4450 • PIC18F4520

- PIC18F4585

#### FIGURE 2-3: 40-Pin PDIP

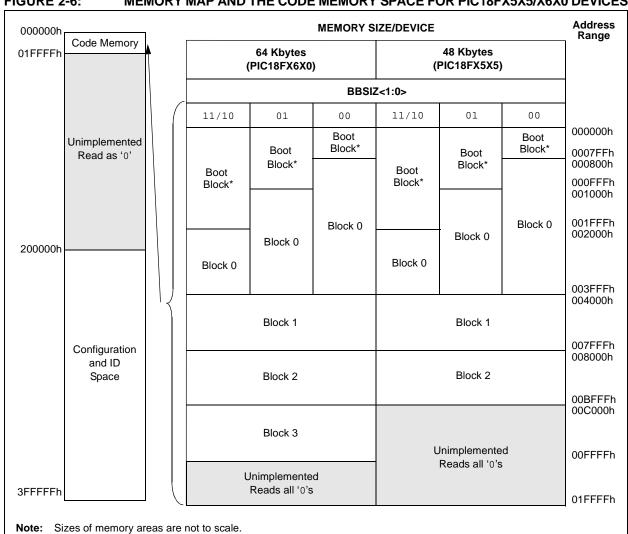

**TABLE 2-2:** IMPLEMENTATION OF CODE MEMORY

| Device     | Code Memory Size (Bytes) |

|------------|--------------------------|

| PIC18F2515 |                          |

| PIC18F2525 |                          |

| PIC18F2585 | 000000h 00DEEEh (40K)    |

| PIC18F4515 | 000000h-00BFFFh (48K)    |

| PIC18F4525 |                          |

| PIC18F4585 | 1                        |

| PIC18F2610 |                          |

| PIC18F2620 |                          |

| PIC18F2680 | 000000h 005555h (64K)    |

| PIC18F4610 | 000000h-00FFFFh (64K)    |

| PIC18F4620 |                          |

| PIC18F4680 |                          |

MEMORY MAP AND THE CODE MEMORY SPACE FOR PIC18FX5X5/X6X0 DEVICES FIGURE 2-6:

Boot Block size is determined by the BBSIZ<1:0> bits in the CONFIG4L register.

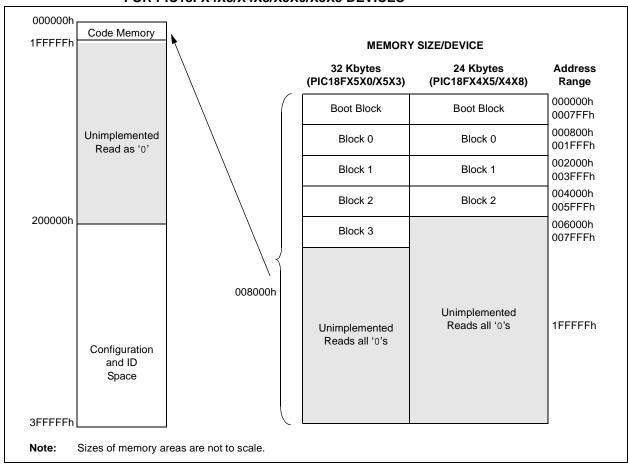

TABLE 2-4: IMPLEMENTATION OF CODE MEMORY

| Device     | Code Memory Size (Bytes) |

|------------|--------------------------|

| PIC18F2455 |                          |

| PIC18F2458 | 000000h 005FFFh (04K)    |

| PIC18F4455 | 000000h-005FFFh (24K)    |

| PIC18F4458 |                          |

| PIC18F2510 |                          |

| PIC18F2520 |                          |

| PIC18F2523 |                          |

| PIC18F2550 |                          |

| PIC18F2553 | 000000h 007FFFh (20K)    |

| PIC18F4510 | 000000h-007FFFh (32K)    |

| PIC18F4520 |                          |

| PIC18F4523 |                          |

| PIC18F4550 |                          |

| PIC18F4553 |                          |

FIGURE 2-8: MEMORY MAP AND THE CODE MEMORY SPACE FOR PIC18FX4X5/X4X8/X5X0/X5X3 DEVICES

For PIC18FX4X0/X4X3 devices, the code memory space extends from 000000h to 003FFh (16 Kbytes) in two 8-Kbyte blocks. Addresses, 000000h through 0003FFh, however, define a "Boot Block" region that is treated separately from Block 0. All of these blocks define code protection boundaries within the code memory space.

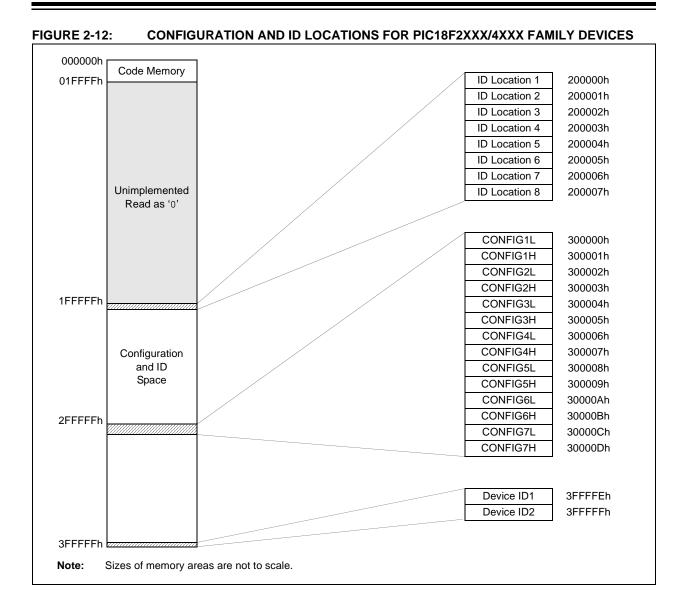

In addition to the code memory space, there are three blocks that are accessible to the user through Table Reads and Table Writes. Their locations in the memory map are shown in Figure 2-12.

Users may store identification information (ID) in eight ID registers. These ID registers are mapped in addresses, 200000h through 200007h. The ID locations read out normally, even after code protection is applied.

Locations, 300000h through 30000Dh, are reserved for the Configuration bits. These bits select various device options and are described in **Section 5.0 "Configuration Word"**. These Configuration bits read out normally, even after code protection.

Locations, 3FFFFEh and 3FFFFFh, are reserved for the Device ID bits. These bits may be used by the programmer to identify what device type is being programmed and are described in **Section 5.0 "Configuration Word"**. These Device ID bits read out normally, even after code protection.

#### 2.3.1 MEMORY ADDRESS POINTER

Memory in the address space, 0000000h to 3FFFFFh, is addressed via the Table Pointer register, which is comprised of three pointer registers:

- TBLPTRU at RAM address 0FF8h

- TBLPTRH at RAM address 0FF7h

- · TBLPTRL at RAM address 0FF6h

| TBLPTRU     | TBLPTRH    | TBLPTRL   |

|-------------|------------|-----------|

| Addr[21:16] | Addr[15:8] | Addr[7:0] |

The 4-bit command, '0000' (core instruction), is used to load the Table Pointer prior to using many read or write operations.

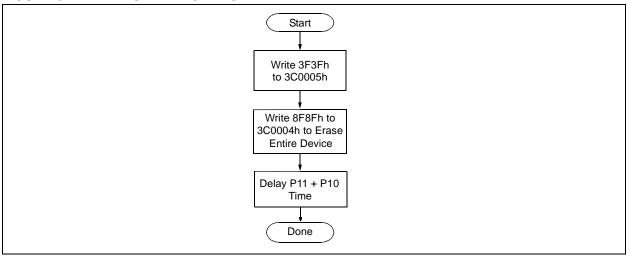

TABLE 3-2: BULK ERASE COMMAND SEQUENCE

| 4-Bit Command | Data Payload | Core Instruction                               |

|---------------|--------------|------------------------------------------------|

| 0000          | 0E 3C        | MOVLW 3Ch                                      |

| 0000          | 6E F8        | MOVWF TBLPTRU                                  |

| 0000          | 0E 00        | MOVLW 00h                                      |

| 0000          | 6E F7        | MOVWF TBLPTRH                                  |

| 0000          | 0E 05        | MOVLW 05h                                      |

| 0000          | 6E F6        | MOVWF TBLPTRL                                  |

| 1100          | 3F 3F        | Write 3F3Fh to 3C0005h                         |

| 0000          | 0E 3C        | MOVLW 3Ch                                      |

| 0000          | 6E F8        | MOVWF TBLPTRU                                  |

| 0000          | 0E 00        | MOVLW 00h                                      |

| 0000          | 6E F7        | MOVWF TBLPTRH                                  |

| 0000          | 0E 04        | MOVLW 04h                                      |

| 0000          | 6E F6        | MOVWF TBLPTRL                                  |

| 1100          | 8F 8F        | Write 8F8Fh TO 3C0004h to erase entire device. |

|               |              | NOP                                            |

|               |              | Hold PGD low until erase completes.            |

| 0000          | 00 00        |                                                |

| 0000          | 00 00        |                                                |

FIGURE 3-1: BULK ERASE FLOW

#### 3.1.2 LOW-VOLTAGE ICSP BULK ERASE

When using low-voltage ICSP, the part must be supplied by the voltage specified in Parameter D111 if a Bulk Erase is to be executed. All other Bulk Erase details, as described above, apply.

If it is determined that a program memory erase must be performed at a supply voltage below the Bulk Erase limit, refer to the erase methodology described in **Section 3.1.3** "**ICSP Row Erase**" and **Section 3.2.1** "**Modifying Code Memory**".

If it is determined that a data EEPROM erase (selected devices only, see **Section 3.3 "Data EEPROM Programming"**) must be performed at a supply voltage below the Bulk Erase limit, follow the methodology described in **Section 3.3 "Data EEPROM Programming"** and write '1's to the array.

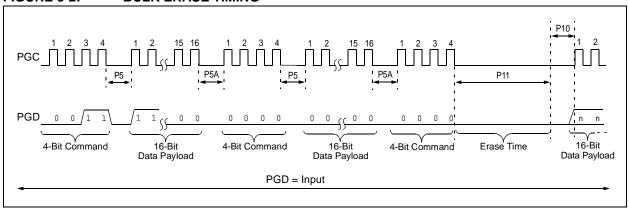

FIGURE 3-2: BULK ERASE TIMING

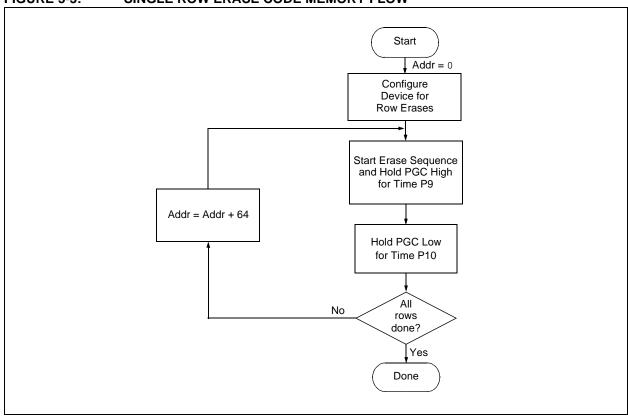

#### 3.1.3 ICSP ROW ERASE

Regardless of whether high or low-voltage ICSP is used, it is possible to erase one row (64 bytes of data), provided the block is not code or write-protected. Rows are located at static boundaries, beginning at program memory address, 000000h, extending to the internal program memory limit (see **Section 2.3 "Memory Maps"**).

The Row Erase duration is externally timed and is controlled by PGC. After the WR bit in EECON1 is set, a NOP is issued, where the 4th PGC is held high for the duration of the programming time, P9.

After PGC is brought low, the programming sequence is terminated. PGC must be held low for the time specified by Parameter P10 to allow high-voltage discharge of the memory array.

The code sequence to Row Erase a PIC18F2XXX/4XXX Family device is shown in Table 3-3. The flowchart, shown in Figure 3-3, depicts the logic necessary to completely erase a PIC18F2XXX/4XXX Family device. The timing diagram that details the Start Programming command and Parameters P9 and P10 is shown in Figure 3-5.

**Note:** The TBLPTR register can point to any byte within the row intended for erase.

TABLE 3-3: ERASE CODE MEMORY CODE SEQUENCE

| Step 1: Direct access to code memory and enable writes.           0000         8E A6         BSF EECON1, EEPGD           0000         9C A6         BCF EECON1, CFGS           0000         84 A6         BSF EECON1, WREN           Step 2: Point to first row in code memory.           0000         6A F8         CLRF TBLPTRU           0000         6A F7         CLRF TBLPTRH           0000         6A F6         CLRF TBLPTRL           Step 3: Enable erase and erase single row.           0000         88 A6         BSF EECON1, FREE           0000         82 A6         BSF EECON1, WR           0000         00 00         NOP - hold PGC high for time P9 and low for time P10. | 4-Bit<br>Command   | Data Payload             | Core Instruction |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------|------------------|

| 0000         9C A6         BCF         EECON1, CFGS           0000         84 A6         BSF         EECON1, WREN           Step 2: Point to first row in code memory.           0000         6A F8         CLRF         TBLPTRU           0000         6A F7         CLRF         TBLPTRH           0000         6A F6         CLRF         TBLPTRL           Step 3: Enable erase and erase single row.           0000         88 A6         BSF         EECON1, FREE           0000         82 A6         BSF         EECON1, WR                                                                                                                                                             | Step 1: Direct ac  | cess to code memory an   | d enable writes. |

| 0000 6A F8 CLRF TBLPTRU 0000 6A F7 CLRF TBLPTRH 0000 6A F6 CLRF TBLPTRL  Step 3: Enable erase and erase single row.  0000 88 A6 BSF EECON1, FREE 0000 82 A6 BSF EECON1, WR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0000               | 9C A6                    | BCF EECON1, CFGS |

| 0000         6A F7         CLRF TBLPTRH           0000         6A F6         CLRF TBLPTRL           Step 3: Enable erase and erase single row.           0000         88 A6         BSF EECON1, FREE           0000         82 A6         BSF EECON1, WR                                                                                                                                                                                                                                                                                                                                                                                                                                        | Step 2: Point to f | irst row in code memory. |                  |

| 0000 88 A6 BSF EECON1, FREE<br>0000 82 A6 BSF EECON1, WR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0000               | 6A F7                    | CLRF TBLPTRH     |

| 0000 82 A6 BSF EECON1, WR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Step 3: Enable e   | rase and erase single ro | w.               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0000               | 82 A6                    | BSF EECON1, WR   |

#### FIGURE 3-3: SINGLE ROW ERASE CODE MEMORY FLOW

### 3.2 Code Memory Programming

Programming code memory is accomplished by first loading data into the write buffer and then initiating a programming sequence. The write and erase buffer sizes, shown in Table 3-4, can be mapped to any location of the same size, beginning at 000000h. The actual memory write sequence takes the contents of this buffer and programs the proper amount of code memory that contains the Table Pointer.

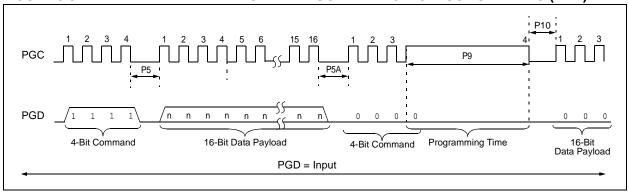

The programming duration is externally timed and is controlled by PGC. After a Start Programming command is issued (4-bit command, '1111'), a NOP is issued, where the 4th PGC is held high for the duration of the programming time, P9.

After PGC is brought low, the programming sequence is terminated. PGC must be held low for the time specified by Parameter P10 to allow high-voltage discharge of the memory array.

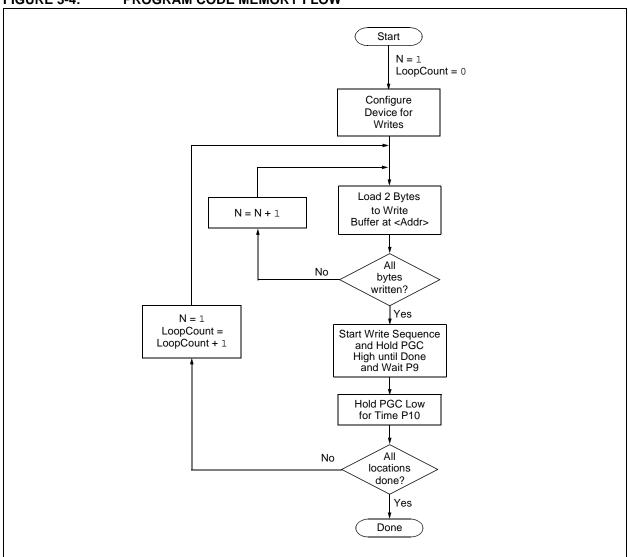

The code sequence to program a PIC18F2XXX/4XXX Family device is shown in Table 3-5. The flowchart, shown in Figure 3-4, depicts the logic necessary to completely write a PIC18F2XXX/4XXX Family device. The timing diagram that details the Start Programming command and Parameters P9 and P10 is shown in Figure 3-5.

**Note:** The TBLPTR register must point to the same region when initiating the programming sequence as it did when the write buffers were loaded.

TABLE 3-4: WRITE AND ERASE BUFFER SIZES

| Devices (Arranged by Family)                   | Write Buffer Size (Bytes) | Erase Buffer Size (Bytes) |

|------------------------------------------------|---------------------------|---------------------------|

| PIC18F2221, PIC18F2321, PIC18F4221, PIC18F4321 | 8                         | 64                        |

| PIC18F2450, PIC18F4450                         | 16                        | 64                        |

| PIC18F2410, PIC18F2510, PIC18F4410, PIC18F4510 |                           |                           |

| PIC18F2420, PIC18F2520, PIC18F4420, PIC18F4520 |                           |                           |

| PIC18F2423, PIC18F2523, PIC18F4423, PIC18F4523 | 32                        | 64                        |

| PIC18F2480, PIC18F2580, PIC18F4480, PIC18F4580 | 32                        | 04                        |

| PIC18F2455, PIC18F2550, PIC18F4455, PIC18F4550 |                           |                           |

| PIC18F2458, PIC18F2553, PIC18F4458, PIC18F4553 |                           |                           |

| PIC18F2515, PIC18F2610, PIC18F4515, PIC18F4610 |                           |                           |

| PIC18F2525, PIC18F2620, PIC18F4525, PIC18F4620 | 64                        | 64                        |

| PIC18F2585, PIC18F2680, PIC18F4585, PIC18F4680 | - 64                      | 64                        |

| PIC18F2682, PIC18F2685, PIC18F4682, PIC18F4685 |                           |                           |

FIGURE 3-4: PROGRAM CODE MEMORY FLOW

FIGURE 3-5: TABLE WRITE AND START PROGRAMMING INSTRUCTION TIMING (1111)

#### 4.0 READING THE DEVICE

### 4.1 Read Code Memory, ID Locations and Configuration Bits

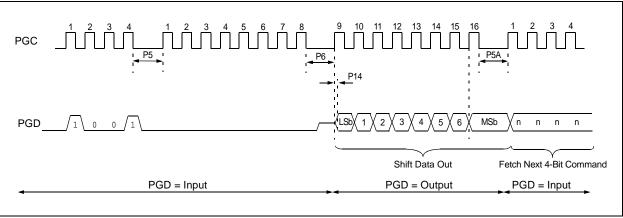

Code memory is accessed, one byte at a time, via the 4-bit command, '1001' (Table Read, post-increment). The contents of memory pointed to by the Table Pointer (TBLPTRU:TBLPTRH) are serially output on PGD.

The 4-bit command is shifted in, LSb first. The read is executed during the next eight clocks, then shifted out on PGD during the last eight clocks, LSb to MSb. A delay of P6 must be introduced after the falling edge of the 8th PGC of the operand to allow PGD to transition from an input to an output. During this time, PGC must be held low (see Figure 4-1). This operation also increments the Table Pointer by one, pointing to the next byte in code memory for the next read.

This technique will work to read any memory in the 000000h to 3FFFFFh address space, so it also applies to the reading of the ID and Configuration registers.

TABLE 4-1: READ CODE MEMORY SEQUENCE

| 4-Bit<br>Command  | Data Payload                                               | Core Instruction                |  |

|-------------------|------------------------------------------------------------|---------------------------------|--|

| Step 1: Set Table | Pointer.                                                   |                                 |  |

| 0000              | OE <addr[21:16]></addr[21:16]>                             | MOVLW Addr[21:16]               |  |

| 0000              | 6E F8                                                      | MOVWF TBLPTRU                   |  |

| 0000              | 0E <addr[15:8]></addr[15:8]>                               | MOVLW <addr[15:8]></addr[15:8]> |  |

| 0000              | 6E F7                                                      | MOVWF TBLPTRH                   |  |

| 0000              | 0E <addr[7:0]></addr[7:0]>                                 | MOVLW <addr[7:0]></addr[7:0]>   |  |

| 0000              | 6E F6                                                      | MOVWF TBLPTRL                   |  |

| Step 2: Read mer  | Step 2: Read memory and then shift out on PGD, LSb to MSb. |                                 |  |

| 1001              | 00 00                                                      | TBLRD *+                        |  |

#### 5.0 CONFIGURATION WORD

The PIC18F2XXX/4XXX Family devices have several Configuration Words. These bits can be set or cleared to select various device configurations. All other memory areas should be programmed and verified prior to setting the Configuration Words. These bits may be read out normally, even after read or code protection. See Table 5-1 for a list of Configuration bits and Device IDs, and Table 5-3 for the Configuration bit descriptions.

#### 5.1 ID Locations

A user may store identification information (ID) in eight ID locations, mapped in 200000h:200007h. It is recommended that the Most Significant nibble of each ID be Fh. In doing so, if the user code inadvertently tries to execute from the ID space, the ID data will execute as a NOP.

#### 5.2 Device ID Word

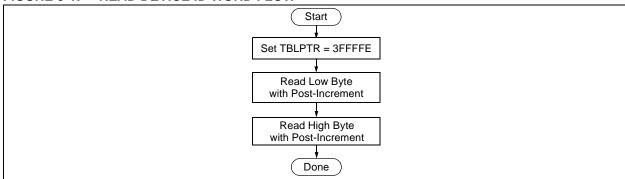

The Device ID Word for the PIC18F2XXX/4XXX Family devices is located at 3FFFFEh:3FFFFh. These bits may be used by the programmer to identify what device type is being programmed and read out normally, even after code or read protection.

In some cases, devices may share the same DEVID values. In such cases, the Most Significant bit of the device revision, REV4 (DEVID1<4>), will need to be examined to completely determine the device being accessed.

See Table 5-2 for a complete list of Device ID values.

FIGURE 5-1: READ DEVICE ID WORD FLOW

TABLE 5-2: DEVICE ID VALUES

| Device -   | Device | e ID Value               |

|------------|--------|--------------------------|

| Device     | DEVID2 | DEVID1                   |

| PIC18F2221 | 21h    | 011x xxxx                |

| PIC18F2321 | 21h    | 001x xxxx                |

| PIC18F2410 | 11h    | 011x xxxx                |

| PIC18F2420 | 11h    | 010x xxxx <sup>(1)</sup> |

| PIC18F2423 | 11h    | 010x xxxx <sup>(2)</sup> |

| PIC18F2450 | 24h    | 001x xxxx                |

| PIC18F2455 | 12h    | 011x xxxx                |

| PIC18F2458 | 2Ah    | 011x xxxx                |

| PIC18F2480 | 1Ah    | 111x xxxx                |

| PIC18F2510 | 11h    | 001x xxxx                |

| PIC18F2515 | 0Ch    | 111x xxxx                |

| PIC18F2520 | 11h    | 000x xxxx(1)             |

| PIC18F2523 | 11h    | 000x xxxx <sup>(2)</sup> |

| PIC18F2525 | 0Ch    | 110x xxxx                |

| PIC18F2550 | 12h    | 010x xxxx                |

| PIC18F2553 | 2Ah    | 010x xxxx                |

| PIC18F2580 | 1Ah    | 110x xxxx                |

| PIC18F2585 | 0Eh    | 111x xxxx                |

| PIC18F2610 | 0Ch    | 101x xxxx                |

| PIC18F2620 | 0Ch    | 100x xxxx                |

| PIC18F2680 | 0Eh    | 110x xxxx                |

| PIC18F2682 | 27h    | 000x xxxx                |

| PIC18F2685 | 27h    | 001x xxxx                |

| PIC18F4221 | 21h    | 010x xxxx                |

| PIC18F4321 | 21h    | 000x xxxx                |

| PIC18F4410 | 10h    | 111x xxxx                |

| PIC18F4420 | 10h    | 110x xxxx(1)             |

| PIC18F4423 | 10h    | 110x xxxx <sup>(2)</sup> |

| PIC18F4450 | 24h    | 000x xxxx                |

| PIC18F4455 | 12h    | 001x xxxx                |

| PIC18F4458 | 2Ah    | 001x xxxx                |

| PIC18F4480 | 1Ah    | 101x xxxx                |

| PIC18F4510 | 10h    | 101x xxxx                |

| PIC18F4515 | 0Ch    | 011x xxxx                |

| PIC18F4520 | 10h    | 100x xxxx <sup>(1)</sup> |

| PIC18F4523 | 10h    | 100x xxxx <sup>(2)</sup> |

| PIC18F4525 | 0Ch    | 010x xxxx                |

| PIC18F4550 | 12h    | 000x xxxx                |

| PIC18F4553 | 2Ah    | 000x xxxx                |

| PIC18F4580 | 1Ah    | 100x xxxx                |

**Legend:** The 'x's in DEVID1 contain the device revision code.

**Note 1:** DEVID1 bit 4 is used to determine the device type (REV4 = 0).

**2:** DEVID1 bit 4 is used to determine the device type (REV4 = 1).

TABLE 5-2: DEVICE ID VALUES (CONTINUED)

| Device     | Device ID Value |           |  |

|------------|-----------------|-----------|--|

| Device     | DEVID2          | DEVID1    |  |

| PIC18F4585 | 0Eh             | 101x xxxx |  |

| PIC18F4610 | 0Ch             | 001x xxxx |  |

| PIC18F4620 | 0Ch             | 000x xxxx |  |

| PIC18F4680 | 0Eh             | 100x xxxx |  |

| PIC18F4682 | 27h             | 010x xxxx |  |

| PIC18F4685 | 27h             | 011x xxxx |  |

**Legend:** The 'x's in DEVID1 contain the device revision code.

**Note 1:** DEVID1 bit 4 is used to determine the device type (REV4 = 0).

2: DEVID1 bit 4 is used to determine the device type (REV4 = 1).

TABLE 5-3: PIC18F2XXX/4XXX FAMILY BIT DESCRIPTIONS

| Bit Name    | Configuration Words | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IESO        | CONFIG1H            | Internal External Switchover bit  1 = Internal External Switchover mode is enabled  0 = Internal External Switchover mode is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FCMEN       | CONFIG1H            | Fail-Safe Clock Monitor Enable bit  1 = Fail-Safe Clock Monitor is enabled  0 = Fail-Safe Clock Monitor is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FOSC<3:0>   | CONFIG1H            | Oscillator Selection bits  11xx = External RC oscillator, CLKO function on RA6  101x = External RC oscillator, CLKO function on RA6  1001 = Internal RC oscillator, CLKO function on RA6, port function on RA7  1000 = Internal RC oscillator, port function on RA6, port function on RA7  0111 = External RC oscillator, port function on RA6  0110 = HS oscillator, PLL is enabled (Clock Frequency = 4 x FOSC1)  0101 = EC oscillator, port function on RA6  0100 = EC oscillator, CLKO function on RA6  0011 = External RC oscillator, CLKO function on RA6  0010 = HS oscillator  0001 = XT oscillator  0000 = LP oscillator                                                                                                                                                                                                              |

| FOSC<3:0>   | CONFIG1H            | Oscillator Selection bits (PIC18F2455/2550/4455/4550, PIC18F2458/2553/4458/4553 and PIC18F2450/4450 devices only)  111x = HS oscillator, PLL is enabled, HS is used by USB 110x = HS oscillator, HS is used by USB 1011 = Internal oscillator, HS is used by USB 1010 = Internal oscillator, XT is used by USB 1001 = Internal oscillator, CLKO function on RA6, EC is used by USB 1000 = Internal oscillator, port function on RA6, EC is used by USB 0111 = EC oscillator, PLL is enabled, CLKO function on RA6, EC is used by USB 0110 = EC oscillator, PLL is enabled, port function on RA6, EC is used by USB 0101 = EC oscillator, CLKO function on RA6, EC is used by USB 0100 = EC oscillator, port function on RA6, EC is used by USB 010x = XT oscillator, PLL is enabled, XT is used by USB 000x = XT oscillator, XT is used by USB |

| USBDIV      | CONFIG1L            | USB Clock Selection bit (PIC18F2455/2550/4455/4550, PIC18F2458/2553/4458/4553 and PIC18F2450/4450 devices only) Selects the clock source for full-speed USB operation:  1 = USB clock source comes from the 96 MHz PLL divided by 2  0 = USB clock source comes directly from the OSC1/OSC2 oscillator block; no divide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CPUDIV<1:0> | CONFIG1L            | CPU System Clock Selection bits (PIC18F2455/2550/4455/4550, PIC18F2458/2553/4458/4553 and PIC18F2450/4450 devices only)  11 = CPU system clock divided by 4  10 = CPU system clock divided by 3  01 = CPU system clock divided by 2  00 = No CPU system clock divide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

**Note 1:** The BBSIZ bits, BBSIZ<1:0> and BBSIZ<2:1> bits, cannot be changed once any of the following code-protect bits are enabled: CPB or CP0, WRTB or WRT0, EBTRB or EBTR0.

2: Not available in PIC18FXX8X and PIC18F2450/4450 devices.

TABLE 5-3: PIC18F2XXX/4XXX FAMILY BIT DESCRIPTIONS (CONTINUED)

| Bit Name                  | Configuration<br>Words | Description                                                                                                                                                                                                      |

|---------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BBSIZ<1:0> <sup>(1)</sup> | CONFIG4L               | Boot Block Size Select bits (PIC18F2321/4321 devices only)  11 = 1K word (2 Kbytes) Boot Block  10 = 1K word (2 Kbytes) Boot Block  01 = 512 words (1 Kbyte) Boot Block  00 = 256 words (512 bytes) Boot Block   |

|                           |                        | Boot Block Size Select bits (PIC18F2221/4221 devices only)  11 = 512 words (1 Kbyte) Boot Block  10 = 512 words (1 Kbyte) Boot Block  01 = 512 words (1 Kbyte) Boot Block  00 = 256 words (512 bytes) Boot Block |

| BBSIZ <sup>(1)</sup>      | CONFIG4L               | Boot Block Size Select bits (PIC18F2480/2580/4480/4580 and PIC18F2450/4450 devices only)  1 = 2K words (4 Kbytes) Boot Block 0 = 1K word (2 Kbytes) Boot Block                                                   |

| LVP                       | CONFIG4L               | Low-Voltage Programming Enable bit  1 = Low-Voltage Programming is enabled, RB5 is the PGM pin  0 = Low-Voltage Programming is disabled, RB5 is an I/O pin                                                       |

| STVREN                    | CONFIG4L               | Stack Overflow/Underflow Reset Enable bit  1 = Reset on stack overflow/underflow is enabled  0 = Reset on stack overflow/underflow is disabled                                                                   |

| CP5                       | CONFIG5L               | Code Protection bit (Block 5 code memory area) (PIC18F2685 and PIC18F4685 devices only)  1 = Block 5 is not code-protected 0 = Block 5 is code-protected                                                         |

| CP4                       | CONFIG5L               | Code Protection bit (Block 4 code memory area) (PIC18F2682/2685 and PIC18F4682/4685 devices only)  1 = Block 4 is not code-protected 0 = Block 4 is code-protected                                               |

| CP3                       | CONFIG5L               | Code Protection bit (Block 3 code memory area)  1 = Block 3 is not code-protected  0 = Block 3 is code-protected                                                                                                 |

| CP2                       | CONFIG5L               | Code Protection bit (Block 2 code memory area)  1 = Block 2 is not code-protected  0 = Block 2 is code-protected                                                                                                 |

| CP1                       | CONFIG5L               | Code Protection bit (Block 1 code memory area)  1 = Block 1 is not code-protected  0 = Block 1 is code-protected                                                                                                 |

| CP0                       | CONFIG5L               | Code Protection bit (Block 0 code memory area)  1 = Block 0 is not code-protected  0 = Block 0 is code-protected                                                                                                 |

| CPD                       | CONFIG5H               | Code Protection bit (Data EEPROM)  1 = Data EEPROM is not code-protected  0 = Data EEPROM is code-protected                                                                                                      |

| СРВ                       | CONFIG5H               | Code Protection bit (Boot Block memory area)  1 = Boot Block is not code-protected  0 = Boot Block is code-protected                                                                                             |

**Note 1:** The BBSIZ bits, BBSIZ<1:0> and BBSIZ<2:1> bits, cannot be changed once any of the following code-protect bits are enabled: CPB or CP0, WRTB or WRT0, EBTRB or EBTR0.

<sup>2:</sup> Not available in PIC18FXX8X and PIC18F2450/4450 devices.

TABLE 5-4: DEVICE BLOCK LOCATIONS AND SIZES (CONTINUED)

|             | Memory          |      | Ending Address |         |         |         |         |         |         |               | Size (Bytes) |                     |                 |  |  |

|-------------|-----------------|------|----------------|---------|---------|---------|---------|---------|---------|---------------|--------------|---------------------|-----------------|--|--|

| Device      | Size<br>(Bytes) | Pins | Boot<br>Block  | Block 0 | Block 1 | Block 2 | Block 3 | Block 4 | Block 5 | Boot<br>Block | Block 0      | Remaining<br>Blocks | Device<br>Total |  |  |

| PIC18F4455  | 24K             | 40   | 0007FF         | 001FFF  | 003FFF  | 005FFF  | _       | _       | _       | 2048          | 6144         | 16384               | 24576           |  |  |

| PIC18F4458  | 24K             | 40   | 0007FF         | 001FFF  | 003FFF  | 005FFF  | _       | _       | _       | 2048          | 6144         | 16384               | 24576           |  |  |

| PIC18F4480  | 401/            | 40   | 0007FF         | 001FFF  | 003FFF  | 1       | 1       | _       |         | 2048          | 6144         | 8192                | 40004           |  |  |

| PIC 18F4480 | 16K             | 40   | 000FFF         |         |         |         |         |         | _       | 4096          | 4096         |                     | 16384           |  |  |

| PIC18F4510  | 32K             | 40   | 0007FF         | 001FFF  | 003FFF  | 005FFF  | 007FFF  | _       | _       | 2048          | 6144         | 24576               | 32768           |  |  |

| PIC18F4515  | 48K             | 40   | 0007FF         | 003FFF  | 007FFF  | 00BFFF  | _       | _       | _       | 2048          | 14336        | 32768               | 49152           |  |  |

| PIC18F4520  | 32K             | 40   | 0007FF         | 001FFF  | 003FFF  | 005FFF  | 007FFF  | _       | _       | 2048          | 14336        | 16384               | 32768           |  |  |

| PIC18F4523  | 32K             | 40   | 0007FF         | 001FFF  | 003FFF  | 005FFF  | 007FFF  | _       | _       | 2048          | 14336        | 16384               | 32768           |  |  |

| PIC18F4525  | 48K             | 40   | 0007FF         | 003FFF  | 007FFF  | 00BFFF  | _       | _       | _       | 2048          | 14336        | 32768               | 49152           |  |  |

| PIC18F4550  | 32K             | 40   | 0007FF         | 001FFF  | 003FFF  | 005FFF  | 007FFF  | _       | _       | 2048          | 6144         | 24576               | 32768           |  |  |

| PIC18F4553  | 32K             | 40   | 0007FF         | 001FFF  | 003FFF  | 005FFF  | 007FFF  | _       | _       | 2048          | 6144         | 24576               | 32768           |  |  |

| PIC18F4580  | 32K             | 40   | 0007FF         | 001FFF  | 003FFF  | 005FFF  | 007FFF  | _       | _       | 2048          | 6144         | 24576               | 32768           |  |  |

| PIC 10F4500 |                 |      | 000FFF         |         |         |         |         |         |         | 4096          | 4096         |                     |                 |  |  |

|             | 48K             |      | 0007FF         | 003FFF  | 007FFF  | 00BFFF  | _       | _       | _       | 2048          | 14336        | 32768               | 49152           |  |  |

| PIC18F4585  |                 | 40   | 000FFF         |         |         |         |         |         |         | 4096          | 12288        |                     |                 |  |  |

|             |                 |      | 001FFF         |         |         |         |         |         |         | 8192          | 8192         |                     |                 |  |  |

| PIC18F4610  | 64K             | 40   | 0007FF         | 003FFF  | 007FFF  | 00BFFF  | 00FFFF  | _       | _       | 2048          | 14336        | 49152               | 65536           |  |  |

| PIC18F4620  | 64K             | 40   | 0007FF         | 003FFF  | 007FFF  | 00BFFF  | 00FFFF  | _       | _       | 2048          | 14336        | 49152               | 65536           |  |  |

|             |                 |      | 0007FF         |         |         |         |         | _       |         | 2048          | 14336        | 49152               | 65536           |  |  |

| PIC18F4680  | 64K             | 40   | 000FFF         | 003FFF  | 007FFF  | 00BFFF  | 00FFFF  |         |         | 4096          | 12288        |                     |                 |  |  |

|             |                 |      | 001FFF         |         |         |         |         |         |         | 8192          | 8192         |                     |                 |  |  |

| PIC18F4682  |                 |      | 0007FF         |         |         |         |         | 013FFF  | _       | 2048          | 14336        | 65536               | 81920           |  |  |

|             | 80K             | 40   | 000FFF         | 003FFF  | 007FFF  | 00BFFF  | 00FFFF  |         |         | 4096          | 12288        |                     |                 |  |  |

|             |                 |      | 001FFF         |         |         |         |         |         |         | 8192          | 8192         |                     |                 |  |  |

|             |                 |      | 0007FF         |         |         |         |         | 013FFF  | 017FFF  | 2048          | 14336        |                     | 98304           |  |  |

| PIC18F4685  | 96K             | 44   | 000FFF         | 003FFF  | 007FFF  | 00BFFF  | 00FFFF  |         |         | 4096          | 12288        | 81920               |                 |  |  |

|             |                 |      | 001FFF         |         |         |         |         |         |         | 8192          | 8192         |                     |                 |  |  |

**Legend:** — = unimplemented.

TABLE 5-5: CONFIGURATION WORD MASKS FOR COMPUTING CHECKSUMS

| <b>TABLE 5-5:</b>        | -5: CONFIGURATION WORD MASKS FOR COMPUTING CHECKSUMS |            |          |          |    |          |          |      |          |          |          |          |          |          |

|--------------------------|------------------------------------------------------|------------|----------|----------|----|----------|----------|------|----------|----------|----------|----------|----------|----------|

|                          | Configuration Word (CONFIGxx)                        |            |          |          |    |          |          |      |          |          |          |          |          |          |

| Davisa                   | 1L                                                   | 1H         | 2L       | 2H       | 3L | 3H       | 4L       | 4H   | 5L       | 5H       | 6L       | 6H       | 7L       | 7H       |

| Device                   | Address (30000xh)                                    |            |          |          |    |          |          |      |          |          |          |          |          |          |

|                          | 0h                                                   | 1h         | 2h       | 3h       | 4h | 5h       | 6h       | 7h   | 8h       | 9h       | Ah       | Bh       | Ch       | Dh       |

| PIC18F2221               | 00                                                   | CF         | 1F       | 1F       | 00 | 87       | F5       | 00   | 03       | C0       | 03       | E0       | 03       | 40       |

| PIC18F2321               | 00                                                   | CF         | 1F       | 1F       | 00 | 87       | F5       | 00   | 03       | C0       | 03       | E0       | 03       | 40       |

| PIC18F2410               | 00                                                   | CF         | 1F       | 1F       | 00 | 87       | C5       | 00   | 03       | C0       | 03       | E0       | 03       | 40       |

| PIC18F2420               | 00                                                   | CF         | 1F       | 1F       | 00 | 87       | C5       | 00   | 03       | C0       | 03       | E0       | 03       | 40       |

| PIC18F2423               | 00                                                   | CF         | 1F       | 1F       | 00 | 87       | C5       | 00   | 03       | C0       | 03       | E0       | 03       | 40       |

| PIC18F2450               | 3F                                                   | CF         | 3F       | 1F       | 00 | 86       | ED       | 00   | 03       | 40       | 03       | 60       | 03       | 40       |

| PIC18F2455               | 3F                                                   | CF         | 3F       | 1F       | 00 | 87       | E5       | 00   | 07       | C0       | 07       | E0       | 07       | 40       |

| PIC18F2458               | 3F                                                   | CF         | 3F       | 1F       | 00 | 87       | E5       | 00   | 07       | C0       | 07       | E0       | 07       | 40       |

| PIC18F2480               | 00                                                   | CF         | 1F       | 1F       | 00 | 86       | D5       | 00   | 03       | C0       | 03       | E0       | 03       | 40       |

| PIC18F2510               | 00                                                   | 1F         | 1F       | 1F       | 00 | 87       | C5       | 00   | 0F       | C0       | 0F       | E0       | 0F       | 40       |

| PIC18F2515               | 00                                                   | CF         | 1F       | 1F       | 00 | 87       | C5       | 00   | 0F       | C0       | 0F       | E0       | 0F       | 40       |

| PIC18F2520               | 00                                                   | CF         | 1F       | 1F       | 00 | 87       | C5       | 00   | 0F       | C0       | 0F       | E0       | 0F       | 40       |

| PIC18F2523               | 00                                                   | CF         | 1F       | 1F       | 00 | 87       | C5       | 00   | 0F       | C0       | 0F       | E0       | 0F       | 40       |

| PIC18F2525               | 00                                                   | CF         | 1F       | 1F       | 00 | 87       | C5       | 00   | 0F       | C0       | 0F       | E0       | 0F       | 40       |

| PIC18F2550               | 3F                                                   | CF         | 3F       | 1F       | 00 | 87       | E5       | 00   | 0F       | C0       | 0F       | E0       | 0F       | 40       |

| PIC18F2553               | 3F                                                   | CF         | 3F       | 1F       | 00 | 87       | E5       | 00   | 0F       | C0       | 0F       | E0       | 0F       | 40       |

| PIC18F2580               | 00                                                   | CF         | 1F       | 1F       | 00 | 86       | D5       | 00   | 0F       | C0       | 0F       | E0       | 0F       | 40       |

| PIC18F2585               | 00                                                   | CF         | 1F       | 1F       | 00 | 86       | C5       | 00   | 0F       | C0       | 0F       | E0       | 0F       | 40       |

| PIC18F2610               | 00                                                   | CF         | 1F       | 1F       | 00 | 87       | C5       | 00   | 0F       | C0       | 0F       | E0       | 0F       | 40       |

| PIC18F2620               | 00                                                   | CF         | 1F       | 1F       | 00 | 87       | C5       | 00   | 0F       | C0       | 0F       | E0       | 0F       | 40       |

| PIC18F2680               | 00                                                   | CF         | 1F       | 1F       | 00 | 86       | C5       | 00   | 0F       | C0       | 0F       | E0       | 0F       | 40       |

| PIC18F2682               | 00                                                   | CF         | 1F       | 1F       | 00 | 86       | C5       | 00   | 3F       | C0       | 3F       | E0       | 3F       | 40       |

| PIC18F2685               | 00                                                   | CF         | 1F       | 1F       | 00 | 86       | C5       | 00   | 3F       | C0       | 3F       | E0       | 3F       | 40       |

| PIC18F4221               | 00                                                   | CF         | 1F       | 1F       | 00 | 87       | F5       | 00   | 03       | C0       | 03       | E0       | 03       | 40       |

| PIC18F4321               | 00                                                   | CF         | 1F       | 1F       | 00 | 87       | F5       | 00   | 03       | C0       | 03       | E0       | 03       | 40       |

| PIC18F4410               | 00                                                   | CF         | 1F       | 1F       | 00 | 87       | C5       | 00   | 03       | C0       | 03       | E0       | 03       | 40       |

| PIC18F4420               | 00                                                   | CF<br>CF   | 1F<br>1F | 1F<br>1F | 00 | 87<br>87 | C5       | 00   | 03       | C0       | 03       | E0<br>E0 | 03       | 40<br>40 |

| PIC18F4423<br>PIC18F4450 | 00<br>3F                                             | CF         | 3F       | 1F       | 00 |          | C5       | 00   | 03       | C0       | 03       |          | 03       | 40       |

| PIC18F4455               | 3F                                                   | CF         | 3F       | 1F       | 00 | 86<br>87 | ED<br>E5 | 00   | 03<br>07 | 40<br>C0 | 03<br>07 | 60<br>E0 | 03<br>07 | 40       |

| PIC18F4458               | 3F                                                   | CF         | 3F       | 1F       | 00 | 87       | E5       | 00   | 07       | CO       | 07       | E0       | 07       | 40       |

| PIC18F4480               | 00                                                   | CF         | 1F       | 1F       | 00 | 86       | D5       | 00   | 03       | CO       | 03       | E0       | 03       | 40       |

| PIC18F4510               | 00                                                   | CF         | 1F       | 1F       | 00 | 87       | C5       | 00   | 05<br>0F | CO       | 05<br>0F | E0       | 05<br>0F | 40       |

| PIC18F4515               | 00                                                   | CF         | 1F       | 1F       | 00 | 87       | C5       | 00   | 0F       | CO       | 0F       | E0       | 0F       | 40       |

| PIC18F4515               | 00                                                   | CF         | 1F       | 1F       | 00 | 87       | C5       | 00   | 0F       | CO       | 0F       | E0       | 0F       | 40       |

| PIC18F4523               | 00                                                   | CF         | 1F       | 1F       | 00 | 87       | C5       | 00   | 0F       | CO       | 0F       | E0       | 0F       | 40       |

| PIC18F4525               | 00                                                   | CF         | 1F       | 1F       | 00 | 87       | C5       | 00   | 0F       | CO       | 0F       | E0       | 0F       | 40       |

| PIC18F4550               | 3F                                                   | CF         | 3F       | 1F       | 00 | 87       | E5       | 00   | 0F       | CO       | 0F       | E0       | 0F       | 40       |

| PIC18F4553               | 3F                                                   | CF         | 3F       | 1F       | 00 | 87       | E5       | 00   | 0F       | CO       | 0F       | E0       | 0F       | 40       |

| PIC18F4580               | 00                                                   | CF         | 1F       | 1F       | 00 | 86       | D5       | 00   | 0F       | CO       | 0F       | E0       | 0F       | 40       |

| PIC18F4585               | 00                                                   | CF         | 1F       | 1F       | 00 | 86       | C5       | 00   | 0F       | CO       | 0F       | E0       | 0F       | 40       |

| PIC18F4610               | 00                                                   | CF         | 1F       | 1F       | 00 | 87       | C5       | 00   | 0F       | C0       | 0F       | E0       | 0F       | 40       |

|                          |                                                      | olle ere i |          |          | 00 | L 01     | 00       | - 00 | OI.      | - 00     | _ U      |          | UI.      | 70       |

**Legend:** Shaded cells are unimplemented.

TABLE 5-5: CONFIGURATION WORD MASKS FOR COMPUTING CHECKSUMS (CONTINUED)

|            | Configuration Word (CONFIGxx) |    |    |    |    |    |    |    |    |    |    |    |    |    |

|------------|-------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Device     | 1L                            | 1H | 2L | 2H | 3L | 3H | 4L | 4H | 5L | 5H | 6L | 6H | 7L | 7H |

| Device     | Address (30000xh)             |    |    |    |    |    |    |    |    |    |    |    |    |    |

|            | 0h                            | 1h | 2h | 3h | 4h | 5h | 6h | 7h | 8h | 9h | Ah | Bh | Ch | Dh |

| PIC18F4620 | 00                            | CF | 1F | 1F | 00 | 87 | C5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F4680 | 00                            | CF | 1F | 1F | 00 | 86 | C5 | 00 | 0F | C0 | 0F | E0 | 0F | 40 |

| PIC18F4682 | 00                            | CF | 1F | 1F | 00 | 86 | C5 | 00 | 3F | C0 | 3F | E0 | 3F | 40 |

| PIC18F4685 | 00                            | CF | 1F | 1F | 00 | 86 | C5 | 00 | 3F | C0 | 3F | E0 | 3F | 40 |

Legend: Shaded cells are unimplemented.

# 6.0 AC/DC CHARACTERISTICS TIMING REQUIREMENTS FOR PROGRAM/VERIFY TEST MODE

**Standard Operating Conditions**

Operating Temperature: 25°C is recommended

| Operat       | ing rem | perature: 25°C is recommended                                                | <u> </u>  | 1       | 1     | i                                              |

|--------------|---------|------------------------------------------------------------------------------|-----------|---------|-------|------------------------------------------------|

| Param<br>No. | Sym     | Characteristic                                                               | Min       | Max     | Units | Conditions                                     |

| D110         | VIHH    | High-Voltage Programming Voltage on MCLR/Vpp/RE3                             | VDD + 4.0 | 12.5    | V     | (Note 2)                                       |

| D110A        | VIHL    | Low-Voltage Programming Voltage on MCLR/VPP/RE3                              | 2.00      | 5.50    | V     | (Note 2)                                       |

| D111         | VDD     | Supply Voltage During Programming                                            | 2.00      | 5.50    | V     | Externally timed,<br>Row Erases and all writes |

|              |         |                                                                              | 3.0       | 5.50    | V     | Self-timed,<br>Bulk Erases only (Note 3)       |

| D112         | IPP     | Programming Current on MCLR/VPP/RE3                                          | _         | 300     | μΑ    | (Note 2)                                       |

| D113         | IDDP    | Supply Current During Programming                                            | _         | 10      | mA    |                                                |

| D031         | VIL     | Input Low Voltage                                                            | Vss       | 0.2 VDD | V     |                                                |

| D041         | VIH     | Input High Voltage                                                           | 0.8 VDD   | VDD     | V     |                                                |

| D080         | Vol     | Output Low Voltage                                                           | _         | 0.6     | V     | IOL = 8.5 mA @ 4.5V                            |

| D090         | Vон     | Output High Voltage                                                          | VDD - 0.7 | _       | V     | IOH = -3.0 mA @ 4.5V                           |

| D012         | Сю      | Capacitive Loading on I/O pin (PGD)                                          | _         | 50      | pF    | To meet AC specifications                      |

|              | •       |                                                                              |           |         |       |                                                |

| P1           | TR      | MCLR/VPP/RE3 Rise Time to Enter Program/Verify mode                          | _         | 1.0     | μS    | (Notes 1, 2)                                   |

| P2           | TPGC    | Serial Clock (PGC) Period                                                    | 100       | _       | ns    | VDD = 5.0V                                     |

|              |         |                                                                              | 1         | _       | μS    | VDD = 2.0V                                     |

| P2A          | TPGCL   | Serial Clock (PGC) Low Time                                                  | 40        | _       | ns    | VDD = 5.0V                                     |

|              |         |                                                                              | 400       | _       | ns    | VDD = 2.0V                                     |

| P2B          | TPGCH   | Serial Clock (PGC) High Time                                                 | 40        | _       | ns    | VDD = 5.0V                                     |

|              |         |                                                                              | 400       | _       | ns    | VDD = 2.0V                                     |

| P3           | TSET1   | Input Data Setup Time to Serial Clock ↓                                      | 15        | _       | ns    |                                                |

| P4           | THLD1   | Input Data Hold Time from PGC ↓                                              | 15        | _       | ns    |                                                |

| P5           | TDLY1   | Delay Between 4-Bit Command and Command Operand                              | 40        | _       | ns    |                                                |

| P5A          | TDLY1A  | Delay Between 4-Bit Command Operand and<br>Next 4-Bit Command                | 40        | _       | ns    |                                                |

| P6           | TDLY2   | Delay Between Last PGC ↓ of Command Byte to First PGC ↑ of Read of Data Word | 20        | _       | ns    |                                                |

| P9           | TDLY5   | PGC High Time (minimum programming time)                                     | 1         | _       | ms    | Externally timed                               |

| P10          | TDLY6   | PGC Low Time After Programming (high-voltage discharge time)                 | 100       | _       | μS    |                                                |

| P11          | TDLY7   | Delay to Allow Self-Timed Data Write or<br>Bulk Erase to Occur               | 5         | _       | ms    |                                                |

Note 1: Do not allow excess time when transitioning MCLR between VIL and VIHH. This can cause spurious program executions to occur. The maximum transition time is:

<sup>1</sup> TCY + TPWRT (if enabled) + 1024 Tosc (for LP, HS, HS/PLL and XT modes only) +

<sup>2</sup> ms (for HS/PLL mode only) + 1.5  $\mu$ s (for EC mode only)

where TCY is the instruction cycle time, TPWRT is the Power-up Timer period and ToSC is the oscillator period. For specific values, refer to the Electrical Characteristics section of the device data sheet for the particular device.

<sup>2:</sup> When ICPRT = 1, this specification also applies to ICVPP.

<sup>3:</sup> At 0°C-50°C.