Welcome to **E-XFL.COM**

**Embedded - System On Chip (SoC):** The Heart of Modern Embedded Systems

Embedded - System On Chip (SoC) refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

What are **Embedded - System On Chip (SoC)?**

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

| Details                 |                                                                            |  |

|-------------------------|----------------------------------------------------------------------------|--|

| Product Status          | Active                                                                     |  |

| Architecture            | MCU, FPGA                                                                  |  |

| Core Processor          | Quad ARM® Cortex®-A53 MPCore™ with CoreSight™                              |  |

| Flash Size              | -                                                                          |  |

| RAM Size                | 256KB                                                                      |  |

| Peripherals             | DMA, WDT                                                                   |  |

| Connectivity            | EBI/EMI, Ethernet, I <sup>2</sup> C, MMC/SD/SDIO, SPI, UART/USART, USB OTG |  |

| Speed                   | 1.5GHz                                                                     |  |

| Primary Attributes      | FPGA - 2800K Logic Elements                                                |  |

| Operating Temperature   | -40°C ~ 100°C (TJ)                                                         |  |

| Package / Case          | 1760-BBGA, FCBGA                                                           |  |

| Supplier Device Package | 1760-FBGA, FC (42.5x42.5)                                                  |  |

| Purchase URL            | https://www.e-xfl.com/product-detail/intel/1sx280ln2f43i2lg                |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Contents**

| 1. | Intel® Stratix® 10 GX/SX Device Overview                                       | 3  |

|----|--------------------------------------------------------------------------------|----|

|    | 1.1. Intel Stratix 10 Family Variants                                          | 4  |

|    | 1.1.1. Available Options                                                       |    |

|    | 1.2. Innovations in Intel Stratix 10 FPGAs and SoCs                            | 6  |

|    | 1.3. FPGA and SoC Features Summary                                             | 8  |

|    | 1.4. Intel Stratix 10 Block Diagram                                            |    |

|    | 1.5. Intel Stratix 10 FPGA and SoC Family Plan                                 | 11 |

|    | 1.6. HyperFlex Core Architecture                                               | 15 |

|    | 1.7. Heterogeneous 3D SiP Transceiver Tiles                                    | 16 |

|    | 1.8. Intel Stratix 10 Transceivers                                             | 17 |

|    | 1.8.1. PMA Features                                                            | 18 |

|    | 1.8.2. PCS Features                                                            | 20 |

|    | 1.9. PCI Express Gen1/Gen2/Gen3 Hard IP                                        | 21 |

|    | 1.10. Interlaken PCS Hard IP                                                   | 21 |

|    | 1.11. 10G Ethernet Hard IP                                                     |    |

|    | 1.12. External Memory and General Purpose I/O                                  | 22 |

|    | 1.13. Adaptive Logic Module (ALM)                                              |    |

|    | 1.14. Core Clocking                                                            | 24 |

|    | 1.15. Fractional Synthesis PLLs and I/O PLLs                                   |    |

|    | 1.16. Internal Embedded Memory                                                 | 25 |

|    | 1.17. Variable Precision DSP Block                                             |    |

|    | 1.18. Hard Processor System (HPS)                                              |    |

|    | 1.18.1. Key Features of the Intel Stratix 10 HPS                               |    |

|    | 1.19. Power Management                                                         |    |

|    | 1.20. Device Configuration and Secure Device Manager (SDM)                     |    |

|    | 1.21. Device Security                                                          |    |

|    | 1.22. Configuration via Protocol Using PCI Express                             |    |

|    | 1.23. Partial and Dynamic Reconfiguration                                      |    |

|    | 1.24. Fast Forward Compile                                                     |    |

|    | 1.25. Single Event Upset (SEU) Error Detection and Correction                  |    |

|    | 1.26. Document Revision History for the Intel Stratix 10 GX/SX Device Overview | 36 |

# 1. Intel® Stratix® 10 GX/SX Device Overview

Intel's 14-nm Intel® Stratix $^{\mathbb{R}}$  10 GX FPGAs and SX SoCs deliver 2X the core performance and up to 70% lower power over previous generation high-performance FPGAs.

Featuring several groundbreaking innovations, including the all new HyperFlex  $^{\text{\tiny{TM}}}$  core architecture, this device family enables you to meet the demand for ever-increasing bandwidth and processing performance in your most advanced applications, while meeting your power budget.

With an embedded hard processor system (HPS) based on a quad-core 64-bit ARM® Cortex®-A53, the Intel Stratix 10 SoC devices deliver power efficient, application-class processing and allow designers to extend hardware virtualization into the FPGA fabric. Intel Stratix 10 SoC devices demonstrate Intel's commitment to high-performance SoCs and extend Intel's leadership in programmable devices featuring an ARM-based processor system.

Important innovations in Intel Stratix 10 FPGAs and SoCs include:

- All new HyperFlex core architecture delivering 2X the core performance compared to previous generation high-performance FPGAs

- Industry leading Intel 14-nm Tri-Gate (FinFET) technology

- Heterogeneous 3D System-in-Package (SiP) technology

- Monolithic core fabric with up to 5.5 million logic elements (LEs)

- Up to 96 full duplex transceiver channels on heterogeneous 3D SiP transceiver tiles

- Transceiver data rates up to 28.3 Gbps chip-to-chip/module and backplane performance

- M20K (20 kbit) internal SRAM memory blocks

- Fractional synthesis and ultra-low jitter LC tank based transmit phase locked loops (PLLs)

- Hard PCI Express<sup>®</sup> Gen3 x16 intellectual property (IP) blocks

- Hard 10GBASE-KR/40GBASE-KR4 Forward Error Correction (FEC) in every transceiver channel

- Hard memory controllers and PHY supporting DDR4 rates up to 2666 Mbps per pin

- Hard fixed-point and IEEE 754 compliant hard floating-point variable precision digital signal processing (DSP) blocks with up to 10 TFLOPS compute performance with a power efficiency of 80 GFLOPS per Watt

- Quad-core 64-bit ARM Cortex-A53 embedded processor running up to 1.5 GHz in SoC family variants

- Programmable clock tree synthesis for flexible, low power, low skew clock trees

- Dedicated secure device manager (SDM) for:

- Enhanced device configuration and security

- AES-256, SHA-256/384 and ECDSA-256/384 encrypt/decrypt accelerators and authentication

- Multi-factor authentication

- Physically Unclonable Function (PUF) service and software programmable device configuration capability

- Comprehensive set of advanced power saving features delivering up to 70% lower power compared to previous generation high-performance FPGAs

- Non-destructive register state readback and writeback, to support ASIC prototyping and other applications

With these capabilities, Intel Stratix 10 FPGAs and SoCs are ideally suited for the most demanding applications in diverse markets such as:

- **Compute and Storage**—for custom servers, cloud computing and data center acceleration

- **Networking**—for Terabit, 400G and multi-100G bridging, aggregation, packet processing and traffic management

- Optical Transport Networks—for OTU4, 2xOTU4, 4xOTU4

- **Broadcast**—for high-end studio distribution, headend encoding/decoding, edge quadrature amplitude modulation (QAM)

- Military—for radar, electronic warfare, and secure communications

- Medical—for diagnostic scanners and diagnostic imaging

- **Test and Measurement**—for protocol and application testers

- **Wireless**—for next-generation 5G networks

- **ASIC Prototyping**—for designs that require the largest monolithic FPGA fabric with the highest I/O count

## 1.1. Intel Stratix 10 Family Variants

Intel Stratix 10 devices are available in FPGA (GX) and SoC (SX) variants.

- Intel Stratix 10 GX devices deliver up to 1 GHz core fabric performance and contain up to 5.5 million LEs in a monolithic fabric. They also feature up to 96 general purpose transceivers on separate transceiver tiles, and 2666 Mbps DDR4 external memory interface performance. The transceivers are capable of up to 28.3 Gbps short reach and across the backplane. These devices are optimized for FPGA applications that require the highest transceiver bandwidth and core fabric performance, with the power efficiency of Intel's industry-leading 14-nm Tri-Gate process technology.

- **Intel Stratix 10 SX** devices have a feature set that is identical to Intel Stratix 10 GX devices, with the addition of an embedded quad-core 64-bit ARM Cortex A53 hard processor system.

#### 1.1.1. Available Options

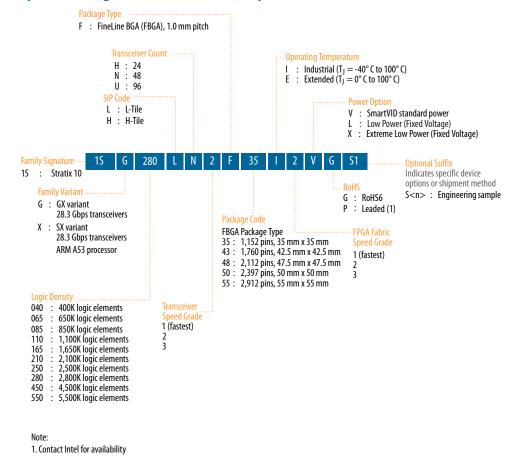

Figure 1. Sample Ordering Code and Available Options for Intel Stratix 10 Devices

#### 1.2. Innovations in Intel Stratix 10 FPGAs and SoCs

Intel Stratix 10 FPGAs and SoCs deliver many significant improvements over the previous generation high-performance Stratix V FPGAs.

Table 1. Key Features of Intel Stratix 10 Devices Compared to Stratix V Devices

| Feature             | Stratix V FPGAs                                               | Intel Stratix 10 FPGAs and SoCs                                         |  |

|---------------------|---------------------------------------------------------------|-------------------------------------------------------------------------|--|

| Process technology  | 28-nm TSMC (planar transistor)                                | 14 nm Intel Tri-Gate (FinFET)                                           |  |

| Hard processor core | None                                                          | Quad-core 64-bit ARM Cortex-A53 (SoC only)                              |  |

| Core architecture   | Conventional core architecture with conventional interconnect | HyperFlex core architecture with<br>Hyper-Registers in the interconnect |  |

| Core performance    | 500 MHz                                                       | 1 GHz                                                                   |  |

| Power dissipation   | 1x                                                            | As low as 0.3x                                                          |  |

| continued           |                                                               |                                                                         |  |

| Feature                                      | Stratix V FPGAs                                                              | Intel Stratix 10 FPGAs and SoCs                                                                                                              |

|----------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Logic density                                | 952 KLE (monolithic)                                                         | 5,500 KLE (monolithic)                                                                                                                       |

| Embedded memory (M20K)                       | 52 Mbits                                                                     | 229 Mbits                                                                                                                                    |

| 18x19 multipliers                            | 3,926<br>Note: Multiplier is 18x18 in<br>Stratix V devices.                  | 11,520 Note: Multiplier is 18x19 in Intel Stratix 10 devices.                                                                                |

| Floating point DSP capability                | Up to 1 TFLOP, requires soft floating point adder and multiplier             | Up to 10 TFLOPS, hard IEEE 754 compliant single precision floating point adder and multiplier                                                |

| Maximum transceivers                         | 66                                                                           | 96                                                                                                                                           |

| Maximum transceiver data rate (chip-to-chip) | 28.05 Gbps                                                                   | 28.3 Gbps L-Tile<br>28.3 Gbps H-Tile                                                                                                         |

| Maximum transceiver data rate (backplane)    | 12.5 Gbps                                                                    | 12.5 Gbps L-Tile<br>28.3 Gbps H-Tile                                                                                                         |

| Hard memory controller                       | None                                                                         | DDR4 @ 1333 MHz/2666 Mbps<br>DDR3 @ 1067 MHz/2133 Mbps                                                                                       |

| Hard protocol IP                             | PCIe Gen3 x8 (up to 4 instances)                                             | PCIe Gen3 x16 (up to 4 instances)<br>SR-IOV (4 physical functions / 2k<br>virtual functions) on H-Tile devices<br>10GBASE-KR/40GBASE-KR4 FEC |

| Core clocking and PLLs                       | Global, quadrant and regional clocks supported by fractional-synthesis fPLLs | Programmable clock tree synthesis supported by fractional synthesis fPLLs and integer IO PLLs                                                |

| Register state readback and writeback        | Not available                                                                | Non-destructive register state<br>readback and writeback for ASIC<br>prototyping and other applications                                      |

These innovations result in the following improvements:

- **Improved Core Logic Performance**: The HyperFlex core architecture combined with Intel's 14-nm Tri-Gate technology allows Intel Stratix 10 devices to achieve 2X the core performance compared to the previous generation

- **Lower Power**: Intel Stratix 10 devices use up to 70% lower power compared to the previous generation, enabled by 14-nm Intel Tri-Gate technology, the HyperFlex core architecture, and optional power saving features built into the architecture

- Higher Density: Intel Stratix 10 devices offer over five times the level of integration, with up to 5,500K logic elements (LEs) in a monolithic fabric, over 229 Mbits of embedded memory blocks (M20K), and 11,520 18x19 multipliers

- **Embedded Processing**: Intel Stratix 10 SoCs feature a Quad-Core 64-bit ARM Cortex-A53 processor optimized for power efficiency and software compatible with previous generation Arria and Cyclone SoC devices

- Improved Transceiver Performance: With up to 96 transceiver channels implemented in heterogeneous 3D SiP transceiver tiles, Intel Stratix 10 GX and SX devices support data rates up to 28.3 Gbps chip-to-chip and 28.3 Gbps across the backplane with signal conditioning circuits capable of equalizing over 30 dB of system loss

- Improved DSP Performance: The variable precision DSP block in Intel Stratix 10 devices features hard fixed and floating point capability, with up to 10 TeraFLOPS IEEE754 single-precision floating point performance

#### 1. Intel® Stratix® 10 GX/SX Device Overview

| Feature                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Power management                        | SmartVID controlled core voltage, standard power devices     0.85-V fixed core voltage, low static power devices available     Intel Quartus® Prime Pro Edition integrated power analysis                                                                                                                                                                                                                                                                       |  |

| High performance monolithic core fabric | HyperFlex core architecture with Hyper-Registers throughout the interconnect routing and at the inputs of all functional blocks  Monolithic fabric minimizes compile times and increases logic utilization  Enhanced adaptive logic module (ALM)  Improved multi-track routing architecture reduces congestion and improves compile times  Hierarchical core clocking architecture with programmable clock tree synthesis  Fine-grained partial reconfiguration |  |

| Internal memory blocks                  | M20K—20-Kbit with hard ECC support     MLAB—640-bit distributed LUTRAM                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Variable precision DSP blocks           | IEEE 754-compliant hard single-precision floating point capability Supports signal processing with precision ranging from 18x19 up to 54x54 Native 27x27 and 18x19 multiply modes 64-bit accumulator and cascade for systolic FIRs Internal coefficient memory banks Pre-adder/subtractor improves efficiency Additional pipeline register increases performance and reduces power                                                                              |  |

| Phase locked loops (PLL)                | <ul> <li>Fractional synthesis PLLs (fPLL) support both fractional and integer modes</li> <li>Fractional mode with third-order delta-sigma modulation</li> <li>Precision frequency synthesis</li> <li>Integer PLLs adjacent to general purpose I/Os, support external memory, and LVDS interfaces, clock delay compensation, zero delay buffering</li> </ul>                                                                                                     |  |

| Core clock networks                     | 1 GHz fabric clocking     667 MHz external memory interface clocking, supports 2666 Mbps DDR4 interface     800 MHz LVDS interface clocking, supports 1600 Mbps LVDS interface     Programmable clock tree synthesis, backwards compatible with global, regional and peripheral clock networks     Clocks only synthesized where needed, to minimize dynamic power                                                                                              |  |

| SoC Subsystem                   | Feature                    | Description                                                                       |

|---------------------------------|----------------------------|-----------------------------------------------------------------------------------|

| NAND flash controller           |                            | 1 ONFI 1.0, 8- and 16-bit support                                                 |

|                                 | General-purpose I/O (GPIO) | Maximum of 48 software programmable GPIO                                          |

|                                 | Timers                     | 4 general-purpose timers     4 watchdog timers                                    |

| Secure Device<br>Manager        | Security                   | Secure boot     Advanced Encryption Standard (AES) and authentication (SHA/ECDSA) |

| External<br>Memory<br>Interface | External Memory Interface  | Hard Memory Controller with DDR4 and DDR3, and LPDDR3                             |

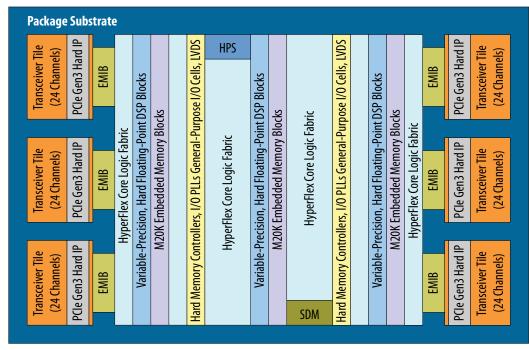

## 1.4. Intel Stratix 10 Block Diagram

Figure 2. Intel Stratix 10 FPGA and SoC Architecture Block Diagram

HPS: Quad ARM Cortex-A53 Hard Processor System

SDM: Secure Device Manager

EMIB: Embedded Multi-Die Interconnect Bridge

## 1.5. Intel Stratix 10 FPGA and SoC Family Plan

<sup>(1)</sup> The number of 27x27 multipliers is one-half the number of 18x19 multipliers.

#### 1. Intel® Stratix® 10 GX/SX Device Overview

S10-OVERVIEW | 2018.08.08

| Intel Stratix 10     | Interco       | Interconnects |       | PLLs     | Hard IP                |  |

|----------------------|---------------|---------------|-------|----------|------------------------|--|

| GX/SX Device<br>Name | Maximum GPIOs | Maximum XCVR  | fPLLs | I/O PLLs | PCIe Hard IP<br>Blocks |  |

| GX 2800/<br>SX 2800  | 1160          | 96            | 32    | 24       | 4                      |  |

| GX 4500/<br>SX 4500  | 1640          | 24            | 8     | 34       | 1                      |  |

| GX 5500/<br>SX 5500  | 1640          | 24            | 8     | 34       | 1                      |  |

Table 6. Intel Stratix 10 GX/SX FPGA and SoC Family Package Plan, part 1

Cell legend: General Purpose I/Os, High-Voltage I/Os, LVDS Pairs, Transceivers (2) (3) (4) (5) (6) (7)

| Intel Stratix 10 GX/SX<br>Device Name | F1152<br>HF35<br>(35x35 mm²) | F1760<br>NF43<br>(42.5x42.5 mm <sup>2</sup> ) | F1760<br>NF43<br>(42.5x42.5 mm <sup>2</sup> ) |

|---------------------------------------|------------------------------|-----------------------------------------------|-----------------------------------------------|

| GX 400/<br>SX 400                     | 392, 8, 192, 24              |                                               |                                               |

| GX 650/<br>SX 650                     | 392, 8, 192, 24              | 400, 16, 192, 48                              |                                               |

| GX 850/<br>SX 850                     |                              |                                               | 688, 16, 336, 48                              |

| GX 1100/<br>SX 1100                   |                              |                                               | 688, 16, 336, 48                              |

| GX 1650/<br>SX 1650                   |                              |                                               | 688, 16, 336, 48                              |

| GX 2100/<br>SX 2100                   |                              |                                               | 688, 16, 336, 48                              |

| GX 2500/<br>SX 2500                   |                              |                                               | 688, 16, 336, 48                              |

| GX 2800/                              |                              |                                               | 688, 16, 336, 48                              |

<sup>(2)</sup> All packages are ball grid arrays with 1.0 mm pitch.

<sup>(3)</sup> High-Voltage I/O pins are used for 3 V and 2.5 V interfacing.

<sup>(4)</sup> Each LVDS pair can be configured as either a differential input or a differential output.

<sup>(5)</sup> High-Voltage I/O pins and LVDS pairs are included in the General Purpose I/O count. Transceivers are counted separately.

<sup>(6)</sup> Each package column offers pin migration (common circuit board footprint) for all devices in the column.

<sup>(7)</sup> Intel Stratix 10 GX devices are pin migratable with Intel Stratix 10 SX devices in the same package.

| Intel Stratix 10 GX/SX<br>Device Name | F1152<br>HF35<br>(35x35 mm²) | F1760<br>NF43<br>(42.5x42.5 mm <sup>2</sup> ) | F1760<br>NF43<br>(42.5x42.5 mm <sup>2</sup> ) |

|---------------------------------------|------------------------------|-----------------------------------------------|-----------------------------------------------|

| SX 2800                               |                              |                                               |                                               |

| GX 4500/<br>SX 4500                   |                              |                                               |                                               |

| GX 5500/<br>SX 5500                   |                              |                                               |                                               |

#### Table 7. Intel Stratix 10 GX/SX FPGA and SoC Family Package Plan, part 2

Cell legend: General Purpose I/Os, High-Voltage I/Os, LVDS Pairs, Transceivers (2) (3) (4) (5) (6) (7)

| Intel Stratix 10<br>GX/SX Device Name | F2112<br>NF48<br>(47.5x47.5 mm²) | F2397<br>UF50<br>(50x50 mm²) | F2912<br>HF55<br>(55x55 mm²) |

|---------------------------------------|----------------------------------|------------------------------|------------------------------|

| GX 400/<br>SX 400                     |                                  |                              |                              |

| GX 650/<br>SX 650                     |                                  |                              |                              |

| GX 850/<br>SX 850                     | 736, 16, 360, 48                 |                              |                              |

| GX 1100/<br>SX 1100                   | 736, 16, 360, 48                 |                              |                              |

| GX 1650/<br>SX 1650                   |                                  | 704, 32, 336, 96             |                              |

| GX 2100/<br>SX 2100                   |                                  | 704, 32, 336, 96             |                              |

| GX 2500/<br>SX 2500                   |                                  | 704, 32, 336, 96             | 1160, 8, 576, 24             |

| GX 2800/<br>SX 2800                   |                                  | 704, 32, 336, 96             | 1160, 8, 576, 24             |

| GX 4500/<br>SX 4500                   |                                  |                              | 1640, 8, 816, 24             |

| GX 5500/<br>SX 5500                   |                                  |                              | 1640, 8, 816, 24             |

### 1.6. HyperFlex Core Architecture

Intel Stratix 10 FPGAs and SoCs are based on a monolithic core fabric featuring the new HyperFlex core architecture. The HyperFlex core architecture delivers 2X the clock frequency performance and up to 70% lower power compared to previous generation high-end FPGAs. Along with this performance breakthrough, the HyperFlex core architecture delivers a number of advantages including:

- Higher Throughput—Leverages 2X core clock frequency performance to obtain throughput breakthroughs

- **Improved Power Efficiency**—Uses reduced IP size, enabled by HyperFlex, to consolidate designs which previously spanned multiple devices into a single device, thereby reducing power by up to 70% versus previous generation devices

- Greater Design Functionality—Uses faster clock frequency to reduce bus widths and reduce IP size, freeing up additional FPGA resources to add greater functionality

- **Increased Designer Productivity**—Boosts performance with less routing congestion and fewer design iterations using Hyper-Aware design tools, obtaining greater timing margin for more rapid timing closure

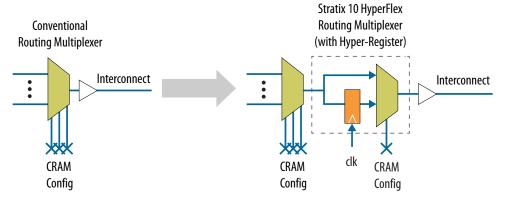

In addition to the traditional user registers found in the Adaptive Logic Modules (ALM), the HyperFlex core architecture introduces additional bypassable registers everywhere throughout the fabric of the FPGA. These additional registers, called Hyper-Registers are available on every interconnect routing segment and at the inputs of all functional blocks.

Figure 3. Bypassable Hyper-Register

The Hyper-Registers enable the following key design techniques to achieve the 2X core performance increases:

- Fine grain Hyper-Retiming to eliminate critical paths

- Zero latency Hyper-Pipelining to eliminate routing delays

- Flexible Hyper-Optimization for best-in-class performance

By implementing these techniques in your design, the Hyper-Aware design tools automatically make use of the Hyper-Registers to achieve maximum core clock frequency.

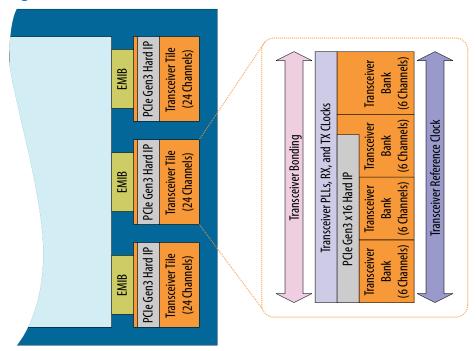

Each transceiver tile contains:

- 24 full-duplex transceiver channels (PMA and PCS)

- · Reference clock distribution network

- Transmit PLLs

- High-speed clocking and bonding networks

- One instance of PCI Express hard IP

Figure 6. Heterogeneous 3D SiP Transceiver Tile Architecture

#### 1.8. Intel Stratix 10 Transceivers

Intel Stratix 10 devices offer up to 96 total full-duplex transceiver channels. These channels provide continuous data rates from 1 Gbps to 28.3 Gbps for chip-to-chip, chip-to-module, and backplane applications. In each device, two thirds of the transceivers can be configured up to the maximum data rate of 28.3 Gbps to drive 100G interfaces and C form-factor pluggable CFP2/CFP4 optical modules. For longer-reach backplane driving applications, advanced adaptive equalization circuits are used to equalize over 30 dB of system loss.

All transceiver channels feature a dedicated Physical Medium Attachment (PMA) and a hardened Physical Coding Sublayer (PCS).

- The PMA provides primary interfacing capabilities to physical channels.

- The PCS typically handles encoding/decoding, word alignment, and other preprocessing functions before transferring data to the FPGA core fabric.

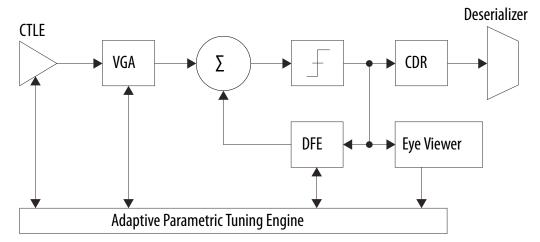

Figure 7. Intel Stratix 10 Receiver Block Features

All link equalization parameters feature automatic adaptation using the new Advanced Digital Adaptive Parametric Tuning (ADAPT) circuit. This circuit is used to dynamically set DFE tap weights, adjust CTLE parameters, and optimize VGA gain and threshold voltage. Finally, optimal and consistent signal integrity is ensured by using the new hardened Precision Signal Integrity Calibration Engine (PreSICE) to automatically calibrate all transceiver circuit blocks on power-up. This gives the most link margin and ensures robust, reliable, and error-free operation.

**Table 8.** Transceiver PMA Features

| Feature                                                    | Capability                                                                                                                                                                                          |  |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Chip-to-Chip Data Rates                                    | 1 Gbps <sup>(8)</sup> to 28.3 Gbps (Intel Stratix 10 GX/SX devices)                                                                                                                                 |  |

| Backplane Support                                          | Drive backplanes at data rates up to 28.3 Gbps, including 10GBASE-KR compliance                                                                                                                     |  |

| Optical Module Support                                     | SFP+/SFP, XFP, CXP, QSFP/QSFP28, QSFPDD, CFP/CFP2/CFP4                                                                                                                                              |  |

| Cable Driving Support                                      | SFP+ Direct Attach, PCI Express over cable, eSATA                                                                                                                                                   |  |

| Transmit Pre-Emphasis                                      | 5-tap transmit pre-emphasis and de-emphasis to compensate for system channel loss                                                                                                                   |  |

| Continuous Time Linear<br>Equalizer (CTLE)                 | Dual mode, high-gain, and high-data rate, linear receive equalization to compensate for system channel loss                                                                                         |  |

| Decision Feedback Equalizer (DFE)                          | 15 fixed tap DFE to equalize backplane channel loss in the presence of crosstalk and nois environments                                                                                              |  |

| Advanced Digital Adaptive<br>Parametric Tuning (ADAPT)     | Fully digital adaptation engine to automatically adjust all link equalization parameters—including CTLE, DFE, and VGA blocks—that provide optimal link margin without interven from user logic      |  |

| Precision Signal Integrity<br>Calibration Engine (PreSICE) | Hardened calibration controller to quickly calibrate all transceiver control parameters on power-up, which provides the optimal signal integrity and jitter performance                             |  |

| ATX Transmit PLLs                                          | Low jitter ATX (inductor-capacitor) transmit PLLs with continuous tuning range to cover a wide range of standard and proprietary protocols, with optional fractional frequency synthesis capability |  |

| Fractional PLLs                                            | On-chip fractional frequency synthesizers to replace on-board crystal oscillators and reduce system cost                                                                                            |  |

|                                                            | continued                                                                                                                                                                                           |  |

<sup>(8)</sup> Stratix 10 transceivers can support data rates below 1 Gbps with over sampling.

#### 1.11. 10G Ethernet Hard IP

Intel Stratix 10 devices include IEEE 802.3 10-Gbps Ethernet (10GbE) compliant 10GBASE-R PCS and PMA hard IP. The scalable 10GbE hard IP supports multiple independent 10GbE ports while using a single PLL for all the 10GBASE-R PCS instantiations, which saves on core logic resources and clock networks.

The integrated serial transceivers simplify multi-port 10GbE systems compared to 10 GbE Attachment Unit Interface (XAUI) interfaces that require an external XAUI-to-10G PHY. Furthermore, the integrated transceivers incorporate signal conditioning circuits, which enable direct connection to standard 10G XFP and SFP+ pluggable optical modules. The transceivers also support backplane Ethernet applications and include a hard 10GBASE-KR/40GBASE-KR4 Forward Error Correction (FEC) circuit that can be used for both 10G and 40G applications. The integrated 10G Ethernet hard IP and 10G transceivers save external PHY cost, board space and system power. The 10G Ethernet PCS hard IP and 10GBASE-KR FEC are present in every transceiver channel.

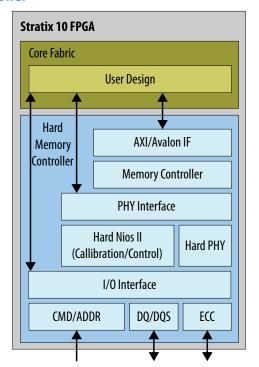

### 1.12. External Memory and General Purpose I/O

Intel Stratix 10 devices offer substantial external memory bandwidth, with up to ten 72-bit wide DDR4 memory interfaces running at up to 2666 Mbps.

This bandwidth is provided along with the ease of design, lower power, and resource efficiencies of hardened high-performance memory controllers. The external memory interfaces can be configured up to a maximum width of 144 bits when using either hard or soft memory controllers.

Figure 8. Hard Memory Controller

The core clock network in Intel Stratix 10 devices supports the new HyperFlex core architecture at clock rates up to 1 GHz. It also supports the hard memory controllers up to 2666 Mbps with a quarter rate transfer to the core. The core clock network is supported by dedicated clock input pins, fractional clock synthesis PLLs, and integer I/O PLLs.

### 1.15. Fractional Synthesis PLLs and I/O PLLs

Intel Stratix 10 devices have up to 32 fractional synthesis PLLs (fPLL) available for use with transceivers or in the core fabric.

The fPLLs are located in the 3D SiP transceiver H-tiles, eight per tile, adjacent to the transceiver channels. The fPLLs can be used to reduce both the number of oscillators required on the board and the number of clock pins required, by synthesizing multiple clock frequencies from a single reference clock source. In addition to synthesizing reference clock frequencies for the transceiver transmit PLLs, the fPLLs can also be used directly for transmit clocking. Each fPLL can be independently configured for conventional integer mode, or enhanced fractional synthesis mode with third-order delta-sigma modulation.

In addition to the fPLLs, Intel Stratix 10 devices contain up to 34 integer I/O PLLs (IOPLLs) available for general purpose use in the core fabric and for simplifying the design of external memory interfaces and high-speed LVDS interfaces. The IOPLLs are located in each bank of 48 general purpose I/O, 1 per I/O bank, adjacent to the hard memory controllers and LVDS SerDes in each I/O bank. This makes it easier to close timing because the IOPLLs are tightly coupled with the I/Os that need to use them. The IOPLLs can be used for general purpose applications in the core such as clock network delay compensation and zero-delay clock buffering.

## 1.16. Internal Embedded Memory

Intel Stratix 10 devices contain two types of embedded memory blocks: M20K (20-Kbit) and MLAB (640-bit).

The M20K and MLAB blocks are familiar block sizes carried over from previous Intel device families. The MLAB blocks are ideal for wide and shallow memories, while the M20K blocks are intended to support larger memory configurations and include hard ECC. Both M20K and MLAB embedded memory blocks can be configured as a single-port or dual-port RAM, FIFO, ROM, or shift register. These memory blocks are highly flexible and support a number of memory configurations as shown in Table 11 on page 25

**Table 11. Internal Embedded Memory Block Configurations**

| MLAB (640 bits)                                  | M20K (20 Kbits)                     |

|--------------------------------------------------|-------------------------------------|

| 64 x 10 (supported through emulation)<br>32 x 20 | 2K x 10 (or x8)<br>1K x 20 (or x16) |

| 32 X 20                                          | 512 x 40 (or x32)                   |

#### 1.17. Variable Precision DSP Block

The Intel Stratix 10 DSP blocks are based upon the Variable Precision DSP Architecture used in Intel's previous generation devices. They feature hard fixed point and IEEE-754 compliant floating point capability.

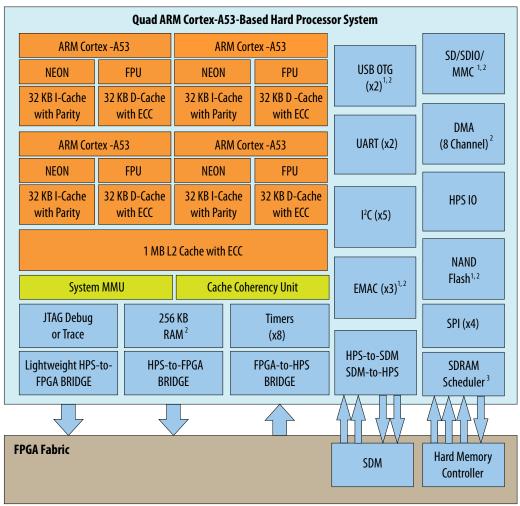

Figure 13. HPS Block Diagram

Notes:

- 1. Integrated direct memory access (DMA)

- 2. Integrated error correction code (ECC)

- 3. Multiport front-end interface to hard memory controller

#### 1.18.1. Key Features of the Intel Stratix 10 HPS

Table 14. Key Features of the Intel Stratix 10 GX/SX HPS

| Feature                                           | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Quad-core ARM Cortex-A53<br>MPCore processor unit | <ul> <li>2.3 MIPS/MHz instruction efficiency</li> <li>CPU frequency up to 1.5 GHz</li> <li>At 1.5 GHz total performance of 13,800 MIPS</li> <li>ARMv8-A architecture</li> <li>Runs 64-bit and 32-bit ARM instructions</li> <li>16-bit and 32-bit Thumb instructions for 30% reduction in memory footprint</li> <li>Jazelle® RCT execution architecture with 8-bit Java bytecodes</li> </ul> |

|                                                   | continued                                                                                                                                                                                                                                                                                                                                                                                   |

| Feature                                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                       | <ul> <li>Superscalar, variable length, out-of-order pipeline with dynamic branch prediction</li> <li>Improved ARM NEON™ media processing engine</li> <li>Single- and double-precision floating-point unit</li> <li>CoreSight™ debug and trace technology</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| System Memory<br>Management Unit                      | Enables a unified memory model and extends hardware virtualization into peripherals implemented in the FPGA fabric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Cache Coherency unit                                  | Changes in shared data stored in cache are propagated throughout the system providing bi-directional coherency for co-processing elements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Cache                                                 | L1 Cache  32 KB of instruction cache w/ parity check  32 KB of L1 data cache w /ECC  Parity checking  L2 Cache  1MB shared  8-way set associative  SEU Protection with parity on TAG ram and ECC on data RAM  Cache lockdown support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| On-Chip Memory                                        | 256 KB of scratch on-chip RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| External SDRAM and Flash<br>Memory Interfaces for HPS | <ul> <li>Hard memory controller with support for DDR4, DDR3, LPDDR3         <ul> <li>40-bit (32-bit + 8-bit ECC) with select packages supporting 72-bit (64-bit + 8-bit ECC)</li> <li>Support for up to 2666 Mbps DDR4 and 2166 Mbps DDR3 frequencies</li> <li>Error correction code (ECC) support including calculation, error correction, write-back correction, and error counters</li> <li>Software Configurable Priority Scheduling on individual SDRAM bursts</li> <li>Fully programmable timing parameter support for all JEDEC-specified timing parameters</li> <li>Multiport front-end (MPFE) scheduler interface to the hard memory controller, which supports the AXI® Quality of Service (QoS) for interface to the FPGA fabric</li> </ul> </li> <li>NAND flash controller         <ul> <li>ONFI 1.0</li> <li>Integrated descriptor based with DMA</li> <li>Programmable hardware ECC support</li> <li>Support for 8- and 16-bit Flash devices</li> </ul> </li> <li>Secure Digital SD/SDIO/MMC controller         <ul> <li>eMMC 4.5</li> <li>Integrated descriptor based DMA</li> <li>CE-ATA digital commands supported</li> <li>50 MHz operating frequency</li> <li>Direct memory access (DMA) controller</li> <li>8-channel</li> <li>Supports up to 32 peripheral handshake interface</li> </ul></li></ul> |

| Feature                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Communication Interface Controllers | Three 10/100/1000 Ethernet media access controls (MAC) with integrated DMA  — Supports RGMII and RMII external PHY Interfaces  — Option to support other PHY interfaces through FPGA logic  • GMII  • MII  • RMII (requires MII to RMII adapter)  • RGMII (requires GMII to RGMII adapter)  • SGMII (requires GMII to SGMII adapter)  • SGMII (requires GMII to SGMII adapter)  — Supports IEEE 1588-2002 and IEEE 1588-2008 standards for precision networked clock synchronization  — Supports IEEE 802.1Q VLAN tag detection for reception frames  — Supports Ethernet AVB standard  • Two USB On-the-Go (OTG) controllers with DMA  — Dual-Role Device (device and host functions)  • High-speed (480 Mbps)  • Full-speed (12 Mbps)  • Low-speed (1.5 Mbps)  • Supports USB 1.1 (full-speed and low-speed)  — Integrated descriptor-based scatter-gather DMA  — Support for external ULPI PHY  — Up to 16 bidirectional endpoints, including control endpoint  — Up to 16 bidirectional endpoints, including control endpoint  — Up to 16 host channels  — Support speneric root hub  — Configurable to OTG 1.3 and OTG 2.0 modes  • Five I²C controllers (three can be used by EMAC for MIO to external PHY)  — Support both 100Kbps and 400Kbps modes  — Support Master and Slave operating mode  • Two UART 16550 compatible  — Programmable baud rate up to 115.2Kbaud  • Four serial peripheral interfaces (SPI) (2 Master, 2 Slaves)  — Full and Half duplex |

| Timers and I/O                      | Timers  — 4 general-purpose timers  — 4 watchdog timers  4 8 HPS direct I/O allow HPS peripherals to connect directly to I/O  Up to three IO48 banks may be assigned to HPS for HPS DDR access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Interconnect to Logic Core          | <ul> <li>FPGA-to-HPS Bridge         <ul> <li>Allows IP bus masters in the FPGA fabric to access to HPS bus slaves</li> <li>Configurable 32-, 64-, or 128-bit AMBA AXI interface</li> </ul> </li> <li>HPS-to-FPGA Bridge         <ul> <li>Allows HPS bus masters to access bus slaves in FPGA fabric</li> <li>Configurable 32-, 64-, or 128-bit AMBA AXI interface allows high-bandwidth HPS master transactions to FPGA fabric</li> </ul> </li> <li>HPS-to-SDM and SDM-to-HPS Bridges         <ul> <li>Allows the HPS to reach the SDM block and the SDM to bootstrap the HPS</li> </ul> </li> <li>Light Weight HPS-to-FPGA Bridge         <ul> <li>Light weight 32-bit AXI interface suitable for low-latency register accesses from HPS to soft peripherals in FPGA fabric</li> </ul> </li> <li>FPGA-to-HPS SDRAM Bridge         <ul> <li>Up to three AMBA AXI interfaces supporting 32, 64, or 128-bit data paths</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

### 1.19. Power Management

Intel Stratix 10 devices leverage the advanced Intel 14-nm Tri-Gate process technology, the all new HyperFlex core architecture to enable Hyper-Folding, power gating, and several optional power reduction techniques to reduce total power consumption by as much as 70% compared to previous generation high-performance Stratix V devices.

Intel Stratix 10 standard power devices (-V) are SmartVID devices. The core voltage supplies (VCC and VCCP) for each SmartVID device must be driven by a PMBus voltage regulator dedicated to that Intel Stratix 10 device. Use of a PMBus voltage regulator for each SmartVID (-V) device is mandatory; it is not an option. A code is programmed into each SmartVID device during manufacturing that allows the PMBus voltage regulator to operate at the optimum core voltage to meet the device performance specifications.

With the new HyperFlex core architecture, designs can run 2X faster than previous generation FPGAs. With 2X performance and same required throughput, architects can cut the data path width in half to save power. This optimization is called Hyper-Folding. Additionally, power gating reduces static power of unused resources in the FPGA by powering them down. The Intel Quartus Prime software automatically powers down specific unused resource blocks such as DSP and M20K blocks, at configuration time.

The optional power reduction techniques in Intel Stratix 10 devices include:

Available Low Static Power Devices—Intel Stratix 10 devices are available with a fixed core voltage that provides lower static power than the SmartVID standard power devices, while maintaining device performance

Furthermore, Intel Stratix 10 devices feature Intel's industry-leading low power transceivers and include a number of hard IP blocks that not only reduce logic resources but also deliver substantial power savings compared to soft implementations. In general, hard IP blocks consume up to 50% less power than the equivalent soft logic implementations.

## 1.20. Device Configuration and Secure Device Manager (SDM)

All Intel Stratix 10 devices contain a Secure Device Manager (SDM), which is a dedicated triple-redundant processor that serves as the point of entry into the device for all JTAG and configuration commands. The SDM also bootstraps the HPS in SoC devices ensuring that the HPS can boot using the same security features that the FPGA devices have.

The SDM enables robust, secure, fully-authenticated device configuration. It also allows for customization of the configuration scheme, which can enhance device security. For configuration and reconfiguration, this approach offers a variety of advantages:

- · Dedicated secure configuration manager

- Reduced device configuration time, because sectors are configured in parallel

- Updateable configuration process

- Reconfiguration of one or more sectors independent of all other sectors

- Zeroization of individual sectors or the complete device

The SDM also provides additional capabilities such as register state readback and writeback to support ASIC prototyping and other applications.

### 1.21. Device Security

Building on top of the robust security features present in the previous generation devices, Intel Stratix 10 FPGAs and SoCs include a number of new and innovative security enhancements. These features are also managed by the SDM, tightly coupling device configuration and reconfiguration with encryption, authentication, key storage and anti-tamper services.

Security services provided by the SDM include:

- Bitstream encryption

- Multi-factor authentication

- Hard encryption and authentication acceleration; AES-256, SHA-256/384, ECDSA-256/384

- Volatile and non-volatile encryption key storage and management

- Boot code authentication for the HPS

- Physically Unclonable Function (PUF) service

- Updateable configuration process

- Secure device maintenance and upgrade functions

- Side channel attack protection

- Scripted response to sensor inputs and security attacks, including selective sector zeroization

- · Readback, JTAG and test mode disable

- Enhanced response to single-event upsets (SEU)

The SDM and associated security services provide a robust, multi-layered security solution for your Intel Stratix 10 design.

## 1.22. Configuration via Protocol Using PCI Express

Configuration via protocol using PCI Express allows the FPGA to be configured across the PCI Express bus, simplifying the board layout and increasing system integration. Making use of the embedded PCI Express hard IP operating in autonomous mode before the FPGA is configured, this technique allows the PCI Express bus to be

powered up and active within the 100 ms time allowed by the PCI Express specification. Intel Stratix 10 devices also support partial reconfiguration across the PCI Express bus which reduces system down time by keeping the PCI Express link active while the device is being reconfigured.

### 1.23. Partial and Dynamic Reconfiguration

Partial reconfiguration allows you to reconfigure part of the FPGA while other sections continue running. This capability is required in systems where uptime is critical, because it allows you to make updates or adjust functionality without disrupting services.

In addition to lowering power and cost, partial reconfiguration also increases the effective logic density by removing the necessity to place in the FPGA those functions that do not operate simultaneously. Instead, these functions can be stored in external memory and loaded as needed. This reduces the size of the required FPGA by allowing multiple applications on a single FPGA, saving board space and reducing power. The partial reconfiguration process is built on top of the proven incremental compile design flow in the Intel Quartus Prime design software

Dynamic reconfiguration in Intel Stratix 10 devices allows transceiver data rates, protocols and analog settings to be changed dynamically on a channel-by-channel basis while maintaining data transfer on adjacent transceiver channels. Dynamic reconfiguration is ideal for applications that require on-the-fly multiprotocol or multirate support. Both the PMA and PCS blocks within the transceiver can be reconfigured using this technique. Dynamic reconfiguration of the transceivers can be used in conjunction with partial reconfiguration of the FPGA to enable partial reconfiguration of both core and transceivers simultaneously.

## 1.24. Fast Forward Compile

The innovative Fast Forward Compile feature in the Intel Quartus Prime software identifies performance bottlenecks in your design and provides detailed, step-by-step performance improvement recommendations that you can then implement. The Compiler reports estimates of the maximum operating frequency that can be achieved by applying the recommendations. As part of the new Hyper-Aware design flow, Fast Forward Compile maximizes the performance of your Intel Stratix 10 design and achieves rapid timing closure.

Previously, this type of optimization required multiple time-consuming design iterations, including full design re-compilation to determine the effectiveness of the changes. Fast Forward Compile enables you to make better decisions about where to focus your optimization efforts, and how to increase your design performance and throughput. This technique removes much of the guesswork of performance exploration, resulting in fewer design iterations and as much as 2X core performance gains for Intel Stratix 10 designs.

## 1.25. Single Event Upset (SEU) Error Detection and Correction

Intel Stratix 10 FPGAs and SoCs offer robust SEU error detection and correction circuitry. The detection and correction circuitry includes protection for Configuration RAM (CRAM) programming bits and user memories. The CRAM is protected by a continuously running parity checker circuit with integrated ECC that automatically corrects one or two bit errors and detects higher order multibit errors.