# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI                                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 22                                                                      |

| Program Memory Size        | 3.5KB (2K x 14)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 5x8b                                                                |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-VQFN Exposed Pad                                                     |

| Supplier Device Package    | 28-QFN (6x6)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f72-e-ml |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### FIGURE 2-2:

#### -2: PIC16F72 REGISTER FILE MAP

| Indirect addr.(*) | 00h        | Indirect addr.(*)              | 80h        | Indirect addr.(*) | 100h | Indirect addr.(*)    | 180 |

|-------------------|------------|--------------------------------|------------|-------------------|------|----------------------|-----|

| TMR0              | 01h        | OPTION                         | 81h        | TMR0              | 101h | OPTION               | 181 |

| PCL               | 02h        | PCL                            | 82h        | PCL               | 102h | PCL                  | 182 |

| STATUS            | 03h        | STATUS                         | 83h        | STATUS            | 103h | STATUS               | 183 |

| FSR               | 04h        | FSR                            | 84h        | FSR               | 104h | FSR                  | 184 |

| PORTA             | 05h        | TRISA                          | 85h        |                   | 105h |                      | 185 |

| PORTB             | 06h        | TRISB                          | 86h        | PORTB             | 106h | TRISB                | 186 |

| PORTC             | 07h        | TRISC                          | 87h        |                   | 107h |                      | 187 |

|                   | 08h        |                                | 88h        |                   | 108h |                      | 188 |

|                   | 09h        |                                | 89h        |                   | 109h |                      | 189 |

| PCLATH            | 0Ah        | PCLATH                         | 8Ah        | PCLATH            | 10Ah | PCLATH               | 18A |

| INTCON            | 0Bh        | INTCON                         | 8Bh        | INTCON            | 10Bh | INTCON               | 18E |

| PIR1              | 0Ch        | PIE1                           | 8Ch        | PMDATL            | 10Ch | PMCON1               | 180 |

|                   | 0Dh        |                                | 8Dh        | PMADRL            | 10Dh |                      | 180 |

| TMR1L             | 0Eh        | PCON                           | 8Eh        | PMDATH            | 10Eh |                      | 18E |

| TMR1H             | 0Fh        |                                | 8Fh        | PMADRH            | 10Fh |                      | 18F |

| T1CON             | 10h        |                                | 90h        |                   | 110h |                      | 190 |

| TMR2              | 11h        |                                | 91h        |                   |      |                      |     |

| T2CON             | 12h        | PR2                            | 92h        |                   |      |                      |     |

| SSPBUF            | 13h        | SSPADD                         | 93h        |                   |      |                      |     |

| SSPCON            | 14h        | SSPSTAT                        | 94h        |                   |      |                      |     |

| CCPR1L            | 15h        |                                | 95h        |                   |      |                      |     |

| CCPR1H            | 16h        |                                | 96h        |                   |      |                      |     |

| CCP1CON           | 17h        |                                | 97h        |                   |      |                      |     |

|                   | 18h        |                                | 98h        |                   |      |                      |     |

|                   | 19h        |                                | 99h        |                   |      |                      |     |

|                   | 1Ah        |                                | 9Ah        |                   |      |                      |     |

|                   | 1Bh        |                                | 9Bh        |                   |      |                      |     |

|                   | 1Ch        |                                | 9Ch        |                   |      |                      |     |

|                   | 1Dh        |                                | 9Dh        |                   |      |                      |     |

| ADRES             | 1Eh        |                                | 9Eh        |                   | 11Fh |                      | 19F |

| ADCON0            | 1Fh        | ADCON1                         | 9Fh        |                   |      |                      |     |

|                   | 20h        | General<br>Purpose<br>Register | A0h        |                   | 120h | accesses<br>A0h -BFh | 1A) |

| General           |            | 32 Bytes                       | BFh        |                   |      |                      | 1B  |

| Purpose           |            |                                | C0h        | accesses          |      |                      | 1C  |

| Register          |            | accesses                       |            | 20h-7Fh           |      | accesses             |     |

| 96 Bytes          |            | 40h-7Fh                        |            |                   |      | 40h -7Fh             |     |

|                   | 7Fh        |                                | FFh        |                   | 17Fh |                      | 1FF |

| Bank 0            |            | Bank 1                         |            | Bank 2            |      | Bank 3               |     |

| Unimplem          | ented data | a memory location              | s, read as | ·'O'.             |      |                      |     |

#### 2.2.2.6 PCON Register

| Note: | Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate inter- |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | rupt flag bits are clear prior to enabling an interrupt.                                                                                                                                                              |

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR), a Brown-out Reset, an external MCLR Reset and WDT Reset.

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent RESETS to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a 'don't care' and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BOREN bit in the Configuration word).

#### REGISTER 2-6: PCON: POWER CONTROL REGISTER (ADDRESS 8Eh)

| U-0                        | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-x |  |  |  |

|----------------------------|-----|-----|-----|-----|-----|-------|-------|--|--|--|

| _                          | _   | _   | _   | _   | —   | POR   | BOR   |  |  |  |

| bit 7                      |     |     |     |     |     |       | bit 0 |  |  |  |

|                            |     |     |     |     |     |       |       |  |  |  |

| Unimplemented: Read as '0' |     |     |     |     |     |       |       |  |  |  |

| bit 1 | POR: Power-on Reset Status bit |

|-------|--------------------------------|

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0

bit 7-2

**BOR:** Brown-out Reset Status bit 1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 8.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The CCP (Capture/Compare/PWM) module contains a 16-bit register that can operate as a:

- 16-bit capture register

- 16-bit compare register

- PWM master/slave duty cycle register.

Table 8-1 shows the timer resources of the CCP Module modes.

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable. Additional information on the CCP module is available in the PIC<sup>™</sup> Mid-Range MCU Reference Manual, (DS33023).

## TABLE 8-1:CCP MODE - TIMER<br/>RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

#### **REGISTER 8-1:** CCPCON1: CAPTURE/COMPARE/PWM CONTROL REGISTER 1 (ADDRESS 17h)

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

| —     | _   | CCPxX | CCPxY | CCPxM3 | CCPxM2 | CCPxM1 | CCPxM0 |

| bit 7 |     |       |       |        |        |        | bit 0  |

- bit 7-6 Unimplemented: Read as '0'

- bit 5-4 CCPxX:CCPxY: PWM Least Significant bits Capture mode:

|         | Capture mode:                                                                                                                                                       |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Unused                                                                                                                                                              |

|         | Compare mode:                                                                                                                                                       |

|         | Unused                                                                                                                                                              |

|         | PWM mode:                                                                                                                                                           |

|         | These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                                              |

| bit 3-0 | CCPxM3:CCPxM0: CCPx Mode Select bits                                                                                                                                |

|         | 0000 = Capture/Compare/PWM disabled (resets CCPx module)                                                                                                            |

|         | 0100 = Capture mode, every falling edge                                                                                                                             |

|         | 0101 = Capture mode, every rising edge                                                                                                                              |

|         | 0110 = Capture mode, every 4th rising edge                                                                                                                          |

|         | 0111 = Capture mode, every 16th rising edge                                                                                                                         |

|         | 1000 = Compare mode, set output on match (CCPxIF bit is set)                                                                                                        |

|         | 1001 = Compare mode, clear output on match (CCPxIF bit is set)                                                                                                      |

|         | 1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set,                                                                                       |

|         | CCPx pin is unaffected)                                                                                                                                             |

|         | 1011 = Compare mode, trigger special event (CCPxIF bit is set, CCPx pin is unaffected);<br>CCP1 resets TMR1 and starts an A/D conversion (if A/D module is enabled) |

|         | 11xx = PWM mode                                                                                                                                                     |

|         |                                                                                                                                                                     |

|         |                                                                                                                                                                     |

|         | Legend:                                                                                                                                                             |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| Address              | Name    | Bit 7   | Bit 6                               | Bit 5         | Bit 4         | Bit 3         | Bit 2        | Bit 1     | Bit 0  |      | e on<br>BOR | all o | e on<br>other<br>SETS |

|----------------------|---------|---------|-------------------------------------|---------------|---------------|---------------|--------------|-----------|--------|------|-------------|-------|-----------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE     | PEIE                                | TMR0IE        | INTE          | RBIE          | TMR0IF       | INTF      | RBIF   | 0000 | 000x        | 0000  | 000u                  |

| 0Ch                  | PIR1    | —       | ADIF                                | —             |               | SSPIF         | CCP1IF       | TMR2IF    | TMR1IF | - 0  | 0000        | 0000  | 0000                  |

| 8Ch                  | PIE1    | —       | ADIE                                | —             | _             | SSPIE         | CCP1IE       | TMR2IE    | TMR1IE | - 0  | 0000        | 0000  | 0000                  |

| 87h                  | TRISC   | PORTC   | Data D                              | irection Re   | gister        |               |              |           |        | 1111 | 1111        | 1111  | 1111                  |

| 0Eh                  | TMR1L   | Holding | Registe                             | er for the Le | ast Signific  | ant Byte of   | the 16-bit 7 | FMR1 Regi | ster   | xxxx | xxxx        | uuuu  | uuuu                  |

| 0Fh                  | TMR1H   | Holding | Registe                             | er for the M  | ost Significa | ant Byte of t | he 16-bit T  | MR1 Regis | ster   | xxxx | xxxx        | uuuu  | uuuu                  |

| 10h                  | T1CON   | —       |                                     | T1CKPS1       | T1CKPS0       | T1OSCEN       | T1SYNC       | TMR1CS    | TMR10N | 00   | 0000        | uu    | uuuu                  |

| 15h                  | CCPR1L  | Capture | Capture/Compare/PWM Register1 (LSB) |               |               |               |              |           |        | xxxx | xxxx        | uuuu  | uuuu                  |

| 16h                  | CCPR1H  | Capture | Capture/Compare/PWM Register1 (MSB) |               |               |               |              |           |        | xxxx | xxxx        | uuuu  | uuuu                  |

| 17h                  | CCP1CON | _       | _                                   | CCP1X         | CCP1Y         | CCP1M3        | CCP1M2       | CCP1M1    | CCP1M0 | 00   | 0000        | 00    | 0000                  |

## TABLE 8-2: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.

| ER 9-2: | SSPCON                                                                                                                                                                               | SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)                                                                                                                                                                                                                                                                                                                                                                                                                              |               |                                      |               |               |              |             |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------|---------------|---------------|--------------|-------------|--|--|--|

|         | R/W-0                                                                                                                                                                                | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0         | R/W-0                                | R/W-0         | R/W-0         | R/W-0        | R/W-0       |  |  |  |

|         | WCOL                                                                                                                                                                                 | SSPOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SSPEN         | CKP                                  | SSPM3         | SSPM2         | SSPM1        | SSPM0       |  |  |  |

|         | bit 7                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |                                      |               |               |              | bit 0       |  |  |  |

| bit 7   | WCOL: W                                                                                                                                                                              | /rite Collision                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Detect bit    |                                      |               |               |              |             |  |  |  |

|         |                                                                                                                                                                                      | d in software                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               | en while it is                       | still transmi | tting the pr  | evious word  | d (must be  |  |  |  |

| bit 6   |                                                                                                                                                                                      | Receive Over                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | flow Indicate | or bit                               |               |               |              |             |  |  |  |

| DILO    |                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | now mulcall   |                                      |               |               |              |             |  |  |  |

|         | 1 = A new<br>of ove<br>must<br>mode<br>by wr<br>0 = No ov                                                                                                                            | <ul> <li>In SPI mode:</li> <li>1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is lost. Overflow can only occur in Slave mode. The user must read the SSPBUF, even if only transmitting data, to avoid setting overflow. In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPBUF register.</li> <li>0 = No overflow</li> </ul> |               |                                      |               |               |              |             |  |  |  |

|         | 1 = A byte<br>is a "c                                                                                                                                                                | <u>In I<sup>2</sup>C mode:</u><br>1 = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV<br>is a "don't care" in Transmit mode. SSPOV must be cleared in software in either mode.<br>0 = No overflow                                                                                                                                                                                                                                             |               |                                      |               |               |              |             |  |  |  |

| bit 5   | SSPEN: S                                                                                                                                                                             | SSPEN: Synchronous Serial Port Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |                                      |               |               |              |             |  |  |  |

|         | In SPI mode:<br>1 = Enables serial port and configures SCK, SDO, and SDI as serial port pins<br>0 = Disables serial port and configures these pins as I/O port pins                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |                                      |               |               |              |             |  |  |  |

|         | In l <sup>2</sup> C mode:                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |                                      |               |               |              |             |  |  |  |

|         | <ul> <li>1 = Enables the serial port and configures the SDA and SCL pins as serial port pins</li> <li>0 = Disables serial port and configures these pins as I/O port pins</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |                                      |               |               |              |             |  |  |  |

|         | In both modes, when enabled, these pins must be properly configured as input or output.                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |                                      |               |               |              |             |  |  |  |

| bit 4   |                                                                                                                                                                                      | <b>CKP:</b> Clock Polarity Select bit                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |                                      |               |               |              |             |  |  |  |

|         | In SPI mode:                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |                                      |               |               |              |             |  |  |  |

|         | <ul> <li>1 = IDLE state for clock is a high level (Microwire<sup>®</sup> default)</li> <li>0 = IDLE state for clock is a low level (Microwire alternate)</li> </ul>                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |                                      |               |               |              |             |  |  |  |

|         | In I <sup>2</sup> C mode:<br>SCK release control<br>1 = Enable clock                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |                                      |               |               |              |             |  |  |  |

|         | 0 = Holds                                                                                                                                                                            | clock low (cl                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ock stretch - | used to ens                          | ure data setu | ıp time)      |              |             |  |  |  |

| bit 3-0 | SSPM<3:                                                                                                                                                                              | 0>: Synchro                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | nous Serial F | Port Mode Se                         | lect bits     |               |              |             |  |  |  |

|         | 0000 = SI                                                                                                                                                                            | SSPM<3:0>: Synchronous Serial Port Mode Select bits<br>0000 = SPI Master mode, clock = Fosc/4                                                                                                                                                                                                                                                                                                                                                                                        |               |                                      |               |               |              |             |  |  |  |

|         |                                                                                                                                                                                      | 0001 = SPI Master mode, clock = Fosc/16                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |                                      |               |               |              |             |  |  |  |

|         |                                                                                                                                                                                      | PI Master mo                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |                                      | 10            |               |              |             |  |  |  |

|         |                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               | TMR2 o <u>utp</u> ut<br>CK pin. SS p |               | abled.        |              |             |  |  |  |

|         |                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |                                      |               |               | an be used   | as I/O pin. |  |  |  |

|         | $0110 = I^2$                                                                                                                                                                         | 0101 = SPI Slave mode, clock = SCK pin. $\overline{SS}$ pin control disabled. $\overline{SS}$ can be used as I/O pin.<br>0110 = I <sup>2</sup> C Slave mode, 7-bit address                                                                                                                                                                                                                                                                                                           |               |                                      |               |               |              |             |  |  |  |

|         |                                                                                                                                                                                      | 0111 = $I^2C$ Slave mode, 10-bit address<br>1011 = $I^2C$ firmware controlled Master mode (Slave IDLE)                                                                                                                                                                                                                                                                                                                                                                               |               |                                      |               |               |              |             |  |  |  |

|         |                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |                                      |               | D hit intorru | into onoblo  | 4           |  |  |  |

|         | 1110 = $I^2C$ Slave mode, 7-bit address with START and STOP bit interrupts enabled<br>1111 = $I^2C$ Slave mode, 10-bit address with START and STOP bit interrupts enabled            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |                                      |               |               |              |             |  |  |  |

|         | Legend:                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |                                      |               |               |              |             |  |  |  |

|         | R = Read                                                                                                                                                                             | able bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | W = V         | Vritable bit                         | U = Unim      | plemented     | bit, read as | '0'         |  |  |  |

|         |                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | v             |                                      | 0 - 01111     | plomonicu     | , 1000 05    | ~           |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

- n = Value at POR

x = Bit is unknown

In 10-bit Address mode, two address bytes need to be received by the slave device. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit  $R/\overline{W}$  (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address.

The sequence of events for 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF, and bit UA (SSPSTAT<1>) are set).

- 2. Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF, and UA are set).

- 5. Update the SSPADD register with the first (high) byte of Address, if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated START condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

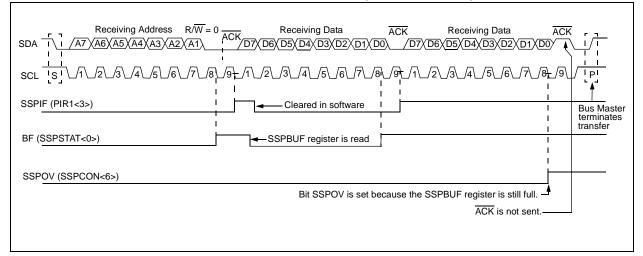

## 9.3.1.2 Reception

When the R/W bit of the address byte is clear and an address match occurs, the R/W bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then a no Acknowledge (ACK) pulse is given. An overflow condition is indicated if either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON<6>) is set.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

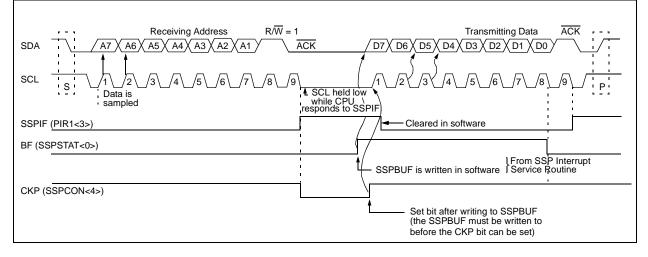

#### 9.3.1.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit, and pin RC3/SCK/SCL is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master device must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master device by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 9-7).

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software and the SSPSTAT register is used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the ACK pulse from the masterreceiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not ACK), then the data transfer is complete. When the ACK is latched by the slave device, the slave logic is reset (resets SSPSTAT register) and the slave device then monitors for another occurrence of the START bit. If the SDA line was low (ACK), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, pin RC3/SCK/SCL should be enabled by setting bit CKP.

| TABLE 9-2: | DATA TRANSFER RECEIVED BYTE ACTIO | NS    |

|------------|-----------------------------------|-------|

| IADLE 3-Z. | DATA TRANSFER RECEIVED BITE ACTIO | UND - |

|    | ts as Data<br>s Received |                            |                    | Set bit SSPIF                     |

|----|--------------------------|----------------------------|--------------------|-----------------------------------|

| BF | SSPOV                    | $SSPSR \rightarrow SSPBUF$ | Generate ACK Pulse | (SSP Interrupt occurs if enabled) |

| 0  | 0                        | Yes                        | Yes                | Yes                               |

| 1  | 0                        | No                         | No                 | Yes                               |

| 1  | 1                        | No                         | No                 | Yes                               |

| 0  | 1                        | No                         | No                 | Yes                               |

**Note 1:** Shaded cells show the conditions where the user software did not properly clear the overflow condition.

## 11.2 Oscillator Configurations

#### 11.2.1 OSCILLATOR TYPES

The PIC16F72 can be operated in four different Oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

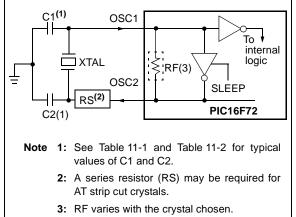

## 11.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

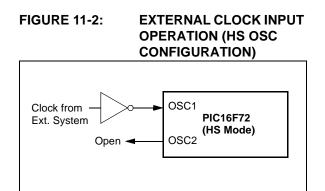

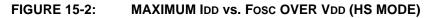

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKI and OSC2/CLKO pins to establish oscillation (Figure 11-1). The PIC16F72 oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in HS mode, the device can accept an external clock source to drive the OSC1/CLKI pin (Figure 11-2). See Figure 14-1 or Figure 14-2 (depending on the part number and VDD range) for valid external clock frequencies.

#### FIGURE 11-1: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

#### TABLE 11-1: CERAMIC RESONATORS (FOR DESIGN GUIDANCE ONLY)

| -    | Typical Capac | itor Values Use | ed:   |

|------|---------------|-----------------|-------|

| Mode | Freq          | OSC1            | OSC2  |

| XT   | 455 kHz       | 56 pF           | 56 pF |

|      | 2.0 MHz       | 47 pF           | 47 pF |

|      | 4.0 MHz       | 33 pF           | 33 pF |

| HS   | 8.0 MHz       | 27 pF           | 27 pF |

|      | 16.0 MHz      | 22 pF           | 22 pF |

#### Capacitor values are for design guidance only.

These capacitors were tested with the resonators listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes at the bottom of page 62 for additional information.

#### TABLE 11-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR (FOR DESIGN GUIDANCE ONLY)

| Osc Type | Crystal<br>Freq | Typical Capa<br>Tes |       |

|----------|-----------------|---------------------|-------|

|          | печ             | C1                  | C2    |

| LP       | 32 kHz          | 33 pF               | 33 pF |

|          | 200 kHz         | 15 pF               | 15 pF |

| XT       | 200 kHz         | 56 pF               | 56 pF |

|          | 1 MHz           | 15 pF               | 15 pF |

|          | 4 MHz           | 15 pF               | 15 pF |

| HS       | 4 MHz           | 15 pF               | 15 pF |

|          | 8 MHz           | 15 pF               | 15 pF |

|          | 20 MHz          | 15 pF               | 15 pF |

Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

- Note 1: Higher capacitance increases the stability of oscillator, but also increases the start-up time.

- Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- **3:** Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- **4:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

#### 11.2.3 RC OSCILLATOR

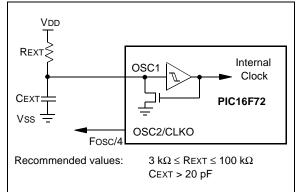

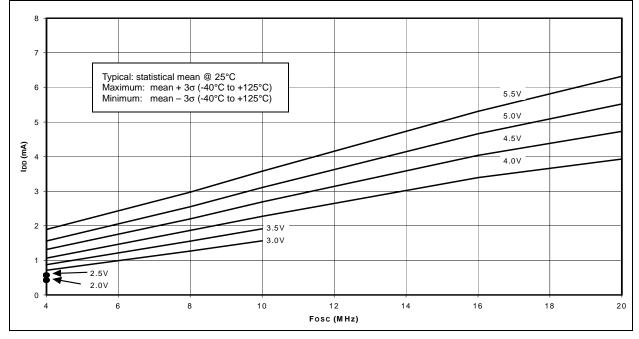

For timing insensitive applications, the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 11-3 shows how the R/C combination is connected to the PIC16F72.

## 11.3 **RESET**

The PIC16F72 differentiates between various kinds of RESET:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during SLEEP

- WDT Reset (during normal operation)

- WDT Wake-up (during SLEEP)

- Brown-out Reset (BOR)

Some registers are not affected in any RESET condition. Their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset (POR), on the MCLR and WDT Reset, on MCLR Reset during SLEEP, and Brown-out Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different RESET situations, as indicated in Table 11-4. These bits are used in software to determine the nature of the RESET. See Table 11-6 for a full description of RESET states of all registers.

A simplified block diagram of the on-chip RESET circuit is shown in Figure 11-4.

| SUBLW            | Subtract W from Literal                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                     |

| Operands:        | $0 \le k \le 255$                                                                                                            |

| Operation:       | $k \text{ - (W)} \rightarrow (W)$                                                                                            |

| Status Affected: | C, DC, Z                                                                                                                     |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register. |

| XORLW            | Exclusive OR Literal with W                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] XORLW k                                                                                                            |

| Operands:        | $0 \le k \le 255$                                                                                                          |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                              |

| Status Affected: | Z                                                                                                                          |

| Description:     | The contents of the W register<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed in<br>the W register. |

| SUBWF            | Subtract W from f                                                                                                                                                                         |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SUBWF f,d                                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                     |

| Status Affected: | C, DC, Z                                                                                                                                                                                  |

| Description:     | Subtract (2's complement method)<br>W register from register 'f'. If<br>'d' = '0', the result is stored in the W<br>register. If 'd' = '1', the result is<br>stored back in register 'f'. |

| XORWF            | Exclusive OR W with f                                                                                                                                                         |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] XORWF f,d                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                            |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                     |

| Status Affected: | Z                                                                                                                                                                             |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' = '0', the result is stored in the W register. If 'd' = '1', the result is stored back in register 'f'. |

| SWAPF            | Swap Nibbles in f                                                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                          |

| Status Affected: | None                                                                                                                                                             |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' = '0', the result is placed in W register. If 'd' = '1', the result is placed in register 'f'. |

## TABLE 13-1: DEVELOPMENT TOOLS FROM MICROCHIP

|                                                                       | PIC12CXXX | PIC14000 | PIC16C5X | PIC16C6X | VXX381219 | PIC16F62X | X7Oði Olq | (X7O81OI9 | PIC16C8X/ | PIC16F8X | (X6D81DI9 | X43713I9 | (XTOTIOI9 | PIC18CXX | PIC18FXX | 83CXX<br>52CXX/<br>54CXX/ | хххэн | МСКFXXX | MCP2510 |

|-----------------------------------------------------------------------|-----------|----------|----------|----------|-----------|-----------|-----------|-----------|-----------|----------|-----------|----------|-----------|----------|----------|---------------------------|-------|---------|---------|

| MPLAB <sup>®</sup> Integrated<br>Development Environment              | >         | >        | >        | >        | >         | >         | >         | >         | >         | >        | >         | >        | >         | >        | >        |                           |       |         |         |

| MPLAB <sup>®</sup> C17 C Compiler                                     |           |          |          | 1        |           |           |           |           |           |          |           | >        | >         |          |          |                           |       |         |         |

| MPLAB <sup>®</sup> C18 C Compiler                                     |           |          |          |          |           |           |           |           |           |          |           |          |           | >        | >        |                           |       |         |         |

| MPLINK <sup>TM</sup> Assembler/<br>MPLINK <sup>TM</sup> Object Linker | >         | >        | >        | >        | ^         | ^         | >         | >         | >         | >        | >         | >        | >         | >        | >        | >                         | >     |         |         |

| MPLAB® ICE In-Circuit Emulator                                        | ~         | ~        | >        | >        | ~         | ×*`       | >         | >         | >         | ~        | >         | >        | >         | ~        | ~        |                           |       |         |         |

| ICEPIC <sup>TM</sup> In-Circuit Emulator                              | >         |          | >        | >        | >         |           | >         | >         | >         |          | >         |          |           |          |          |                           |       |         |         |

| MPLAB® ICD In-Circuit<br>Debugger                                     |           |          |          | *>       |           |           | * >       |           |           | >        |           |          |           |          | >        |                           |       |         |         |

| PICSTART <sup>®</sup> Plus Entry Level<br>Development Programmer      | >         | >        | >        | >        | >         | **^       | >         | `         | `         | `        | >         | >        | >         | >        | >        |                           |       |         |         |

| PRO MATE® II<br>Universal Device Programmer                           | >         | >        | >        | >        | >         | **/       | ^         | ^         | ^         | ^        | >         | >        | >         | >        | >        | >                         | >     |         |         |

| PICDEM <sup>TM</sup> 1 Demonstration<br>Board                         |           |          | >        |          | >         |           | ÷+        |           | >         |          |           | >        |           |          |          |                           |       |         |         |

| PICDEM <sup>™</sup> 2 Demonstration<br>Board                          |           |          |          | .↓       |           |           | .↓        |           |           |          |           |          |           | >        | >        |                           |       |         |         |

| PICDEM <sup>TM</sup> 3 Demonstration<br>Board                         |           |          |          |          |           |           |           |           |           |          | >         |          |           |          |          |                           |       |         |         |

| PICDEM <sup>TM</sup> 14A Demonstration<br>Board                       |           | >        |          |          |           |           |           |           |           |          |           |          |           |          |          |                           |       |         |         |

| PICDEM <sup>TM</sup> 17 Demonstration<br>Board                        |           |          |          |          |           |           |           |           |           |          |           |          | >         |          |          |                           |       |         |         |

| KEELoQ <sup>®</sup> Evaluation Kit                                    |           |          |          |          |           |           |           |           |           |          |           |          |           |          |          |                           | >     |         |         |

| KEELoq® Transponder Kit                                               |           |          |          |          |           |           |           |           |           |          |           |          |           |          |          |                           | >     |         |         |

| microlD™ Programmer's Kit                                             |           |          |          |          |           |           |           |           |           |          |           |          |           |          |          |                           |       | ~       |         |

| 125 kHz microlD™<br>Developer's Kit                                   |           |          |          |          |           |           |           |           |           |          |           |          |           |          |          |                           |       | >       |         |

| 125 kHz Anticollision microlD™<br>Developer's Kit                     |           |          |          |          |           |           |           |           |           |          |           |          |           |          |          |                           |       | `       |         |

| 13.56 MHz Anticollision<br>microlD <sup>TM</sup> Developer's Kit      |           |          |          |          |           |           |           |           |           |          |           |          |           |          |          |                           |       | >       |         |

| MCD0610 CAN Barrelande Kit                                            |           |          |          |          |           |           |           |           |           |          |           |          |           |          |          |                           |       |         | >       |

\*\* Contact Microchip Technology Inc. for availability date.

<sup>†</sup> Development tool is available on select devices.

### 14.2 DC Characteristics: PIC16F72 (Industrial, Extended) PIC16LF72 (Industrial)

|              | RACTE | RISTICS                      | $ \begin{array}{lll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \\ \mbox{Operating voltage VDD range as described in DC Specification,} \\ \mbox{Section 14.1.} \end{array} $ |      |          |       |                                                             |

|--------------|-------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|-------------------------------------------------------------|

| Param<br>No. | Sym   | Characteristic               | Min                                                                                                                                                                                                                                                                                                                                                               | Тур† | Max      | Units | Conditions                                                  |

|              | VIL   | Input Low Voltage            |                                                                                                                                                                                                                                                                                                                                                                   |      |          |       |                                                             |

|              |       | I/O ports                    |                                                                                                                                                                                                                                                                                                                                                                   |      |          |       |                                                             |

| D030         |       | with TTL buffer              | Vss                                                                                                                                                                                                                                                                                                                                                               | —    | 0.15 Vdd | V     | For entire VDD range                                        |

| D030A        |       |                              | Vss                                                                                                                                                                                                                                                                                                                                                               |      | 0.8V     | V     | $4.5V \le VDD \le 5.5V$                                     |

| D031         |       | with Schmitt Trigger buffer  | Vss                                                                                                                                                                                                                                                                                                                                                               | —    | 0.2 Vdd  | V     |                                                             |

| D032         |       | MCLR, OSC1 (in RC mode)      | Vss                                                                                                                                                                                                                                                                                                                                                               |      | 0.2 Vdd  | V     |                                                             |

| D033         |       | OSC1 (in XT and LP mode)     | Vss                                                                                                                                                                                                                                                                                                                                                               | —    | 0.3V     | V     | (Note 1)                                                    |

|              |       | OSC1 (in HS mode)            | Vss                                                                                                                                                                                                                                                                                                                                                               | —    | 0.3 Vdd  | V     | (Note 1)                                                    |

|              | Vih   | Input High Voltage           |                                                                                                                                                                                                                                                                                                                                                                   |      |          |       |                                                             |

|              |       | I/O ports                    |                                                                                                                                                                                                                                                                                                                                                                   |      |          |       |                                                             |

| D040         |       | with TTL buffer              | 2.0                                                                                                                                                                                                                                                                                                                                                               |      | Vdd      | V     | $4.5V \le VDD \le 5.5V$                                     |

| D040A        |       |                              | 0.25 VDD + 0.8V                                                                                                                                                                                                                                                                                                                                                   |      | Vdd      | V     | For entire VDD range                                        |

| D041         |       | with Schmitt Trigger buffer  | 0.8 Vdd                                                                                                                                                                                                                                                                                                                                                           | —    | Vdd      | V     | For entire VDD range                                        |