Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI                                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 22                                                                      |

| Program Memory Size        | 3.5KB (2K x 14)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 5x8b                                                                |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 28-SPDIP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f72-e-sp |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Device Overview                              |    |

|-------|----------------------------------------------|----|

| 2.0   | Memory Organization                          | 7  |

| 3.0   | I/O Ports                                    |    |

| 4.0   | Reading Program Memory                       | 27 |

| 5.0   | Timer0 Module                                |    |

| 6.0   | Timer1 Module                                | 31 |

| 7.0   | Timer2 Module                                | 35 |

| 8.0   | Capture/Compare/PWM (CCP) Module             | 37 |

| 9.0   | Synchronous Serial Port (SSP) Module         |    |

| 10.0  | Analog-to-Digital Converter (A/D) Module     |    |

| 11.0  | Special Features of the CPU                  | 59 |

| 12.0  | Instruction Set Summary                      |    |

| 13.0  | Development Support                          | 81 |

| 14.0  | Electrical Characteristics                   | 87 |

| 15.0  | DC and AC Characteristics Graphs and Tables1 | 07 |

| 16.0  | Package Marking Information1                 | 17 |

| Appe  | ndix A: Revision History1                    | 23 |

|       | ndix B: Conversion Considerations1           |    |

| Index |                                              | 25 |

| On-Li | ne Support1                                  | 31 |

|       | er Response 1                                |    |

| Produ | ict Identification System 1                  | 33 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## 4.3 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI, with the internal phase clocks, is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2 Tosc (and a small RC delay of 20 ns) and low for at least 2 Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

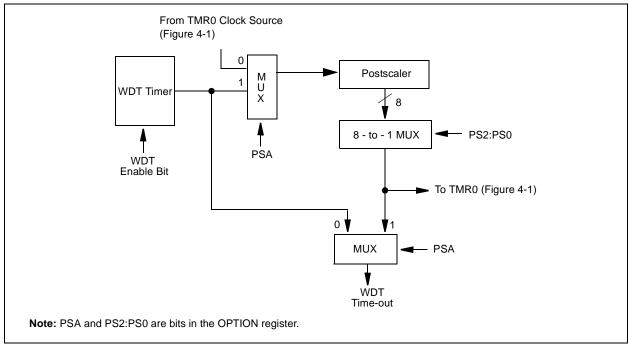

## 4.4 Prescaler

There is only one prescaler available, which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa. This prescaler is not readable or writable (see Figure 4-1).

The PSA and PS2:PS0 bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

Note: Writing to TMR0 when the prescaler is assigned to Timer0, will clear the prescaler count but will not change the prescaler assignment.

| Address               | Name   | Bit 7  | Bit 6    | Bit 5    | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>RESETS |

|-----------------------|--------|--------|----------|----------|-------|-------|--------|-------|-------|----------------------|---------------------------------|

| 01h,101h              | TMR0   | Timer0 | Module F | Register |       |       |        |       |       | xxxx xxxx            | uuuu uuuu                       |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE    | PEIE     | TMR0IE   | INTE  | RBIE  | TMR0IF | INTF  | RBIF  | 0000 000x            | 0000 000u                       |

| 81h,181h              | OPTION | RBPU   | INTEDG   | TOCS     | T0SE  | PSA   | PS2    | PS1   | PS0   | 1111 1111            | 1111 1111                       |

TABLE 4-1: REGISTERS ASSOCIATED WITH TIMER0

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

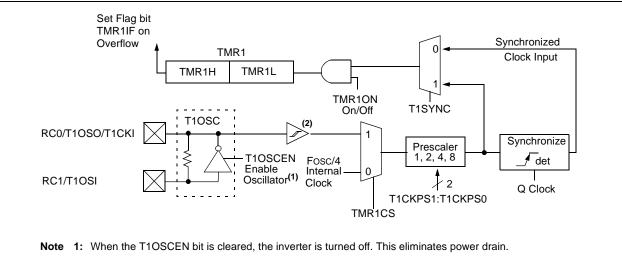

# 5.2 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect, since the internal clock is always in sync.

# 5.3 Timer1 Counter Operation

Timer1 may operate in Asynchronous or Synchronous mode, depending on the setting of the TMR1CS bit.

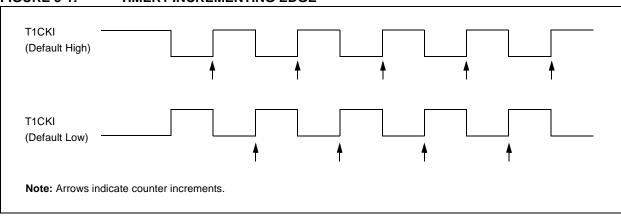

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

# 5.4 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RC1/T1OSI when bit T1OSCEN is set, or on pin RC0/T1OSO/T1CKI when bit T1OSCEN is cleared.

If  $\overline{T1SYNC}$  is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut-off. The prescaler, however, will continue to increment.

## FIGURE 5-1: TIMER1 INCREMENTING EDGE

| Address              | Name    | Bit 7   | Bit 6                               | Bit 5         | Bit 4         | Bit 3         | Bit 2        | Bit 1     | Bit 0  |      | e on<br>BOR | all o | e on<br>other<br>SETS |

|----------------------|---------|---------|-------------------------------------|---------------|---------------|---------------|--------------|-----------|--------|------|-------------|-------|-----------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE     | PEIE                                | TMR0IE        | INTE          | RBIE          | TMR0IF       | INTF      | RBIF   | 0000 | 000x        | 0000  | 000u                  |

| 0Ch                  | PIR1    | —       | ADIF                                | —             |               | SSPIF         | CCP1IF       | TMR2IF    | TMR1IF | - 0  | 0000        | 0000  | 0000                  |

| 8Ch                  | PIE1    | —       | ADIE                                | —             | _             | SSPIE         | CCP1IE       | TMR2IE    | TMR1IE | - 0  | 0000        | 0000  | 0000                  |

| 87h                  | TRISC   | PORTC   | Data D                              | irection Re   | gister        |               |              |           |        | 1111 | 1111        | 1111  | 1111                  |

| 0Eh                  | TMR1L   | Holding | Registe                             | er for the Le | ast Signific  | ant Byte of   | the 16-bit 7 | MR1 Regi  | ster   | xxxx | xxxx        | uuuu  | uuuu                  |

| 0Fh                  | TMR1H   | Holding | Registe                             | er for the M  | ost Significa | ant Byte of t | he 16-bit T  | MR1 Regis | ster   | xxxx | xxxx        | uuuu  | uuuu                  |

| 10h                  | T1CON   | —       |                                     | T1CKPS1       | T1CKPS0       | T1OSCEN       | T1SYNC       | TMR1CS    | TMR10N | 00   | 0000        | uu    | uuuu                  |

| 15h                  | CCPR1L  | Capture | Capture/Compare/PWM Register1 (LSB) |               |               |               |              |           |        |      |             |       |                       |

| 16h                  | CCPR1H  | Capture | Capture/Compare/PWM Register1 (MSB) |               |               |               |              |           |        |      |             |       |                       |

| 17h                  | CCP1CON | _       | _                                   | CCP1X         | CCP1Y         | CCP1M3        | CCP1M2       | CCP1M1    | CCP1M0 | 00   | 0000        | 00    | 0000                  |

# TABLE 8-2: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.

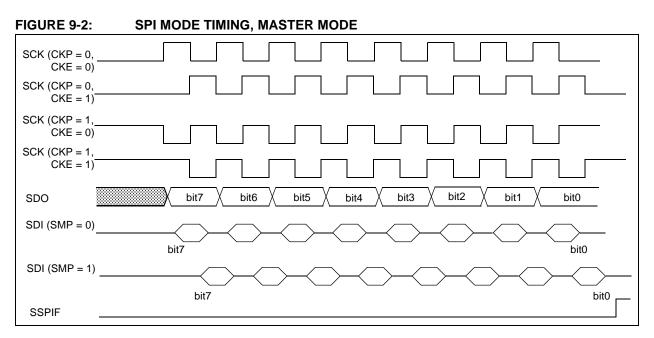

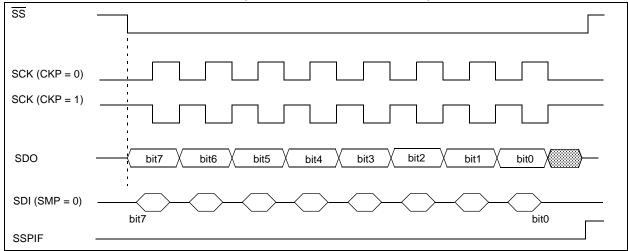

| ER 9-2: | SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)                                                                                                                              |                                                                                                                                                                     |                                                |                                                                           |                                   |                            |               |                            |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------|----------------------------|---------------|----------------------------|--|--|--|

|         | R/W-0                                                                                                                                                                                | R/W-0                                                                                                                                                               | R/W-0                                          | R/W-0                                                                     | R/W-0                             | R/W-0                      | R/W-0         | R/W-0                      |  |  |  |

|         | WCOL                                                                                                                                                                                 | SSPOV                                                                                                                                                               | SSPEN                                          | CKP                                                                       | SSPM3                             | SSPM2                      | SSPM1         | SSPM0                      |  |  |  |

|         | bit 7                                                                                                                                                                                |                                                                                                                                                                     |                                                |                                                                           |                                   |                            |               | bit 0                      |  |  |  |

| bit 7   | WCOL: W                                                                                                                                                                              | /rite Collision                                                                                                                                                     | Detect bit                                     |                                                                           |                                   |                            |               |                            |  |  |  |

|         |                                                                                                                                                                                      | d in software                                                                                                                                                       |                                                | en while it is                                                            | still transmi                     | tting the pr               | evious word   | d (must be                 |  |  |  |

| bit 6   |                                                                                                                                                                                      | Receive Over                                                                                                                                                        | flow Indicate                                  | or bit                                                                    |                                   |                            |               |                            |  |  |  |

| DILO    | In SPI mo                                                                                                                                                                            |                                                                                                                                                                     | now mulcall                                    |                                                                           |                                   |                            |               |                            |  |  |  |

|         | 1 = A new<br>of ove<br>must<br>mode<br>by wr<br>0 = No ov                                                                                                                            | v byte is rece<br>erflow, the da<br>read the SSI<br>, the overflo<br>iting to the S<br>verflow                                                                      | ata in SSPSF<br>PBUF, even i<br>w bit is not s | e SSPBUF re<br>R is lost. Ove<br>if only transm<br>et since each<br>ster. | erflow can on<br>hitting data, to | ly occur in<br>avoid setti | Slave mode    | e. The user<br>. In Master |  |  |  |

|         |                                                                                                                                                                                      | e is received<br>lon't care" in                                                                                                                                     |                                                | SPBUF regi<br>ode. SSPOV                                                  |                                   |                            |               |                            |  |  |  |

| bit 5   | SSPEN: S                                                                                                                                                                             | Synchronous                                                                                                                                                         | Serial Port E                                  | Enable bit                                                                |                                   |                            |               |                            |  |  |  |

|         | 1 = Enabl                                                                                                                                                                            | In SPI mode:<br>1 = Enables serial port and configures SCK, SDO, and SDI as serial port pins<br>0 = Disables serial port and configures these pins as I/O port pins |                                                |                                                                           |                                   |                            |               |                            |  |  |  |

|         | In I <sup>2</sup> C mo                                                                                                                                                               |                                                                                                                                                                     | t and comig                                    |                                                                           |                                   | ( pino                     |               |                            |  |  |  |

|         | <ul> <li>1 = Enables the serial port and configures the SDA and SCL pins as serial port pins</li> <li>0 = Disables serial port and configures these pins as I/O port pins</li> </ul> |                                                                                                                                                                     |                                                |                                                                           |                                   |                            |               |                            |  |  |  |

|         | In both mo                                                                                                                                                                           | odes, when e                                                                                                                                                        | enabled, thes                                  | se pins must                                                              | be properly o                     | configured a               | as input or o | utput.                     |  |  |  |

| bit 4   |                                                                                                                                                                                      | ck Polarity S                                                                                                                                                       |                                                |                                                                           | ,                                 | Ū                          | •             | •                          |  |  |  |

|         | In SPI mode:                                                                                                                                                                         |                                                                                                                                                                     |                                                |                                                                           |                                   |                            |               |                            |  |  |  |

|         | 1 = IDLE :<br>0 = IDLE :                                                                                                                                                             | <ul> <li>1 = IDLE state for clock is a high level (Microwire<sup>®</sup> default)</li> <li>0 = IDLE state for clock is a low level (Microwire alternate)</li> </ul> |                                                |                                                                           |                                   |                            |               |                            |  |  |  |

|         | In I <sup>2</sup> C mod<br>SCK relea<br>1 = Enable                                                                                                                                   | se control                                                                                                                                                          |                                                |                                                                           |                                   |                            |               |                            |  |  |  |

|         | 0 = Holds                                                                                                                                                                            | clock low (cl                                                                                                                                                       | ock stretch -                                  | used to ens                                                               | ure data setu                     | ıp time)                   |               |                            |  |  |  |

| bit 3-0 | SSPM<3:                                                                                                                                                                              | 0>: Synchro                                                                                                                                                         | nous Serial F                                  | Port Mode Se                                                              | lect bits                         |                            |               |                            |  |  |  |

|         | 0000 = SI                                                                                                                                                                            | SSPM<3:0>: Synchronous Serial Port Mode Select bits<br>0000 = SPI Master mode, clock = Fosc/4                                                                       |                                                |                                                                           |                                   |                            |               |                            |  |  |  |

|         |                                                                                                                                                                                      | PI Master mo                                                                                                                                                        |                                                |                                                                           |                                   |                            |               |                            |  |  |  |

|         |                                                                                                                                                                                      | PI Master mo                                                                                                                                                        |                                                |                                                                           | 10                                |                            |               |                            |  |  |  |

|         |                                                                                                                                                                                      |                                                                                                                                                                     |                                                | TMR2 o <u>utp</u> ut<br>CK pin. SS p                                      |                                   | abled.                     |               |                            |  |  |  |

|         |                                                                                                                                                                                      |                                                                                                                                                                     |                                                | CK pin. SS p                                                              |                                   |                            | an be used    | as I/O pin.                |  |  |  |

|         | $0110 = I^2$                                                                                                                                                                         | C Slave mod                                                                                                                                                         | le, 7-bit addr                                 | ess                                                                       |                                   |                            |               | •                          |  |  |  |

|         |                                                                                                                                                                                      | C Slave mod                                                                                                                                                         |                                                |                                                                           |                                   |                            |               |                            |  |  |  |

|         |                                                                                                                                                                                      |                                                                                                                                                                     |                                                | ster mode (S<br>ess with STA                                              |                                   | D hit intorru              | into onoblo   | 4                          |  |  |  |

|         |                                                                                                                                                                                      |                                                                                                                                                                     |                                                | lress with STA                                                            |                                   |                            |               |                            |  |  |  |

|         | Legend:                                                                                                                                                                              |                                                                                                                                                                     |                                                |                                                                           |                                   |                            |               |                            |  |  |  |

|         | R = Read                                                                                                                                                                             | able bit                                                                                                                                                            | W = V                                          | Vritable bit                                                              | U = Unim                          | plemented                  | bit, read as  | '0'                        |  |  |  |

|         |                                                                                                                                                                                      |                                                                                                                                                                     | v                                              |                                                                           | 0 - 01111                         | plomonicu                  | , 1000 05     | ~                          |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

- n = Value at POR

x = Bit is unknown

© 2007 Microchip Technology Inc.

In 10-bit Address mode, two address bytes need to be received by the slave device. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit  $R/\overline{W}$  (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address.

The sequence of events for 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF, and bit UA (SSPSTAT<1>) are set).

- 2. Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF, and UA are set).

- 5. Update the SSPADD register with the first (high) byte of Address, if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated START condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

# 9.3.1.2 Reception

When the R/W bit of the address byte is clear and an address match occurs, the R/W bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then a no Acknowledge (ACK) pulse is given. An overflow condition is indicated if either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON<6>) is set.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

## 9.3.1.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit, and pin RC3/SCK/SCL is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master device must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master device by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 9-7).

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software and the SSPSTAT register is used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the ACK pulse from the masterreceiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not ACK), then the data transfer is complete. When the ACK is latched by the slave device, the slave logic is reset (resets SSPSTAT register) and the slave device then monitors for another occurrence of the START bit. If the SDA line was low (ACK), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, pin RC3/SCK/SCL should be enabled by setting bit CKP.

| TABLE 9-2: | DATA TRANSFER RECEIVED BYTE ACTIO | NS    |

|------------|-----------------------------------|-------|

| IADLE 3-Z. | DATA TRANSFER RECEIVED BITE ACTIO | UND - |

|    | ts as Data<br>s Received |                            |                    | Set bit SSPIF                     |  |  |

|----|--------------------------|----------------------------|--------------------|-----------------------------------|--|--|

| BF | SSPOV                    | $SSPSR \rightarrow SSPBUF$ | Generate ACK Pulse | (SSP Interrupt occurs if enabled) |  |  |

| 0  | 0                        | Yes                        | Yes                | Yes                               |  |  |

| 1  | 0                        | No                         | No                 | Yes                               |  |  |

| 1  | 1                        | No                         | No                 | Yes                               |  |  |

| 0  | 1                        | No                         | No                 | Yes                               |  |  |

**Note 1:** Shaded cells show the conditions where the user software did not properly clear the overflow condition.

## 9.3.2 MASTER MODE OPERATION

Master mode operation is supported in firmware using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle, based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is IDLE and both the S and P bits are clear.

In Master mode operation, the SCL and SDA lines are manipulated in firmware by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So, when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- START condition

- STOP condition

- Data transfer byte transmitted/received

Master mode operation can be done with either the Slave mode IDLE (SSPM3:SSPM0 = 1011), or with the Slave mode active. When both Master mode operation and Slave modes are used, the software needs to differentiate the source(s) of the interrupt.

For more information on Master mode operation, see AN554 - Software Implementation of  $l^2C$  Bus Master.

## 9.3.3 MULTI-MASTER MODE OPERATION

In Multi-Master mode operation, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a RESET or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle, based on the START and STOP conditions. Control of the I<sup>2</sup>C bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is IDLE and both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the STOP condition occurs.

In Multi-Master mode operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the Slave device continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to retransfer the data at a later time.

For more information on Multi-Master mode operation, see AN578 - Use of the SSP Module in the  $l^2C$  Multi-Master Environment.

| ABLE 9-3: REGISTERS ASSOCIATED WITH I C OPERATION |         |                    |                                                   |                            |           |           |          |        |        |                      |                                 |

|---------------------------------------------------|---------|--------------------|---------------------------------------------------|----------------------------|-----------|-----------|----------|--------|--------|----------------------|---------------------------------|

| Address                                           | Name    | Bit 7              | Bit 6                                             | Bit 5                      | Bit 4     | Bit 3     | Bit 2    | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>RESETS |

| 0Bh, 8Bh,<br>10Bh,18Bh                            | INTCON  | GIE                | PEIE                                              | TMR0IE                     | INTE      | RBIE      | TMR0IF   | INTF   | RBIF   | 0000 000x            | 0000 000u                       |

| 0Ch                                               | PIR1    | —                  | ADIF                                              | _                          | _         | SSPIF     | CCP1IF   | TMR2IF | TMR1IF | -0 0000              | 0000 0000                       |

| 8Ch                                               | PIE1    | —                  | ADIE                                              | _                          | _         | SSPIE     | CCP1IE   | TMR2IE | TMR1IE | -00000               | 0000 0000                       |

| 13h                                               | SSPBUF  | Synchron           | ous Seria                                         | I Port Recei               | ve Buffer | /Transmit | Register |        |        | xxxx xxxx            | uuuu uuuu                       |

| 93h                                               | SSPADD  | Synchron           | ous Seria                                         | l Port (l <sup>2</sup> C n | node) Ad  | dress Reg | gister   |        |        | 0000 0000            | 0000 0000                       |

| 14h                                               | SSPCON  | WCOL               | SSPOV                                             | SSPEN                      | CKP       | SSPM3     | SSPM2    | SSPM1  | SSPM0  | 0000 0000            | 0000 0000                       |

| 94h                                               | SSPSTAT | SMP <sup>(1)</sup> | CKE <sup>(1)</sup>                                | D/A                        | Р         | S         | R/W      | UA     | BF     | 0000 0000            | 0000 0000                       |

| 87h                                               | TRISC   | PORTC D            | PORTC Data Direction Register 1111 1111 1111 1111 |                            |           |           |          |        |        |                      |                                 |

TABLE 9-3:

REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in SPI mode.

**Note 1:** Maintain these bits clear in  $I^2C$  mode.

# **10.1** A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 10-2. The source impedance (RS) and the internal sampling switch (RSS) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (RSS) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current).

The maximum recommended impedance for analog sources is 10 k $\Omega$ . After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, TACQ, see the PIC<sup>TM</sup> Mid-Range MCU Reference Manual, (DS33023). In general, however, given a max of 10 k $\Omega$  and at a temperature of 100°C, TACQ will be no more than 16  $\mu$ s.

# 10.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 9.0 TAD per 8-bit conversion. The source of the A/D conversion clock is software selectable. The four possible options for TAD are:

- 2 Tosc

- 8 Tosc

- 32 Tosc

- Internal RC oscillator (2 6 μs)

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time as small as possible, but no less than 1.6  $\mu$ s and not greater than 6.4  $\mu$ s.

Table 10-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

# **10.3 Configuring Analog Port Pins**

The ADCON1, and TRISA registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS<2:0> bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs, will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- 2: Analog levels on any pin that is defined as a digital input (including the AN4:AN0 pins), may cause the input buffer to consume current out of the device specification.

## 10.4 A/D Conversions

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRES register will NOT be updated with the partially completed A/D conversion sample. That is, the ADRES register will continue to contain the value of the last completed conversion (or the last value written to the ADRES register). After the A/D conversion is aborted, a 2 TAD wait is required before the next acquisition is started. After this 2 TAD wait, an acquisition is automatically started on the selected channel. The GO/DONE bit can then be set to start the conversion.

| AD Clock             | AD Clock Source (TAD) |          |  |  |  |  |

|----------------------|-----------------------|----------|--|--|--|--|

| Operation            | ADCS<1:0>             | Max.     |  |  |  |  |

| 2 Tosc               | 00                    | 1.25 MHz |  |  |  |  |

| 8 Tosc               | 01                    | 5 MHz    |  |  |  |  |

| 32 Tosc              | 10                    | 20 MHz   |  |  |  |  |

| RC <sup>(1, 2)</sup> | 11                    | (Note 1) |  |  |  |  |

#### TABLE 10-1: TAD VS. MAXIMUM DEVICE OPERATING FREQUENCIES (STANDARD DEVICES (C))

Note 1: The RC source has a typical TAD time of 4 µs, but can vary between 2-6 µs.

2: When the device frequencies are greater than 1 MHz, the RC A/D conversion clock source is only recommended for SLEEP operation.

NOTES:

#### TABLE 11-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR (FOR DESIGN GUIDANCE ONLY)

| Osc Type | Crystal<br>Freq | Typical Capacitor Values<br>Tested: |       |  |  |  |

|----------|-----------------|-------------------------------------|-------|--|--|--|

|          | печ             | C1                                  | C2    |  |  |  |

| LP       | 32 kHz          | 33 pF                               | 33 pF |  |  |  |

|          | 200 kHz         | 15 pF                               | 15 pF |  |  |  |

| XT       | 200 kHz         | 56 pF                               | 56 pF |  |  |  |

|          | 1 MHz           | 15 pF                               | 15 pF |  |  |  |

|          | 4 MHz           | 15 pF                               | 15 pF |  |  |  |

| HS       | 4 MHz           | 15 pF                               | 15 pF |  |  |  |

|          | 8 MHz           | 15 pF                               | 15 pF |  |  |  |

|          | 20 MHz          | 15 pF                               | 15 pF |  |  |  |

Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

- Note 1: Higher capacitance increases the stability of oscillator, but also increases the start-up time.

- Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- **3:** Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- **4:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

## 11.2.3 RC OSCILLATOR

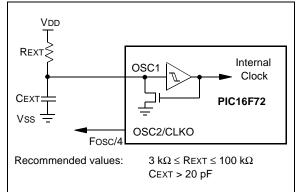

For timing insensitive applications, the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 11-3 shows how the R/C combination is connected to the PIC16F72.

# 11.3 **RESET**

The PIC16F72 differentiates between various kinds of RESET:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during SLEEP

- WDT Reset (during normal operation)

- WDT Wake-up (during SLEEP)

- Brown-out Reset (BOR)

Some registers are not affected in any RESET condition. Their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset (POR), on the MCLR and WDT Reset, on MCLR Reset during SLEEP, and Brown-out Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different RESET situations, as indicated in Table 11-4. These bits are used in software to determine the nature of the RESET. See Table 11-6 for a full description of RESET states of all registers.

A simplified block diagram of the on-chip RESET circuit is shown in Figure 11-4.

# 11.13 Watchdog Timer (WDT)

The Watchdog Timer is a free running, on-chip RC oscillator that does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKI pin. That means that the WDT will run, even if the clock on the OSC1/CLKI and OSC2/CLKO pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit WDTEN (see Section 11.1).

WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler) may be assigned using the OPTION register.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

## FIGURE 11-11: WATCHDOG TIMER BLOCK DIAGRAM

TABLE 11-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                 | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|-----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BOREN <sup>(1)</sup> |       | CP    | PWRTEN <sup>(1)</sup> | WDTEN | FOSC1 | FOSC0 |

| 81h,181h | OPTION       | RBPU  | INTEDG               | TOCS  | T0SE  | PSA                   | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 11-1 for operation of these bits.

| COMF             | Complement f                                                                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                         |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                           |

| Status Affected: | Z                                                                                                                                                         |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' = '0', the<br>result is stored in W. If 'd' = '1', the<br>result is stored back in register 'f'. |

| GOTO             | Unconditional Branch                                                                                                                                                                             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                          |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                               |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                  |

| Status Affected: | None                                                                                                                                                                                             |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>two-cycle instruction. |

| DECF             | Decrement f                                                                                                                                     | INCF             | Increment f                                                                                                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] DECF f,d                                                                                                                              | Syntax:          | [label] INCF f,d                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                      | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                        |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                             | Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                      |

| Status Affected: | Z                                                                                                                                               | Status Affected: | Z                                                                                                                                                                        |

| Description:     | Decrement register 'f'. If 'd' = '0',<br>the result is stored in the W<br>register. If 'd' = '1', the result is<br>stored back in register 'f'. | Description:     | The contents of register 'f' are<br>incremented. If 'd' = '0', the result<br>is placed in the W register. If<br>'d' = '1', the result is placed back<br>in register 'f'. |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                       | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                         |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                           | Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                                                                                                   | Operands:        | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                                                                                                                                                                                       |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                   | Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                     |

| Status Affected: | None                                                                                                                                                                                                                                                                                                         | Status Affected: | None                                                                                                                                                                                                                                                                                                                           |

| Description:     | The contents of register 'f' are decremented. If 'd' = '0', the result is placed in the W register. If 'd' = '1', the result is placed back in register 'f'.<br>If the result is '1', the next instruction is executed. If the result is '0', then a NOP is executed instead, making it a 2 TCY instruction. | Description:     | The contents of register 'f' are<br>incremented. If 'd' = '0', the result<br>is placed in the W register. If<br>'d' = '1', the result is placed back<br>in register 'f'.<br>If the result is '1', the next instruc-<br>tion is executed. If the result is '0',<br>a NOP is executed instead, making<br>it a 2 Tcy instruction. |

# PIC16F72

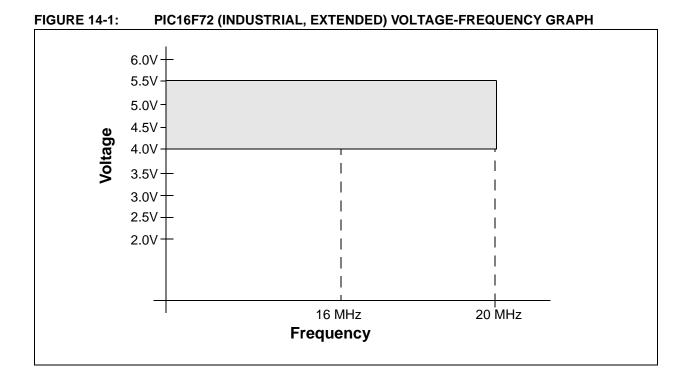

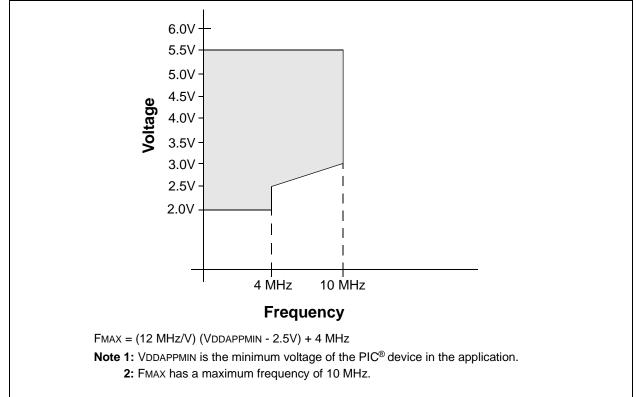

# 14.2 DC Characteristics: PIC16F72 (Industrial, Extended) PIC16LF72 (Industrial)

|              | RACTE | RISTICS                      | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extendedOperating voltage VDD range as described in DC Specification,<br>Section 14.1. |      |          |       |                                                             |

|--------------|-------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|-------------------------------------------------------------|

| Param<br>No. | Sym   | Characteristic               | Min                                                                                                                                                                                                                                                                   | Тур† | Max      | Units | Conditions                                                  |

|              | VIL   | Input Low Voltage            |                                                                                                                                                                                                                                                                       |      |          |       |                                                             |

|              |       | I/O ports                    |                                                                                                                                                                                                                                                                       |      |          |       |                                                             |

| D030         |       | with TTL buffer              | Vss                                                                                                                                                                                                                                                                   | —    | 0.15 Vdd | V     | For entire VDD range                                        |

| D030A        |       |                              | Vss                                                                                                                                                                                                                                                                   |      | 0.8V     | V     | $4.5V \le VDD \le 5.5V$                                     |

| D031         |       | with Schmitt Trigger buffer  | Vss                                                                                                                                                                                                                                                                   | —    | 0.2 Vdd  | V     |                                                             |

| D032         |       | MCLR, OSC1 (in RC mode)      | Vss                                                                                                                                                                                                                                                                   |      | 0.2 Vdd  | V     |                                                             |

| D033         |       | OSC1 (in XT and LP mode)     | Vss                                                                                                                                                                                                                                                                   | —    | 0.3V     | V     | (Note 1)                                                    |

|              |       | OSC1 (in HS mode)            | Vss                                                                                                                                                                                                                                                                   | —    | 0.3 Vdd  | V     | (Note 1)                                                    |

|              | Vih   | Input High Voltage           |                                                                                                                                                                                                                                                                       |      |          |       |                                                             |

|              |       | I/O ports                    |                                                                                                                                                                                                                                                                       |      |          |       |                                                             |

| D040         |       | with TTL buffer              | 2.0                                                                                                                                                                                                                                                                   |      | Vdd      | V     | $4.5V \le VDD \le 5.5V$                                     |

| D040A        |       |                              | 0.25 VDD + 0.8V                                                                                                                                                                                                                                                       |      | Vdd      | V     | For entire VDD range                                        |

| D041         |       | with Schmitt Trigger buffer  | 0.8 Vdd                                                                                                                                                                                                                                                               | —    | Vdd      | V     | For entire VDD range                                        |

| D042         |       | MCLR                         | 0.8 Vdd                                                                                                                                                                                                                                                               | —    | Vdd      | V     |                                                             |

| D042A        |       | OSC1 (in XT and LP mode)     | 1.6V                                                                                                                                                                                                                                                                  |      | Vdd      | V     | (Note 1)                                                    |

|              |       | OSC1 (in HS mode)            | 0.7 Vdd                                                                                                                                                                                                                                                               |      | Vdd      | V     | (Note 1)                                                    |

| D043         |       | OSC1 (in RC mode)            | 0.9 Vdd                                                                                                                                                                                                                                                               | —    | Vdd      | V     |                                                             |

| D070         | IPURB | PORTB Weak Pull-up Current   | 50                                                                                                                                                                                                                                                                    | 250  | 400      | μΑ    | VDD = 5V, VPIN = VSS                                        |

|              | lı∟   | Input Leakage Current (Notes | 2, 3)                                                                                                                                                                                                                                                                 |      |          |       |                                                             |

| D060         |       | I/O ports                    |                                                                                                                                                                                                                                                                       | _    | ±1       | μΑ    | $Vss \le VPIN \le VDD$ , Pin at hi-impedance                |

| D061         |       | MCLR, RA4/T0CKI              | —                                                                                                                                                                                                                                                                     |      | ±5       | μA    | $Vss \le VPIN \le VDD$                                      |

| D063         |       | OSC1                         | —                                                                                                                                                                                                                                                                     | —    | ±5       | μΑ    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC16F72 be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

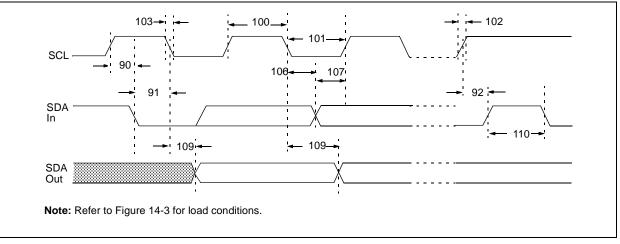

| Param<br>No. | Symbol  | Charact         | teristic     | Min  | Тур | Max | Units | Conditions                         |

|--------------|---------|-----------------|--------------|------|-----|-----|-------|------------------------------------|

| 90*          | TSU:STA | START condition | 100 kHz mode | 4700 | —   | —   | ns    | Only relevant for Repeated         |

|              |         | Setup time      | 400 kHz mode | 600  |     | _   |       | START condition                    |

| 91*          | THD:STA | START condition | 100 kHz mode | 4000 |     | _   |       | After this period, the first clock |

|              |         | Hold time       | 400 kHz mode | 600  |     | _   |       | pulse is generated                 |

| 92*          | Tsu:sto | STOP condition  | 100 kHz mode | 4700 |     | _   | ns    |                                    |

|              |         | Setup time      | 400 kHz mode | 600  |     | _   |       |                                    |

| 93           | THD:STO | STOP condition  | 100 kHz mode | 4000 |     | _   | ns    |                                    |

|              |         | Hold time       | 400 kHz mode | 600  |     | _   |       |                                    |

# TABLE 14-7: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

\* These parameters are characterized but not tested.

# FIGURE 14-15: I<sup>2</sup>C BUS DATA TIMING

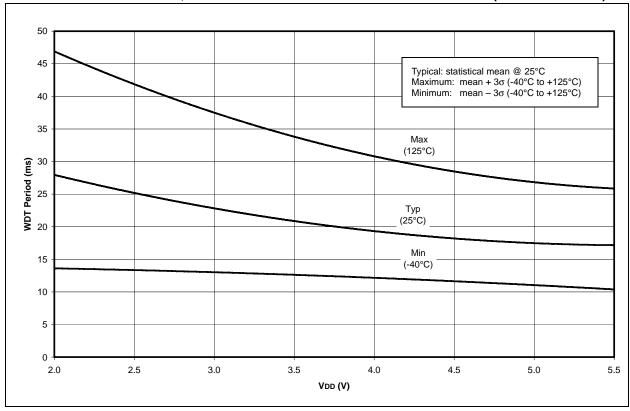

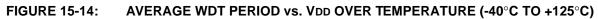

FIGURE 15-13: TYPICAL, MINIMUM AND MAXIMUM WDT PERIOD vs. VDD (-40°C TO +125°C)

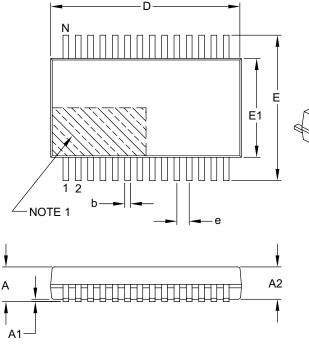

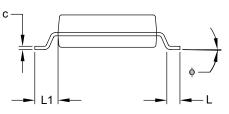

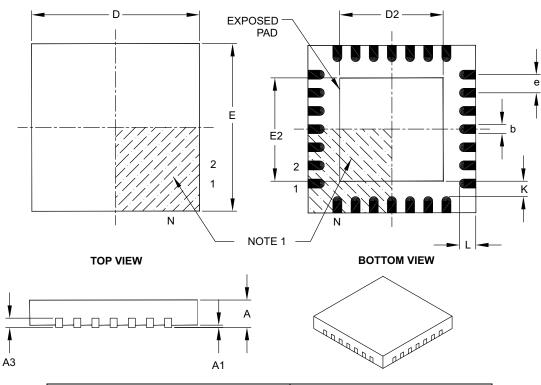

# 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    |          | MILLIMETERS | 3     |  |

|--------------------------|----------|----------|-------------|-------|--|

| Dimension                | n Limits | MIN      | NOM         | MAX   |  |

| Number of Pins           | Ν        |          | 28          |       |  |

| Pitch                    | е        |          | 0.65 BSC    |       |  |

| Overall Height           | А        | -        | -           | 2.00  |  |

| Molded Package Thickness | A2       | 1.65     | 1.75        | 1.85  |  |

| Standoff                 | A1       | 0.05     | -           | -     |  |

| Overall Width            | E        | 7.40     | 7.80        | 8.20  |  |

| Molded Package Width     | E1       | 5.00     | 5.30        | 5.60  |  |

| Overall Length           | D        | 9.90     | 10.20       | 10.50 |  |

| Foot Length              | L        | 0.55     | 0.75        | 0.95  |  |

| Footprint                | L1       | 1.25 REF |             |       |  |

| Lead Thickness           | с        | 0.09     | -           | 0.25  |  |

| Foot Angle               | φ        | 0°       | 4°          | 8°    |  |

| Lead Width               | b        | 0.22     | -           | 0.38  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.