Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI                                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 22                                                                      |

| Program Memory Size        | 3.5KB (2K x 14)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 5x8b                                                                |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                          |

| Supplier Device Package    | 28-SSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f72-e-ss |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address              | Name    | Bit 7      | Bit 6         | Bit 5                     | Bit 4         | Bit 3        | Bit 2           | Bit 1         | Bit 0          | Value on POR, BOR | Details on page: |

|----------------------|---------|------------|---------------|---------------------------|---------------|--------------|-----------------|---------------|----------------|-------------------|------------------|

| Bank 1               |         |            |               |                           |               |              |                 |               |                |                   |                  |

| 80h <sup>(1)</sup>   | INDF    | Addressi   | ng this loca  | tion uses cor             | ntents of FSR | to address   | data memor      | y (not a phys | ical register) | 0000 0000         | 19               |

| 81h                  | OPTION  | RBPU       | INTEDG        | TOCS                      | TOSE          | PSA          | PS2             | PS1           | PS0            | 1111 1111         | 13               |

| 82h <sup>(1)</sup>   | PCL     | Program    | Counter's     | PC) Least S               | ignificant By | te           | -               | -             |                | 0000 0000         | 18               |

| 83h <b>(1)</b>       | STATUS  | IRP        | RP1           | RP0                       | ТО            | PD           | Z               | DC            | С              | 0001 1xxx         | 12               |

| 84h <b>(1)</b>       | FSR     | Indirect [ | Data Memo     | ry Address F              | Pointer       |              |                 |               |                | xxxx xxxx         | 19               |

| 85h                  | TRISA   |            | _             | PORTA Dat                 | a Direction F | Register     |                 |               |                | 11 1111           | 21               |

| 86h                  | TRISB   | PORTB      | Data Direct   | on Register               |               |              |                 |               |                | 1111 1111         | 23               |

| 87h                  | TRISC   | PORTC      | Data Direct   | ion Register              |               |              |                 |               |                | 1111 1111         | 25               |

| 88h                  | _       | Unimple    | mented        |                           |               |              |                 |               |                | _                 | _                |

| 89h                  |         | Unimple    | mented        |                           |               |              |                 |               |                | _                 | _                |

| 8Ah <sup>(1,2)</sup> | PCLATH  |            | —             | _                         | Write Buffer  | for the uppe | er 5 bits of th | ne PC         |                | 0 0000            | 18               |

| 8Bh <sup>(1)</sup>   | INTCON  | GIE        | PEIE          | TMR0IE                    | INTE          | RBIE         | TMR0IF          | INTF          | RBIF           | 0000 000x         | 14               |

| 8Ch                  | PIE1    |            | ADIE          | _                         | —             | SSPIE        | CCP1IE          | TMR2IE        | TMR1IE         | -0 0000           | 15               |

| 8Dh                  | _       | Unimple    | mented        |                           |               |              |                 |               |                | _                 | —                |

| 8Eh                  | PCON    |            | _             | _                         | —             | _            | _               | POR           | BOR            | qq                | 17               |

| 8Fh                  |         | Unimple    | mented        |                           |               |              |                 |               |                | _                 | _                |

| 90h                  |         | Unimple    | mented        |                           |               |              |                 |               |                | _                 | _                |

| 91h                  |         | Unimple    | mented        |                           |               |              |                 |               |                | _                 | _                |

| 92h                  | PR2     | Timer2 F   | Period Regis  | ster                      |               |              |                 |               |                | 1111 1111         | 41               |

| 93h                  | SSPADD  | Synchro    | nous Serial   | Port (I <sup>2</sup> C mo | ode) Address  | Register     | -               | -             |                | 0000 0000         | 43,48            |

| 94h                  | SSPSTAT | SMP        | CKE           | D/A                       | Р             | S            | R/W             | UA            | BF             | 0000 0000         | 44               |

| 95h                  |         | Unimple    | mented        |                           |               |              |                 |               |                | _                 | —                |

| 96h                  | _       | Unimple    | mented        |                           |               |              |                 |               |                | _                 | _                |

| 97h                  |         | Unimple    | mented        |                           |               |              |                 |               |                | _                 | —                |

| 98h                  | _       | Unimple    | mented        |                           |               |              |                 |               |                | _                 | _                |

| 99h                  | _       | Unimple    | mented        |                           |               |              |                 |               |                | _                 | _                |

| 9Ah                  | _       | Unimple    | mented        |                           |               |              |                 |               |                | _                 | _                |

| 9Bh                  | _       | Unimple    | mented        |                           |               |              |                 |               |                | _                 | _                |

| 9Ch                  |         | Unimple    | Jnimplemented |                           |               |              |                 |               |                | _                 | _                |

| 9Dh                  |         | Unimple    | Jnimplemented |                           |               |              |                 |               |                | _                 | _                |

| 9Eh                  | _       | Unimple    | mented        |                           |               |              |                 |               |                |                   |                  |

| 9Fh                  | ADCON1  |            | _             | _                         | _             | _            | PCFG2           | PCFG1         | PCFG0          | 000               | 54               |

#### TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

$\label{eq:Legend: Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. \\ Shaded locations are unimplemented, read as '0'.$

**Note 1:** These registers can be addressed from any bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

**3:** This bit always reads as a '1'.

| Address               | Name   | Bit 7      | Bit 6         | Bit 5         | Bit 4          | Bit 3         | Bit 2           | Bit 1         | Bit 0          | Value on<br>POR, BOR | Details on<br>page: |

|-----------------------|--------|------------|---------------|---------------|----------------|---------------|-----------------|---------------|----------------|----------------------|---------------------|

| Bank 2                | r      | T          |               |               |                |               |                 |               |                |                      | 1                   |

| 100h <sup>(1)</sup>   | INDF   | Addressi   | ng this loca  | tion uses cor | ntents of FSR  | to address of | data memory     | / (not a phys | ical register) | 0000 0000            | 19                  |

| 101h                  | TMR0   | Timer0 M   | lodule's Re   | gister        |                |               |                 |               |                | xxxx xxxx            | 27                  |

| 102h <sup>(1</sup>    | PCL    | Program    | Counter's (   | PC) Least Si  | gnificant Byte | e             |                 |               |                | 0000 0000            | 18                  |

| 103h <b>(1)</b>       | STATUS | IRP        | RP1           | RP0           | TO             | PD            | Z               | DC            | С              | 0001 1xxx            | 12                  |

| 104h <b>(1)</b>       | FSR    | Indirect D | Data Memor    | y Address Po  | ointer         |               |                 |               |                | xxxx xxxx            | 19                  |

| 105h                  | _      | Unimpler   | nented        |               |                |               |                 |               |                | _                    | _                   |

| 106h                  | PORTB  | PORTB I    | Data Latch    | when written: | PORTB pin      | s when read   |                 |               |                | xxxx xxxx            | 23                  |

| 107h                  | —      | Unimpler   | nented        |               |                |               |                 |               |                | —                    | _                   |

| 108h                  | —      | Unimpler   | nented        |               |                |               |                 |               |                | —                    | _                   |

| 109h                  | _      | Unimpler   | nented        |               |                |               |                 |               |                | _                    | _                   |

| 10Ah <sup>(1,2)</sup> | PCLATH | _          |               | —             | Write Buffer   | for the uppe  | r 5 bits of the | e Program C   | ounter         | 0 0000               | 18                  |

| 10Bh <b>(1)</b>       | INTCON | GIE        | PEIE          | TMR0IE        | INTE           | RBIE          | TMR0IF          | INTF          | RBIF           | 0000 000x            | 14                  |

| 10Ch                  | PMDATL | Data Reg   | gister Low B  | syte          | •              | •             | •               |               | •              | xxxx xxxx            | 35                  |

| 10Dh                  | PMADRL | Address    | Register Lo   | w Byte        |                |               |                 |               |                | xxxx xxxx            | 35                  |

| 10Eh                  | PMDATH | —          | _             | Data Regist   | er High Byte   |               |                 |               |                | xx xxxx              | 35                  |

| 10Fh                  | PMADRH |            |               | —             | Address Re     | gister High B | Byte            |               |                | x xxxx               | 35                  |

| Bank 3                |        |            |               |               |                |               |                 |               |                |                      |                     |

| 180h <b>(1)</b>       | INDF   | Addressi   | ng this loca  | tion uses cor | ntents of FSR  | to address of | data memory     | / (not a phys | ical register) | 0000 0000            | 19                  |

| 181h                  | OPTION | RBPU       | INTEDG        | TOCS          | TOSE           | PSA           | PS2             | PS1           | PS0            | 1111 1111            | 13                  |

| 182h <sup>(1)</sup>   | PCL    | Program    | Counter's (   | PC) Least S   | ignificant By  | te            |                 |               |                | 0000 0000            | 18                  |

| 183h <b>(1)</b>       | STATUS | IRP        | RP1           | RP0           | TO             | PD            | Z               | DC            | С              | 0001 1xxx            | 12                  |

| 184h <b>(1)</b>       | FSR    | Indirect D | Data Memor    | y Address Po  | ointer         |               |                 |               |                | xxxx xxxx            | 19                  |

| 185h                  |        | Unimpler   | nented        |               |                |               |                 |               |                | _                    | _                   |

| 186h                  | TRISB  | PORTB I    | Data Directi  | on Register   |                |               |                 |               |                | 1111 1111            | 23                  |

| 187h                  | _      | Unimpler   | nented        |               |                |               |                 |               |                | —                    | _                   |

| 188h                  | _      | Unimpler   | nented        |               |                |               |                 |               |                | _                    | _                   |

| 189h                  |        | Unimpler   | nented        |               |                |               |                 |               |                | _                    | _                   |

| 18Ah <sup>(1,2)</sup> | PCLATH | —          | —             | —             | Write Buffer   | for the uppe  | r 5 bits of the | e Program C   | ounter         | 0 0000               | 18                  |

| 18Bh <b>(1)</b>       | INTCON | GIE        | PEIE          | TMR0IE        | INTE           | RBIE          | TMR0IF          | INTF          | RBIF           | 0000 000x            | 14                  |

| 18Ch                  | PMCON1 | (3)        | —             | —             | —              | —             | —               | —             | RD             | 10                   | 35                  |

| 18Dh                  | —      | Unimpler   | nented        |               |                |               |                 |               |                | —                    | —                   |

| 18Eh                  | —      | Reserved   | d, maintain o | clear         |                |               |                 |               |                | 0000 0000            | _                   |

| 18Fh                  | _      | Reserved   | d, maintain ( | clear         |                |               |                 |               |                | 0000 0000            | _                   |

| TABLE 2-1: SP | PECIAL FUNCTION REGISTER SUMMAR | Y (CONTINUED) |

|---------------|---------------------------------|---------------|

|---------------|---------------------------------|---------------|

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** These registers can be addressed from any bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

**3:** This bit always reads as a '1'.

#### 2.2.2.5 PIR1 Register

This register contains the individual flag bits for the Peripheral interrupts.

- n = Value at POR

| EGISTER 2-5: | PIR1: PERIPHERAL INTERRUPT FLAG REGISTER 1 (ADDRESS 0Ch) |                                                   |                                                                    |                        |               |               |              |        |  |  |

|--------------|----------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------|------------------------|---------------|---------------|--------------|--------|--|--|

|              | U-0                                                      | R/W-0                                             | U-0                                                                | U-0                    | R/W-0         | R/W-0         | R/W-0        | R/W-0  |  |  |

|              |                                                          | ADIF                                              | —                                                                  | —                      | SSPIF         | CCP1IF        | TMR2IF       | TMR1IF |  |  |

|              | bit 7                                                    |                                                   |                                                                    |                        |               |               |              | bit 0  |  |  |

|              |                                                          |                                                   |                                                                    |                        |               |               |              |        |  |  |

| bit 7        | Unimplem                                                 | ented: Read                                       | d as '0'                                                           |                        |               |               |              |        |  |  |

| bit 6        |                                                          |                                                   | nterrupt Flag                                                      | bit                    |               |               |              |        |  |  |

|              |                                                          | ) conversion<br>/D conversio                      | completed                                                          | olete                  |               |               |              |        |  |  |

| bit 5-4      | Unimplem                                                 | ented: Read                                       | d as '0'                                                           |                        |               |               |              |        |  |  |

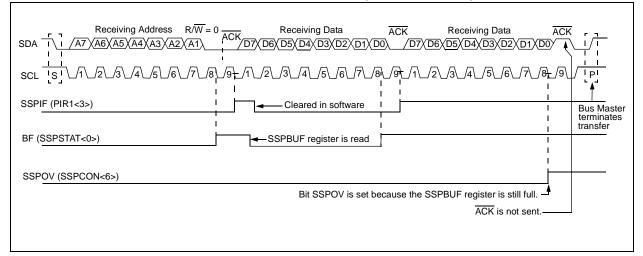

| bit 3        | SSPIF: Sy                                                | nchronous S                                       | Serial Port (S                                                     | SP) Interrupt          | Flag bit      |               |              |        |  |  |

|              | from th<br>The co<br>0 = No SS                           | ne Interrupt S<br>onditions that<br>P interrupt c | condition has<br>Service Routi<br>t will set this<br>condition has | ine.<br>bit are a tran |               |               |              | Ū      |  |  |

| bit 2        | CCP1IF: C                                                | CP1 Interru                                       | pt Flag bit                                                        |                        |               |               |              |        |  |  |

|              |                                                          | R1 register ca                                    | apture occurr<br>capture occu                                      |                        | cleared in s  | oftware)      |              |        |  |  |

|              |                                                          | R1 register co                                    | ompare matc<br>compare mat                                         |                        | must be clea  | ared in softv | vare)        |        |  |  |

|              | <u>PWM mod</u><br>Unused in                              |                                                   |                                                                    |                        |               |               |              |        |  |  |

| bit 1        | TMR2IF: T                                                | MR2 to PR2                                        | 2 Match Inter                                                      | rupt Flag bit          |               |               |              |        |  |  |

|              |                                                          |                                                   | ch occurred (<br>natch occurr                                      |                        | ared in softw | /are)         |              |        |  |  |

| bit 0        | TMR1IF: T                                                | MR1 Overflo                                       | ow Interrupt                                                       | Flag bit               |               |               |              |        |  |  |

|              | 1 = TMR1                                                 | register ove                                      | rflowed (mus<br>not overflow                                       | -                      | in software)  | )             |              |        |  |  |

|              | Legend:                                                  |                                                   |                                                                    |                        |               |               |              | ]      |  |  |

|              | R = Reada                                                | ble bit                                           | W = W                                                              | ritable bit            | U = Unim      | plemented     | bit, read as | '0'    |  |  |

|              | 1                                                        |                                                   |                                                                    |                        |               |               |              |        |  |  |

'1' = Bit is set

x = Bit is unknown

'0' = Bit is cleared

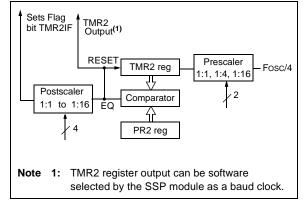

# 6.0 TIMER2 MODULE

The Timer2 module timer has the following features:

- 8-bit timer (TMR2 register)

- 8-bit period register (PR2)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2 match of PR2

- SSP module optional use of TMR2 output to generate clock shift

Timer2 has a control register, shown in Register 6-1. Timer2 can be shut-off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Figure 6-1 is a simplified block diagram of the Timer2 module.

Additional information on timer modules is available in the PIC<sup>™</sup> Mid-Range MCU Reference Manual, (DS33023).

## 6.1 Timer2 Operation

Timer2 can be used as the PWM time-base for PWM mode of the CCP module.

The TMR2 register is readable and writable, and is cleared on any device RESET.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

## 6.2 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- A write to the TMR2 register

- A write to the T2CON register

- Any device RESET (Power-on Reset, MCLR , WDT Reset, or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

## 6.3 Timer2 Interrupt

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon RESET.

### 6.4 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module, which optionally uses it to generate a shift clock.

#### FIGURE 6-1: TIMER2 BLOCK DIAGRAM

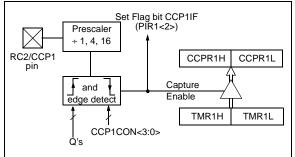

## 8.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as:

- · Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

#### 8.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 is configured as an out-     |

|-------|----------------------------------------------|

|       | put, a write to the port can cause a capture |

|       | condition.                                   |

#### FIGURE 8-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 8.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 8.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF, following any such change in Operating mode.

#### 8.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any RESET will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 8-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 8-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ; Turn CCP module off   |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ; Load the W reg with   |

|       |             | ; the new prescaler     |

|       |             | ; mode value and CCP ON |

| MOVWF | CCP1CON     | ; Load CCP1CON with     |

|       |             | ; this value            |

|       |             |                         |

| ER 9-2: | SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)                                                                                                             |                                                                                                |                                                |                                                                           |                                   |                            |                |                            |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------|----------------------------|----------------|----------------------------|--|--|--|

|         | R/W-0                                                                                                                                                               | R/W-0                                                                                          | R/W-0                                          | R/W-0                                                                     | R/W-0                             | R/W-0                      | R/W-0          | R/W-0                      |  |  |  |

|         | WCOL                                                                                                                                                                | SSPOV                                                                                          | SSPEN                                          | CKP                                                                       | SSPM3                             | SSPM2                      | SSPM1          | SSPM0                      |  |  |  |

|         | bit 7                                                                                                                                                               |                                                                                                |                                                |                                                                           |                                   |                            |                | bit 0                      |  |  |  |

| bit 7   | WCOL: W                                                                                                                                                             | /rite Collision                                                                                | Detect bit                                     |                                                                           |                                   |                            |                |                            |  |  |  |

|         |                                                                                                                                                                     | d in software                                                                                  |                                                | en while it is                                                            | still transmi                     | tting the pr               | evious word    | d (must be                 |  |  |  |

| bit 6   |                                                                                                                                                                     | Receive Over                                                                                   | flow Indicate                                  | or bit                                                                    |                                   |                            |                |                            |  |  |  |

| DILO    | In SPI mo                                                                                                                                                           |                                                                                                | now mulcall                                    |                                                                           |                                   |                            |                |                            |  |  |  |

|         | 1 = A new<br>of ove<br>must<br>mode<br>by wr<br>0 = No ov                                                                                                           | v byte is rece<br>erflow, the da<br>read the SSI<br>, the overflo<br>iting to the S<br>verflow | ata in SSPSF<br>PBUF, even i<br>w bit is not s | e SSPBUF re<br>R is lost. Ove<br>if only transm<br>et since each<br>ster. | erflow can on<br>hitting data, to | ly occur in<br>avoid setti | Slave mode     | e. The user<br>. In Master |  |  |  |

|         |                                                                                                                                                                     | e is received<br>lon't care" in                                                                |                                                | SPBUF regi<br>ode. SSPOV                                                  |                                   |                            |                |                            |  |  |  |

| bit 5   | SSPEN: S                                                                                                                                                            | Synchronous                                                                                    | Serial Port E                                  | Enable bit                                                                |                                   |                            |                |                            |  |  |  |

|         | In SPI mode:<br>1 = Enables serial port and configures SCK, SDO, and SDI as serial port pins<br>0 = Disables serial port and configures these pins as I/O port pins |                                                                                                |                                                |                                                                           |                                   |                            |                |                            |  |  |  |

|         | In l <sup>2</sup> C mode:                                                                                                                                           |                                                                                                |                                                |                                                                           |                                   |                            |                |                            |  |  |  |

|         | 1 = Enabl                                                                                                                                                           | es the serial                                                                                  |                                                | figures the S<br>ures these pi                                            |                                   |                            | rial port pins | 5                          |  |  |  |

|         | In both mo                                                                                                                                                          | odes, when e                                                                                   | enabled, thes                                  | se pins must                                                              | be properly o                     | configured a               | as input or o  | utput.                     |  |  |  |

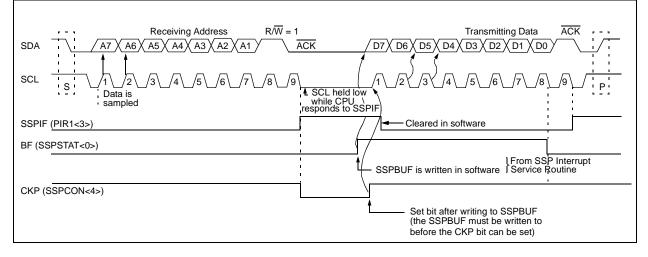

| bit 4   |                                                                                                                                                                     |                                                                                                |                                                |                                                                           | ,                                 | Ū                          | •              | ·                          |  |  |  |

|         | CKP: Clock Polarity Select bit<br>In SPI mode:                                                                                                                      |                                                                                                |                                                |                                                                           |                                   |                            |                |                            |  |  |  |

|         | <ul> <li>1 = IDLE state for clock is a high level (Microwire<sup>®</sup> default)</li> <li>0 = IDLE state for clock is a low level (Microwire alternate)</li> </ul> |                                                                                                |                                                |                                                                           |                                   |                            |                |                            |  |  |  |

|         | In I <sup>2</sup> C mod<br>SCK relea<br>1 = Enable                                                                                                                  | se control                                                                                     |                                                |                                                                           |                                   |                            |                |                            |  |  |  |

|         | 0 = Holds                                                                                                                                                           | clock low (cl                                                                                  | ock stretch -                                  | used to ens                                                               | ure data setu                     | ıp time)                   |                |                            |  |  |  |

| bit 3-0 | SSPM<3:                                                                                                                                                             | 0>: Synchro                                                                                    | nous Serial F                                  | Port Mode Se                                                              | lect bits                         |                            |                |                            |  |  |  |

|         | 0000 = SPI Master mode, clock = FOSC/4                                                                                                                              |                                                                                                |                                                |                                                                           |                                   |                            |                |                            |  |  |  |

|         |                                                                                                                                                                     | 0001 = SPI Master mode, clock = Fosc/16                                                        |                                                |                                                                           |                                   |                            |                |                            |  |  |  |

|         |                                                                                                                                                                     | PI Master mo                                                                                   |                                                |                                                                           | 10                                |                            |                |                            |  |  |  |

|         |                                                                                                                                                                     |                                                                                                |                                                | TMR2 o <u>utp</u> ut<br>CK pin. SS p                                      |                                   | abled.                     |                |                            |  |  |  |

|         |                                                                                                                                                                     |                                                                                                |                                                | CK pin. SS p                                                              |                                   |                            | an be used     | as I/O pin.                |  |  |  |

|         | $0110 = I^2$                                                                                                                                                        | C Slave mod                                                                                    | le, 7-bit addr                                 | ess                                                                       |                                   |                            |                | •                          |  |  |  |

|         |                                                                                                                                                                     | C Slave mod                                                                                    |                                                |                                                                           |                                   |                            |                |                            |  |  |  |

|         |                                                                                                                                                                     |                                                                                                |                                                | ster mode (S<br>ess with STA                                              |                                   | D hit intorru              | unto onoblo    | 4                          |  |  |  |

|         |                                                                                                                                                                     |                                                                                                |                                                | lress with STA                                                            |                                   |                            |                |                            |  |  |  |

|         | Legend:                                                                                                                                                             |                                                                                                |                                                |                                                                           |                                   |                            |                |                            |  |  |  |

|         | R = Read                                                                                                                                                            | able bit                                                                                       | W = V                                          | Vritable bit                                                              | U = Unim                          | plemented                  | bit, read as   | '0'                        |  |  |  |

|         |                                                                                                                                                                     |                                                                                                | vv — v                                         |                                                                           | 0 - 01111                         | plomonicu                  | , 1000 05      | ~                          |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

- n = Value at POR

x = Bit is unknown

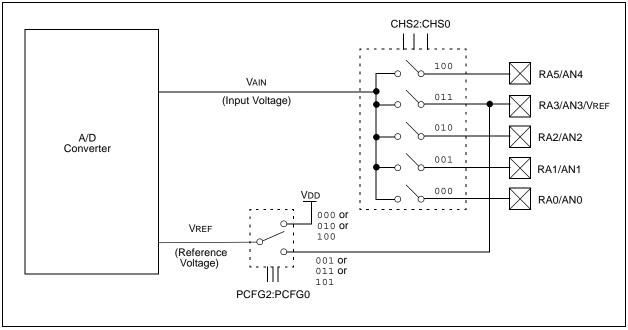

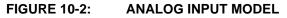

## **10.1** A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 10-2. The source impedance (RS) and the internal sampling switch (RSS) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (RSS) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current).

The maximum recommended impedance for analog sources is 10 k $\Omega$ . After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, TACQ, see the PIC<sup>TM</sup> Mid-Range MCU Reference Manual, (DS33023). In general, however, given a max of 10 k $\Omega$  and at a temperature of 100°C, TACQ will be no more than 16  $\mu$ s.

## 10.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 9.0 TAD per 8-bit conversion. The source of the A/D conversion clock is software selectable. The four possible options for TAD are:

- 2 Tosc

- 8 Tosc

- 32 Tosc

- Internal RC oscillator (2 6 μs)

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time as small as possible, but no less than 1.6  $\mu$ s and not greater than 6.4  $\mu$ s.

Table 10-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

## **10.3 Configuring Analog Port Pins**

The ADCON1, and TRISA registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS<2:0> bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs, will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- 2: Analog levels on any pin that is defined as a digital input (including the AN4:AN0 pins), may cause the input buffer to consume current out of the device specification.

### 10.4 A/D Conversions

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRES register will NOT be updated with the partially completed A/D conversion sample. That is, the ADRES register will continue to contain the value of the last completed conversion (or the last value written to the ADRES register). After the A/D conversion is aborted, a 2 TAD wait is required before the next acquisition is started. After this 2 TAD wait, an acquisition is automatically started on the selected channel. The GO/DONE bit can then be set to start the conversion.

| AD Clock             | AD Clock Source (TAD) |          |  |  |  |

|----------------------|-----------------------|----------|--|--|--|

| Operation            | ADCS<1:0>             | Max.     |  |  |  |

| 2 Tosc               | 00                    | 1.25 MHz |  |  |  |

| 8 Tosc               | 01                    | 5 MHz    |  |  |  |

| 32 Tosc              | 10                    | 20 MHz   |  |  |  |

| RC <sup>(1, 2)</sup> | 11                    | (Note 1) |  |  |  |

#### TABLE 10-1: TAD VS. MAXIMUM DEVICE OPERATING FREQUENCIES (STANDARD DEVICES (C))

Note 1: The RC source has a typical TAD time of 4 µs, but can vary between 2-6 µs.

2: When the device frequencies are greater than 1 MHz, the RC A/D conversion clock source is only recommended for SLEEP operation.

#### 11.11.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge triggered, either rising, if bit INTEDG (OPTION<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 11.14 for details on SLEEP mode.

#### 11.11.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit TMR0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit TMR0IE (INTCON<5>) (see Section 4.0).

#### 11.11.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>) (see Section 3.2).

## 11.12 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (i.e., W, STATUS registers). This will have to be implemented in software, as shown in Example 11-1.

For the PIC16F72 device, the register W\_TEMP must be defined in both banks 0 and 1 and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 20h in bank 0, it must also be defined at A0h in bank 1). The register STATUS\_TEMP is only defined in bank 0.

EXAMPLE 11-1: SAVING STATUS, W AND PCLATH REGISTERS IN RAM

| MOVWF  | W_TEMP        | ;Copy W to TEMP register                                |

|--------|---------------|---------------------------------------------------------|

| SWAPF  | STATUS,W      | ;Swap status to be saved into W                         |

| CLRF   | STATUS        | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

| MOVWF  | STATUS_TEMP   | ;Save status to bank zero STATUS_TEMP register          |

| :      |               |                                                         |

| :(ISR) |               | ;Insert user code here                                  |

| :      |               |                                                         |

| SWAPF  | STATUS_TEMP,W | ;Swap STATUS_TEMP register into W                       |

|        |               | ;(sets bank to original state)                          |

| MOVWF  | STATUS        | ;Move W into STATUS register                            |

| SWAPF  | W_TEMP,F      | ;Swap W_TEMP                                            |

| SWAPF  | W_TEMP,W      | ;Swap W_TEMP into W                                     |

|        |               |                                                         |

# 13.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PIC MCUs and can be used to develop for this and other PIC microcontrollers. The MPLAB ICD utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>TM</sup> protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time.

## 13.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In stand-alone mode, the PRO MATE II device programmer can read, verify, or program PIC devices. It can also set code protection in this mode.

## 13.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PIC devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

## 13.11 PICDEM 1 Low Cost PIC Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44, All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

## 13.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the  $I^2C^{TM}$  bus and separate headers for connection to an LCD module and a keypad.

| Param<br>No. | Sym  | Characteristic                     |           | Min        | Тур†       | Мах                | Units                                                                        | Conditions                                                                   |

|--------------|------|------------------------------------|-----------|------------|------------|--------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| A01          | Nr   | Resolution                         | PIC16F72  | _          | _          | 8 bits             | bit                                                                          | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$         |

|              |      |                                    | PIC16LF72 | —          | _          | 8 bits             | bit                                                                          | VREF = VDD = 2.2V                                                            |

| A02          | Eabs | Total Absolute Er                  | ror       | _          | _          | < ± 1              | LSb                                                                          | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$         |

| A03          | EIL  | Integral Linearity                 | Error     | —          | _          | < ± 1              | LSb                                                                          | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$         |

| A04          | Edl  | Differential Linear                | —         | _          | < ± 1      | LSb                | $\begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$ |                                                                              |

| A05          | Efs  | Full Scale Error                   |           | —          | _          | < ± 1              | LSb                                                                          | $\begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$ |

| A06          | EOFF | Offset Error                       |           | —          | —          | < ± 1              | LSb                                                                          | $\begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$ |

| A10          | —    | Monotonicity (No                   | te 3)     | —          | guaranteed | —                  | —                                                                            | $VSS \leq VAIN \leq VREF$                                                    |

| A20          | Vref | Reference Voltag                   | e         | 2.5<br>2.2 | _          | Vdd+0.3<br>Vdd+0.3 | V<br>V                                                                       | -40°C to +85°C<br>0°C to +85°C                                               |

| A25          | VAIN | Analog Input Volt                  | age       | Vss - 0.3  | _          | VREF + 0.3         | V                                                                            |                                                                              |

| A30          | ZAIN | Recommended Ir<br>Analog Voltage S |           | —          | _          | 10.0               | kΩ                                                                           |                                                                              |

| A40          | IAD  | A/D Conversion                     | PIC16F72  | —          | 180        | —                  | μA                                                                           | Average current                                                              |

|              |      | Current (VDD)                      | PIC16LF72 | —          | 90         | —                  | μA                                                                           | consumption when A/D<br>is on <b>(Note 1)</b> .                              |

| A50          | IREF | VREF input current (Note 2)        |           | N/A<br>—   |            | ± 5<br>500         | μΑ<br>μΑ                                                                     | During VAIN acquisition.<br>During A/D Conversion<br>cycle.                  |

#### TABLE 14-9: A/D CONVERTER CHARACTERISTICS: PIC16F72 (INDUSTRIAL) PIC16LF72 (INDUSTRIAL)

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from the RA3 pin or the VDD pin, whichever is selected as a reference input.

**3:** The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

NOTES:

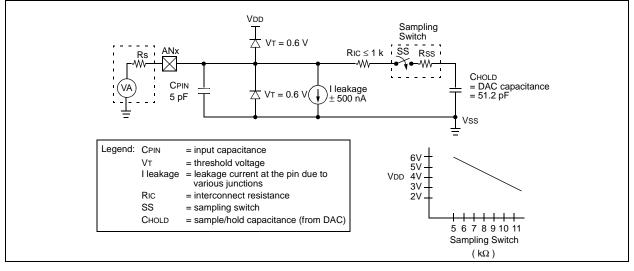

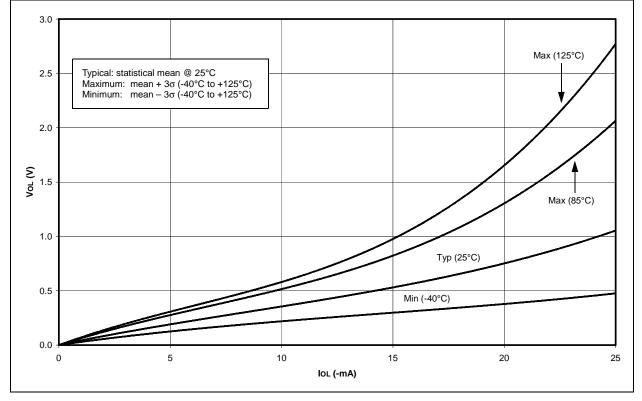

FIGURE 15-17: TYPICAL, MINIMUM AND MAXIMUM Vol vs. lol (VDD = 5V, -40°C TO +125°C)

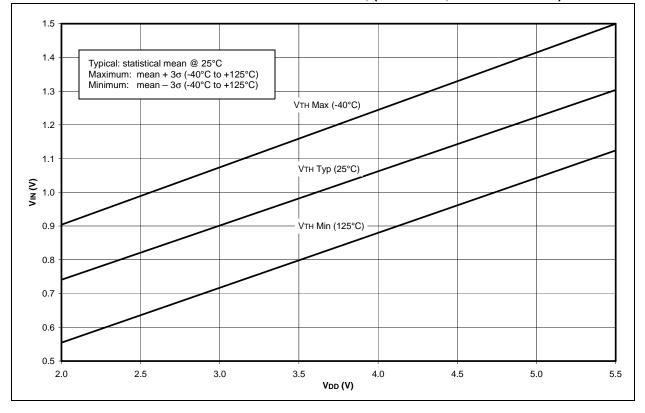

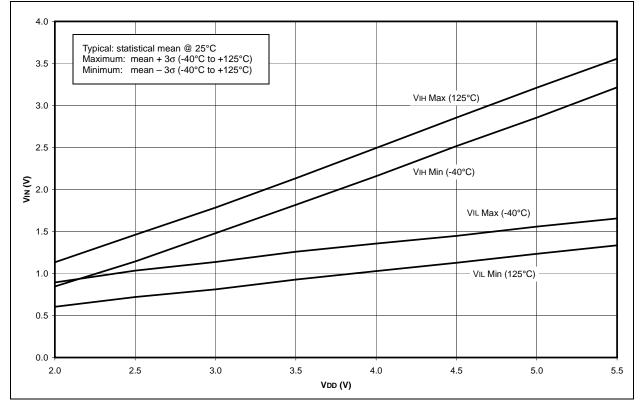

#### FIGURE 15-19: MINIMUM AND MAXIMUM VIN vs. VDD, (TTL INPUT, -40°C TO +125°C)

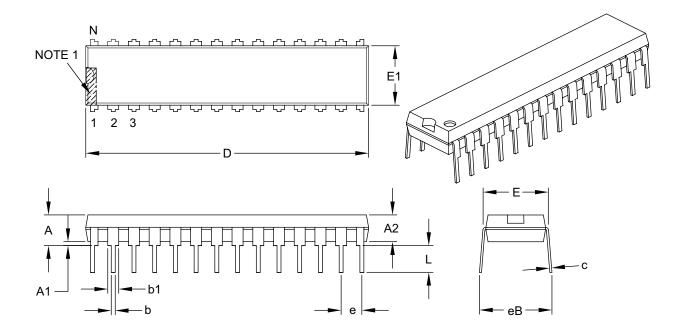

# 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |       |          |       |  |

|----------------------------|----------|-------|----------|-------|--|

| Dimensior                  | n Limits | MIN   | NOM      | MAX   |  |

| Number of Pins             | Ν        |       | 28       |       |  |

| Pitch                      | е        |       | .100 BSC |       |  |

| Top to Seating Plane       | Α        | -     | -        | .200  |  |

| Molded Package Thickness   | A2       | .120  | .135     | .150  |  |

| Base to Seating Plane      | A1       | .015  | -        | -     |  |

| Shoulder to Shoulder Width | E        | .290  | .310     | .335  |  |

| Molded Package Width       | E1       | .240  | .285     | .295  |  |

| Overall Length             | D        | 1.345 | 1.365    | 1.400 |  |

| Tip to Seating Plane       | L        | .110  | .130     | .150  |  |

| Lead Thickness             | С        | .008  | .010     | .015  |  |

| Upper Lead Width           | b1       | .040  | .050     | .070  |  |

| Lower Lead Width           | b        | .014  | .018     | .022  |  |

| Overall Row Spacing §      | eВ       | -     | -        | .430  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

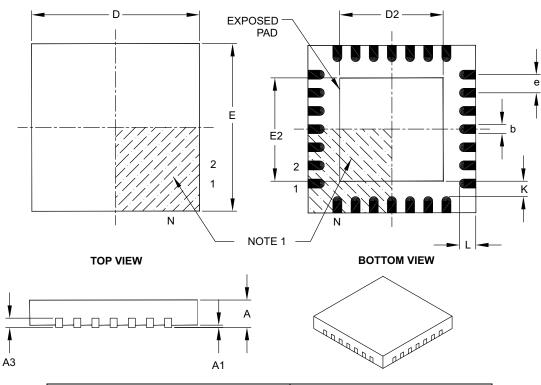

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

| Units                  |          | MILLIMETERS |      |      |

|------------------------|----------|-------------|------|------|

| Dimension              | n Limits | MIN         | NOM  | MAX  |

| Number of Pins         | Ν        | 28          |      |      |

| Pitch                  | е        | 0.65 BSC    |      |      |

| Overall Height         | А        | 0.80        | 0.90 | 1.00 |

| Standoff               | A1       | 0.00        | 0.02 | 0.05 |

| Contact Thickness      | A3       | 0.20 REF    |      |      |

| Overall Width          | Е        | 6.00 BSC    |      |      |

| Exposed Pad Width      | E2       | 3.65        | 3.70 | 4.20 |

| Overall Length         | D        | 6.00 BSC    |      |      |

| Exposed Pad Length     | D2       | 3.65        | 3.70 | 4.20 |

| Contact Width          | b        | 0.23        | 0.30 | 0.35 |

| Contact Length         | L        | 0.50        | 0.55 | 0.70 |

| Contact-to-Exposed Pad | K        | 0.20        | -    | -    |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

NOTES:

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.          | <u>x /xx xxx</u>                                                                                           | Examples:                                                                                                                                                                            |

|-------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device            | Temperature Package Pattern<br>Range                                                                       | a) PIC16F72-04I/SO = Industrial Temp.,<br>SOIC package, normal VDD limits                                                                                                            |

| Device            | PIC16F72: Standard VDD range<br>PIC16F72T: (Tape and Reel)<br>PIC16LF72: Extended VDD range                | <ul> <li>b) PIC16LF72-20I/SS = Industrial Temp.,<br/>SSOP package, extended VDD limits</li> <li>c) PIC16F72-20I/ML = Industrial Temp.,<br/>QFN package, normal VDD limits</li> </ul> |

| Temperature Range | $- = 0^{\circ}C \text{ to } +70^{\circ}C$<br>I = -40^{\circ}C to +85^{\circ}C                              |                                                                                                                                                                                      |

| Package           | $\begin{array}{rcl} SO & = & SOIC \\ SS & = & SSOP \\ ML & = & QFN \\ P & = & PDIP \end{array}$            |                                                                                                                                                                                      |

| Pattern           | QTP, SQTP, ROM Code (factory specified) or<br>Special Requirements. Blank for OTP and<br>Windowed devices. |                                                                                                                                                                                      |

\* JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type.