#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI                                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 22                                                                      |

| Program Memory Size        | 3.5KB (2K x 14)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 5x8b                                                                |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                          |

| Supplier Device Package    | 28-SSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f72-i-ss |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.6 PCON Register

| Note: | Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate inter- |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | rupt flag bits are clear prior to enabling an interrupt.                                                                                                                                                              |

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR), a Brown-out Reset, an external MCLR Reset and WDT Reset.

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent RESETS to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a 'don't care' and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BOREN bit in the Configuration word).

# REGISTER 2-6: PCON: POWER CONTROL REGISTER (ADDRESS 8Eh)

| U-0      | U-0                        | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-x |  |  |  |  |

|----------|----------------------------|-----|-----|-----|-----|-------|-------|--|--|--|--|

| _        | _                          | _   | _   | _   | —   | POR   | BOR   |  |  |  |  |

| bit 7    |                            |     |     |     |     |       | bit 0 |  |  |  |  |

|          |                            |     |     |     |     |       |       |  |  |  |  |

| Unimplen | Unimplemented: Read as '0' |     |     |     |     |       |       |  |  |  |  |

| bit 1 | POR: Power-on Reset Status bit |

|-------|--------------------------------|

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0

bit 7-2

**BOR:** Brown-out Reset Status bit 1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the Application Note, *"Implementing a Table Read"* (AN556).

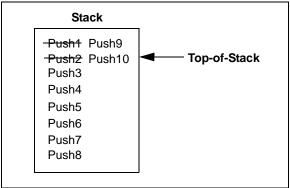

# 2.3.2 STACK

The stack allows a combination of up to eight program calls and interrupts to occur. The stack contains the return address from this branch in program execution.

Mid-range devices have an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSH'd onto the stack when a CALL instruction is executed, or an interrupt causes a branch. The stack is POP'd in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not modified when the stack is PUSH'd or POP'd.

After the stack has been PUSH'd eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on). An example of the overwriting of the stack is shown in Figure 2-4.

#### FIGURE 2-4: STACK MODIFICATION

Note 1: There are no status bits to indicate stack overflow or stack underflow conditions.

2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

# 2.4 Program Memory Paging

The CALL and GOTO instructions provide 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper two bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the return instructions (which POPs the address from the stack).

| Note: | The PIC16F72 device ignores the paging      |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|--|

|       | bit PCLATH<4:3>. The use of                 |  |  |  |  |  |  |  |  |

|       | PCLATH<4:3> as a general purpose read/      |  |  |  |  |  |  |  |  |

|       | write bit is not recommended, since this    |  |  |  |  |  |  |  |  |

|       | may affect upward compatibility with future |  |  |  |  |  |  |  |  |

|       | products.                                   |  |  |  |  |  |  |  |  |

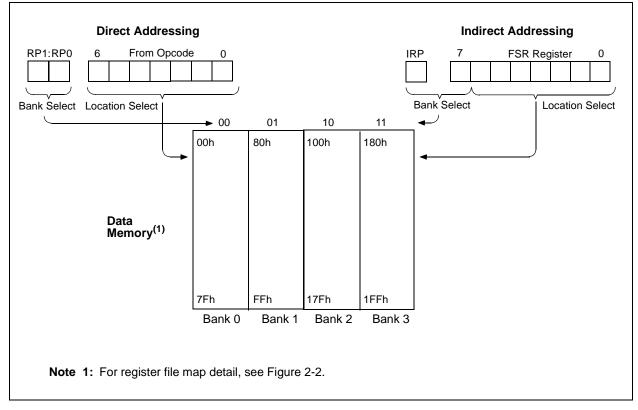

# 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-1.

| EXAMPLE 2-1: | INDIRECT | ADDRESSING |

|--------------|----------|------------|

|              |          |            |

| NEXT     | movwf<br>clrf<br>incf<br>btfss | FSR<br>INDF<br>FSR<br>FSR,4 | <pre>;initialize pointer ;to RAM ;clear INDF register ;inc pointer ;all done? ;NO, clear next</pre> |

|----------|--------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------|

| CONTINUE | :                              |                             | ;YES, continue                                                                                      |

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-5.

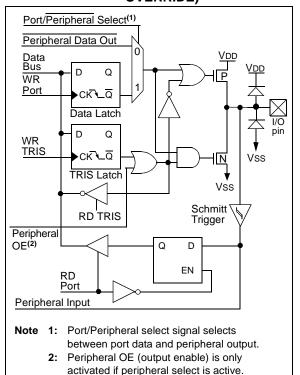

# 3.3 PORTC and the TRISC Register

PORTC is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

PORTC is multiplexed with several peripheral functions (Table 3-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

EXAMPLE 3-3: INITIALIZING PORTC

| BANKSEL | PORTC | ; Select Bank for PORTC |

|---------|-------|-------------------------|

|         |       |                         |

| CLRF    | PORTC | ; Initialize PORTC by   |

|         |       | ; clearing output       |

|         |       | ; data latches          |

| BANKSEL | TRISC | ; Select Bank for TRISC |

| MOVLW   | 0xCF  | ; Value used to         |

|         |       | ; initialize data       |

|         |       | ; direction             |

| MOVWF   | TRISC | ; Set RC<3:0> as inputs |

|         |       | ; RC<5:4> as outputs    |

|         |       | ; RC<7:6> as inputs     |

|         |       |                         |

# FIGURE 3-5:

#### PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

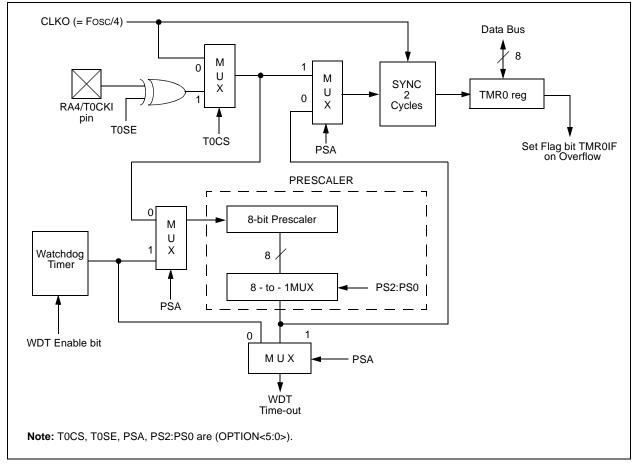

# 4.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

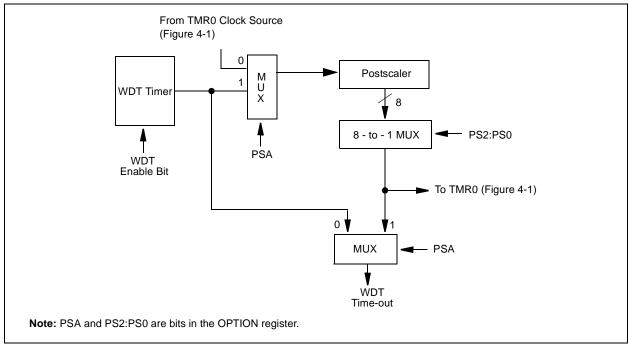

Figure 4-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

Additional information on the Timer0 module is available in the PIC<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

# 4.1 Timer0 Operation

Timer mode is selected by clearing bit T0CS (OPTION<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION<5>). In Counter mode, Timer0 will increment, either on every rising or falling edge of pin RA4/ T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit T0SE (OPTION<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 4.3.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. Section 4.4 details the operation of the prescaler.

# 4.2 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit TMR0IF (INTCON<2>). The interrupt can be masked by clearing bit TMR0IE (INTCON<5>). Bit TMR0IF must be cleared in software by the Timer0 module Interrupt Service Routine, before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut-off during SLEEP.

#### FIGURE 4-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

# 7.0 READING PROGRAM MEMORY

The FLASH Program Memory is readable during normal operation over the entire VDD range. It is indirectly addressed through Special Function Registers (SFR). Up to 14-bit wide numbers can be stored in memory for use as calibration parameters, serial numbers, packed 7-bit ASCII, etc. Executing a program memory location containing data that forms an invalid instruction results in a NOP.

There are five SFRs used to read the program and memory:

- PMCON1

- PMDATL

- PMDATH

- PMADRL

- PMADRH

The program memory allows word reads. Program memory access allows for checksum calculation and reading calibration tables.

When interfacing to the program memory block, the PMDATH:PMDATL registers form a two-byte word, which holds the 14-bit data for reads. The PMADRH:PMADRL registers form a two-byte word, which holds the 13-bit address of the FLASH location being accessed. This device has up to 2K words of program FLASH, with an address range from 0h to 07FFh. The unused upper bits PMDATH<7:6> and PMADRH<7:5> are not implemented and read as zeros.

R = Readable bit

'1' = Bit is set

# 7.1 PMADR

The address registers can address up to a maximum of 8K words of program FLASH.

When selecting a program address value, the MSByte of the address is written to the PMADRH register and the LSByte is written to the PMADRL register. The upper MSbits of PMADRH must always be clear.

# 7.2 PMCON1 Register

PMCON1 is the control register for memory accesses.

The control bit RD initiates read operations. This bit cannot be cleared, only set, in software. It is cleared in hardware at the completion of the read operation.

## REGISTER 7-1: PMCON1: PROGRAM MEMORY CONTROL REGISTER 1 (ADDRESS 18Ch)

|                                                                                                                 |        |       | •••••       |              |        |     | ···,  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|--------|-------|-------------|--------------|--------|-----|-------|--|--|--|--|

| R-1                                                                                                             | U-0    | U-0   | U-0         | U-0          | U-0    | U-0 | R/S-0 |  |  |  |  |

| reserved                                                                                                        | _      | —     | _           | —            | —      | —   | RD    |  |  |  |  |

| bit 7 bit 0                                                                                                     |        |       |             |              |        |     |       |  |  |  |  |

|                                                                                                                 |        |       |             |              |        |     |       |  |  |  |  |

| Reserved: Read as '1'                                                                                           |        |       |             |              |        |     |       |  |  |  |  |

| Unimplemented: Read as '0'                                                                                      |        |       |             |              |        |     |       |  |  |  |  |

| RD: Read Control bit                                                                                            |        |       |             |              |        |     |       |  |  |  |  |

| 1 = Initiates a FLASH read, RD is cleared in hardware. The RD bit can only be set (not cleared)<br>in software. |        |       |             |              |        |     |       |  |  |  |  |

| 0 = Does not initiate a FLASH read                                                                              |        |       |             |              |        |     |       |  |  |  |  |

|                                                                                                                 |        |       |             |              |        |     |       |  |  |  |  |

| Legend:                                                                                                         |        |       |             |              |        |     |       |  |  |  |  |

| W = Writab                                                                                                      | le bit | U = l | Jnimplement | ed bit, read | as '0' |     |       |  |  |  |  |

S = Settable bit

'0' = Bit is cleared

bit 7 bit 6-1 bit 0

-n = Value at POR

x = Bit is unknown

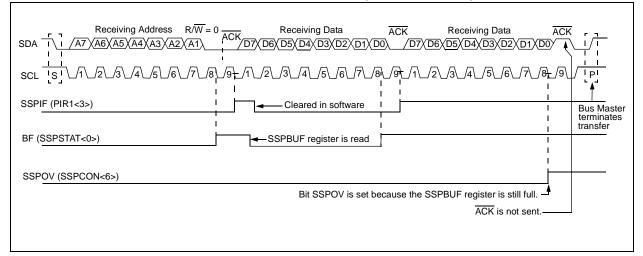

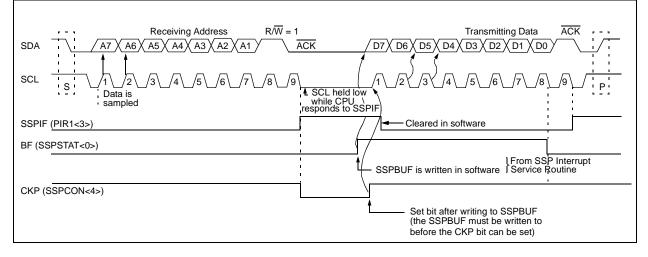

# 9.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

# 9.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

An overview of I<sup>2</sup>C operations and additional information on the SSP module can be found in the PIC<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

Refer to Application Note AN578, "Use of the SSP Module in the  $I^2C$  Multi-Master Environment."

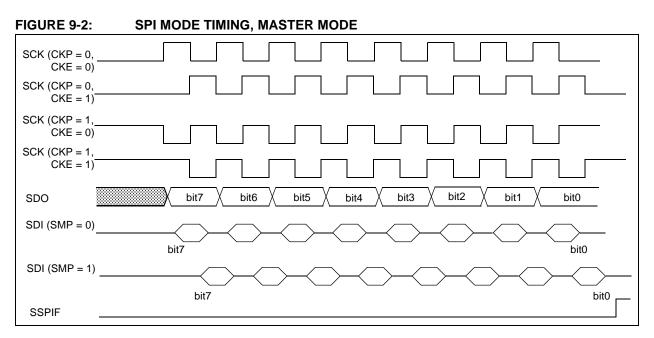

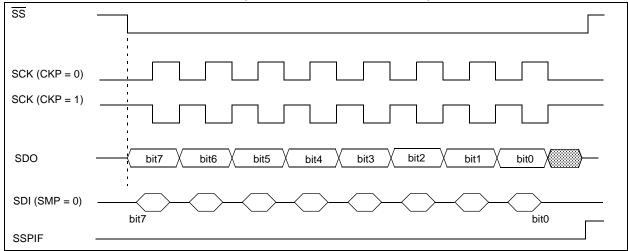

# 9.2 SPI Mode

This section contains register definitions and operational characteristics of the SPI module.

SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS) RA5/AN4/SS

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (IDLE state of SCK)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

© 2007 Microchip Technology Inc.

#### 11.11.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge triggered, either rising, if bit INTEDG (OPTION<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 11.14 for details on SLEEP mode.

#### 11.11.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit TMR0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit TMR0IE (INTCON<5>) (see Section 4.0).

#### 11.11.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>) (see Section 3.2).

# 11.12 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (i.e., W, STATUS registers). This will have to be implemented in software, as shown in Example 11-1.

For the PIC16F72 device, the register W\_TEMP must be defined in both banks 0 and 1 and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 20h in bank 0, it must also be defined at A0h in bank 1). The register STATUS\_TEMP is only defined in bank 0.

EXAMPLE 11-1: SAVING STATUS, W AND PCLATH REGISTERS IN RAM

| MOVWF  | W_TEMP        | ;Copy W to TEMP register                                |

|--------|---------------|---------------------------------------------------------|

| SWAPF  | STATUS,W      | ;Swap status to be saved into W                         |

| CLRF   | STATUS        | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

| MOVWF  | STATUS_TEMP   | ;Save status to bank zero STATUS_TEMP register          |

| :      |               |                                                         |

| :(ISR) |               | ;Insert user code here                                  |

| :      |               |                                                         |

| SWAPF  | STATUS_TEMP,W | ;Swap STATUS_TEMP register into W                       |

|        |               | ;(sets bank to original state)                          |

| MOVWF  | STATUS        | ;Move W into STATUS register                            |

| SWAPF  | W_TEMP,F      | ;Swap W_TEMP                                            |

| SWAPF  | W_TEMP,W      | ;Swap W_TEMP into W                                     |

|        |               |                                                         |

# 11.13 Watchdog Timer (WDT)

The Watchdog Timer is a free running, on-chip RC oscillator that does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKI pin. That means that the WDT will run, even if the clock on the OSC1/CLKI and OSC2/CLKO pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit WDTEN (see Section 11.1).

WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler) may be assigned using the OPTION register.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

## FIGURE 11-11: WATCHDOG TIMER BLOCK DIAGRAM

TABLE 11-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                 | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|-----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BOREN <sup>(1)</sup> |       | CP    | PWRTEN <sup>(1)</sup> | WDTEN | FOSC1 | FOSC0 |

| 81h,181h | OPTION       | RBPU  | INTEDG               | TOCS  | T0SE  | PSA                   | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 11-1 for operation of these bits.

# 12.1 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] ADDLW k                                                                                                            |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                          |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                          |  |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |  |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |  |  |

| ANDWF            | AND W with f                                                                                                                                                  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                             |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                             |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                     |  |  |

| Status Affected: | Z                                                                                                                                                             |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' = '0', the result is stored in<br>the W register. If 'd' = '1', the<br>result is stored back in register 'f'. |  |  |

| ADDWF            | Add W and f                                                                                                                                                                      |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                                |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                            |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                         |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' = '0', the<br>result is stored in the W register. If<br>'d' = '1', the result is stored back<br>in register 'f'. |  |  |

| BCF              | Bit Clear f                                                         |  |

|------------------|---------------------------------------------------------------------|--|

| Syntax:          | [ label ] BCF f,b                                                   |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |

| Operation:       | $0 \rightarrow (f < b >)$                                           |  |

| Status Affected: | None                                                                |  |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |  |

| ANDLW            | AND Literal with W                                                                                                     |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ label ] ANDLW k                                                                                                      |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                      |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |  |  |

| Status Affected: | Z                                                                                                                      |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |  |  |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| COMF             | Complement f                                                                                                                                              |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                 |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                         |  |  |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                           |  |  |

| Status Affected: | Z                                                                                                                                                         |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' = '0', the<br>result is stored in W. If 'd' = '1', the<br>result is stored back in register 'f'. |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                             |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                          |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                               |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                  |  |  |

| Status Affected: | None                                                                                                                                                                                             |  |  |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>two-cycle instruction. |  |  |

| DECF             | Decrement f                                                                                                                                     | INCF             | Increment f                                                                                                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] DECF f,d                                                                                                                              | Syntax:          | [label] INCF f,d                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                      | Operands:        | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                                 |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                             | Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                      |

| Status Affected: | Z                                                                                                                                               | Status Affected: | Z                                                                                                                                                                        |

| Description:     | Decrement register 'f'. If 'd' = '0',<br>the result is stored in the W<br>register. If 'd' = '1', the result is<br>stored back in register 'f'. | Description:     | The contents of register 'f' are<br>incremented. If 'd' = '0', the result<br>is placed in the W register. If<br>'d' = '1', the result is placed back<br>in register 'f'. |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                       | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                         |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                           | Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                                                                                                   | Operands:        | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                                                                                                                                                                                       |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                   | Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                     |

| Status Affected: | None                                                                                                                                                                                                                                                                                                         | Status Affected: | None                                                                                                                                                                                                                                                                                                                           |

| Description:     | The contents of register 'f' are decremented. If 'd' = '0', the result is placed in the W register. If 'd' = '1', the result is placed back in register 'f'.<br>If the result is '1', the next instruction is executed. If the result is '0', then a NOP is executed instead, making it a 2 TCY instruction. | Description:     | The contents of register 'f' are<br>incremented. If 'd' = '0', the result<br>is placed in the W register. If<br>'d' = '1', the result is placed back<br>in register 'f'.<br>If the result is '1', the next instruc-<br>tion is executed. If the result is '0',<br>a NOP is executed instead, making<br>it a 2 Tcy instruction. |

| RETFIE           | Return from Interrupt      | RLF              | Rotate Left f through Carry                                                                                                                                                                                                         |

|------------------|----------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETFIE             | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                                            |

| Operands:        | None                       | Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                   |

| Operation:       | $TOS \rightarrow PC$ ,     |                  | d ∈ [0,1]                                                                                                                                                                                                                           |

|                  | $1 \rightarrow \text{GIE}$ | Operation:       | See description below                                                                                                                                                                                                               |

| Status Affected: | None                       | Status Affected: | С                                                                                                                                                                                                                                   |

|                  |                            | Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag. If 'd' = '0', the<br>result is placed in the W register.<br>If 'd' = '1', the result is stored<br>back in register 'f'.<br>-C Register f |

| RETLW            | Return with Literal in W                                                                                                                                                            | RRF              | Rotate Right f through Carry                                                                                                                                                                                                      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            | Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                          |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   | Operands:        | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                                                                                          |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        | Operation:       | See description below                                                                                                                                                                                                             |

| Status Affected: | None                                                                                                                                                                                | Status Affected: | С                                                                                                                                                                                                                                 |

| Description:     | The W register is loaded with the<br>eight-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction. | Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' = '0', the<br>result is placed in the W register.<br>If 'd' = '1', the result is placed back<br>in register 'f'.<br>Register f |

| RETURN           | Return from Subroutine                                                | SLEEP            |                                                                                                                                                                                      |  |  |  |

|------------------|-----------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] RETURN                                                        | Syntax:          | [label] SLEEP                                                                                                                                                                        |  |  |  |

| Operands:        | None                                                                  | Operands:        | None                                                                                                                                                                                 |  |  |  |

| Operation:       | $TOS\toPC$                                                            | Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                 |  |  |  |

| Status Affected: | None                                                                  |                  |                                                                                                                                                                                      |  |  |  |

| Description:     | Return from subroutine. The stack                                     |                  |                                                                                                                                                                                      |  |  |  |

|                  | is POPed and the top of the stack<br>(TOS) is loaded into the program | Status Affected: | TO, PD                                                                                                                                                                               |  |  |  |

|                  | counter. This is a two-cycle instruction.                             | Description:     | The power-down status bit, $\overline{PD}$ is cleared. Time-out status bit, $\overline{TO}$ is set. Watchdog Timer and its prescaler are cleared.<br>The processor is put into SLEEP |  |  |  |

mode with the oscillator stopped.

| Param<br>No. | Symbol                | Characteristic                                           | Min                                           | Тур†     | Max      | Units     | Conditions |  |

|--------------|-----------------------|----------------------------------------------------------|-----------------------------------------------|----------|----------|-----------|------------|--|

| 70*          | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input                                | Тсү                                           |          | —        | ns        |            |  |

| 71*          | TscH                  | SCK input high time (Slave mod                           | e)                                            | TCY + 20 |          | —         | ns         |  |

| 72*          | TscL                  | SCK input low time (Slave mode                           | e)                                            | TCY + 20 | _        | —         | ns         |  |

| 73*          | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to S                        | 100                                           |          | _        | ns        |            |  |

| 74*          | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge                  |                                               | 100      | _        | _         | ns         |  |

| 75*          | TdoR                  | SDO data output rise time                                | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) | _        | 10<br>25 | 25<br>50  | ns<br>ns   |  |

| 76*          | TdoF                  | SDO data output fall time                                |                                               | —        | 10       | 25        | ns         |  |

| 77*          | TssH2doZ              | SS <sup>↑</sup> to SDO output hi-impedance               |                                               | 10       | _        | 50        | ns         |  |

| 78*          | TscR                  | SCK output rise timeStandard(F)(Master mode)Extended(LF) |                                               |          | 10<br>25 | 25<br>50  | ns<br>ns   |  |

| 79*          | TscF                  | SCK output fall time (Master mode)                       |                                               | _        | 10       | 25        | ns         |  |

| 80*          | TscH2doV,<br>TscL2doV | SDO data output valid after<br>SCK edge                  | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) |          |          | 50<br>145 | ns<br>ns   |  |

| 81*          | TdoV2scH,<br>TdoV2scL | SDO data output setup to SCK e                           | Тсү                                           | _        | —        | ns        |            |  |

| 82*          | TssL2doV              | SDO data output valid after SS↓                          | _                                             | _        | 50       | ns        |            |  |

| 83*          | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                      | 1.5 Tcy + 40                                  |          | _        | ns        |            |  |

#### TABLE 14-6: SPI MODE REQUIREMENTS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

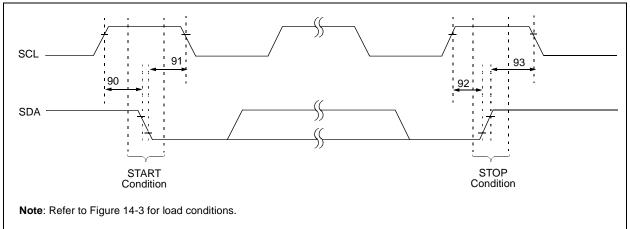

# FIGURE 14-14: I<sup>2</sup>C BUS START/STOP BITS TIMING

| Param<br>No. | Symbol  | Characte                      | eristic      | Min         | Мах  | Units | Conditions                                  |

|--------------|---------|-------------------------------|--------------|-------------|------|-------|---------------------------------------------|

| 100*         | Тнідн   | Clock High Time               | 100 kHz mode | 4.0         |      | μs    | Device must operate at a minimum of 1.5 MHz |

|              |         |                               | 400 kHz mode | 0.6         | _    | μs    | Device must operate at a minimum of 10 MHz  |

|              |         |                               | SSP Module   | 1.5 TCY     |      |       |                                             |

| 101*         | TLOW    | Clock Low Time                | 100 kHz mode | 4.7         |      | μs    | Device must operate at a minimum of 1.5 MHz |

|              |         |                               | 400 kHz mode | 1.3         |      | μs    | Device must operate at a minimum of 10 MHz  |

|              |         |                               | SSP Module   | 1.5 TCY     | _    |       |                                             |

| 102*         | TR      | SDA and SCL Rise              | 100 kHz mode | —           | 1000 | ns    |                                             |

|              |         | Time                          | 400 kHz mode | 20 + 0.1 Св | 300  | ns    | CB is specified to be from 10 - 400 pF      |

| 103*         | 13* TF  | SDA and SCL Fall<br>Time      | 100 kHz mode | —           | 300  | ns    |                                             |

|              |         |                               | 400 kHz mode | 20 + 0.1 Св | 300  | ns    | CB is specified to be from 10 - 400 pF      |

| 90*          | TSU:STA | START Condition<br>Setup Time | 100 kHz mode | 4.7         |      | μs    | Only relevant for                           |

|              |         |                               | 400 kHz mode | 0.6         |      | μs    | Repeated START condition                    |

| 91*          | THD:STA | START Condition               | 100 kHz mode | 4.0         |      | μs    | After this period, the first                |

|              |         | Hold Time                     | 400 kHz mode | 0.6         | _    | μs    | clock pulse is generated                    |

| 106*         | THD:DAT | Data Input Hold               | 100 kHz mode | 0           | _    | ns    |                                             |

|              |         | Time                          | 400 kHz mode | 0           | 0.9  | μs    |                                             |

| 107*         | TSU:DAT | Data Input Setup<br>Time      | 100 kHz mode | 250         | _    | ns    | (Note 2)                                    |

|              |         |                               | 400 kHz mode | 100         | _    | ns    |                                             |

| 92*          | Tsu:sto | STOP Condition<br>Setup Time  | 100 kHz mode | 4.7         | _    | μs    | _                                           |

|              |         |                               | 400 kHz mode | 0.6         | -    | μs    |                                             |

| 109*         | ΤΑΑ     | Output Valid from<br>Clock    | 100 kHz mode | —           | 3500 | ns    | (Note 1)                                    |

|              |         |                               | 400 kHz mode | —           |      | ns    |                                             |

| 110*         | TBUF    | Bus Free Time                 | 100 kHz mode | 4.7         | _    | μs    | Time the bus must be free                   |

|              |         |                               | 400 kHz mode | 1.3         | —    | μs    | before a new transmissior<br>can start      |

|              | Св      | Bus Capacitive Load           | ling         | _           | 400  | pF    |                                             |

| TABLE 14-8: I <sup>2</sup> C BU | S DATA REQUIREMENTS |

|---------------------------------|---------------------|

|---------------------------------|---------------------|

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement TsU:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max.+TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

| Param<br>No. | Sym  | Characte                                          | eristic            | Min        | Тур†       | Мах                | Units                                                                        | Conditions                                                                   |

|--------------|------|---------------------------------------------------|--------------------|------------|------------|--------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| A01          | Nr   | Resolution                                        | PIC16F72           | —          | _          | 8 bits             | bit                                                                          | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$         |

|              |      |                                                   | PIC16LF72          | —          | _          | 8 bits             | bit                                                                          | VREF = VDD = 2.2V                                                            |

| A02          | Eabs | Total Absolute Error                              |                    | _          | _          | < ± 1              | LSb                                                                          | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$         |

| A03          | EIL  | Integral Linearity                                | Error              | —          | _          | < ± 1              | LSb                                                                          | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$         |

| A04          | Edl  | Differential Linear                               | —                  | _          | < ± 1      | LSb                | $\begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$ |                                                                              |

| A05          | Efs  | Full Scale Error                                  |                    | —          | _          | < ± 1              | LSb                                                                          | $\begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$ |

| A06          | EOFF | Offset Error                                      |                    | —          | —          | < ± 1              | LSb                                                                          | $\begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$ |

| A10          | —    | Monotonicity (Note 3)                             |                    | —          | guaranteed | —                  | —                                                                            | $VSS \leq VAIN \leq VREF$                                                    |

| A20          | Vref | Reference Voltage                                 |                    | 2.5<br>2.2 | _          | Vdd+0.3<br>Vdd+0.3 | V<br>V                                                                       | -40°C to +85°C<br>0°C to +85°C                                               |

| A25          | VAIN | Analog Input Voltage                              |                    | Vss - 0.3  | _          | VREF + 0.3         | V                                                                            |                                                                              |

| A30          | ZAIN | Recommended Impedance of<br>Analog Voltage Source |                    | —          | _          | 10.0               | kΩ                                                                           |                                                                              |

| A40          | IAD  | A/D Conversion                                    | PIC16F72           | —          | 180        | —                  | μΑ                                                                           | Average current                                                              |

|              |      | Current (VDD)                                     | PIC16LF72          | —          | 90         | —                  | μA                                                                           | consumption when A/D<br>is on <b>(Note 1)</b> .                              |

| A50          | IREF | VREF input currer                                 | nt <b>(Note 2)</b> | N/A<br>—   |            | ± 5<br>500         | μΑ<br>μΑ                                                                     | During VAIN acquisition.<br>During A/D Conversion<br>cycle.                  |

## TABLE 14-9: A/D CONVERTER CHARACTERISTICS: PIC16F72 (INDUSTRIAL) PIC16LF72 (INDUSTRIAL)

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from the RA3 pin or the VDD pin, whichever is selected as a reference input.

**3:** The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

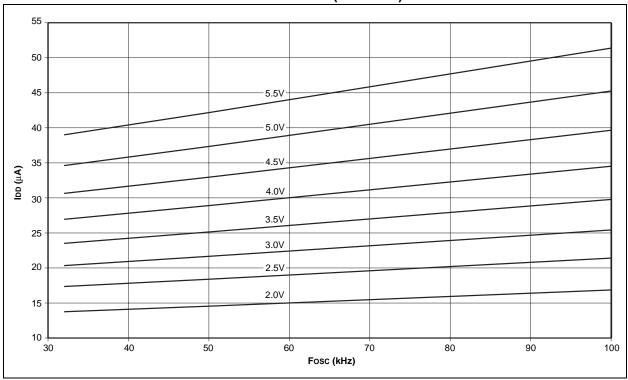

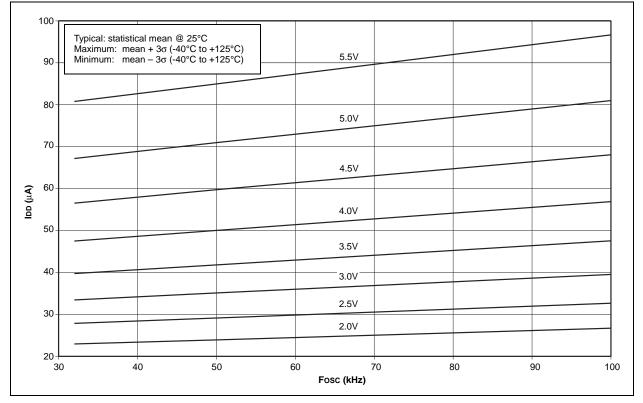

FIGURE 15-5: TYPICAL IDD vs. Fosc OVER VDD (LP MODE)

NOTES:

| Timing Diagrams                                  |

|--------------------------------------------------|

| A/D Conversion105                                |

| Brown-out Reset96                                |

| Capture/Compare/PWM (CCP1)98                     |

| CLKO and I/O95                                   |

| External Clock94                                 |

| I <sup>2</sup> C Bus Data102                     |

| I <sup>2</sup> C Bus START/STOP bits101          |

| I <sup>2</sup> C Reception (7-bit Address) 50    |

| I <sup>2</sup> C Transmission (7-bit Address)    |

| RESET, Watchdog Timer, Oscillator Start-up Timer |

| and Power-up Timer96                             |

| Slow Rise Time (MCLR Tied to VDD Through         |

| RC Network)68                                    |

| SPI Master Mode 47                               |

| SPI Master Mode (CKE = 0, SMP = 0)               |

| SPI Master Mode (CKE = 1, SMP = 1)               |

| SPI Slave Mode (CKE = 0) 47, 100                 |

| SPI Slave Mode (CKE = 1)                         |

| Time-out Sequence on Power-up (MCLR Tied to      |

| VDD Through Pull-up Resistor)                    |

| Time-out Sequence on Power-up (MCLR Tied to      |

| VDD Through RC Network): Case 1                  |

| Time-out Sequence on Power-up (MCLR Tied to      |

| VDD Through RC Network): Case 2                  |

| Timer0 and Timer1 External Clock                 |

| Wake-up from SLEEP through Interrupt             |

| Timing Parameter Symbology                       |

| TMR1H Register9                                  |

| TMR1L Register9                                  |

| TMR2 Register9                                   |

| TMR2ON bit                                       |

| TOUTPS0 bit                                      |

| TOUTPS1 bit                                      |

| TOUTPS2 bit                                      |

| TOUTPS3 bit                                      |

| TRISA Register 10, 21                            |

| TRISB Register 10, 23                            |

| TRISC Register 10, 25                            |

|                                                  |

# U

| 0                                |        |

|----------------------------------|--------|

| UA                               | 44     |

| Update Address bit, UA           | 44     |

| W                                |        |

| Wake-up from SLEEP               | 59, 71 |

| Interrupts                       |        |

| MCLR Reset                       | 66     |

| WDT Reset                        |        |

| Watchdog Timer (WDT)             | 59, 70 |

| Associated Registers             |        |

| Enable (WDTEN bit)               |        |

| Postscaler. See Postscaler, WDT  |        |

| Programming Considerations       |        |

| RC Oscillator                    |        |

| Time-out Period                  |        |

| WDT Reset, Normal Operation      |        |

| WDT Reset, SLEEP                 |        |

| WCOL                             | , ,    |

| Write Collision Detect bit, WCOL |        |

| WWW, On-Line Support             |        |

|                                  |        |