Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

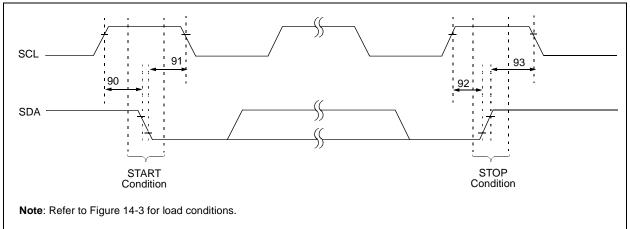

| Connectivity               | I²C, SPI                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f72t-e-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Linear Active Thermistor, Mindi, MiWi, MPASM, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2007, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona, Gresham, Oregon and Mountain View, California. The Company's quality system processes and procedures are for its PIC<sup>®</sup> MCUs and dsPIC DSCs, KEELOQ<sup>®</sup> code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

#### **Table of Contents**

| 1.0   | Device Overview                              |    |  |  |  |  |  |

|-------|----------------------------------------------|----|--|--|--|--|--|

| 2.0   | Memory Organization                          | 7  |  |  |  |  |  |

| 3.0   | I/O Ports                                    |    |  |  |  |  |  |

| 4.0   | Reading Program Memory                       | 27 |  |  |  |  |  |

| 5.0   | Timer0 Module                                |    |  |  |  |  |  |

| 6.0   | Timer1 Module                                | 31 |  |  |  |  |  |

| 7.0   | Timer2 Module                                | 35 |  |  |  |  |  |

| 8.0   | Capture/Compare/PWM (CCP) Module             | 37 |  |  |  |  |  |

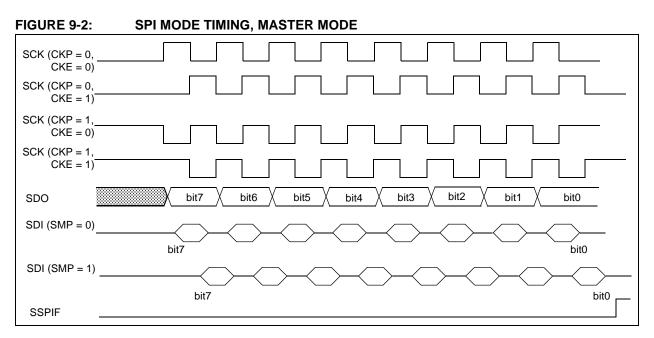

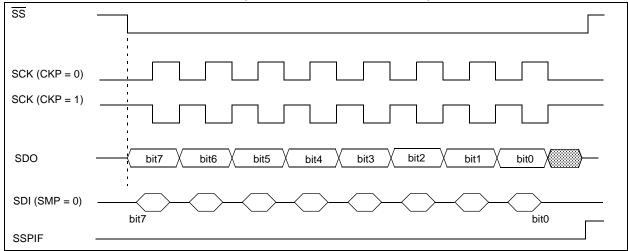

| 9.0   | Synchronous Serial Port (SSP) Module         |    |  |  |  |  |  |

| 10.0  | Analog-to-Digital Converter (A/D) Module     |    |  |  |  |  |  |

| 11.0  | Special Features of the CPU                  | 59 |  |  |  |  |  |

| 12.0  | Instruction Set Summary                      |    |  |  |  |  |  |

| 13.0  | Development Support                          | 81 |  |  |  |  |  |

| 14.0  | Electrical Characteristics                   | 87 |  |  |  |  |  |

| 15.0  | DC and AC Characteristics Graphs and Tables1 | 07 |  |  |  |  |  |

| 16.0  | Package Marking Information1                 | 17 |  |  |  |  |  |

| Appe  | ndix A: Revision History1                    | 23 |  |  |  |  |  |

|       | ndix B: Conversion Considerations1           |    |  |  |  |  |  |

| Index |                                              | 25 |  |  |  |  |  |

| On-Li | ne Support1                                  | 31 |  |  |  |  |  |

|       | ader Response                                |    |  |  |  |  |  |

| Produ | ict Identification System 1                  | 33 |  |  |  |  |  |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# 1.0 DEVICE OVERVIEW

This document contains device specific information for the operation of the PIC16F72 device. Additional information may be found in the PIC<sup>™</sup> Mid-Range MCU Reference Manual (DS33023), which may be downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

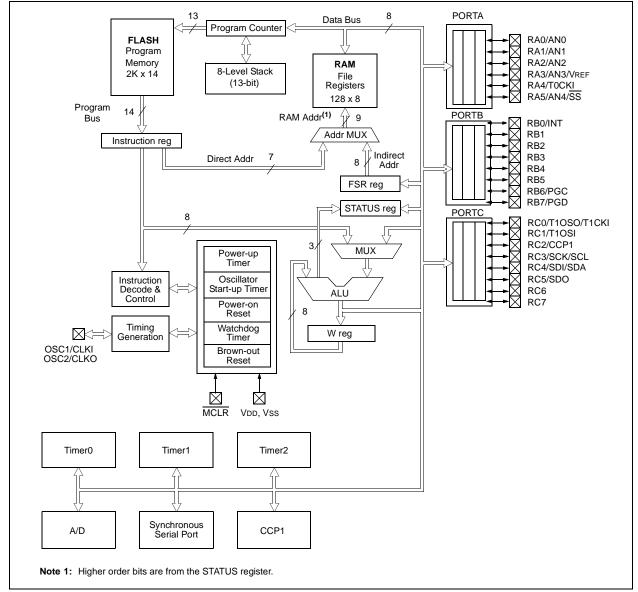

The PIC16F72 belongs to the Mid-Range family of the PIC devices. A block diagram of the device is shown in Figure 1-1.

The program memory contains 2K words, which translate to 2048 instructions, since each 14-bit program memory word is the same width as each device instruction. The data memory (RAM) contains 128 bytes.

There are 22 I/O pins that are user configurable on a pin-to-pin basis. Some pins are multiplexed with other device functions. These functions include:

- External interrupt

- Change on PORTB interrupt

- Timer0 clock input

- Timer1 clock/oscillator

- Capture/Compare/PWM

- A/D converter

- SPI/I<sup>2</sup>C

Table 1-1 details the pinout of the device with descriptions and details for each pin.

### FIGURE 1-1: PIC16F72 BLOCK DIAGRAM

#### 2.2.2.1 STATUS Register

The STATUS register, shown in Register 2-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see Section 12.0, Instruction Set Summary.

Note 1: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| REGISTER 2-1: | STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h) |

|---------------|------------------------------------------------|

|---------------|------------------------------------------------|

| ER 2-1:      | STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)                                                                                                 |                                                                      |                                  |                  |              |               |               |             |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------|------------------|--------------|---------------|---------------|-------------|--|--|--|--|

|              | R/W-0                                                                                                                                          | R/W-0                                                                | R/W-0                            | R-1              | R-1          | R/W-x         | R/W-x         | R/W-x       |  |  |  |  |

|              | IRP                                                                                                                                            | RP1                                                                  | RP0                              | TO               | PD           | Z             | DC            | С           |  |  |  |  |

|              | bit 7                                                                                                                                          |                                                                      |                                  |                  |              | •             |               | bit 0       |  |  |  |  |

|              |                                                                                                                                                |                                                                      |                                  |                  |              |               |               |             |  |  |  |  |

| bit 7        | IRP: Regis                                                                                                                                     | ter Bank Sel                                                         | ect bit (used f                  | for indirect ad  | ldressing)   |               |               |             |  |  |  |  |

|              |                                                                                                                                                | 2, 3 (100h - 1                                                       |                                  |                  |              |               |               |             |  |  |  |  |

|              |                                                                                                                                                | ), 1 (00h - FF                                                       | •                                |                  |              |               |               |             |  |  |  |  |

| bit 6-5      |                                                                                                                                                | -                                                                    | k Select bits                    | (used for dire   | ct address   | ing)          |               |             |  |  |  |  |

|              |                                                                                                                                                | 3 (180h - 1F                                                         |                                  |                  |              |               |               |             |  |  |  |  |

|              |                                                                                                                                                | 2 (100h - 17<br>1 (80h - FFh                                         |                                  |                  |              |               |               |             |  |  |  |  |

|              |                                                                                                                                                | 0 (00h - 7Fh                                                         |                                  |                  |              |               |               |             |  |  |  |  |

|              | Each bank                                                                                                                                      | is 128 bytes                                                         |                                  |                  |              |               |               |             |  |  |  |  |

| bit 4        | TO: Time-o                                                                                                                                     | out bit                                                              |                                  |                  |              |               |               |             |  |  |  |  |

|              |                                                                                                                                                | 1 = After power-up, CLRWDT instruction, or SLEEP instruction         |                                  |                  |              |               |               |             |  |  |  |  |

|              |                                                                                                                                                | T time-out oc                                                        | curred                           |                  |              |               |               |             |  |  |  |  |

| bit 3        | PD: Power                                                                                                                                      |                                                                      |                                  |                  |              |               |               |             |  |  |  |  |

|              | <ul> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul>                         |                                                                      |                                  |                  |              |               |               |             |  |  |  |  |

| <b>h</b> # 0 | -                                                                                                                                              |                                                                      | SLEEP INSUU                      | iction           |              |               |               |             |  |  |  |  |

| bit 2        | <b>Z</b> : Zero bit                                                                                                                            |                                                                      |                                  |                  |              |               |               |             |  |  |  |  |

|              | <ol> <li>The result of an arithmetic or logic operation is zero</li> <li>The result of an arithmetic or logic operation is not zero</li> </ol> |                                                                      |                                  |                  |              |               |               |             |  |  |  |  |

| bit 1        | DC: Digit carry/borrow bit (ADDWF, ADDLW, SUBLW and SUBWF instructions) <sup>(1)</sup>                                                         |                                                                      |                                  |                  |              |               |               |             |  |  |  |  |

|              | 1 = A carry-out from the 4th low order bit of the result occurred                                                                              |                                                                      |                                  |                  |              |               |               |             |  |  |  |  |

|              | 0 = No car                                                                                                                                     | ry-out from th                                                       | ne 4th Iow ord                   | der bit of the r | result       |               |               |             |  |  |  |  |

| bit 0        | C: Carry/borrow bit (ADDWF, ADDLW, SUBLW and SUBWF instructions) <sup>(1,2)</sup>                                                              |                                                                      |                                  |                  |              |               |               |             |  |  |  |  |

|              |                                                                                                                                                | 1 = A carry-out from the Most Significant bit of the result occurred |                                  |                  |              |               |               |             |  |  |  |  |

|              | 0 <b>= No car</b>                                                                                                                              | ry-out from th                                                       | ne Most Signi                    | ficant bit of th | ne result or | ccurred       |               |             |  |  |  |  |

|              | Note 1:                                                                                                                                        |                                                                      | the polarity is tof the secor    |                  | subtractio   | n is execute  | ed by addin   | g the two's |  |  |  |  |

|              | 2:                                                                                                                                             | •                                                                    | RRF, RLF) inst<br>urce register. |                  | bit is loade | ed with eithe | er the high o | r low order |  |  |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 2.2.2.5 PIR1 Register

This register contains the individual flag bits for the Peripheral interrupts.

- n = Value at POR

| EGISTER 2-5: | PIR1: PERIPHERAL INTERRUPT FLAG REGISTER 1 (ADDRESS 0Ch)                                                                                                                                                                                                                                            |                              |                              |               |              |               |              |        |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|---------------|--------------|---------------|--------------|--------|--|--|

|              | U-0                                                                                                                                                                                                                                                                                                 | R/W-0                        | U-0                          | U-0           | R/W-0        | R/W-0         | R/W-0        | R/W-0  |  |  |

|              |                                                                                                                                                                                                                                                                                                     | ADIF                         | —                            | —             | SSPIF        | CCP1IF        | TMR2IF       | TMR1IF |  |  |

|              | bit 7                                                                                                                                                                                                                                                                                               |                              |                              |               |              |               |              | bit 0  |  |  |

|              |                                                                                                                                                                                                                                                                                                     |                              |                              |               |              |               |              |        |  |  |

| bit 7        | Unimplem                                                                                                                                                                                                                                                                                            | ented: Read                  | d as '0'                     |               |              |               |              |        |  |  |

| bit 6        |                                                                                                                                                                                                                                                                                                     |                              | nterrupt Flag                | bit           |              |               |              |        |  |  |

|              |                                                                                                                                                                                                                                                                                                     | ) conversion<br>/D conversio | completed                    | olete         |              |               |              |        |  |  |

| bit 5-4      | Unimplem                                                                                                                                                                                                                                                                                            | ented: Read                  | d as '0'                     |               |              |               |              |        |  |  |

| bit 3        | SSPIF: Sy                                                                                                                                                                                                                                                                                           | nchronous S                  | Serial Port (S               | SP) Interrupt | Flag bit     |               |              |        |  |  |

|              | <ul> <li>1 = The SSP interrupt condition has occurred, and must be cleared in software before returning from the Interrupt Service Routine.<br/>The conditions that will set this bit are a transmission/reception has taken place.</li> <li>0 = No SSP interrupt condition has occurred</li> </ul> |                              |                              |               |              |               |              |        |  |  |

| bit 2        | CCP1IF: CCP1 Interrupt Flag bit                                                                                                                                                                                                                                                                     |                              |                              |               |              |               |              |        |  |  |

|              | <u>Capture mode:</u><br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred                                                                                                                                                                 |                              |                              |               |              |               |              |        |  |  |

|              |                                                                                                                                                                                                                                                                                                     | R1 register co               | ompare matc<br>compare mat   |               | must be clea | ared in softv | vare)        |        |  |  |

|              | <u>PWM mod</u><br>Unused in                                                                                                                                                                                                                                                                         |                              |                              |               |              |               |              |        |  |  |

| bit 1        | TMR2IF: TMR2 to PR2 Match Interrupt Flag bit                                                                                                                                                                                                                                                        |                              |                              |               |              |               |              |        |  |  |

|              | <ul> <li>1 = TMR2 to PR2 match occurred (must be cleared in software)</li> <li>0 = No TMR2 to PR2 match occurred</li> </ul>                                                                                                                                                                         |                              |                              |               |              |               |              |        |  |  |

| bit 0        | TMR1IF: TMR1 Overflow Interrupt Flag bit                                                                                                                                                                                                                                                            |                              |                              |               |              |               |              |        |  |  |

|              | 1 = TMR1                                                                                                                                                                                                                                                                                            | register ove                 | rflowed (mus<br>not overflow | -             | in software) | )             |              |        |  |  |

|              | Legend:                                                                                                                                                                                                                                                                                             |                              |                              |               |              |               |              | ]      |  |  |

|              | R = Reada                                                                                                                                                                                                                                                                                           | ble bit                      | W = W                        | ritable bit   | U = Unim     | plemented     | bit, read as | '0'    |  |  |

|              | 1                                                                                                                                                                                                                                                                                                   |                              |                              |               |              |               |              |        |  |  |

'1' = Bit is set

x = Bit is unknown

'0' = Bit is cleared

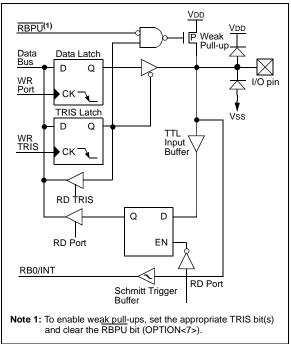

## 3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

EXAMPLE 3-2: INITIALIZING PORTB

| BANKSEL | PORTB | ; Select bank for PORTB |

|---------|-------|-------------------------|

| CLRF    | PORTB | ; Initialize PORTB by   |

|         |       | ; clearing output       |

|         |       | ; data latches          |

| BANKSEL | TRISB | ; Select Bank for TRISB |

| MOVLW   | 0xCF  | ; Value used to         |

|         |       | ; initialize data       |

|         |       | ; direction             |

| MOVWF   | TRISB | ; Set RB<3:0> as inputs |

|         |       | ; RB<5:4> as outputs    |

|         |       | ; RB<7:6> as inputs     |

|         |       |                         |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overline{\mathsf{RBPU}}$  (OPTION<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

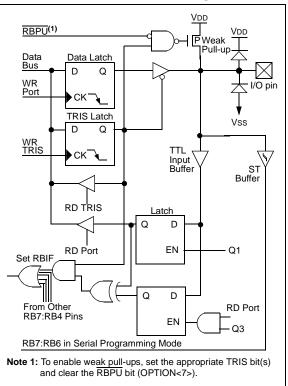

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'd together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

This interrupt-on-mismatch feature, together with software configurable pull-ups on these four pins, allow easy interface to a keypad and make it possible for wake-up on key depression. Refer to the Embedded Control Handbook, *"Implementing Wake-Up on Key Stroke"* (AN552).

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION<6>).

#### FIGURE 3-4: BLOCK DIAGRAM OF RB7:RB4 PINS

## 5.5 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt on overflow, that will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 5.5.1).

In Asynchronous Counter mode, Timer1 cannot be used as a time base for capture or compare operations.

### 5.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register. Data in the Timer1 register (TMR1) may become corrupted. Corruption occurs when the timer enable is turned off at the same instant that a ripple carry occurs in the timer module.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>™</sup> Mid-Range MCU

Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

# 5.6 Timer1 Oscillator

A crystal oscillator circuit is built between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 5-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

# TABLE 5-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type                                                                                                                                                                                   | Freq                                                                                                    | C1            | C2        |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------|-----------|--|--|--|--|

| LP                                                                                                                                                                                         | 32 kHz                                                                                                  | 33 pF         | 33 pF     |  |  |  |  |

|                                                                                                                                                                                            | 100 kHz                                                                                                 | 15 pF         | 15 pF     |  |  |  |  |

|                                                                                                                                                                                            | 200 kHz                                                                                                 | 15 pF         | 15 pF     |  |  |  |  |

| These v                                                                                                                                                                                    | alues are for                                                                                           | design guidar | ice only. |  |  |  |  |

| c                                                                                                                                                                                          | Note 1: Higher capacitance increases the stability of oscillator, but also increases the start-up time. |               |           |  |  |  |  |

| <ul> <li>2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.</li> </ul> |                                                                                                         |               |           |  |  |  |  |

# 5.7 Timer1 Interrupt

The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/ clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

## 5.8 Resetting Timer1 Using a CCP Trigger Output

If the CCP module is configured in Compare mode to generate a "special event trigger" signal (CCP1M3:CCP1M0 = 1011), the signal will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

**Note:** The special event triggers from the CCP1 module will not set interrupt flag bit TMR1IF (PIR1<0>).

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L registers pair effectively becomes the period register for Timer1.

# **PIC16F72**

| REGISTER 6-1: | TER 6-1: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h) |              |             |               |               |           |              |         |

|---------------|-------------------------------------------------------|--------------|-------------|---------------|---------------|-----------|--------------|---------|

|               | U-0                                                   | R/W-0        | R/W-0       | R/W-0         | R/W-0         | R/W-0     | R/W-0        | R/W-0   |

|               | _                                                     | TOUTPS3      | TOUTPS2     | TOUTPS1       | TOUTPS0       | TMR2ON    | T2CKPS1      | T2CKPS0 |

|               | bit 7                                                 |              |             |               |               |           |              | bit 0   |

| bit 7         | Unimple                                               | nented: Rea  | ad as '0'   |               |               |           |              |         |

| bit 6-3       | -                                                     |              |             | put Postscale | e Select bits |           |              |         |

|               |                                                       | 1 Postscale  |             |               |               |           |              |         |

|               | 0001 = 1:                                             | 2 Postscale  |             |               |               |           |              |         |

|               | 0010 = 1:                                             | 3 Postscale  |             |               |               |           |              |         |

|               | •                                                     |              |             |               |               |           |              |         |

|               | •                                                     |              |             |               |               |           |              |         |

|               | 1111 <b>= 1</b> :                                     | 16 Postscale | 9           |               |               |           |              |         |

| bit 2         | TMR2ON                                                | : Timer2 On  | bit         |               |               |           |              |         |

|               | 1 = Timei                                             | 2 is on      |             |               |               |           |              |         |

|               | 0 = Time                                              | 2 is off     |             |               |               |           |              |         |

| bit 1-0       | T2CKPS                                                | I:T2CKPS0:   | Timer2 Cloc | k Prescale S  | elect bits    |           |              |         |

|               | 00 = Pre:                                             | scaler is 1  |             |               |               |           |              |         |

|               |                                                       | scaler is 4  |             |               |               |           |              |         |

|               | 1x = Pres                                             | scaler is 16 |             |               |               |           |              |         |

|               |                                                       |              |             |               |               |           |              |         |

|               | Legend:                                               |              |             |               |               |           |              |         |

|               | R = Read                                              | able bit     | W = V       | Vritable bit  | U = Unim      | plemented | bit, read as | '0'     |

| TABLE 6-1: | <b>REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER</b> |

|------------|------------------------------------------------------------|

|            |                                                            |

- n = Value at POR

| Address                | Name   | Bit 7 | Bit 6                  | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>POR, |      | Valu<br>all c<br>RES | other |

|------------------------|--------|-------|------------------------|---------|---------|---------|--------|---------|---------|---------------|------|----------------------|-------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON | GIE   | PEIE                   | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000          | 000x | 0000                 | 000u  |

| 0Ch                    | PIR1   |       | ADIF                   | —       | _       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | - 0           | 0000 | 0000                 | 0000  |

| 8Ch                    | PIE1   | _     | ADIE                   | —       | _       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | - 0           | 0000 | 0000                 | 0000  |

| 11h                    | TMR2   | Timer | Timer2 Module Register |         |         |         |        |         |         | 0000          | 0000 | 0000                 | 0000  |

| 12h                    | T2CON  | _     | TOUTPS3                | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000          | 0000 | -000                 | 0000  |

| 92h                    | PR2    | Timer | 2 Period Re            | gister  |         |         |        |         |         | 1111          | 1111 | 1111                 | 1111  |

'1' = Bit is set

'0' = Bit is cleared

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

x = Bit is unknown

## 7.3 Reading the FLASH Program Memory

To read a program memory location, the user must write two bytes of the address to the PMADRL and PMADRH registers and then set control bit, RD (PMCON1<0>). Once the read control bit is set, the program memory FLASH controller will use the second instruction cycle after to read the data. This causes the second instruction immediately following the "BSF PMCON1, RD" instruction to be ignored. The data is available in the very next cycle in the PMDATL and PMDATH registers; therefore, it can be read as two bytes in the following instructions. PMDATL and PMDATH registers will hold this value until another read, or until it is written to by the user (during a write operation).

# 7.4 Operation During Code Protect

The FLASH program memory control can read anywhere within the program memory, whether or not the program memory is code protected.

This does not compromise the code, because there is no way to rewrite a portion of the program memory, or leave contents of a program memory read in a register while changing modes.

### EXAMPLE 7-1: FLASH PROGRAM READ

|         | PMADRH          | ; Select Bank for PMADRH                                   |

|---------|-----------------|------------------------------------------------------------|

| MOVLW   | MS_PROG_EE_ADDR | i                                                          |

| MOVWF   | PMADRH          | ; MS Byte of Program Address to read                       |

| MOVLW   | LS_PROG_EE_ADDR | ;                                                          |

| MOVWF   | PMADRL          | ; LS Byte of Program Address to read                       |

| BANKSEL | PMCON1          | ; Select Bank for PMCON1                                   |

| BSF     | PMCON1, RD      | ; EE Read                                                  |

|         |                 | ;                                                          |

| NOP     |                 | ; Any instructions here are ignored as program             |

| NOP     |                 | ; memory is read in second cycle after BSF PMCON1,RD       |

|         |                 | ;                                                          |

|         |                 | ; First instruction after BSF PMCON1, RD executes normally |

| BANKSEL | PMDATL          | ; Select Bank for PMDATL                                   |

| MOVF    | PMDATL, W       | ; W = LS Byte of Program PMDATL                            |

| MOVF    | PMDATH, W       | ; W = MS Byte of Program PMDATL                            |

#### TABLE 7-1: REGISTERS ASSOCIATED WITH PROGRAM FLASH

| Address | Name   | Bit 7   | Bit 6                     | Bit 5   | Bit 4                                          | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value<br>all o<br>RES | ther |

|---------|--------|---------|---------------------------|---------|------------------------------------------------|-------|-------|-------|-------|----------------------|-----------------------|------|

| 10Dh    | PMADRL | Address | Address Register Low Byte |         |                                                |       |       |       |       | xxxx xxxx            | uuuu                  | uuuu |

| 10Fh    | PMADRH |         | —                         | —       | <ul> <li>Address Register High Byte</li> </ul> |       |       |       |       | xxxx xxxx            | uuuu                  | uuuu |

| 10Ch    | PMDATL | Data Re | gister Lo                 | ow Byte |                                                |       |       |       |       | xxxx xxxx            | uuuu                  | uuuu |

| 10Eh    | PMDATH |         | —                         | Data Re | Register High Byte                             |       |       |       |       | xxxx xxxx            | uuuu                  | uuuu |

| 18Ch    | PMCON1 | (1)     |                           | —       |                                                | _     | _     | —     | RD    | 10                   | 1                     | 0    |

Legend: x = unknown, u = unchanged, r = reserved, - = unimplemented, read as '0'. Shaded cells are not used during FLASH access.

Note 1: This bit always reads as a '1'.

Maximum PWM resolution (bits) for a given PWM frequency is calculated using Equation 8-3.

### EQUATION 8-3: PWM MAX RESOLUTION

PWM Maximum Resolution =  $\frac{\log{(\frac{Fosc}{FpWM})}}{\log(2)}$  bits

| Note: | If the PWM duty cycle value is longer than |

|-------|--------------------------------------------|

|       | the PWM period, the CCP1 pin will not be   |

|       | cleared.                                   |

For a sample PWM period and duty cycle calculation, see the PIC<sup>™</sup> Mid-Range MCU Reference Manual (DS33023).

## 8.3.3 SET-UP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

| <b>TABLE 8-3</b> : | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz |

|--------------------|---------------------------------------------------|

|                    |                                                   |

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

### TABLE 8-4: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address              | Name    | Bit 7                               | Bit 6                               | Bit 5        | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   |      | e on<br>BOR |      | e on<br>ther<br>ETS |

|----------------------|---------|-------------------------------------|-------------------------------------|--------------|---------|---------|--------|---------|---------|------|-------------|------|---------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE                                 | PEIE                                | TMR0IE       | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000 | 000x        | 0000 | 000u                |

| 0Ch                  | PIR1    | _                                   | ADIF                                | _            | _       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | - 0  | 0000        | 0000 | 0000                |

| 8Ch                  | PIE1    | —                                   | ADIE                                | _            | _       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | - 0  | 0000        | 0000 | 0000                |

| 87h                  | TRISC   | PORT                                | PORTC Data Direction Register       |              |         |         |        |         |         |      | 1111        | 1111 | 1111                |

| 11h                  | TMR2    | Timer2                              | Module Re                           | gister       |         |         |        |         |         | 0000 | 0000        | 0000 | 0000                |

| 92h                  | PR2     | Timer2                              | Module Pe                           | riod Registe | r       |         |        |         |         | 1111 | 1111        | 1111 | 1111                |

| 12h                  | T2CON   | _                                   | TOUTPS3                             | TOUTPS2      | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 | 0000        | -000 | 0000                |

| 15h                  | CCPR1L  | Captur                              | Capture/Compare/PWM Register1 (LSB) |              |         |         |        |         |         | xxxx | xxxx        | uuuu | uuuu                |

| 16h                  | CCPR1H  | Capture/Compare/PWM Register1 (MSB) |                                     |              |         |         |        |         | xxxx    | xxxx | uuuu        | uuuu |                     |

| 17h                  | CCP1CON | _                                   | _                                   | CCP1X        | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00   | 0000        | 00   | 0000                |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2.

© 2007 Microchip Technology Inc.

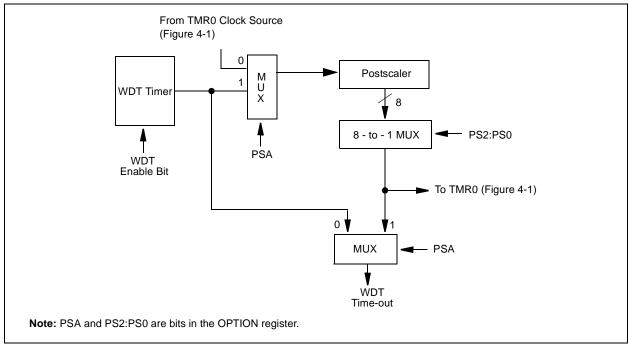

# 11.13 Watchdog Timer (WDT)

The Watchdog Timer is a free running, on-chip RC oscillator that does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKI pin. That means that the WDT will run, even if the clock on the OSC1/CLKI and OSC2/CLKO pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit WDTEN (see Section 11.1).

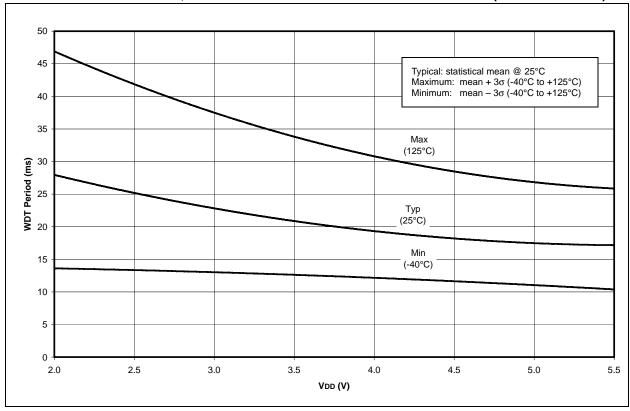

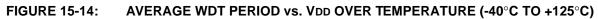

WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler) may be assigned using the OPTION register.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

## FIGURE 11-11: WATCHDOG TIMER BLOCK DIAGRAM

TABLE 11-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                 | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|-----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BOREN <sup>(1)</sup> |       | CP    | PWRTEN <sup>(1)</sup> | WDTEN | FOSC1 | FOSC0 |

| 81h,181h | OPTION       | RBPU  | INTEDG               | TOCS  | T0SE  | PSA                   | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 11-1 for operation of these bits.

## 14.1 DC Characteristics: PIC16F72 (Industrial, Extended) PIC16LF72 (Industrial)

| PIC16L<br>(Indus                   |      |                                                                  | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                                                                                                                                                                                         |                   |             |                                                                                        |  |  |  |

|------------------------------------|------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------|----------------------------------------------------------------------------------------|--|--|--|

| PIC16F72<br>(Industrial, Extended) |      |                                                                  |                                                                                                                                        | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                   |             |                                                                                        |  |  |  |

| Param<br>No.                       | Sym  | Characteristic                                                   | Min Typ† Max Units Conditions                                                                                                          |                                                                                                                                                                                         |                   |             |                                                                                        |  |  |  |

|                                    | Vdd  | Supply Voltage                                                   |                                                                                                                                        |                                                                                                                                                                                         |                   |             |                                                                                        |  |  |  |

| D001                               |      | PIC16LF72                                                        | 2.0<br>2.5<br>2.2                                                                                                                      |                                                                                                                                                                                         | 5.5<br>5.5<br>5.5 | V<br>V<br>V | A/D not used, -40°C to +85°C<br>A/D in use, -40°C to +85°C<br>A/D in use, 0°C to +85°C |  |  |  |

| D001<br>D001A                      |      | PIC16F72                                                         | 4.0<br>Vbor*                                                                                                                           | _                                                                                                                                                                                       | 5.5<br>5.5        | V<br>V      | All configurations<br>BOR enabled <b>(Note 7)</b>                                      |  |  |  |

| D002*                              | Vdr  | RAM Data Retention<br>Voltage (Note 1)                           |                                                                                                                                        | 1.5                                                                                                                                                                                     | —                 | V           |                                                                                        |  |  |  |

| D003                               | VPOR | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | _                                                                                                                                      | Vss                                                                                                                                                                                     | _                 | V           | See section on Power-on Reset for details                                              |  |  |  |

| D004*                              | SVDD | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05                                                                                                                                   | —                                                                                                                                                                                       | _                 | V/ms        | See section on Power-on Reset for details                                              |  |  |  |

| D005                               | VBOR | Brown-out Reset Voltage                                          | 3.65                                                                                                                                   | 4.0                                                                                                                                                                                     | 4.35              | V           | BOREN bit in configuration word enabled                                                |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements in active Operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

## 14.1 DC Characteristics: PIC16F72 (Industrial, Extended) PIC16LF72 (Industrial) (Continued)

| PIC16LI<br>(Indus                  | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                                     |          |                                                                                                                                                                                         |          |          |                                                                                                                               |  |  |  |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIC16F72<br>(Industrial, Extended) |                                                                                                                                        |                                     |          | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |          |          |                                                                                                                               |  |  |  |

| Param<br>No.                       | Sym                                                                                                                                    | Characteristic                      | Min      | Typ† Max Units Conditions                                                                                                                                                               |          |          |                                                                                                                               |  |  |  |

|                                    | Idd                                                                                                                                    | Supply Current (Notes 2, 5          | 5)       |                                                                                                                                                                                         |          |          |                                                                                                                               |  |  |  |

| D010                               |                                                                                                                                        | PIC16LF72                           | _        | 0.4                                                                                                                                                                                     | 2.0      | mA       | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                 |  |  |  |

| D010A                              |                                                                                                                                        |                                     | —        | 25                                                                                                                                                                                      | 48       | μA       | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                                               |  |  |  |

| D010                               |                                                                                                                                        | PIC16F72                            | -        | 0.9                                                                                                                                                                                     | 4        | mA       | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)                                                                 |  |  |  |

| D013                               |                                                                                                                                        |                                     | —        | 5.2                                                                                                                                                                                     | 15       | mA       | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                             |  |  |  |

| D015*                              | $\Delta$ Ibor                                                                                                                          | Brown-out Reset Current<br>(Note 6) |          | 25                                                                                                                                                                                      | 200      | μA       | BOR enabled, VDD = 5.0V                                                                                                       |  |  |  |

|                                    | IPD                                                                                                                                    | Power-down Current (Note            | es 3, 5) |                                                                                                                                                                                         |          |          |                                                                                                                               |  |  |  |

| D020<br>D021                       |                                                                                                                                        | PIC16LF72                           | _        | 2.0<br>0.1                                                                                                                                                                              | 30<br>5  | μΑ<br>μΑ | VDD = 3.0V, WDT enabled, -40°C to +85°C<br>VDD = 3.0V, WDT disabled, -40°C to +85°C                                           |  |  |  |

| D020<br>D021                       |                                                                                                                                        | PIC16F72                            | —        | 5.0<br>0.1                                                                                                                                                                              | 42<br>19 | μΑ<br>μΑ | $VDD = 4.0V$ , WDT enabled, $-40^{\circ}C$ to $+85^{\circ}C$<br>$VDD = 4.0V$ , WDT disabled, $-40^{\circ}C$ to $+85^{\circ}C$ |  |  |  |

| D023*                              | $\Delta$ Ibor                                                                                                                          | Brown-out Reset Current<br>(Note 6) |          | 25                                                                                                                                                                                      | 200      | μA       | BOR enabled, VDD = 5.0V                                                                                                       |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements in active Operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD  $\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.