Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 20000                      |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f72t-i-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Key Reference Manual Features                          | PIC16F72               |

|--------------------------------------------------------|------------------------|

| Operating Frequency                                    | DC - 20 MHz            |

| RESETS and (Delays)                                    | POR, BOR, (PWRT, OST)  |

| FLASH Program Memory - (14-bit words, 1000 E/W cycles) | 2K                     |

| Data Memory - RAM (8-bit bytes)                        | 128                    |

| Interrupts                                             | 8                      |

| I/O Ports                                              | PORTA, PORTB, PORTC    |

| Timers                                                 | Timer0, Timer1, Timer2 |

| Capture/Compare/PWM Modules                            | 1                      |

| Serial Communications                                  | SSP                    |

| 8-bit A/D Converter                                    | 5 channels             |

| Instruction Set (No. of Instructions)                  | 35                     |

#### TABLE 1-1: PIC16F72 PINOUT DESCRIPTION

| OSC1/CLKI<br>OSC2/CLKO |       | Pin#  | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                                 |  |

|------------------------|-------|-------|---------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OSC2/CLKO              | 9     | 6     | I             | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                       |  |

|                        | 10    | 7     | 0             | _                      | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. In RC mode, the OSC2 pin outputs CLKO, which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |  |

| MCLR/Vpp               | 1     | 26    | I/P           | ST                     | Master Clear (Reset) input or programming voltage input. This pin is an active low RESET to the device.                                                                                                     |  |

|                        |       |       |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                         |  |

| RA0/AN0                | 2     | 27    | I/O           | TTL                    | RA0 can also be analog input0.                                                                                                                                                                              |  |

| RA1/AN1                | 3     | 28    | I/O           | TTL                    | RA1 can also be analog input1.                                                                                                                                                                              |  |

| RA2/AN2                | 4     | 1     | I/O           | TTL                    | RA2 can also be analog input2.                                                                                                                                                                              |  |

| RA3/AN3/VREF           | 5     | 2     | I/O           | TTL                    | RA3 can also be analog input3 or analog reference voltage.                                                                                                                                                  |  |

| RA4/T0CKI              | 6     | 3     | I/O           | ST                     | RA4 can also be the clock input to the Timer0 module. Output is open drain type.                                                                                                                            |  |

| RA5/AN4/SS             | 7     | 4     | I/O           | TTL                    | RA5 can also be analog input4 or the slave select for the<br>synchronous serial port.                                                                                                                       |  |

|                        |       |       |               |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                               |  |

| RB0/INT                | 21    | 18    | I/O           | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                                 |  |

| RB1                    | 22    | 19    | I/O           | TTL                    |                                                                                                                                                                                                             |  |

| RB2                    | 23    | 20    | I/O           | TTL                    |                                                                                                                                                                                                             |  |

| RB3                    | 24    | 21    | I/O           | TTL                    |                                                                                                                                                                                                             |  |

| RB4                    | 25    | 22    | I/O           | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                    |  |

| RB5                    | 26    | 23    | I/O           | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                    |  |

| RB6/PGC                | 27    | 24    | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin. Serial programming clock.                                                                                                                                                          |  |

| RB7/PGD                | 28    | 25    | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin. Serial programming data.                                                                                                                                                           |  |

|                        |       |       |               |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                         |  |

| RC0/T1OSO/<br>T1CKI    | 11    | 8     | I/O           | ST                     | RC0 can also be the Timer1 oscillator output or Timer1 clock input                                                                                                                                          |  |

| RC1/T1OSI              | 12    | 9     | I/O           | ST                     | RC1 can also be the Timer1 oscillator input.                                                                                                                                                                |  |

| RC2/CCP1               | 13    | 10    | I/O           | ST                     | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                                                                                                                         |  |

| RC3/SCK/SCL            | 14    | 11    | I/O           | ST                     | RC3 can also be the synchronous serial clock input/output for both SPI and I <sup>2</sup> C modes.                                                                                                          |  |

| RC4/SDI/SDA            | 15    | 12    | I/O           | ST                     | RC4 can also be the SPI Data In (SPI mode) or Data I/O (I <sup>2</sup> C mode).                                                                                                                             |  |

| RC5/SDO                | 16    | 13    | I/O           | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                |  |

| RC6                    | 17    | 14    | I/O           | ST                     |                                                                                                                                                                                                             |  |

| RC7                    | 18    | 15    | I/O           | ST                     |                                                                                                                                                                                                             |  |

| Vss                    | 8, 19 | 5, 16 | Р             | _                      | Ground reference for logic and I/O pins.                                                                                                                                                                    |  |

| Vdd                    | 20    | 17    | Р             | _                      | Positive supply for logic and I/O pins.                                                                                                                                                                     |  |

— = Not used TTL = TTL input ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

# 2.0 MEMORY ORGANIZATION

There are two memory blocks in the PIC16F72 device. These are the program memory and the data memory. Each block has separate buses so that concurrent access can occur. Program memory and data memory are explained in this section. Program memory can be read internally by the user code (see Section 7.0).

The data memory can further be broken down into the general purpose RAM and the Special Function Registers (SFRs). The operation of the SFRs that control the "core" are described here. The SFRs used to control the peripheral modules are described in the section discussing each individual peripheral module.

Additional information on device memory may be found in the PIC<sup>™</sup> Mid-Range Reference Manual, (DS33023).

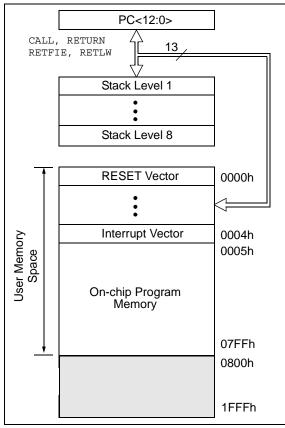

## 2.1 Program Memory Organization

PIC16F72 devices have a 13-bit program counter capable of addressing a 8K x 14 program memory space. The address range for this program memory is 0000h - 07FFh. Accessing a location above the physically implemented address will cause a wraparound.

The RESET Vector is at 0000h and the Interrupt Vector is at 0004h.

#### FIGURE 2-1: PROGRAM MEMORY MAP AND STACK

# 2.2 Data Memory Organization

The Data Memory is partitioned into multiple banks that contain the General Purpose Registers and the Special Function Registers. Bits RP1 (STATUS<6>) and RP0 (STATUS<5>) are the bank select bits.

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM.

All implemented banks contain SFRs. Some "high use" SFRs from one bank may be mirrored in another bank, for code reduction and quicker access (e.g., the STATUS register is in Banks 0 - 3).

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly, through the File Select Register FSR (see Section 2.5).

| Name         | Bit#  | Buffer | Function                                                                        |

|--------------|-------|--------|---------------------------------------------------------------------------------|

| RA0/AN0      | bit 0 | TTL    | Input/output or analog input.                                                   |

| RA1/AN1      | bit 1 | TTL    | Input/output or analog input.                                                   |

| RA2/AN2      | bit 2 | TTL    | Input/output or analog input.                                                   |

| RA3/AN3/VREF | bit 3 | TTL    | Input/output or analog input or VREF.                                           |

| RA4/T0CKI    | bit 4 | ST     | Input/output or external clock input for Timer0. Output is open drain type.     |

| RA5/AN4/SS   | bit 5 | TTL    | Input/output or analog input or slave select input for synchronous serial port. |

#### TABLE 3-1:PORTA FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5   | Bit 4     | Bit 3     | Bit 2  | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>RESETS |

|---------|--------|-------|-------|---------|-----------|-----------|--------|-------|-------|----------------------|---------------------------------|

| 05h     | PORTA  | —     | —     | RA5     | RA4       | RA3       | RA2    | RA1   | RA0   | 0x 0000              | 0u 0000                         |

| 85h     | TRISA  | _     | _     | PORTA I | Data Dire | ction Reg | gister |       |       | 11 1111              | 11 1111                         |

| 9Fh     | ADCON1 | _     | —     | —       | _         | _         | PCFG2  | PCFG1 | PCFG0 | 000                  | 000                             |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

**Note:** When using the SSP module in SPI Slave mode and  $\overline{SS}$  enabled, the A/D Port Configuration Control bits (PCFG2:PCFG0) in the A/D Control Register (ADCON1) must be set to one of the following configurations: 100, 101, 11x.

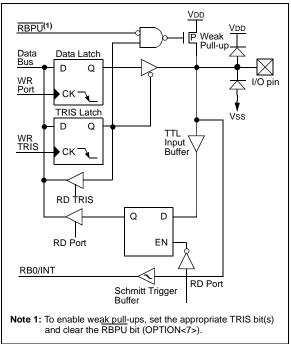

### 3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

EXAMPLE 3-2: INITIALIZING PORTB

| BANKSEL | PORTB | ; Select bank for PORTB |

|---------|-------|-------------------------|

| CLRF    | PORTB | ; Initialize PORTB by   |

|         |       | ; clearing output       |

|         |       | ; data latches          |

| BANKSEL | TRISB | ; Select Bank for TRISB |

| MOVLW   | 0xCF  | ; Value used to         |

|         |       | ; initialize data       |

|         |       | ; direction             |

| MOVWF   | TRISB | ; Set RB<3:0> as inputs |

|         |       | ; RB<5:4> as outputs    |

|         |       | ; RB<7:6> as inputs     |

|         |       |                         |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

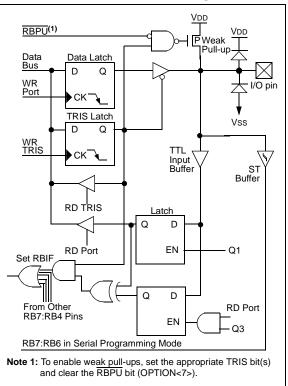

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'd together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

This interrupt-on-mismatch feature, together with software configurable pull-ups on these four pins, allow easy interface to a keypad and make it possible for wake-up on key depression. Refer to the Embedded Control Handbook, *"Implementing Wake-Up on Key Stroke"* (AN552).

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION<6>).

#### FIGURE 3-4: BLOCK DIAGRAM OF RB7:RB4 PINS

## 8.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The CCP (Capture/Compare/PWM) module contains a 16-bit register that can operate as a:

- 16-bit capture register

- 16-bit compare register

- PWM master/slave duty cycle register.

Table 8-1 shows the timer resources of the CCP Module modes.

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable. Additional information on the CCP module is available in the PIC<sup>™</sup> Mid-Range MCU Reference Manual, (DS33023).

# TABLE 8-1:CCP MODE - TIMER<br/>RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

#### **REGISTER 8-1:** CCPCON1: CAPTURE/COMPARE/PWM CONTROL REGISTER 1 (ADDRESS 17h)

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

| —     | _   | CCPxX | CCPxY | CCPxM3 | CCPxM2 | CCPxM1 | CCPxM0 |

| bit 7 |     |       |       |        |        |        | bit 0  |

- bit 7-6 Unimplemented: Read as '0'

- bit 5-4 CCPxX:CCPxY: PWM Least Significant bits Capture mode:

|         | Capture mode:                                                                                                                                                       |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Unused                                                                                                                                                              |

|         | Compare mode:                                                                                                                                                       |

|         | Unused                                                                                                                                                              |

|         | PWM mode:                                                                                                                                                           |

|         | These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                                              |

| bit 3-0 | CCPxM3:CCPxM0: CCPx Mode Select bits                                                                                                                                |

|         | 0000 = Capture/Compare/PWM disabled (resets CCPx module)                                                                                                            |

|         | 0100 = Capture mode, every falling edge                                                                                                                             |

|         | 0101 = Capture mode, every rising edge                                                                                                                              |

|         | 0110 = Capture mode, every 4th rising edge                                                                                                                          |

|         | 0111 = Capture mode, every 16th rising edge                                                                                                                         |

|         | 1000 = Compare mode, set output on match (CCPxIF bit is set)                                                                                                        |

|         | 1001 = Compare mode, clear output on match (CCPxIF bit is set)                                                                                                      |

|         | 1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set,                                                                                       |

|         | CCPx pin is unaffected)                                                                                                                                             |

|         | 1011 = Compare mode, trigger special event (CCPxIF bit is set, CCPx pin is unaffected);<br>CCP1 resets TMR1 and starts an A/D conversion (if A/D module is enabled) |

|         | 11xx = PWM mode                                                                                                                                                     |

|         |                                                                                                                                                                     |

|         |                                                                                                                                                                     |

|         | Legend:                                                                                                                                                             |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

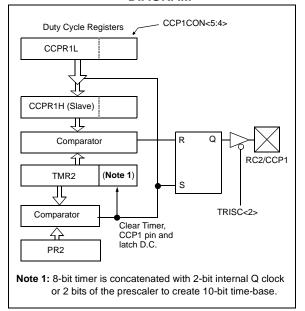

## 8.3 PWM Mode

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force  |

|-------|-------------------------------------------|

|       | the CCP1 PWM output latch to the default  |

|       | low level. This is not the PORTC I/O data |

|       | latch.                                    |

Figure 8-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step by step procedure on how to set up the CCP module for PWM operation, see Section 8.3.3.

#### FIGURE 8-3: SIMPLIFIED PWM BLOCK DIAGRAM

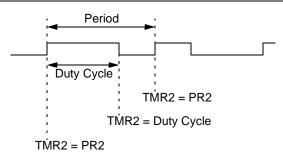

A PWM output (Figure 8-4) has a time-base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### FIGURE 8-4: PWM OUTPUT

#### 8.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the formula in Equation 8-1.

### EQUATION 8-1: PWM PERIOD

$PWM period = [(PR2) + 1] \bullet 4 \bullet TOSC \bullet$ (TMR2 prescale value)

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

Note: The Timer2 postscaler (see Section 6.0) is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

#### 8.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available: the CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. Equation 8-2 is used to calculate the PWM duty cycle in time.

#### EQUATION 8-2: PWM DUTY CYCLE

PWM duty cycle = (CCPR1L:CCP1CON<5:4>) • TOSC • (TMR2 prescale value)

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

| STER 9-1:     | SSPSTAT: SYNCHRONOUS SERIAL PORT STATUS REGISTER (ADDRESS 94h)                                                                                                                                                                             |                                                                   |                            |                                 |             |                      |              |         |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------|---------------------------------|-------------|----------------------|--------------|---------|--|

|               | R/W-0                                                                                                                                                                                                                                      | R/W-0                                                             | R-0                        | R-0                             | R-0         | R-0                  | R-0          | R-0     |  |

|               | SMP                                                                                                                                                                                                                                        | CKE                                                               | D/A                        | Р                               | S           | R/W                  | UA           | BF      |  |

|               | bit 7                                                                                                                                                                                                                                      |                                                                   |                            |                                 |             |                      |              | bit 0   |  |

| bit 7         | SMP: SPI Data Input Sample Phase bits<br>SPI Master mode:                                                                                                                                                                                  |                                                                   |                            |                                 |             |                      |              |         |  |

|               | 1 = Input da                                                                                                                                                                                                                               | ata sampled<br>ata sampled                                        |                            | ata output tim<br>f data output |             | owire <sup>®</sup> ) |              |         |  |

|               |                                                                                                                                                                                                                                            |                                                                   | /hen SPI is                | used in Slave                   | e mode      |                      |              |         |  |

|               | This bit mu                                                                                                                                                                                                                                | st be mainta                                                      | ined clear                 |                                 |             |                      |              |         |  |

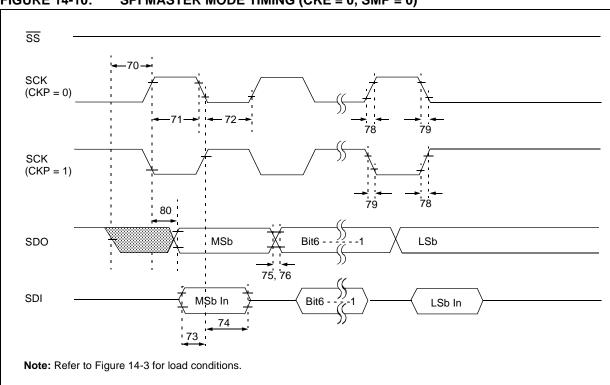

| bit 6         | CKE: SPI (                                                                                                                                                                                                                                 | Clock Edge S                                                      | Select bits (F             | Figure 9-2, Fi                  | gure 9-3, a | nd Figure 9-4        | 4)           |         |  |

|               | <u>SPI mode, CKP = 0:</u><br>1 = Data transmitted on rising edge of SCK (Microwire alternate)<br>0 = Data transmitted on falling edge of SCK                                                                                               |                                                                   |                            |                                 |             |                      |              |         |  |

|               | <u>SPI mode, CKP = 1:</u><br>1 = Data transmitted on falling edge of SCK (Microwire default)<br>0 = Data transmitted on rising edge of SCK<br><u>I<sup>2</sup>C mode:</u>                                                                  |                                                                   |                            |                                 |             |                      |              |         |  |

| 6.14 <b>F</b> |                                                                                                                                                                                                                                            | st be mainta                                                      |                            | - 1- 3                          |             |                      |              |         |  |

| bit 5         | <b>D/A:</b> Data/Address bit (I <sup>2</sup> C mode only)<br>1 = Indicates that the last byte received or transmitted was data                                                                                                             |                                                                   |                            |                                 |             |                      |              |         |  |

|               |                                                                                                                                                                                                                                            |                                                                   |                            | eived or trans                  |             |                      |              |         |  |

| bit 4         | <b>P:</b> STOP bit (I <sup>2</sup> C mode only) – This bit is cleared when the SSP module is disabled, or when the START bit is detected last. SSPEN is cleared.                                                                           |                                                                   |                            |                                 |             |                      |              |         |  |

|               | <ul> <li>1 = Indicates that a STOP bit has been detected last (this bit is '0' on RESET)</li> <li>0 = STOP bit was not detected last</li> </ul>                                                                                            |                                                                   |                            |                                 |             |                      |              |         |  |

| bit 3         | <b>S:</b> START bit (I <sup>2</sup> C mode only) – This bit is cleared when the SSP module is disabled, or when the STOP bit is detected last. SSPEN is cleared.                                                                           |                                                                   |                            |                                 |             |                      |              |         |  |

|               | <ul> <li>1 = Indicates that a START bit has been detected last (this bit is '0' on RESET)</li> <li>0 = START bit was not detected last</li> </ul>                                                                                          |                                                                   |                            |                                 |             |                      |              |         |  |

| bit 2         | <b>R/W</b> : Read/Write Information bit (I <sup>2</sup> C mode only) – This bit holds the R/W bit information following the last address match. This bit is only valid from the address match to the next START bit, STOP bit, or ACK bit. |                                                                   |                            |                                 |             |                      |              |         |  |

|               | 1 = Read<br>0 = Write                                                                                                                                                                                                                      |                                                                   |                            |                                 |             |                      |              |         |  |

| bit 1         | UA: Update                                                                                                                                                                                                                                 | e Address bi                                                      | t (10-bit I <sup>2</sup> C | mode only)                      |             |                      |              |         |  |

|               |                                                                                                                                                                                                                                            | es that the us<br>s does not n                                    |                            |                                 | address in  | the SSPADD           | register     |         |  |

| bit 0         | BF: Buffer                                                                                                                                                                                                                                 | Full Status b                                                     | it                         |                                 |             |                      |              |         |  |

|               | <u>Receive (SPI and I<sup>2</sup>C modes):</u><br>1 = Receive complete, SSPBUF is full<br>0 = Receive not complete, SSPBUF is empty                                                                                                        |                                                                   |                            |                                 |             |                      |              |         |  |

|               | -                                                                                                                                                                                                                                          |                                                                   |                            | - is empty                      |             |                      |              |         |  |

|               | 1 = Transm                                                                                                                                                                                                                                 | <sup>2</sup> C mode onl <u>i</u><br>it in progres<br>it complete, | s, SSPBUF                  |                                 |             |                      |              |         |  |

|               | Legend:                                                                                                                                                                                                                                    |                                                                   |                            |                                 |             |                      |              |         |  |

|               | R = Readal                                                                                                                                                                                                                                 | ole bit                                                           | W = W                      | /ritable bit                    | U = Unir    | nplemented b         | oit, read as | '0'     |  |

|               | - n = Value                                                                                                                                                                                                                                | at POR                                                            | <u>'1' = B</u>             | it is set                       | '0' = Bit   | is cleared           | x = Bit is u | Inknown |  |

In 10-bit Address mode, two address bytes need to be received by the slave device. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit  $R/\overline{W}$  (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address.

The sequence of events for 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF, and bit UA (SSPSTAT<1>) are set).

- 2. Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF, and UA are set).

- 5. Update the SSPADD register with the first (high) byte of Address, if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated START condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

### 9.3.1.2 Reception

When the R/W bit of the address byte is clear and an address match occurs, the R/W bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then a no Acknowledge (ACK) pulse is given. An overflow condition is indicated if either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON<6>) is set.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

#### 9.3.1.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit, and pin RC3/SCK/SCL is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master device must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master device by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 9-7).

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software and the SSPSTAT register is used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the ACK pulse from the masterreceiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not ACK), then the data transfer is complete. When the ACK is latched by the slave device, the slave logic is reset (resets SSPSTAT register) and the slave device then monitors for another occurrence of the START bit. If the SDA line was low (ACK), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, pin RC3/SCK/SCL should be enabled by setting bit CKP.

| TABLE 9-2: | DATA TRANSFER RECEIVED BYTE ACTIO | NS    |

|------------|-----------------------------------|-------|

| IADLE 3-Z. | DATA TRANSFER RECEIVED BITE ACTIO | UND - |

| Status Bits as Data<br>Transfer is Received |       |                            |                    | Set bit SSPIF                     |

|---------------------------------------------|-------|----------------------------|--------------------|-----------------------------------|

| BF                                          | SSPOV | $SSPSR \rightarrow SSPBUF$ | Generate ACK Pulse | (SSP Interrupt occurs if enabled) |

| 0                                           | 0     | Yes                        | Yes                | Yes                               |

| 1                                           | 0     | No                         | No                 | Yes                               |

| 1                                           | 1     | No                         | No                 | Yes                               |

| 0                                           | 1     | No                         | No                 | Yes                               |

**Note 1:** Shaded cells show the conditions where the user software did not properly clear the overflow condition.

# **PIC16F72**

#### REGISTER 10-2: ADCON1: A/D CONTROL REGISTER 1 (ADDRESS 9Fh)

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-----|-------|-------|-------|

| —     | —   | —   | —   | —   | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |     |     |     |       |       | bit 0 |

bit 7-3 Unimplemented: Read as '0'

bit 2-0

PCFG<2:0>: A/D Port Configuration Control bits

| PCFG2:PCFG0 | RA0 | RA1 | RA2 | RA5 | RA3  | VREF |

|-------------|-----|-----|-----|-----|------|------|

| 000         | Α   | А   | Α   | А   | А    | Vdd  |

| 001         | Α   | А   | Α   | А   | Vref | RA3  |

| 010         | Α   | А   | Α   | А   | А    | Vdd  |

| 011         | Α   | А   | Α   | А   | Vref | RA3  |

| 100         | Α   | Α   | D   | D   | А    | Vdd  |

| 101         | Α   | А   | D   | D   | Vref | RA3  |

| 11x         | D   | D   | D   | D   | D    | Vdd  |

A = Analog input

D = Digital I/O

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

The ADRES register contains the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRES register, the GO/DONE bit (ADCON0<2>) is cleared, and A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 10-1.

The value in the ADRES register is not modified for a Power-on Reset. The ADRES register will contain unknown data after a Power-on Reset.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see Section 10.1. After this acquisition time has elapsed, the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins/voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared

OR

- Waiting for the A/D interrupt

- 6. Read A/D Result register (ADRES), clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2 TAD is required before the next acquisition starts.

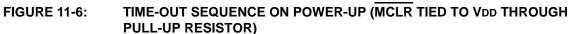

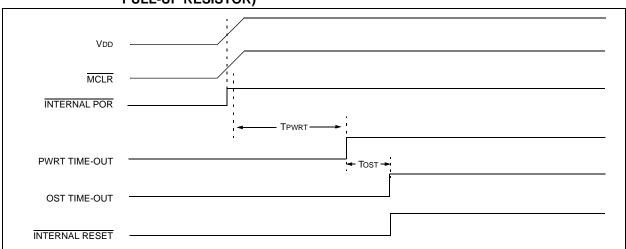

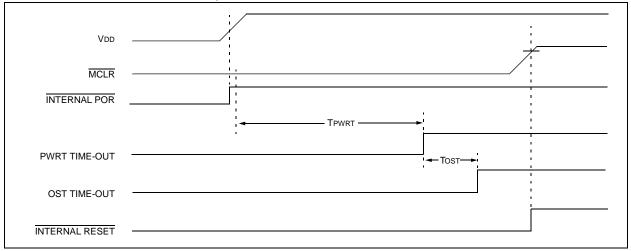

FIGURE 11-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD THROUGH RC NETWORK): CASE 1

FIGURE 11-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD THROUGH RC NETWORK): CASE 2

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                         |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                              |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' = '0', the next instruction is executed.<br>If bit 'b' = '1', then the next instruction is discarded and a NOP is executed instead, making this a 2 TCY instruction. |

| CLRF             | Clear f                                                               |  |  |

|------------------|-----------------------------------------------------------------------|--|--|

| Syntax:          | [label] CLRF f                                                        |  |  |

| Operands:        | $0 \le f \le 127$                                                     |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |  |  |

| Status Affected: | Z                                                                     |  |  |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |  |  |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                                 |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSC f,b                                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                     |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                                    |

| Status Affected: | None                                                                                                                                                                                                                    |

| Description:     | If bit 'b' in register 'f' = '1', the next<br>instruction is executed.<br>If bit 'b' in register 'f' = '0', the next<br>instruction is discarded, and a NOP<br>is executed instead, making this a<br>2 TCY instruction. |

| CLRW             | Clear W                                                                                    |

|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                                               |

| Operands:        | None                                                                                       |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow (\text{W}) \\ 1 \rightarrow \text{Z} \end{array}$ |

| Status Affected: | Z                                                                                          |

| Description:     | W register is cleared. Zero bit (Z) is set.                                                |

| CALL             | Call Subroutine                                                                                                                                                                                             | CLRWDT           | Clear Watchdog Timer                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                     | Syntax:          | [label] CLRWDT                                                                                                                 |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                          | Operands:        | None                                                                                                                           |

| Operation:       | (PC) + 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                           | Operation:       | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \end{array}$      |

| Status Affected: | None                                                                                                                                                                                                        |                  | $1 \rightarrow PD$                                                                                                             |

| Description:     | Call Subroutine. First, return                                                                                                                                                                              | Status Affected: | TO, PD                                                                                                                         |

|                  | address (PC+1) is pushed onto<br>the stack. The eleven-bit immedi-<br>ate address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a two-cycle instruction. | Description:     | CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT. Status bits<br>TO and PD are set. |

## 13.13 PICDEM 3 Low Cost PIC16CXXX Demonstration Board

The PICDEM 3 demonstration board is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with an LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 3 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer with an adapter socket, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 3 demonstration board to test firmware. A prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM 3 demonstration board is a LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM 3 demonstration board provides an additional RS-232 interface and Windows software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

## 13.14 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. All necessary hardware is included to run basic demo programs, which are supplied on a 3.5-inch disk. A programmed sample is included and the user may erase it and program it with the other sample programs using the PRO MATE II device programmer, or the PICSTART Plus development programmer, and easily debug and test the sample code. In addition, the PICDEM 17 demonstration board supports downloading of programs to and executing out of external FLASH memory on board. The PICDEM 17 demonstration board is also usable with the MPLAB ICE in-circuit emulator, or the PICMASTER emulator and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

## 13.15 KEELOQ Evaluation and Programming Tools

KEELOQ evaluation and programming tools support Microchip's HCS Secure Data Products. The HCS evaluation kit includes a LCD display to show changing codes, a decoder to decode transmissions and a programming interface to program test transmitters.

# 14.3 Timing Parameter Symbology

The timing parameter symbols have been created following one of the following formats:

|                                     | 0                                                                                                                                                                                                                                                                                                                                                                                            | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. TppS2ppS                         |                                                                                                                                                                                                                                                                                                                                                                                              | (I <sup>2</sup> C specifications only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2. TppS                             |                                                                                                                                                                                                                                                                                                                                                                                              | (I <sup>2</sup> C specifications only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Frequency                           | Т                                                                                                                                                                                                                                                                                                                                                                                            | Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CCP1                                | OSC                                                                                                                                                                                                                                                                                                                                                                                          | OSC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CLKO                                | rd                                                                                                                                                                                                                                                                                                                                                                                           | RD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CS                                  | rw                                                                                                                                                                                                                                                                                                                                                                                           | RD or WR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SDI                                 | SC                                                                                                                                                                                                                                                                                                                                                                                           | SCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SDO                                 | SS                                                                                                                                                                                                                                                                                                                                                                                           | SS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Data in                             | tO                                                                                                                                                                                                                                                                                                                                                                                           | TOCKI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| I/O port                            | t1                                                                                                                                                                                                                                                                                                                                                                                           | T1CKI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MCLR                                | wr                                                                                                                                                                                                                                                                                                                                                                                           | WR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| se letters and their meanings:      |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |