# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I²C, SPI                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-QFN (6x6)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf72-i-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Device Overview                              |    |

|-------|----------------------------------------------|----|

| 2.0   | Memory Organization                          | 7  |

| 3.0   | I/O Ports                                    |    |

| 4.0   | Reading Program Memory                       | 27 |

| 5.0   | Timer0 Module                                |    |

| 6.0   | Timer1 Module                                | 31 |

| 7.0   | Timer2 Module                                | 35 |

| 8.0   | Capture/Compare/PWM (CCP) Module             | 37 |

| 9.0   | Synchronous Serial Port (SSP) Module         |    |

| 10.0  | Analog-to-Digital Converter (A/D) Module     |    |

| 11.0  | Special Features of the CPU                  | 59 |

| 12.0  | Instruction Set Summary                      |    |

| 13.0  | Development Support                          | 81 |

| 14.0  | Electrical Characteristics                   | 87 |

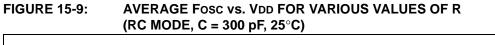

| 15.0  | DC and AC Characteristics Graphs and Tables1 | 07 |

| 16.0  | Package Marking Information1                 | 17 |

| Appe  | ndix A: Revision History1                    | 23 |

|       | ndix B: Conversion Considerations1           |    |

| Index |                                              | 25 |

| On-Li | ne Support1                                  | 31 |

|       | er Response 1                                |    |

| Produ | ict Identification System 1                  | 33 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## 2.0 MEMORY ORGANIZATION

There are two memory blocks in the PIC16F72 device. These are the program memory and the data memory. Each block has separate buses so that concurrent access can occur. Program memory and data memory are explained in this section. Program memory can be read internally by the user code (see Section 7.0).

The data memory can further be broken down into the general purpose RAM and the Special Function Registers (SFRs). The operation of the SFRs that control the "core" are described here. The SFRs used to control the peripheral modules are described in the section discussing each individual peripheral module.

Additional information on device memory may be found in the PIC<sup>™</sup> Mid-Range Reference Manual, (DS33023).

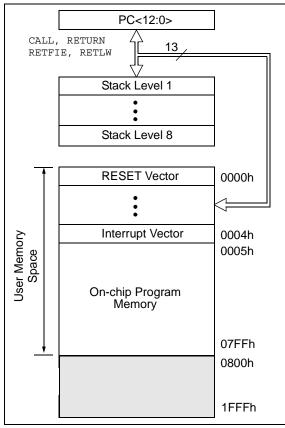

## 2.1 Program Memory Organization

PIC16F72 devices have a 13-bit program counter capable of addressing a 8K x 14 program memory space. The address range for this program memory is 0000h - 07FFh. Accessing a location above the physically implemented address will cause a wraparound.

The RESET Vector is at 0000h and the Interrupt Vector is at 0004h.

#### FIGURE 2-1: PROGRAM MEMORY MAP AND STACK

## 2.2 Data Memory Organization

The Data Memory is partitioned into multiple banks that contain the General Purpose Registers and the Special Function Registers. Bits RP1 (STATUS<6>) and RP0 (STATUS<5>) are the bank select bits.

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM.

All implemented banks contain SFRs. Some "high use" SFRs from one bank may be mirrored in another bank, for code reduction and quicker access (e.g., the STATUS register is in Banks 0 - 3).

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly, through the File Select Register FSR (see Section 2.5).

#### 2.2.2.4 PIE1 Register

This register contains the individual enable bits for the peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

- n = Value at POR

#### REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1 (ADDRESS 8Ch)

| ER 2-4: | PIET: PER                                | IPHERAL      | INTERRU         |               | REGISTI  |             | KE33 00      | n)     |  |

|---------|------------------------------------------|--------------|-----------------|---------------|----------|-------------|--------------|--------|--|

|         | U-0                                      | R/W-0        | U-0             | U-0           | R/W-0    | R/W-0       | R/W-0        | R/W-0  |  |

|         | —                                        | ADIE         | —               | —             | SSPIE    | CCP1IE      | TMR2IE       | TMR1IE |  |

|         | bit 7                                    |              |                 |               |          |             |              | bit 0  |  |

| bit 7   | Unimpleme                                | ented: Rea   | d as '0'        |               |          |             |              |        |  |

| bit 6   | •                                        |              | nterrupt Enal   | hla hit       |          |             |              |        |  |

| DILO    |                                          |              | onverter inter  |               |          |             |              |        |  |

|         |                                          |              | onverter inte   |               |          |             |              |        |  |

| bit 5-4 | Unimplemented: Read as '0'               |              |                 |               |          |             |              |        |  |

| bit 3   | SSPIE: Syr                               | nchronous S  | Serial Port Int | terrupt Enabl | e bit    |             |              |        |  |

|         | 1 = Enables                              |              |                 |               |          |             |              |        |  |

|         | 0 = Disable                              | es the SSP i | nterrupt        |               |          |             |              |        |  |

| bit 2   | CCP1IE: C                                | CP1 Interru  | pt Enable bit   |               |          |             |              |        |  |

|         | 1 = Enables                              |              |                 |               |          |             |              |        |  |

|         | 0 = Disable                              | s the CCP1   | interrupt       |               |          |             |              |        |  |

| bit 1   | TMR2IE: TI                               | MR2 to PR2   | 2 Match Inter   | rupt Enable b | oit      |             |              |        |  |

|         |                                          |              | to PR2 mate     |               |          |             |              |        |  |

|         | 0 = Disable                              | es the TMR2  | 2 to PR2 mat    | ch interrupt  |          |             |              |        |  |

| bit 0   | TMR1IE: T                                | MR1 Overfl   | ow Interrupt    | Enable bit    |          |             |              |        |  |

|         | 1 = Enables the TMR1 overflow interrupt  |              |                 |               |          |             |              |        |  |

|         | 0 = Disables the TMR1 overflow interrupt |              |                 |               |          |             |              |        |  |

|         | Legend:                                  |              |                 |               |          |             |              |        |  |

|         | R = Readab                               | ole bit      | W = W           | /ritable bit  | U = Unim | plemented I | oit, read as | '0'    |  |

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

## 8.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The CCP (Capture/Compare/PWM) module contains a 16-bit register that can operate as a:

- 16-bit capture register

- 16-bit compare register

- PWM master/slave duty cycle register.

Table 8-1 shows the timer resources of the CCP Module modes.

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable. Additional information on the CCP module is available in the PIC<sup>™</sup> Mid-Range MCU Reference Manual, (DS33023).

## TABLE 8-1:CCP MODE - TIMER<br/>RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

#### **REGISTER 8-1:** CCPCON1: CAPTURE/COMPARE/PWM CONTROL REGISTER 1 (ADDRESS 17h)

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

| —     | _   | CCPxX | CCPxY | CCPxM3 | CCPxM2 | CCPxM1 | CCPxM0 |

| bit 7 |     |       |       |        |        |        | bit 0  |

- bit 7-6 Unimplemented: Read as '0'

- bit 5-4 CCPxX:CCPxY: PWM Least Significant bits Capture mode:

|         | Capture mode:                                                                                                                                                       |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Unused                                                                                                                                                              |

|         | Compare mode:                                                                                                                                                       |

|         | Unused                                                                                                                                                              |

|         | PWM mode:                                                                                                                                                           |

|         | These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                                              |

| bit 3-0 | CCPxM3:CCPxM0: CCPx Mode Select bits                                                                                                                                |

|         | 0000 = Capture/Compare/PWM disabled (resets CCPx module)                                                                                                            |

|         | 0100 = Capture mode, every falling edge                                                                                                                             |

|         | 0101 = Capture mode, every rising edge                                                                                                                              |

|         | 0110 = Capture mode, every 4th rising edge                                                                                                                          |

|         | 0111 = Capture mode, every 16th rising edge                                                                                                                         |

|         | 1000 = Compare mode, set output on match (CCPxIF bit is set)                                                                                                        |

|         | 1001 = Compare mode, clear output on match (CCPxIF bit is set)                                                                                                      |

|         | 1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set,                                                                                       |

|         | CCPx pin is unaffected)                                                                                                                                             |

|         | 1011 = Compare mode, trigger special event (CCPxIF bit is set, CCPx pin is unaffected);<br>CCP1 resets TMR1 and starts an A/D conversion (if A/D module is enabled) |

|         | 11xx = PWM mode                                                                                                                                                     |

|         |                                                                                                                                                                     |

|         |                                                                                                                                                                     |

|         | Legend:                                                                                                                                                             |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

Maximum PWM resolution (bits) for a given PWM frequency is calculated using Equation 8-3.

#### EQUATION 8-3: PWM MAX RESOLUTION

PWM Maximum Resolution =  $\frac{\log{(\frac{Fosc}{FpWM})}}{\log(2)}$  bits

| Note: | If the PWM duty cycle value is longer than |

|-------|--------------------------------------------|

|       | the PWM period, the CCP1 pin will not be   |

|       | cleared.                                   |

For a sample PWM period and duty cycle calculation, see the PIC<sup>™</sup> Mid-Range MCU Reference Manual (DS33023).

#### 8.3.3 SET-UP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

| <b>TABLE 8-3</b> : | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz |

|--------------------|---------------------------------------------------|

|                    |                                                   |

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

#### TABLE 8-4: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address              | Name    | Bit 7  | Bit 6                               | Bit 5        | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   |      | Value on<br>POR, BOR |      | Value on all |  | e on<br>ther<br>ETS |

|----------------------|---------|--------|-------------------------------------|--------------|---------|---------|--------|---------|---------|------|----------------------|------|--------------|--|---------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE    | PEIE                                | TMR0IE       | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000 | 000x                 | 0000 | 000u         |  |                     |

| 0Ch                  | PIR1    | _      | ADIF                                | _            | _       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | - 0  | 0000                 | 0000 | 0000         |  |                     |

| 8Ch                  | PIE1    | —      | ADIE                                | _            | _       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | - 0  | 0000                 | 0000 | 0000         |  |                     |

| 87h                  | TRISC   | PORT   | C Data Dire                         | ction Regis  | ter     |         |        |         |         | 1111 | 1111                 | 1111 | 1111         |  |                     |

| 11h                  | TMR2    | Timer2 | Timer2 Module Register              |              |         |         |        |         |         |      | 0000                 | 0000 | 0000         |  |                     |

| 92h                  | PR2     | Timer2 | Module Pe                           | riod Registe | r       |         |        |         |         | 1111 | 1111                 | 1111 | 1111         |  |                     |

| 12h                  | T2CON   | _      | TOUTPS3                             | TOUTPS2      | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 | 0000                 | -000 | 0000         |  |                     |

| 15h                  | CCPR1L  | Captur | Capture/Compare/PWM Register1 (LSB) |              |         |         |        |         |         |      | xxxx                 | uuuu | uuuu         |  |                     |

| 16h                  | CCPR1H  | Captur | Capture/Compare/PWM Register1 (MSB) |              |         |         |        |         |         |      | xxxx                 | uuuu | uuuu         |  |                     |

| 17h                  | CCP1CON | _      | _                                   | CCP1X        | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00   | 0000                 | 00   | 0000         |  |                     |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2.

## **10.1** A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 10-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current).

The maximum recommended impedance for analog sources is 10 k $\Omega$ . After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, TACQ, see the PIC<sup>TM</sup> Mid-Range MCU Reference Manual, (DS33023). In general, however, given a max of 10 k $\Omega$  and at a temperature of 100°C, TACQ will be no more than 16  $\mu$ s.

## 10.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 9.0 TAD per 8-bit conversion. The source of the A/D conversion clock is software selectable. The four possible options for TAD are:

- 2 Tosc

- 8 Tosc

- 32 Tosc

- Internal RC oscillator (2 6 μs)

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time as small as possible, but no less than 1.6  $\mu$ s and not greater than 6.4  $\mu$ s.

Table 10-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

## **10.3 Configuring Analog Port Pins**

The ADCON1, and TRISA registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS<2:0> bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs, will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- 2: Analog levels on any pin that is defined as a digital input (including the AN4:AN0 pins), may cause the input buffer to consume current out of the device specification.

#### 10.4 A/D Conversions

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRES register will NOT be updated with the partially completed A/D conversion sample. That is, the ADRES register will continue to contain the value of the last completed conversion (or the last value written to the ADRES register). After the A/D conversion is aborted, a 2 TAD wait is required before the next acquisition is started. After this 2 TAD wait, an acquisition is automatically started on the selected channel. The GO/DONE bit can then be set to start the conversion.

| AD Clock             | AD Clock Source (TAD) |          |

|----------------------|-----------------------|----------|

| Operation            | ADCS<1:0>             | Max.     |

| 2 Tosc               | 00                    | 1.25 MHz |

| 8 Tosc               | 01                    | 5 MHz    |

| 32 Tosc              | 10                    | 20 MHz   |

| RC <sup>(1, 2)</sup> | 11                    | (Note 1) |

#### TABLE 10-1: TAD VS. MAXIMUM DEVICE OPERATING FREQUENCIES (STANDARD DEVICES (C))

Note 1: The RC source has a typical TAD time of 4 µs, but can vary between 2-6 µs.

2: When the device frequencies are greater than 1 MHz, the RC A/D conversion clock source is only recommended for SLEEP operation.

## 11.5 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V - 1.7V). To take advantage of the POR, tie the MCLR pin to VDD, as described in Section 11.4. A maximum rise time for VDD is specified. See Section 14.0, Electrical Characteristics for details.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met. For more information, see Application Note, *AN607- Power-up Trouble Shooting* (DS00607).

## 11.6 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an accept-able level. A configuration bit is provided to enable/ disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature and process variation. See DC parameters for details (TPWRT, parameter #33).

## 11.7 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycles (from OSC1 input) delay after the PWRT delay is over (if enabled). This helps to ensure that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

## 11.8 Brown-out Reset (BOR)

The configuration bit, BOREN, can enable or disable the Brown-out Reset circuit. If VDD falls below VBOR (parameter D005, about 4V) for longer than TBOR (parameter #35, about 100  $\mu$ s), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a RESET may not occur.

Once the brown-out occurs, the device will remain in Brown-out Reset until VDD rises above VBOR. The Power-up Timer then keeps the device in RESET for TPWRT (parameter #33, about 72 ms). If VDD should fall below VBOR during TPWRT, the Brown-out Reset process will restart when VDD rises above VBOR, with the Power-up Timer Reset. The Power-up Timer is always enabled when the Brown-out Reset circuit is enabled, regardless of the state of the PWRT configuration bit.

## 11.9 Time-out Sequence

On power-up, the time-out sequence is as follows: the PWRT delay starts (if enabled) when a POR occurs. Then, OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS). When the OST ends, the device comes out of RESET.

If MCLR is kept low long enough, all delays will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16F72 device operating in parallel.

Table 11-5 shows the RESET conditions for the STATUS, PCON and PC registers, while Table 11-6 shows the RESET conditions for all the registers.

## 11.10 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON, has two bits to indicate the type of RESET that last occurred.

Bit0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent RESETS to see if bit BOR cleared, indicating a Brown-out Reset occurred. When the Brown-out Reset is disabled, the state of the BOR bit is unpredictable.

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

| Ossillator Configuration | Power-up          |            | Drown out         | Wake-up from |  |

|--------------------------|-------------------|------------|-------------------|--------------|--|

| Oscillator Configuration | PWRTEN = 0        | PWRTEN = 1 | Brown-out         | SLEEP        |  |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc  | 72 ms + 1024 Tosc | 1024 Tosc    |  |

| RC                       | 72 ms             | _          | 72 ms             | _            |  |

#### TABLE 11-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR<br>(PCON<1>) | BOR<br>(PCON<0>) | TO<br>(STATUS<4>) | PD<br>(STATUS<3>) | Significance                                            |

|------------------|------------------|-------------------|-------------------|---------------------------------------------------------|

| 0                | х                | 1                 | 1                 | Power-on Reset                                          |

| 0                | x                | 0                 | x                 | Illegal, TO is set on POR                               |

| 0                | х                | x                 | 0                 | Illegal, PD is set on POR                               |

| u                | 0                | 1                 | 1                 | Brown-out Reset                                         |

| u                | u                | 0                 | 1                 | WDT Reset                                               |

| u                | u                | 0                 | 0                 | WDT Wake-up                                             |

| u                | u                | u                 | u                 | MCLR Reset during normal operation                      |

| u                | u                | 1                 | 0                 | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

#### TABLE 11-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'.

**Note 1:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

#### TABLE 11-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS

| Register | Power-on Reset,<br>Brown-out Reset | MCLR Reset,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|----------|------------------------------------|--------------------------|---------------------------------|

| W        | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| INDF     | N/A                                | N/A                      | N/A                             |

| TMR0     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PCL      | 0000h                              | 0000h                    | PC + 1 <sup>(2)</sup>           |

| STATUS   | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <b>(3)</b>            |

| FSR      | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PORTA    | 0x 0000                            | Ou 0000                  | uu uuuu                         |

| PORTB    | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PORTC    | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PCLATH   | 0 0000                             | 0 0000                   | u uuuu                          |

| INTCON   | x000 0000 x                        | 0000 000u                | uuuu uuuu <b>(1)</b>            |

| PIR1     | -0 0000                            | -0 0000                  | -u uuuu <b>(1)</b>              |

| TMR1L    | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| TMR1H    | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| T1CON    | 00 0000                            | uu uuuu                  | uu uuuu                         |

| TMR2     | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| T2CON    | -000 0000                          | -000 0000                | -uuu uuuu                       |

| SSPBUF   | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| SSPCON   | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| CCPR1L   | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| CCPR1H   | xxxx xxxx                          | uuuu uuuu                | սսսս սսսս                       |

| CCP1CON  | 00 0000                            | 00 0000                  | uu uuuu                         |

| ADRES    | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON0   | 0000 00-0                          | 0000 00-0                | uuuu uu-u                       |

| OPTION   | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISA    | 11 1111                            | 11 1111                  | uu uuuu                         |

| TRISB    | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISC    | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| PIE1     | -0 0000                            | -0 0000                  | -u uuuu                         |

| PCON     | dd                                 | uu                       | uu                              |

| PR2      | 1111 1111                          | 1111 1111                | 1111 1111                       |

| SSPADD   | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| SSPSTAT  | 00 0000                            | 00 0000                  | uu uuuu                         |

| ADCON1   | 000                                | 000                      | uuu                             |

| PMDATL   | 0 0000                             | 0 0000                   | u uuuu                          |

| PMADRL   | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PMDATH   | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PMADRH   | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PMCON1   | 1 0                                | 1 0                      | 1u                              |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear.

**Note 1:** One or more bits in INTCON, PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**3:** See Table 11-5 for RESET value for specific condition.

#### FIGURE 11-12: WAKE-UP FROM SLEEP THROUGH INTERRUPT

| DSC1<br>CLKO <sup>(4)</sup> | ; Q1  Q2  Q3  Q4;<br>/~/<br>\/ |              |               |              | ; Q1 Q2 Q3 Q4;<br>;/~_/~_/~_/<br>\/ |                                       |             |

|-----------------------------|--------------------------------|--------------|---------------|--------------|-------------------------------------|---------------------------------------|-------------|

| NT pin                      | ı ı<br>ıı                      |              |               |              | I I                                 | 1<br>1                                |             |

| NTF Flag<br>INTCON<1>)      |                                |              |               |              | Interrupt Latency<br>(Note 2)       | · · · · · · · · · · · · · · · · · · · |             |

| GIE bit<br>INTCON<7>)       |                                |              | Processor in  |              |                                     | 1<br>1<br>1                           |             |

| NSTRUCTIO                   | N FLOW                         |              |               |              | ı ı<br>ı ı                          | 1                                     |             |

| PC                          | X PC                           | (PC+1        | <u>χ PC+2</u> | PC+2         | X PC + 2                            | <u>    0004h     </u> X               | 0005h       |

| etched                      | Inst(PC) = SLEEP               | Inst(PC + 1) |               | Inst(PC + 2) | 1 I<br>1 I                          | Inst(0004h)                           | Inst(0005h) |

| nstruction                  | Inst(PC - 1)                   | SLEEP        | · · ·         | Inst(PC + 1) | Dummy cycle                         | Dummy cycle                           | Inst(0004h) |

ote 1: XT, HS or LP Oscillator mode assumed.

- 2: TOST = 1024 TOSC (drawing not to scale) This delay will not be there for RC Osc mode.

- 3: GIE = '1' assumed. In this case, after wake-up, the processor jumps to the interrupt routine.

- If GIE = '0', execution will continue in-line.

- 4: CLKO is not available in these Osc modes, but shown here for timing reference.

## 11.15 Program Verification/ Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

#### 11.16 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify. It is recommended that only the four Least Significant bits of the ID location are used.

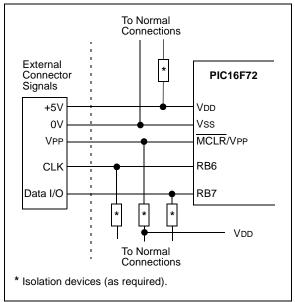

## 11.17 In-Circuit Serial Programming

PIC16F72 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground, and the programming voltage (see Figure 11-13 for an example). This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

For general information of serial programming, please refer to the In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) Guide (DS30277). For specific details on programming commands and operations for the PIC16F72 devices, please refer to the latest version of the PIC16F72 FLASH Program Memory Programming Specification (DS39588).

## FIGURE 11-13:

#### TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

| COMF             | Complement f                                                                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                         |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                           |

| Status Affected: | Z                                                                                                                                                         |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' = '0', the<br>result is stored in W. If 'd' = '1', the<br>result is stored back in register 'f'. |

| GOTO             | Unconditional Branch                                                                                                                                                                             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                          |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                               |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                  |

| Status Affected: | None                                                                                                                                                                                             |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>two-cycle instruction. |

| DECF             | Decrement f                                                                                                                                     | INCF             | Increment f                                                                                                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] DECF f,d                                                                                                                              | Syntax:          | [label] INCF f,d                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                      | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                        |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                             | Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                      |

| Status Affected: | Z                                                                                                                                               | Status Affected: | Z                                                                                                                                                                        |

| Description:     | Decrement register 'f'. If 'd' = '0',<br>the result is stored in the W<br>register. If 'd' = '1', the result is<br>stored back in register 'f'. | Description:     | The contents of register 'f' are<br>incremented. If 'd' = '0', the result<br>is placed in the W register. If<br>'d' = '1', the result is placed back<br>in register 'f'. |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                       | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                         |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                           | Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                                                                                                   | Operands:        | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                                                                                                                                                                                       |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                   | Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                     |

| Status Affected: | None                                                                                                                                                                                                                                                                                                         | Status Affected: | None                                                                                                                                                                                                                                                                                                                           |

| Description:     | The contents of register 'f' are decremented. If 'd' = '0', the result is placed in the W register. If 'd' = '1', the result is placed back in register 'f'.<br>If the result is '1', the next instruction is executed. If the result is '0', then a NOP is executed instead, making it a 2 TCY instruction. | Description:     | The contents of register 'f' are<br>incremented. If 'd' = '0', the result<br>is placed in the W register. If<br>'d' = '1', the result is placed back<br>in register 'f'.<br>If the result is '1', the next instruc-<br>tion is executed. If the result is '0',<br>a NOP is executed instead, making<br>it a 2 Tcy instruction. |

## 13.13 PICDEM 3 Low Cost PIC16CXXX Demonstration Board

The PICDEM 3 demonstration board is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with an LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 3 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer with an adapter socket, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 3 demonstration board to test firmware. A prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM 3 demonstration board is a LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM 3 demonstration board provides an additional RS-232 interface and Windows software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

## 13.14 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. All necessary hardware is included to run basic demo programs, which are supplied on a 3.5-inch disk. A programmed sample is included and the user may erase it and program it with the other sample programs using the PRO MATE II device programmer, or the PICSTART Plus development programmer, and easily debug and test the sample code. In addition, the PICDEM 17 demonstration board supports downloading of programs to and executing out of external FLASH memory on board. The PICDEM 17 demonstration board is also usable with the MPLAB ICE in-circuit emulator, or the PICMASTER emulator and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

## 13.15 KEELOQ Evaluation and Programming Tools

KEELOQ evaluation and programming tools support Microchip's HCS Secure Data Products. The HCS evaluation kit includes a LCD display to show changing codes, a decoder to decode transmissions and a programming interface to program test transmitters.

## 14.0 ELECTRICAL CHARACTERISTICS

## Absolute Maximum Ratings †

| Ambient temperature under bias55 to +1                                                                                                                                              | 25°C   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Storage temperature                                                                                                                                                                 | 50°C   |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)0.3V to (VDD + 0                                                                                                  | 0.3V)  |

| Voltage on VDD with respect to Vss                                                                                                                                                  | +6.5V  |

| Voltage on MCLR with respect to Vss (Note 2)0 to +1                                                                                                                                 |        |

| Voltage on RA4 with respect to Vss0 to -                                                                                                                                            | +12V   |

| Total power dissipation (Note 1)                                                                                                                                                    | 1.0W   |

| Maximum current out of Vss pin                                                                                                                                                      | 0 mA   |

| Maximum current into VDD pin                                                                                                                                                        | 0 mA   |

| Input clamp current, Iik (VI < 0 or VI > VDD)                                                                                                                                       | 0 mA   |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                                                                                                      | 0 mA   |

| Maximum output current sunk by any I/O pin2                                                                                                                                         | 5 mA   |

| Maximum output current sourced by any I/O pin                                                                                                                                       | 5 mA   |

| Maximum current sunk by PORTA, PORTB                                                                                                                                                | 0 mA   |

| Maximum current sourced by PORTA, PORTB                                                                                                                                             | 0 mA   |

| Maximum current sunk by PORTC                                                                                                                                                       | 0 mA   |

| Maximum current sourced by PORTC                                                                                                                                                    | 0 mA   |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD - VOH) x IOH} + $\sum$ (VOI x                                             | x Iol) |

| 2: Voltage spikes at the MCLR pin may cause unpredictable results. A series resistor of greater than should be used to pull MCLR to VDD, rather than tying the pin directly to VDD. | 1 kΩ   |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

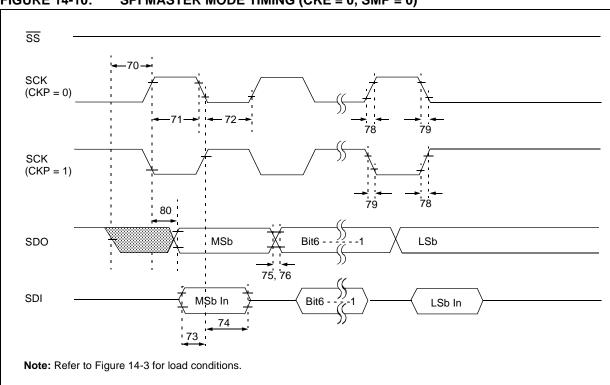

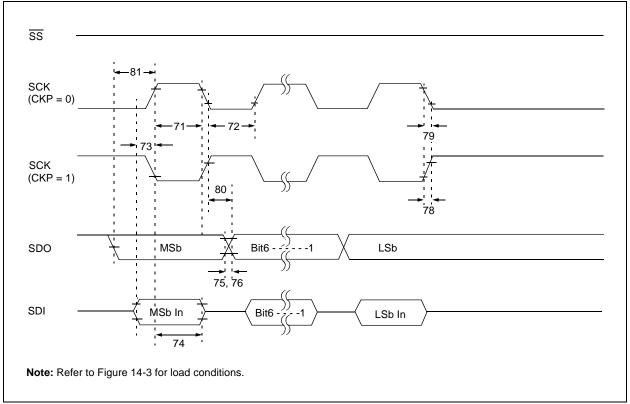

FIGURE 14-10: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

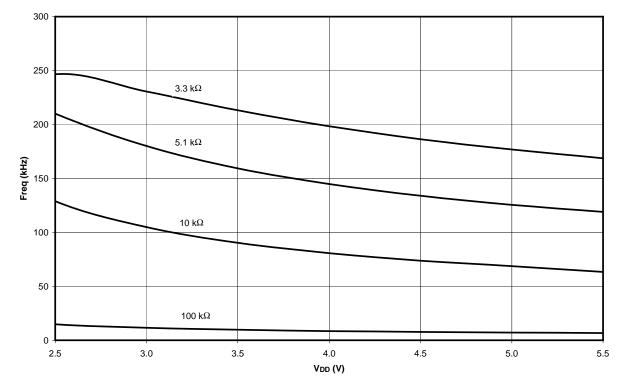

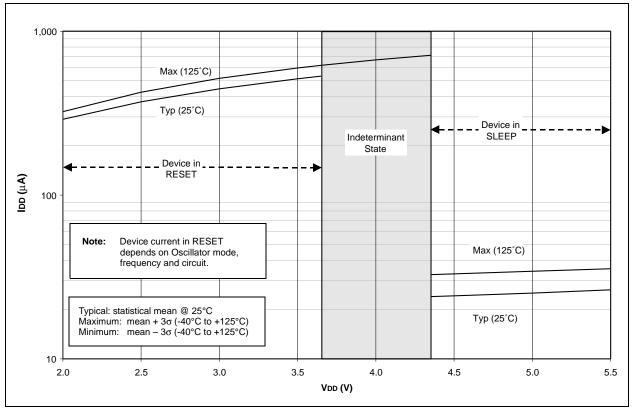

FIGURE 15-10: IPD vs. VDD (SLEEP MODE, ALL PERIPHERALS DISABLED)

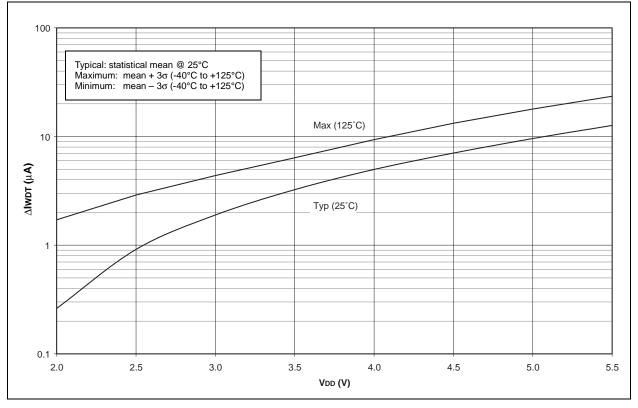

#### FIGURE 15-11: △IBOR vs. VDD OVER TEMPERATURE

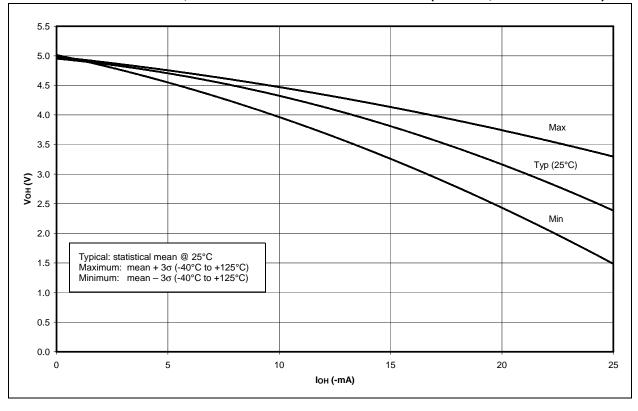

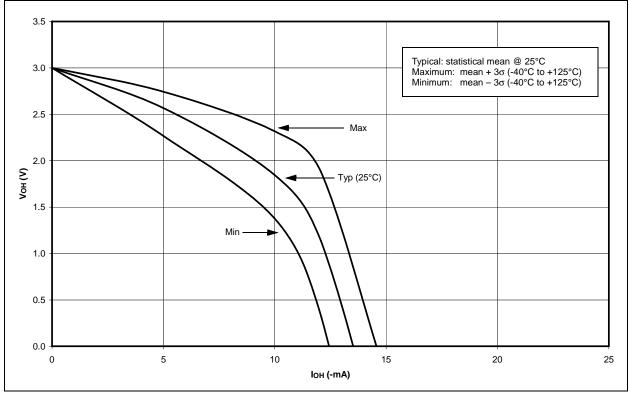

FIGURE 15-15: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD = 5V, -40°C TO +125°C)

NOTES:

NOTES:

## **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:                                                                                           | Technical Publications Manager                                     | Total Pages Sent                                       |

|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------|

| RE:                                                                                           | Reader Response                                                    |                                                        |

| From                                                                                          | n: Name                                                            |                                                        |

|                                                                                               | Company                                                            |                                                        |

|                                                                                               |                                                                    |                                                        |

|                                                                                               |                                                                    |                                                        |

|                                                                                               | Telephone: ()                                                      | FAX: ()                                                |

| Application (optional):                                                                       |                                                                    |                                                        |

| Would you like a reply?YN                                                                     |                                                                    |                                                        |

| Devi                                                                                          | ce: DSTEMP                                                         | Literature Number: DS00000A                            |

| Questions:                                                                                    |                                                                    |                                                        |

| 1. What are the best features of this document?                                               |                                                                    |                                                        |

|                                                                                               |                                                                    |                                                        |

|                                                                                               |                                                                    |                                                        |

| <ol> <li>How does this document meet your hardware and software development needs?</li> </ol> |                                                                    |                                                        |

| _                                                                                             |                                                                    |                                                        |

| _                                                                                             |                                                                    |                                                        |

| 3. Do you find the organization of this document easy to follow? If not, why?                 |                                                                    | document easy to follow? If not, why?                  |

| _                                                                                             |                                                                    |                                                        |

| _                                                                                             |                                                                    |                                                        |

| 4. V                                                                                          | What additions to the document do y                                | you think would enhance the structure and subject?     |

| _                                                                                             |                                                                    |                                                        |

|                                                                                               |                                                                    |                                                        |

| 5. What deletions from the document could be made without affecting the overall usefulness?   |                                                                    | ouid be made without affecting the overall usefulness? |

| -                                                                                             |                                                                    |                                                        |

| 6. I                                                                                          | Is there any incorrect or misleading information (what and where)? |                                                        |

| 0. 1                                                                                          | s there any monteet of misleading i                                |                                                        |

| _                                                                                             |                                                                    |                                                        |

| -<br>7. H                                                                                     | low would you improve this docume                                  | ent?                                                   |

|                                                                                               |                                                                    |                                                        |

| _                                                                                             |                                                                    |                                                        |

| -                                                                                             |                                                                    |                                                        |