Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

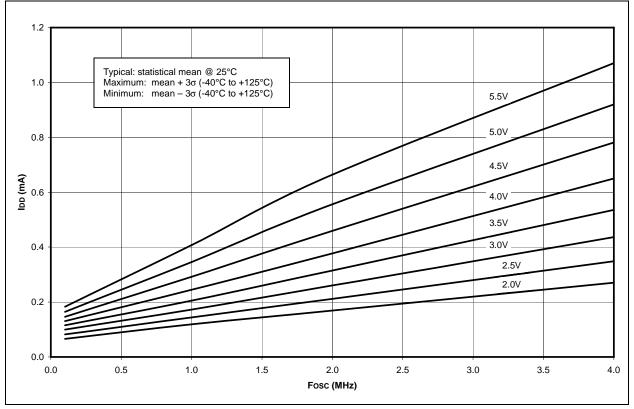

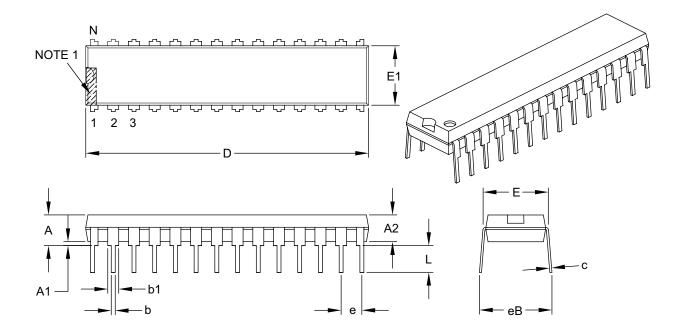

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf72-i-sp |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Linear Active Thermistor, Mindi, MiWi, MPASM, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2007, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona, Gresham, Oregon and Mountain View, California. The Company's quality system processes and procedures are for its PIC<sup>®</sup> MCUs and dsPIC DSCs, KEELOQ<sup>®</sup> code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# **PIC16F72**

## 28-Pin, 8-Bit CMOS FLASH MCU with A/D Converter

#### **Device Included:**

• PIC16F72

#### **High Performance RISC CPU:**

- · Only 35 single word instructions to learn

- All single cycle instructions except for program branches, which are two-cycle

- Operating speed: DC 20 MHz clock input DC - 200 ns instruction cycle

- 2K x 14 words of Program Memory, 128 x 8 bytes of Data Memory (RAM)

- Pinout compatible to PIC16C72/72A and PIC16F872

- Interrupt capability

- Eight-level deep hardware stack

- · Direct, Indirect and Relative Addressing modes

#### **Peripheral Features:**

- High Sink/Source Current: 25 mA

- Timer0: 8-bit timer/counter with 8-bit prescaler

- Timer1: 16-bit timer/counter with prescaler.

- can be incremented during SLEEP via external crystal/clock

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

- Capture, Compare, PWM (CCP) module

- Capture is 16-bit, max. resolution is 12.5 ns

- Compare is 16-bit, max. resolution is 200 ns

- PWM max. resolution is 10-bit

- 8-bit, 5-channel analog-to-digital converter

- Synchronous Serial Port (SSP) with SPI<sup>™</sup> (Master/Slave) and I<sup>2</sup>C<sup>™</sup> (Slave)

- Brown-out detection circuitry for Brown-out Reset (BOR)

#### **CMOS Technology:**

- · Low power, high speed CMOS FLASH technology

- · Fully static design

- Wide operating voltage range: 2.0V to 5.5V

- Industrial temperature range

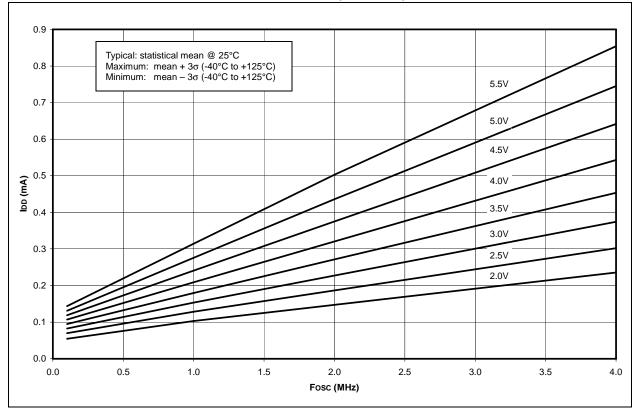

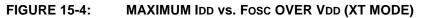

- Low power consumption:

- < 0.6 mA typical @ 3V, 4 MHz

- 20 μA typical @ 3V, 32 kHz

- <1 μA typical standby current

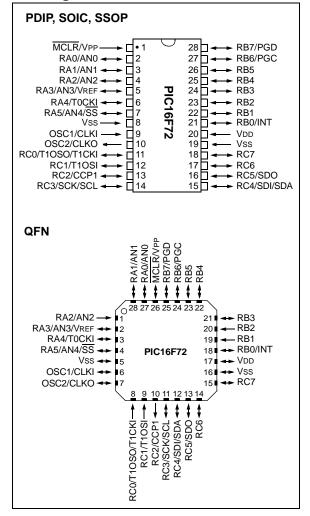

#### Pin Diagrams

#### **Special Microcontroller Features:**

- 1,000 erase/write cycle FLASH program memory typical

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- · Programmable code protection

- Power saving SLEEP mode

- Selectable oscillator options

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via 2 pins

- Processor read access to program memory

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral feature section.

TABLE 2-1:SPECIAL FUNCTION REGISTER SUMMARY

|                    | ·-      | 0. 20./    |                 |               |                |               | · · ·           |               | 1              | 1                    |                     |

|--------------------|---------|------------|-----------------|---------------|----------------|---------------|-----------------|---------------|----------------|----------------------|---------------------|

| Address            | Name    | Bit 7      | Bit 6           | Bit 5         | Bit 4          | Bit 3         | Bit 2           | Bit 1         | Bit 0          | Value on<br>POR, BOR | Details on<br>page: |

| Bank 0             |         |            |                 |               |                |               |                 |               |                |                      |                     |

| 00h <sup>(1)</sup> | INDF    | Addressi   | ng this loca    | tion uses cor | tents of FSR   | to address of | data memor      | / (not a phys | ical register) | 0000 0000            | 19                  |

| 01h                | TMR0    | Timer0 N   | lodule's Re     | gister        |                |               |                 |               |                | xxxx xxxx            | 27,13               |

| 02h <sup>(1)</sup> | PCL     | Program    | Counter's (     | PC) Least S   | ignificant By  | te            |                 |               |                | 0000 0000            | 18                  |

| 03h <sup>(1)</sup> | STATUS  | IRP        | RP1             | RP0           | TO             | PD            | Z               | DC            | С              | 0001 1xxx            | 12                  |

| 04h <sup>(1)</sup> | FSR     | Indirect [ | Data Memo       | ry Address P  | ointer         |               |                 |               |                | xxxx xxxx            | 19                  |

| 05h                | PORTA   | _          |                 | PORTA Dat     | a Latch whe    | n written: PC | ORTA pins w     | hen read      |                | 0x 0000              | 21                  |

| 06h                | PORTB   | PORTB I    | Data Latch      | when written  | : PORTB pir    | ns when read  | ł               |               |                | xxxx xxxx            | 23                  |

| 07h                | PORTC   | PORTC I    | Data Latch      | when written  | : PORTC pir    | ns when read  | b               |               |                | xxxx xxxx            | 25                  |

| 08h                | _       | Unimpler   | mented          |               |                |               |                 |               |                |                      | _                   |

| 09h                | —       | Unimpler   | Unimplemented   |               |                |               |                 |               |                | —                    | —                   |

|                    | PCLATH  |            | —               | —             | Write Buffer   | for the uppe  | er 5 bits of th | ne Program    | Counter        | 0 0000               | 18                  |

| 0Bh <sup>(1)</sup> | INTCON  | GIE        | PEIE            | TMR0IE        | INTE           | RBIE          | TMR0IF          | INTF          | RBIF           | 0000 000x            | 14                  |

| 0Ch                | PIR1    | —          | ADIF            | —             | —              | SSPIF         | CCP1IF          | TMR2IF        | TMR1IF         | -0 0000              | 16                  |

| 0Dh                | —       | Unimpler   | Unimplemented — |               |                |               |                 |               |                |                      | —                   |

| 0Eh                | TMR1L   | Holding F  | Register for    | the Least Si  | ignificant Byt | e of the 16-b | oit TMR1 Re     | gister        |                | XXXX XXXX            | 29                  |

| 0Fh                | TMR1H   | Holding I  | Register for    | the Most Sig  | gnificant Byte | e of the 16-b | it TMR1 Reg     | gister        | _              | xxxx xxxx            | 29                  |

| 10h                | T1CON   |            | —               | T1CKPS1       | T1CKPS0        | T1OSCEN       | T1SYNC          | TMR1CS        | TMR10N         | 00 0000              | 29                  |

| 11h                | TMR2    | Timer2 N   | Iodule's Re     | gister        |                |               |                 |               |                | 0000 0000            | 33                  |

| 12h                | T2CON   | —          | TOUTPS3         | TOUTPS2       | TOUTPS1        | TOUTPS0       | TMR2ON          | T2CKPS1       | T2CKPS0        | -000 0000            | 34                  |

| 13h                | SSPBUF  | Synchror   | nous Serial     | Port Receive  | e Buffer/Tran  | smit Registe  | er              | -             | _              | xxxx xxxx            | 43,48               |

| 14h                | SSPCON  | WCOL       | SSPOV           | SSPEN         | CKP            | SSPM3         | SSPM2           | SSPM1         | SSPM0          | 0000 0000            | 45                  |

| 15h                | CCPR1L  | Capture/   | Compare/P       | WM Registe    | r (LSB)        |               |                 |               |                | xxxx xxxx            | 38,39,41            |

| 16h                | CCPR1H  | Capture/   | Compare/P       | WM Registe    | r (MSB)        | -             | -               | -             | _              | xxxx xxxx            | 38,39,41            |

| 17h                | CCP1CON | —          | —               | CCP1X         | CCP1Y          | CCP1M3        | CCP1M2          | CCP1M1        | CCP1M0         | 00 0000              | 37                  |

| 18h-1Dh            | _       | Unimpler   | mented          |               |                |               |                 |               |                | _                    | _                   |

| 1Eh                | ADRES   | A/D Resu   | ult Register    |               |                |               |                 |               |                | XXXX XXXX            | 53                  |

| 1Fh                | ADCON0  | ADCS1      | ADCS0           | CHS2          | CHS1           | CHS0          | GO/DONE         | —             | ADON           | 0000 00-0            | 53                  |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.Note 1: These registers can be addressed from any bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: This bit always reads as a '1'.

| Address              | Name    | Bit 7         | Bit 6                                                                                      | Bit 5                     | Bit 4         | Bit 3        | Bit 2           | Bit 1  | Bit 0  | Value on POR, BOR | Details on page: |

|----------------------|---------|---------------|--------------------------------------------------------------------------------------------|---------------------------|---------------|--------------|-----------------|--------|--------|-------------------|------------------|

| Bank 1               |         |               |                                                                                            |                           |               |              |                 |        |        |                   |                  |

| 80h <sup>(1)</sup>   | INDF    | Addressi      | Addressing this location uses contents of FSR to address data memory (not a physical regis |                           |               |              |                 |        |        |                   | 19               |

| 81h                  | OPTION  | RBPU          | INTEDG                                                                                     | TOCS                      | TOSE          | PSA          | PS2             | PS1    | PS0    | 1111 1111         | 13               |

| 82h <sup>(1)</sup>   | PCL     | Program       | Counter's                                                                                  | PC) Least S               | ignificant By | te           | -               | -      |        | 0000 0000         | 18               |

| 83h <b>(1)</b>       | STATUS  | IRP           | RP1                                                                                        | RP0                       | ТО            | PD           | Z               | DC     | С      | 0001 1xxx         | 12               |

| 84h <b>(1)</b>       | FSR     | Indirect [    | Data Memo                                                                                  | ry Address F              | Pointer       |              |                 |        |        | xxxx xxxx         | 19               |

| 85h                  | TRISA   |               | _                                                                                          | PORTA Dat                 | a Direction F | Register     |                 |        |        | 11 1111           | 21               |

| 86h                  | TRISB   | PORTB         | Data Direct                                                                                | on Register               |               |              |                 |        |        | 1111 1111         | 23               |

| 87h                  | TRISC   | PORTC         | Data Direct                                                                                | ion Register              |               |              |                 |        |        | 1111 1111         | 25               |

| 88h                  | _       | Unimple       | mented                                                                                     |                           |               |              |                 |        |        | _                 | _                |

| 89h                  |         | Unimple       | mented                                                                                     |                           |               |              |                 |        |        | _                 | _                |

| 8Ah <sup>(1,2)</sup> | PCLATH  |               | —                                                                                          | _                         | Write Buffer  | for the uppe | er 5 bits of th | ne PC  |        | 0 0000            | 18               |

| 8Bh <sup>(1)</sup>   | INTCON  | GIE           | PEIE                                                                                       | TMR0IE                    | INTE          | RBIE         | TMR0IF          | INTF   | RBIF   | 0000 000x         | 14               |

| 8Ch                  | PIE1    |               | ADIE                                                                                       | _                         | —             | SSPIE        | CCP1IE          | TMR2IE | TMR1IE | -0 0000           | 15               |

| 8Dh                  | _       | Unimple       | Unimplemented                                                                              |                           |               |              |                 |        |        |                   | —                |

| 8Eh                  | PCON    |               | _                                                                                          | _                         | —             | _            | _               | POR    | BOR    | qq                | 17               |

| 8Fh                  |         | Unimple       | Unimplemented                                                                              |                           |               |              |                 |        |        |                   | _                |

| 90h                  |         | Unimple       | mented                                                                                     |                           |               |              |                 |        |        | _                 | _                |

| 91h                  |         | Unimple       | mented                                                                                     |                           |               |              |                 |        |        | _                 | _                |

| 92h                  | PR2     | Timer2 F      | Period Regis                                                                               | ster                      |               |              |                 |        |        | 1111 1111         | 41               |

| 93h                  | SSPADD  | Synchro       | nous Serial                                                                                | Port (I <sup>2</sup> C mo | ode) Address  | Register     | -               | -      |        | 0000 0000         | 43,48            |

| 94h                  | SSPSTAT | SMP           | CKE                                                                                        | D/A                       | Р             | S            | R/W             | UA     | BF     | 0000 0000         | 44               |

| 95h                  |         | Unimple       | mented                                                                                     |                           |               |              |                 |        |        | _                 | —                |

| 96h                  | _       | Unimple       | mented                                                                                     |                           |               |              |                 |        |        | _                 | _                |

| 97h                  |         | Unimple       | mented                                                                                     |                           |               |              |                 |        |        | _                 | —                |

| 98h                  | _       | Unimple       | Unimplemented                                                                              |                           |               |              |                 |        |        | _                 | _                |

| 99h                  | _       | Unimple       | mented                                                                                     |                           |               |              |                 |        |        | _                 | _                |

| 9Ah                  | _       | Unimple       | mented                                                                                     |                           |               |              |                 |        |        | _                 | _                |

| 9Bh                  | _       | Unimple       | Unimplemented                                                                              |                           |               |              |                 |        |        | _                 | _                |

| 9Ch                  |         | Unimplemented |                                                                                            |                           |               |              |                 |        |        | _                 | _                |

| 9Dh                  |         | Unimple       | mented                                                                                     |                           |               |              |                 |        |        | _                 | _                |

| 9Eh                  | _       | Unimple       | mented                                                                                     |                           |               |              |                 |        |        |                   |                  |

| 9Fh                  | ADCON1  |               | _                                                                                          | _                         | _             | _            | PCFG2           | PCFG1  | PCFG0  | 000               | 54               |

#### TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

$\label{eq:Legend: Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. \\ Shaded locations are unimplemented, read as '0'.$

**Note 1:** These registers can be addressed from any bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

**3:** This bit always reads as a '1'.

| IADLE J-J. |       |                       |                                                                                                                     |  |  |  |

|------------|-------|-----------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name       | Bit#  | Buffer                | Function                                                                                                            |  |  |  |

| RB0/INT    | bit 0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                          |  |  |  |

| RB1        | bit 1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |  |  |  |

| RB2        | bit 2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |  |  |  |

| RB3        | bit 3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |  |  |  |

| RB4        | bit 4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                           |  |  |  |

| RB5        | bit 5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                           |  |  |  |

| RB6        | bit 6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock. |  |  |  |

| RB7        | bit 7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data.  |  |  |  |

#### TABLE 3-3:PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

| Address   | Name   | Bit 7 | Bit 6      | Bit 5    | Bit 4 | Bit 3     | Bit 2     | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>RESETS |

|-----------|--------|-------|------------|----------|-------|-----------|-----------|-------|-------|----------------------|---------------------------------|

| 06h, 106h | PORTB  | RB7   | RB6        | RB5      | RB4   | RB3       | RB2       | RB1   | RB0   | xxxx xxxx            | uuuu uuuu                       |

| 86h, 186h | TRISB  | PORTB | Data Direc | tion Reg |       | 1111 1111 | 1111 1111 |       |       |                      |                                 |

| 81h, 181h | OPTION | RBPU  | INTEDG     | TOCS     | TOSE  | PSA       | PS2       | PS1   | PS0   | 1111 1111            | 1111 1111                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

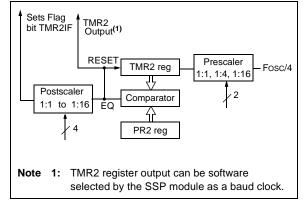

#### 6.0 TIMER2 MODULE

The Timer2 module timer has the following features:

- 8-bit timer (TMR2 register)

- 8-bit period register (PR2)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2 match of PR2

- SSP module optional use of TMR2 output to generate clock shift

Timer2 has a control register, shown in Register 6-1. Timer2 can be shut-off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Figure 6-1 is a simplified block diagram of the Timer2 module.

Additional information on timer modules is available in the PIC<sup>™</sup> Mid-Range MCU Reference Manual, (DS33023).

#### 6.1 Timer2 Operation

Timer2 can be used as the PWM time-base for PWM mode of the CCP module.

The TMR2 register is readable and writable, and is cleared on any device RESET.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

#### 6.2 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- A write to the TMR2 register

- A write to the T2CON register

- Any device RESET (Power-on Reset, MCLR , WDT Reset, or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

#### 6.3 Timer2 Interrupt

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon RESET.

#### 6.4 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module, which optionally uses it to generate a shift clock.

#### FIGURE 6-1: TIMER2 BLOCK DIAGRAM

# **PIC16F72**

| REGISTER 6-1: | T2CON:                                               | TIMER2 CO    | ONTROL R    | EGISTER (A   | ADDRESS    | 12h)      |              |         |  |

|---------------|------------------------------------------------------|--------------|-------------|--------------|------------|-----------|--------------|---------|--|

|               | U-0                                                  | R/W-0        | R/W-0       | R/W-0        | R/W-0      | R/W-0     | R/W-0        | R/W-0   |  |

|               | _                                                    | TOUTPS3      | TOUTPS2     | TOUTPS1      | TOUTPS0    | TMR2ON    | T2CKPS1      | T2CKPS0 |  |

|               | bit 7                                                |              |             |              |            |           |              | bit 0   |  |

| bit 7         | Unimple                                              | nented: Rea  | ad as '0'   |              |            |           |              |         |  |

| bit 6-3       | TOUTPS3:TOUTPS0: Timer2 Output Postscale Select bits |              |             |              |            |           |              |         |  |

|               |                                                      | 1 Postscale  |             |              |            |           |              |         |  |

|               | 0001 = 1:                                            | 2 Postscale  |             |              |            |           |              |         |  |

|               | 0010 = 1:                                            | 3 Postscale  |             |              |            |           |              |         |  |

|               | •                                                    |              |             |              |            |           |              |         |  |

|               | •                                                    |              |             |              |            |           |              |         |  |

|               | 1111 <b>= 1</b> :                                    | 16 Postscale | 9           |              |            |           |              |         |  |

| bit 2         | TMR2ON                                               | : Timer2 On  | bit         |              |            |           |              |         |  |

|               | 1 = Timei                                            | 2 is on      |             |              |            |           |              |         |  |

|               | 0 = Time                                             | 2 is off     |             |              |            |           |              |         |  |

| bit 1-0       | T2CKPS                                               | I:T2CKPS0:   | Timer2 Cloc | k Prescale S | elect bits |           |              |         |  |

|               | 00 = Pre:                                            | scaler is 1  |             |              |            |           |              |         |  |

|               |                                                      | scaler is 4  |             |              |            |           |              |         |  |

|               | 1x = Pres                                            | scaler is 16 |             |              |            |           |              |         |  |

|               |                                                      |              |             |              |            |           |              |         |  |

|               | Legend:                                              |              |             |              |            |           |              |         |  |

|               | R = Read                                             | able bit     | W = V       | Vritable bit | U = Unim   | plemented | bit, read as | '0'     |  |

| TABLE 6-1: | <b>REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER</b> |

|------------|------------------------------------------------------------|

|            |                                                            |

- n = Value at POR

| Address                | Name                           | Bit 7 | Bit 6                  | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>POR, |      | Valu<br>all c<br>RES | other |

|------------------------|--------------------------------|-------|------------------------|---------|---------|---------|--------|---------|---------|---------------|------|----------------------|-------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON                         | GIE   | PEIE                   | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000          | 000x | 0000                 | 000u  |

| 0Ch                    | PIR1                           |       | ADIF                   | —       | _       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | - 0           | 0000 | 0000                 | 0000  |

| 8Ch                    | PIE1                           | _     | ADIE                   | —       | _       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | - 0           | 0000 | 0000                 | 0000  |

| 11h                    | TMR2                           | Timer | Timer2 Module Register |         |         |         |        |         |         |               | 0000 | 0000                 | 0000  |

| 12h                    | T2CON                          | _     | TOUTPS3                | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000          | 0000 | -000                 | 0000  |

| 92h                    | 92h PR2 Timer2 Period Register |       |                        |         |         |         |        |         |         | 1111          | 1111 | 1111                 | 1111  |

'1' = Bit is set

'0' = Bit is cleared

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

x = Bit is unknown

#### 9.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

#### 9.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

An overview of I<sup>2</sup>C operations and additional information on the SSP module can be found in the PIC<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

Refer to Application Note AN578, "Use of the SSP Module in the  $I^2C$  Multi-Master Environment."

#### 9.2 SPI Mode

This section contains register definitions and operational characteristics of the SPI module.

SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS) RA5/AN4/SS

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (IDLE state of SCK)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

#### 11.0 SPECIAL FEATURES OF THE CPU

These devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving Operating modes and offer code protection:

- Oscillator Selection

- RESET

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code Protection

- ID Locations

- In-Circuit Serial Programming

These devices have a Watchdog Timer, which can be enabled or disabled using a configuration bit. It runs off its own RC oscillator for added reliability.

There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. It is designed to keep the part in RESET while the power supply stabilizes, and is enabled or disabled using a configuration bit. With these two timers on-chip, most applications need no external RESET circuitry. SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer Wake-up, or through an interrupt.

Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. Configuration bits are used to select the desired oscillator mode.

Additional information on special features is available in the PIC<sup>™</sup> Mid-Range Reference Manual (DS33023).

#### 11.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space, which can be accessed only during programming.

#### TABLE 11-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS

| Register | Power-on Reset,<br>Brown-out Reset | MCLR Reset,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|----------|------------------------------------|--------------------------|---------------------------------|

| W        | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| INDF     | N/A                                | N/A                      | N/A                             |

| TMR0     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PCL      | 0000h                              | 0000h                    | PC + 1 <sup>(2)</sup>           |

| STATUS   | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <b>(3)</b>            |

| FSR      | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PORTA    | 0x 0000                            | Ou 0000                  | uu uuuu                         |

| PORTB    | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PORTC    | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PCLATH   | 0 0000                             | 0 0000                   | u uuuu                          |

| INTCON   | x000 0000 x                        | 0000 000u                | uuuu uuuu <b>(1)</b>            |

| PIR1     | -0 0000                            | -0 0000                  | -u uuuu <b>(1)</b>              |

| TMR1L    | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| TMR1H    | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| T1CON    | 00 0000                            | uu uuuu                  | uu uuuu                         |

| TMR2     | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| T2CON    | -000 0000                          | -000 0000                | -uuu uuuu                       |

| SSPBUF   | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| SSPCON   | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| CCPR1L   | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| CCPR1H   | xxxx xxxx                          | uuuu uuuu                | սսսս սսսս                       |

| CCP1CON  | 00 0000                            | 00 0000                  | uu uuuu                         |

| ADRES    | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON0   | 0000 00-0                          | 0000 00-0                | uuuu uu-u                       |

| OPTION   | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISA    | 11 1111                            | 11 1111                  | uu uuuu                         |

| TRISB    | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISC    | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| PIE1     | -0 0000                            | -0 0000                  | -u uuuu                         |

| PCON     | dd                                 | uu                       | uu                              |

| PR2      | 1111 1111                          | 1111 1111                | 1111 1111                       |

| SSPADD   | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| SSPSTAT  | 00 0000                            | 00 0000                  | uu uuuu                         |

| ADCON1   | 000                                | 000                      | uuu                             |

| PMDATL   | 0 0000                             | 0 0000                   | u uuuu                          |

| PMADRL   | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PMDATH   | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PMADRH   | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PMCON1   | 1 0                                | 1 0                      | 1u                              |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear.

**Note 1:** One or more bits in INTCON, PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**3:** See Table 11-5 for RESET value for specific condition.

| Mnemonic,<br>Operands |      | Description                  | Cycles        |       | 14-Bit | Opcod | е    | Status   | Note  |

|-----------------------|------|------------------------------|---------------|-------|--------|-------|------|----------|-------|

|                       |      | Description                  | Cycles        | MSb   |        |       | LSb  | Affected | Note  |

|                       |      | BYTE-ORIENTED FILE           | REGISTER OPEI | RATIC | ONS    |       |      |          |       |

| ADDWF                 | f, d | Add W and f                  | 1             | 00    | 0111   | dfff  | ffff | C,DC,Z   | 1,2   |

| ANDWF                 | f, d | AND W with f                 | 1             | 00    | 0101   | dfff  | ffff | Z        | 1,2   |

| CLRF                  | f    | Clear f                      | 1             | 00    | 0001   | lfff  | ffff | Z        | 2     |

| CLRW                  | -    | Clear W                      | 1             | 00    | 0001   | 0xxx  | xxxx | Z        |       |

| COMF                  | f, d | Complement f                 | 1             | 00    | 1001   | dfff  | ffff | Z        | 1,2   |

| DECF                  | f, d | Decrement f                  | 1             | 00    | 0011   | dfff  | ffff | Z        | 1,2   |

| DECFSZ                | f, d | Decrement f, Skip if 0       | 1(2)          | 00    | 1011   | dfff  | ffff |          | 1,2,3 |

| INCF                  | f, d | Increment f                  | 1             | 00    | 1010   | dfff  | ffff | Z        | 1,2   |

| INCFSZ                | f, d | Increment f, Skip if 0       | 1(2)          | 00    | 1111   | dfff  | ffff |          | 1,2,3 |

| IORWF                 | f, d | Inclusive OR W with f        | 1             | 00    | 0100   | dfff  | ffff | Z        | 1,2   |

| MOVF                  | f, d | Move f                       | 1             | 00    | 1000   | dfff  | ffff | Z        | 1,2   |

| MOVWF                 | f    | Move W to f                  | 1             | 00    | 0000   | lfff  |      |          | -     |

| NOP                   | -    | No Operation                 | 1             | 00    | 0000   | 0xx0  | 0000 |          |       |

| RLF                   | f, d | Rotate Left f through Carry  | 1             | 00    | 1101   | dfff  | ffff | С        | 1,2   |

| RRF                   | f, d | Rotate Right f through Carry | 1             | 00    | 1100   | dfff  | ffff | С        | 1,2   |

| SUBWF                 | f, d | Subtract W from f            | 1             | 00    | 0010   | dfff  | ffff | C,DC,Z   | 1,2   |

| SWAPF                 | f, d | Swap nibbles in f            | 1             | 00    | 1110   | dfff  | ffff |          | 1,2   |

| XORWF                 | f, d | Exclusive OR W with f        | 1             | 00    | 0110   |       | ffff | z        | 1,2   |

|                       | ,    | BIT-ORIENTED FILE            |               |       | NS     |       |      |          |       |

| BCF                   | f, b | Bit Clear f                  | 1             | 01    | 00bb   | bfff  | ffff |          | 1,2   |

| BSF                   | f, b | Bit Set f                    | 1             | 01    | 01bb   | bfff  | ffff |          | 1,2   |

| BTFSC                 | f, b | Bit Test f, Skip if Clear    | 1 (2)         | 01    |        | bfff  |      |          | 3     |

| BTFSS                 | f, b | Bit Test f, Skip if Set      | 1 (2)         | 01    | 11bb   | bfff  | ffff |          | 3     |

|                       | ,    | LITERAL AND CO               |               | ONS   |        |       |      |          |       |

| ADDLW                 | k    | Add literal and W            | 1             | 11    | 111x   | kkkk  | kkkk | C,DC,Z   |       |

| ANDLW                 | k    | AND literal with W           | 1             | 11    | 1001   | kkkk  | kkkk | Z        |       |

| CALL                  | k    | Call subroutine              | 2             | 10    | 0kkk   | kkkk  | kkkk |          |       |

| CLRWDT                | -    | Clear Watchdog Timer         | 1             | 00    | 0000   | 0110  | 0100 | TO,PD    |       |

| GOTO                  | k    | Go to address                | 2             | 10    | 1kkk   | kkkk  | kkkk |          |       |

| IORLW                 | k    | Inclusive OR literal with W  | 1             | 11    | 1000   | kkkk  | kkkk | Z        |       |

| MOVLW                 | k    | Move literal to W            | 1             | 11    | 00xx   | kkkk  | kkkk |          |       |

| RETFIE                | -    | Return from interrupt        | 2             | 00    | 0000   | 0000  |      |          |       |

| RETLW                 | k    | Return with literal in W     | 2             | 11    |        | kkkk  |      |          |       |

| RETURN                | -    | Return from Subroutine       | 2             | 00    | 0000   | 0000  | 1000 |          |       |

| SLEEP                 | -    | Go into Standby mode         | 1             | 00    | 0000   | 0110  |      | TO,PD    |       |

| SUBLW                 | k    | Subtract W from literal      | 1             | 11    |        | kkkk  |      | C,DC,Z   |       |

| XORLW                 | k    | Exclusive OR literal with W  | 1             | 11    |        | kkkk  |      | Z        |       |

|                       |      |                              |               |       | 7070   |       |      | 1 -      |       |

#### TABLE 12-2: PIC16F72 INSTRUCTION SET

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

Note: Additional information on the mid-range instruction set is available in the PIC<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

| RETFIE           | Return from Interrupt      | RLF              | Rotate Left f through Carry                                                                                                                                                                                                         |

|------------------|----------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETFIE             | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                                            |

| Operands:        | None                       | Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                   |

| Operation:       | $TOS \rightarrow PC$ ,     |                  | d ∈ [0,1]                                                                                                                                                                                                                           |

|                  | $1 \rightarrow \text{GIE}$ | Operation:       | See description below                                                                                                                                                                                                               |

| Status Affected: | None                       | Status Affected: | С                                                                                                                                                                                                                                   |

|                  |                            | Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag. If 'd' = '0', the<br>result is placed in the W register.<br>If 'd' = '1', the result is stored<br>back in register 'f'.<br>-C Register f |

| RETLW            | Return with Literal in W                                                                                                                                                            | RRF              | Rotate Right f through Carry                                                                                                                                                                                                      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            | Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                          |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   | Operands:        | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                                                                                          |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        | Operation:       | See description below                                                                                                                                                                                                             |

| Status Affected: | None                                                                                                                                                                                | Status Affected: | С                                                                                                                                                                                                                                 |

| Description:     | The W register is loaded with the<br>eight-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction. | Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' = '0', the<br>result is placed in the W register.<br>If 'd' = '1', the result is placed back<br>in register 'f'.<br>Register f |

| RETURN           | Return from Subroutine                                                                                     | SLEEP            |                                                                                                                                                                                               |  |  |

|------------------|------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] RETURN                                                                                             | Syntax:          | [label] SLEEP                                                                                                                                                                                 |  |  |

| Operands:        | None                                                                                                       | Operands:        | None                                                                                                                                                                                          |  |  |

| Operation:       | $TOS\toPC$                                                                                                 | Operation:       | 00h $\rightarrow$ WDT,<br>0 $\rightarrow$ WDT prescaler,<br>1 $\rightarrow$ TO,                                                                                                               |  |  |

| Status Affected: | None                                                                                                       |                  |                                                                                                                                                                                               |  |  |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program |                  | $0 \rightarrow PD$                                                                                                                                                                            |  |  |

|                  |                                                                                                            | Status Affected: | TO, PD                                                                                                                                                                                        |  |  |

|                  | counter. This is a two-cycle instruction.                                                                  | Description:     | The power-down status bit, $\overline{PD}$ is<br>cleared. Time-out status bit, $\overline{TO}$<br>is set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into SLEEP |  |  |

mode with the oscillator stopped.

| SUBLW            | Subtract W from Literal                                                                                                      |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                     |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                            |  |  |  |  |

| Operation:       | $k \text{ - (W)} \rightarrow (W)$                                                                                            |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                     |  |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register. |  |  |  |  |

| XORLW            | Exclusive OR Literal with W                                                                                                |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] XORLW k                                                                                                            |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                          |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                              |  |  |  |  |

| Status Affected: | Z                                                                                                                          |  |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed in<br>the W register. |  |  |  |  |

| SUBWF            | Subtract W from f                                                                                                                                                                         |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] SUBWF f,d                                                                                                                                                                         |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                |  |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                     |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                  |  |  |  |  |

| Description:     | Subtract (2's complement method)<br>W register from register 'f'. If<br>'d' = '0', the result is stored in the W<br>register. If 'd' = '1', the result is<br>stored back in register 'f'. |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                         |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] XORWF f,d                                                                                                                                                             |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                            |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                     |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                             |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' = '0', the result is stored in the W register. If 'd' = '1', the result is stored back in register 'f'. |  |  |  |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                          |

| Status Affected: | None                                                                                                                                                             |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' = '0', the result is placed in W register. If 'd' = '1', the result is placed in register 'f'. |

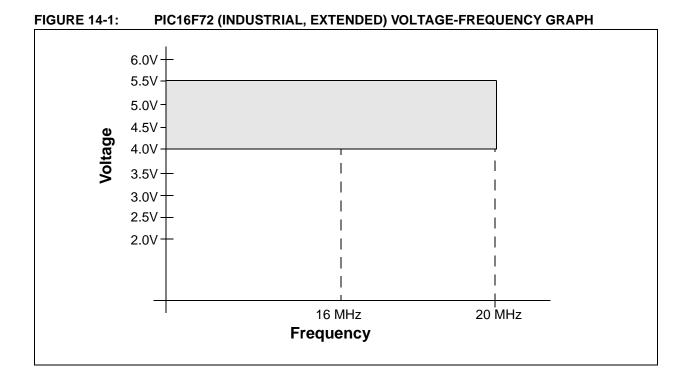

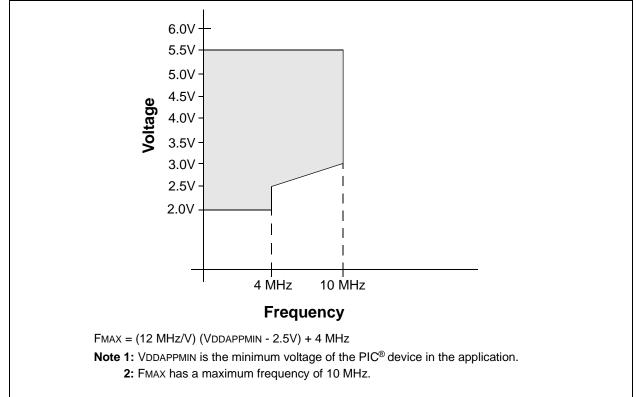

### 14.0 ELECTRICAL CHARACTERISTICS

#### Absolute Maximum Ratings †

| Ambient temperature under bias55 to +1                                                                                                                                              | 25°C   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Storage temperature                                                                                                                                                                 | 50°C   |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)0.3V to (VDD + 0                                                                                                  | 0.3V)  |

| Voltage on VDD with respect to Vss                                                                                                                                                  | +6.5V  |

| Voltage on MCLR with respect to Vss (Note 2)0 to +1                                                                                                                                 |        |

| Voltage on RA4 with respect to Vss0 to -                                                                                                                                            | +12V   |

| Total power dissipation (Note 1)                                                                                                                                                    | 1.0W   |

| Maximum current out of Vss pin                                                                                                                                                      | 0 mA   |

| Maximum current into VDD pin                                                                                                                                                        | 0 mA   |

| Input clamp current, Iik (VI < 0 or VI > VDD)                                                                                                                                       | 0 mA   |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                                                                                                      | 0 mA   |

| Maximum output current sunk by any I/O pin2                                                                                                                                         | 5 mA   |

| Maximum output current sourced by any I/O pin                                                                                                                                       | 5 mA   |

| Maximum current sunk by PORTA, PORTB                                                                                                                                                | 0 mA   |

| Maximum current sourced by PORTA, PORTB                                                                                                                                             | 0 mA   |

| Maximum current sunk by PORTC                                                                                                                                                       | 0 mA   |

| Maximum current sourced by PORTC                                                                                                                                                    | 0 mA   |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD - VOH) x IOH} + $\sum$ (VOI x                                             | x Iol) |

| 2: Voltage spikes at the MCLR pin may cause unpredictable results. A series resistor of greater than should be used to pull MCLR to VDD, rather than tying the pin directly to VDD. | 1 kΩ   |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# PIC16F72

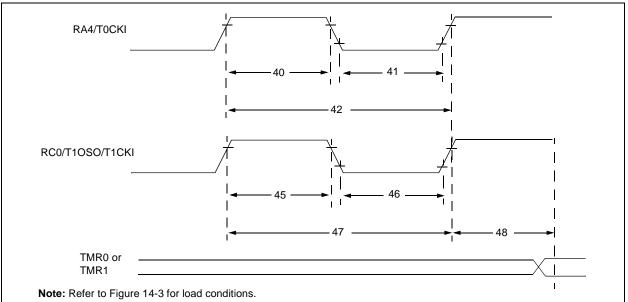

| <b>TABLE 14-4</b> : | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|---------------------|-----------------------------------------------|

|                     |                                               |

| Param<br>No. | Symbol    |                                            | Characteristic     |                       | Min                                       | Тур† | Max    | Units | Conditions                         |

|--------------|-----------|--------------------------------------------|--------------------|-----------------------|-------------------------------------------|------|--------|-------|------------------------------------|

| 40*          | Tt0H      | T0CKI High Pulse                           | Width              | No Prescaler          | 0.5 TCY + 20                              | —    | _      | ns    | Must also meet                     |

|              |           |                                            |                    | With Prescaler        | 10                                        | —    | _      | ns    | parameter 42                       |

| 41*          | Tt0L      | T0CKI Low Pulse                            | Width              | No Prescaler          | 0.5 TCY + 20                              | _    | _      | ns    | Must also meet                     |

|              |           |                                            |                    | With Prescaler        | 10                                        | —    |        | ns    | parameter 42                       |

| 42*          | Tt0P      | T0CKI Period                               |                    | No Prescaler          | Tcy + 40                                  | —    |        | ns    |                                    |

|              |           |                                            |                    | With Prescaler        | Greater of:<br>20 or <u>Tcy + 40</u><br>N | _    | _      | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Tt1H      | T1CKI High Time                            | Synchronous, Pr    | escaler = 1           | 0.5 TCY + 20                              | —    | _      | ns    | Must also meet                     |

|              |           |                                            | Synchronous,       | Standard(F)           | 15                                        | —    | _      | ns    | parameter 47                       |

|              |           |                                            | Prescaler = 2,4,8  | Extended(LF)          | 25                                        | —    | _      | ns    |                                    |

|              |           |                                            | Asynchronous       | Standard(F)           | 30                                        | —    |        | ns    |                                    |

|              |           |                                            |                    | Extended(LF)          | 50                                        | —    |        | ns    |                                    |

| 46*          | Tt1L      | T1CKI Low Time                             | Synchronous, Pr    | escaler = 1           | 0.5 TCY + 20                              | —    | _      | ns    | Must also meet                     |

|              |           |                                            | Synchronous,       | Standard(F)           | 15                                        |      | _      | ns    | parameter 47                       |

|              |           |                                            | Prescaler = 2,4,8  | Extended(LF)          | 25                                        |      | _      | ns    |                                    |

|              |           |                                            | Asynchronous       | Standard(F)           | 30                                        |      | _      | ns    |                                    |

|              |           |                                            |                    | Extended(LF)          | 50                                        | _    | -      | ns    |                                    |

| 47*          | Tt1P      | T1CKI Input<br>Period                      | Synchronous        | Standard( <b>F</b> )  | Greater of:<br>30 or <u>Tcy + 40</u><br>N | _    | _      | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                            |                    | Extended( <b>LF</b> ) | Greater of:<br>50 or <u>Tcy + 40</u><br>N |      |        |       | N = prescale value<br>(1, 2, 4, 8) |