Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | ·                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 28-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf72-i-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | Device Overview                              |    |

|-------|----------------------------------------------|----|

| 2.0   | Memory Organization                          | 7  |

| 3.0   | I/O Ports                                    |    |

| 4.0   | Reading Program Memory                       | 27 |

| 5.0   | Timer0 Module                                |    |

| 6.0   | Timer1 Module                                | 31 |

| 7.0   | Timer2 Module                                | 35 |

| 8.0   | Capture/Compare/PWM (CCP) Module             | 37 |

| 9.0   | Synchronous Serial Port (SSP) Module         |    |

| 10.0  | Analog-to-Digital Converter (A/D) Module     |    |

| 11.0  | Special Features of the CPU                  | 59 |

| 12.0  | Instruction Set Summary                      |    |

| 13.0  | Development Support                          | 81 |

| 14.0  | Electrical Characteristics                   | 87 |

| 15.0  | DC and AC Characteristics Graphs and Tables1 | 07 |

| 16.0  | Package Marking Information1                 | 17 |

| Appe  | ndix A: Revision History1                    | 23 |

|       | ndix B: Conversion Considerations1           |    |

| Index |                                              | 25 |

| On-Li | ne Support1                                  | 31 |

|       | er Response 1                                |    |

| Produ | ict Identification System 1                  | 33 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral feature section.

TABLE 2-1:SPECIAL FUNCTION REGISTER SUMMARY

|                    | ·-      |                                    |                                                                                                        |              |                |               | · · ·           |            | 1         | 1                    |                     |  |  |

|--------------------|---------|------------------------------------|--------------------------------------------------------------------------------------------------------|--------------|----------------|---------------|-----------------|------------|-----------|----------------------|---------------------|--|--|

| Address            | Name    | Bit 7                              | Bit 6                                                                                                  | Bit 5        | Bit 4          | Bit 3         | Bit 2           | Bit 1      | Bit 0     | Value on<br>POR, BOR | Details on<br>page: |  |  |

| Bank 0             |         |                                    |                                                                                                        |              |                |               |                 |            |           |                      |                     |  |  |

| 00h <sup>(1)</sup> | INDF    | Addressi                           | dressing this location uses contents of FSR to address data memory (not a physical register) 0000 0000 |              |                |               |                 |            |           |                      |                     |  |  |

| 01h                | TMR0    | Timer0 N                           | lodule's Re                                                                                            | gister       |                |               |                 |            |           | xxxx xxxx            | 27,13               |  |  |

| 02h <sup>(1)</sup> | PCL     | Program                            | Counter's (                                                                                            | PC) Least S  | ignificant By  | te            |                 |            |           | 0000 0000            | 18                  |  |  |

| 03h <sup>(1)</sup> | STATUS  | IRP                                | RP1                                                                                                    | RP0          | TO             | PD            | Z               | DC         | С         | 0001 1xxx            | 12                  |  |  |

| 04h <sup>(1)</sup> | FSR     | Indirect [                         | Data Memo                                                                                              | ry Address P | ointer         |               |                 |            |           | xxxx xxxx            | 19                  |  |  |

| 05h                | PORTA   | _                                  |                                                                                                        | PORTA Dat    | a Latch whe    | n written: PC | ORTA pins w     | hen read   |           | 0x 0000              | 21                  |  |  |

| 06h                | PORTB   | PORTB I                            | Data Latch                                                                                             | when written | : PORTB pir    | ns when read  | ł               |            |           | xxxx xxxx            | 23                  |  |  |

| 07h                | PORTC   | PORTC I                            | Data Latch                                                                                             | when written | : PORTC pir    | ns when read  | b               |            |           | xxxx xxxx            | 25                  |  |  |

| 08h                | _       | Unimpler                           | mented                                                                                                 |              |                |               |                 |            |           |                      | _                   |  |  |

| 09h                | —       | Unimpler                           | Jnimplemented                                                                                          |              |                |               |                 |            |           |                      | —                   |  |  |

|                    | PCLATH  |                                    | —                                                                                                      | —            | Write Buffer   | for the uppe  | er 5 bits of th | ne Program | Counter   | 0 0000               | 18                  |  |  |

| 0Bh <sup>(1)</sup> | INTCON  | GIE                                | PEIE                                                                                                   | TMR0IE       | INTE           | RBIE          | TMR0IF          | INTF       | RBIF      | 0000 000x            | 14                  |  |  |

| 0Ch                | PIR1    | —                                  | ADIF                                                                                                   | —            | —              | SSPIF         | CCP1IF          | TMR2IF     | TMR1IF    | -0 0000              | 16                  |  |  |

| 0Dh                | —       | Unimpler                           | mented                                                                                                 |              |                |               |                 |            |           | —                    | —                   |  |  |

| 0Eh                | TMR1L   | Holding F                          | Register for                                                                                           | the Least Si | ignificant Byt | e of the 16-b | oit TMR1 Re     | gister     |           | XXXX XXXX            | 29                  |  |  |

| 0Fh                | TMR1H   | Holding I                          | Register for                                                                                           | the Most Sig | gnificant Byte | e of the 16-b | it TMR1 Reg     | gister     | _         | xxxx xxxx            | 29                  |  |  |

| 10h                | T1CON   |                                    | —                                                                                                      | T1CKPS1      | T1CKPS0        | T1OSCEN       | T1SYNC          | TMR1CS     | TMR10N    | 00 0000              | 29                  |  |  |

| 11h                | TMR2    | Timer2 N                           | Iodule's Re                                                                                            | gister       |                |               |                 |            |           | 0000 0000            | 33                  |  |  |

| 12h                | T2CON   | —                                  | TOUTPS3                                                                                                | TOUTPS2      | TOUTPS1        | TOUTPS0       | TMR2ON          | T2CKPS1    | T2CKPS0   | -000 0000            | 34                  |  |  |

| 13h                | SSPBUF  | Synchror                           | nous Serial                                                                                            | Port Receive | e Buffer/Tran  | smit Registe  | er              | -          | _         | xxxx xxxx            | 43,48               |  |  |

| 14h                | SSPCON  | WCOL                               | SSPOV                                                                                                  | SSPEN        | CKP            | SSPM3         | SSPM2           | SSPM1      | SSPM0     | 0000 0000            | 45                  |  |  |

| 15h                | CCPR1L  | Capture/Compare/PWM Register (LSB) |                                                                                                        |              |                |               |                 |            |           | xxxx xxxx            | 38,39,41            |  |  |

| 16h                | CCPR1H  | Capture/Compare/PWM Register (MSB) |                                                                                                        |              |                |               |                 |            | xxxx xxxx | 38,39,41             |                     |  |  |

| 17h                | CCP1CON | —                                  | —                                                                                                      | CCP1X        | CCP1Y          | CCP1M3        | CCP1M2          | CCP1M1     | CCP1M0    | 00 0000              | 37                  |  |  |

| 18h-1Dh            | _       | Unimpler                           | mented                                                                                                 | _            | _              |               |                 |            |           |                      |                     |  |  |

| 1Eh                | ADRES   | A/D Resu                           | ult Register                                                                                           |              |                |               |                 |            |           | XXXX XXXX            | 53                  |  |  |

| 1Fh                | ADCON0  | ADCS1                              | ADCS0                                                                                                  | CHS2         | CHS1           | CHS0          | GO/DONE         | —          | ADON      | 0000 00-0            | 53                  |  |  |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.Note 1: These registers can be addressed from any bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: This bit always reads as a '1'.

#### 2.2.2.2 **OPTION Register**

The OPTION register is a readable and writable register that contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT Interrupt, TMR0, and the weak pull-ups on PORTB.

| Note: | To achieve a 1:1 prescaler assignment for  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|

|       | the TMR0 register, assign the prescaler to |  |  |  |  |  |  |  |

|       | the Watchdog Timer.                        |  |  |  |  |  |  |  |

| REGISTER 2-2: | ER 2-2: OPTION REGISTER (ADDRESS 81h, 181h) |               |                               |                  |                |           |              |         |  |  |

|---------------|---------------------------------------------|---------------|-------------------------------|------------------|----------------|-----------|--------------|---------|--|--|

|               | R/W-1                                       | R/W-1         | R/W-1                         | R/W-1            | R/W-1          | R/W-1     | R/W-1        | R/W-1   |  |  |

|               | RBPU                                        | INTEDG        | TOCS                          | T0SE             | PSA            | PS2       | PS1          | PS0     |  |  |

|               | bit 7                                       |               |                               |                  |                |           |              | bit 0   |  |  |

|               |                                             |               |                               |                  |                |           |              |         |  |  |

| bit 7         | RBPU: PC                                    | RTB Pull-u    | p Enable bit                  |                  |                |           |              |         |  |  |

|               |                                             |               | are disabled                  |                  |                |           |              |         |  |  |

|               |                                             |               |                               | by individual po | ort latch valu | les       |              |         |  |  |

| bit 6         |                                             | -             | ge Select bit                 |                  |                |           |              |         |  |  |

|               |                                             |               | edge of RB(<br>edge of RB     | •                |                |           |              |         |  |  |

| bit 5         |                                             |               | ource Select                  | -                |                |           |              |         |  |  |

|               |                                             |               | /T0CKI pin                    |                  |                |           |              |         |  |  |

|               | 0 = Interna                                 | al instructio | n cycle clock                 | (CLKO)           |                |           |              |         |  |  |

| bit 4         | TOSE: TM                                    | R0 Source     | Edge Select                   | bit              |                |           |              |         |  |  |

|               |                                             |               |                               | ition on RA4/1   |                |           |              |         |  |  |

|               |                                             |               |                               | ition on RA4/1   | OCKI pin       |           |              |         |  |  |

| bit 3         |                                             | caler Assig   |                               |                  |                |           |              |         |  |  |

|               |                                             | -             | ned to the W<br>ned to the Ti | mer0 module      |                |           |              |         |  |  |

| bit 2-0       |                                             |               | Rate Select b                 |                  |                |           |              |         |  |  |

|               | I                                           | Bit Value 1   | MR0 Rate \                    | VDT Rate         |                |           |              |         |  |  |

|               | _                                           | 000           | 1:2                           | 1:1              |                |           |              |         |  |  |

|               |                                             | 001<br>010    | 1:4                           | 1:2<br>1:4       |                |           |              |         |  |  |

|               |                                             | 010           | 1:8<br>1:16                   | 1:8              |                |           |              |         |  |  |

|               |                                             | 100           | 1:32                          | 1:16             |                |           |              |         |  |  |

|               |                                             | 101<br>110    | 1 : 64<br>1 : 128             | 1 : 32<br>1 : 64 |                |           |              |         |  |  |

|               | 111 1 : 256 1 : 128                         |               |                               |                  |                |           |              |         |  |  |

|               |                                             |               |                               |                  |                |           |              |         |  |  |

|               | Legend:                                     |               |                               |                  |                |           |              |         |  |  |

|               | R = Reada                                   | able bit      | VV = V                        | Vritable bit     | U = Unimp      | plemented | bit, read as | '0'     |  |  |

|               | - n = Value                                 | e at POR      | '1' = E                       | Bit is set       | '0' = Bit is   | cleared   | x = Bit is u | Inknown |  |  |

### F

## 3.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PIC<sup>™</sup> Mid-Range MCU Reference Manual, (DS33023).

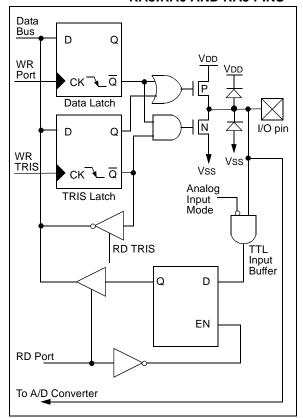

## 3.1 PORTA and the TRISA Register

PORTA is a 6-bit wide, bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register, reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the port data latch.

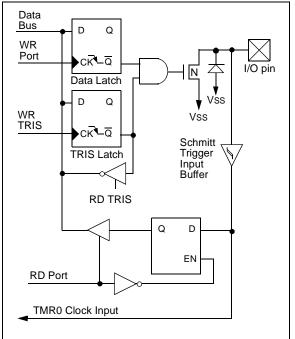

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

| Note: | On a Power-on Reset, these pins are con-  |

|-------|-------------------------------------------|

|       | figured as analog inputs and read as '0'. |

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

| EXAMPLE 3-1: | <b>INITIALIZING PORTA</b> |

|--------------|---------------------------|

|              |                           |

| BANKSEL<br>CLRF  | PORTA<br>PORTA | ; select bank for PORTA<br>; Initialize PORTA by<br>; clearing output<br>; data latches      |

|------------------|----------------|----------------------------------------------------------------------------------------------|

| BANKSEL<br>MOVLW | ADCON1<br>0x06 | ; Select Bank for ADCON1<br>; Configure all pins                                             |

| MOVWF<br>MOVLW   | ADCON1<br>0xCF | ; as digital inputs<br>; Value used to                                                       |

|                  |                | ; initialize data<br>; direction                                                             |

| MOVWF            | TRISA          | ; Set RA<3:0> as inputs<br>; RA<5:4> as outputs<br>; TRISA<7:6> are always<br>; read as `0'. |

### FIGURE 3-1: BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

FIGURE 3-2:

### BLOCK DIAGRAM OF RA4/T0CKI PIN

| Name         | Bit#  | Buffer | Function                                                                        |

|--------------|-------|--------|---------------------------------------------------------------------------------|

| RA0/AN0      | bit 0 | TTL    | Input/output or analog input.                                                   |

| RA1/AN1      | bit 1 | TTL    | Input/output or analog input.                                                   |

| RA2/AN2      | bit 2 | TTL    | Input/output or analog input.                                                   |

| RA3/AN3/VREF | bit 3 | TTL    | Input/output or analog input or VREF.                                           |

| RA4/T0CKI    | bit 4 | ST     | Input/output or external clock input for Timer0. Output is open drain type.     |

| RA5/AN4/SS   | bit 5 | TTL    | Input/output or analog input or slave select input for synchronous serial port. |

### TABLE 3-1:PORTA FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

### TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5   | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>RESETS |

|---------|--------|-------|-------|---------|-------------------------------|-------|-------|-------|-------|----------------------|---------------------------------|

| 05h     | PORTA  | —     | —     | RA5     | RA4                           | RA3   | RA2   | RA1   | RA0   | 0x 0000              | 0u 0000                         |

| 85h     | TRISA  | _     | _     | PORTA I | PORTA Data Direction Register |       |       |       |       |                      | 11 1111                         |

| 9Fh     | ADCON1 | _     | —     | —       | _                             | _     | PCFG2 | PCFG1 | PCFG0 | 000                  | 000                             |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

**Note:** When using the SSP module in SPI Slave mode and  $\overline{SS}$  enabled, the A/D Port Configuration Control bits (PCFG2:PCFG0) in the A/D Control Register (ADCON1) must be set to one of the following configurations: 100, 101, 11x.

| Name            | Bit#  | Buffer Type | Function                                                                              |

|-----------------|-------|-------------|---------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit 0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input.                 |

| RC1/T1OSI       | bit 1 | ST          | Input/output port pin or Timer1 oscillator input.                                     |

| RC2/CCP1        | bit 2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1 output.                  |

| RC3/SCK/SCL     | bit 3 | ST          | RC3 can also be the synchronous serial clock for both SPI and I <sup>2</sup> C modes. |

| RC4/SDI/SDA     | bit 4 | ST          | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).       |

| RC5/SDO         | bit 5 | ST          | Input/output port pin or Synchronous Serial Port data output.                         |

| RC6             | bit 6 | ST          | Input/output port pin.                                                                |

| RC7             | bit 7 | ST          | Input/output port pin.                                                                |

### TABLE 3-5: PORTC FUNCTIONS

Legend: ST = Schmitt Trigger input

### TABLE 3-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7 | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>RESETS |

|---------|-------|-------|-------------------------------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| 07h     | PORTC | RC7   | RC6                           | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx            | uuuu uuuu                       |

| 87h     | TRISC | PORTC | PORTC Data Direction Register |       |       |       |       |       |       |                      | 1111 1111                       |

Legend: x = unknown, u = unchanged

## 5.5 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt on overflow, that will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 5.5.1).

In Asynchronous Counter mode, Timer1 cannot be used as a time base for capture or compare operations.

### 5.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register. Data in the Timer1 register (TMR1) may become corrupted. Corruption occurs when the timer enable is turned off at the same instant that a ripple carry occurs in the timer module.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>™</sup> Mid-Range MCU

Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

## 5.6 Timer1 Oscillator

A crystal oscillator circuit is built between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 5-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

## TABLE 5-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type     | Freq                                                                           | C1            | C2                            |

|--------------|--------------------------------------------------------------------------------|---------------|-------------------------------|

| LP           | 32 kHz                                                                         | 33 pF         | 33 pF                         |

|              | 100 kHz                                                                        | 15 pF         | 15 pF                         |

|              | 200 kHz                                                                        | 15 pF         | 15 pF                         |

| These v      | alues are for                                                                  | design guidar | ice only.                     |

| c            | ligher capacita<br>of oscillator, bu<br>ime.                                   |               | -                             |

| c<br>ti<br>a | Since each res<br>haracteristics<br>he resonator<br>oppropriate<br>components. | , the user sh | ould consult<br>ufacturer for |

## 5.7 Timer1 Interrupt

The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/ clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

## 5.8 Resetting Timer1 Using a CCP Trigger Output

If the CCP module is configured in Compare mode to generate a "special event trigger" signal (CCP1M3:CCP1M0 = 1011), the signal will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

**Note:** The special event triggers from the CCP1 module will not set interrupt flag bit TMR1IF (PIR1<0>).

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L registers pair effectively becomes the period register for Timer1.

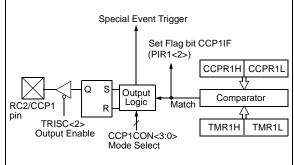

## 8.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven High

- Driven Low

- Remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

The output may become inverted when the mode of the module is changed from Compare/Clear on Match (CCPxM<3:0> = '1001') to Compare/Set on Match (CCPxM<3:0> = '1000'). This may occur as a result of any operation that selectively clears bit CCPxM0, such as a BCF instruction.

When this condition occurs, the output becomes inverted when the instruction is executed. It will remain inverted for all following Compare operations, until the module is reset.

### FIGURE 8-2: COMPARE MODE OPERATION BLOCK DIAGRAM

Special event trigger will:

- RESET Timer1, but not set interrupt flag bit TMR1IF (PIR1<0>)

- Set bit GO/DONE (ADCON0<2>) bit, which starts an A/D conversion

### 8.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force       |

|-------|------------------------------------------------|

|       | the RC2/CCP1 compare output latch to the       |

|       | default low level. This is not the data latch. |

### 8.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode, if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

### 8.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen, the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

### 8.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated that may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special trigger output of CCP1 resets the TMR1 register pair, and starts an A/D conversion (if the A/D module is enabled).

**Note:** The special event trigger from the CCP1 module will not set interrupt flag bit TMR1IF (PIR1<0>).

## 10.0 ANALOG-TO-DIGITAL **CONVERTER (A/D) MODULE**

The analog-to-digital (A/D) converter module has five inputs for the PIC16F72.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number. The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the RA3/AN3/VREF pin.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in SLEEP, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The A/D module has three registers:

- A/D Result Register ADRES

- A/D Control Register 0 ADCON0

- ADCON1 A/D Control Register 1

A device RESET forces all registers to their RESET state. This forces the A/D module to be turned off and any conversion is aborted.

The ADCON0 register, shown in Register 10-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 10-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or a digital I/O.

For more information on use of the A/D Converter, see AN546 - Use of A/D Converter, or refer to the PIC<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

### REGISTER 10-1: ADCON0: A/D CONTROL REGISTER 0 (ADDRESS 1Fh)

|         | R/W-0                  | R/W-0                          | R/W-0         | R/W-0           | R/W-0        | R/W-0           | U-0           | R/W-0     |

|---------|------------------------|--------------------------------|---------------|-----------------|--------------|-----------------|---------------|-----------|

|         | ADCS1                  | ADCS0                          | CHS2          | CHS1            | CHS0         | GO/DONE         |               | ADON      |

|         | bit 7                  |                                |               |                 |              |                 |               | bit 0     |

|         |                        |                                |               |                 |              |                 |               |           |

| bit 7-6 | ADCS<1:0               | >: A/D Conv                    | ersion Cloc   | k Select bits   |              |                 |               |           |

|         | 00 = Fosc              | -                              |               |                 |              |                 |               |           |

|         | 01 = Fosc<br>10 = Fosc |                                |               |                 |              |                 |               |           |

|         |                        |                                | d from the in | iternal A/D m   | nodule RC o  | oscillator)     |               |           |

| bit 5-3 |                        | : Analog Ch                    |               |                 |              | ,               |               |           |

|         | 000 <b>= Ch</b> a      | annel 0, (RA                   | )/AN0)        |                 |              |                 |               |           |

|         |                        | annel 1, (RA                   |               |                 |              |                 |               |           |

|         |                        | annel 2, (RA2<br>annel 3, (RA3 | ,             |                 |              |                 |               |           |

|         |                        | annel 4, (RA                   |               |                 |              |                 |               |           |

| bit 2   | GO/DONE                | A/D Conve                      | rsion Status  | bit             |              |                 |               |           |

|         | If ADON =              |                                |               |                 |              |                 |               |           |

|         |                        |                                |               | •               |              | /D conversion   | ,             |           |

|         |                        | rsion is com                   |               | (this dit is al | Itomatically | cleared by ha   | roware whe    | n the A/D |

| bit 1   | Unimplem               | nented: Rea                    | d as '0'      |                 |              |                 |               |           |

| bit 0   | ADON: A/               | D On bit                       |               |                 |              |                 |               |           |

|         |                        | onverter mod                   | •             | •               |              |                 |               |           |

|         | 0 = A/D cc             | onverter mod                   | ule is shut-o | off and consu   | mes no ope   | erating current |               |           |

|         |                        |                                |               |                 |              |                 |               |           |

|         | Legend:                |                                |               |                 |              |                 |               |           |

|         | R = Reada              |                                |               | /ritable bit    |              | mplemented bi   |               |           |

|         | - n = Value            | e at POR                       | '1' = B       | it is set       | '0' = Bit    | is cleared      | x = Bit is ur | nknown    |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                         |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' = '0', the next instruction is executed.<br>If bit 'b' = '1', then the next instruction is discarded and a NOP is executed instead, making this a 2 TCY instruction. |

| CLRF             | Clear f                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRF f                                                        |

| Operands:        | $0 \le f \le 127$                                                     |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | The contents of register 'f' are<br>cleared and the Z bit is set.     |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                                 |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                     |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                                    |

| Description:     | If bit 'b' in register 'f' = '1', the next<br>instruction is executed.<br>If bit 'b' in register 'f' = '0', the next<br>instruction is discarded, and a NOP<br>is executed instead, making this a<br>2 TCY instruction. |

| CLRW             | Clear W                                                                                    |

|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                                               |

| Operands:        | None                                                                                       |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow (\text{W}) \\ 1 \rightarrow \text{Z} \end{array}$ |

| Status Affected: | Z                                                                                          |

| Description:     | W register is cleared. Zero bit (Z) is set.                                                |

| CALL             | Call Subroutine                                                                                                                                                                                             | CLRWDT           | Clear Watchdog Timer                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                     | Syntax:          | [label] CLRWDT                                                                                                                 |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                          | Operands:        | None                                                                                                                           |

| Operation:       | (PC) + 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                           | Operation:       | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \end{array}$      |

| Status Affected: | None                                                                                                                                                                                                        |                  | $1 \rightarrow PD$                                                                                                             |

| Description:     | Call Subroutine. First, return                                                                                                                                                                              | Status Affected: | TO, PD                                                                                                                         |

|                  | address (PC+1) is pushed onto<br>the stack. The eleven-bit immedi-<br>ate address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a two-cycle instruction. | Description:     | CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT. Status bits<br>TO and PD are set. |

| RETFIE           | Return from Interrupt      | RLF              | Rotate Left f through Carry                                                                                                                                                                                                         |

|------------------|----------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETFIE             | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                                            |

| Operands:        | None                       | Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                   |

| Operation:       | $TOS \rightarrow PC$ ,     |                  | d ∈ [0,1]                                                                                                                                                                                                                           |

|                  | $1 \rightarrow \text{GIE}$ | Operation:       | See description below                                                                                                                                                                                                               |

| Status Affected: | None                       | Status Affected: | С                                                                                                                                                                                                                                   |

|                  |                            | Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag. If 'd' = '0', the<br>result is placed in the W register.<br>If 'd' = '1', the result is stored<br>back in register 'f'.<br>-C Register f |

| RETLW            | Return with Literal in W                                                                                                                                                            | RRF              | Rotate Right f through Carry                                                                                                                                                                                                      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            | Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                          |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   | Operands:        | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                                                                                          |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        | Operation:       | See description below                                                                                                                                                                                                             |

| Status Affected: | None                                                                                                                                                                                | Status Affected: | С                                                                                                                                                                                                                                 |

| Description:     | The W register is loaded with the<br>eight-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction. | Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' = '0', the<br>result is placed in the W register.<br>If 'd' = '1', the result is placed back<br>in register 'f'.<br>Register f |

| RETURN           | Return from Subroutine                                             | SLEEP            |                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETURN                                                     | Syntax:          | [label] SLEEP                                                                                                                                                                                 |

| Operands:        | None                                                               | Operands:        | None                                                                                                                                                                                          |

| Operation:       | $TOS\toPC$                                                         | Operation:       | 00h $\rightarrow$ WDT,                                                                                                                                                                        |

| Status Affected: | None                                                               |                  | $0 \rightarrow WDT$ prescaler,<br>1 $\rightarrow TO$ ,                                                                                                                                        |

| Description:     | Return from subroutine. The stack                                  |                  | $0 \rightarrow PD$                                                                                                                                                                            |

|                  | is POPed and the top of the stack (TOS) is loaded into the program | Status Affected: | TO, PD                                                                                                                                                                                        |

|                  | counter. This is a two-cycle instruction.                          | Description:     | The power-down status bit, $\overline{PD}$ is<br>cleared. Time-out status bit, $\overline{TO}$<br>is set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into SLEEP |

mode with the oscillator stopped.

## TABLE 13-1: DEVELOPMENT TOOLS FROM MICROCHIP

|                                                                       | PIC12CXXX | PIC14000 | PIC16C5X | PIC16C6X | VXX381219 | PIC16F62X | X7Oði Olq | (X7O81OI9 | PIC16C8X/<br>PIC16C8X | PIC16F8X | (X6D81DI9 | X43713I9 | (XTOTIOI9 | PIC18CXX | PIC18FXX | 83CXX<br>52CXX/<br>54CXX/ | хххэн | МСКFXXX | MCP2510 |

|-----------------------------------------------------------------------|-----------|----------|----------|----------|-----------|-----------|-----------|-----------|-----------------------|----------|-----------|----------|-----------|----------|----------|---------------------------|-------|---------|---------|

| MPLAB <sup>®</sup> Integrated<br>Development Environment              | >         | >        | >        | >        | >         | >         | >         | >         | >                     | >        | >         | >        | >         | >        | >        |                           |       |         |         |

| MPLAB <sup>®</sup> C17 C Compiler                                     |           |          |          | 1        |           |           |           |           |                       |          |           | >        | >         |          |          |                           |       |         |         |

| MPLAB <sup>®</sup> C18 C Compiler                                     |           |          |          |          |           |           |           |           |                       |          |           |          |           | >        | >        |                           |       |         |         |

| MPLINK <sup>TM</sup> Assembler/<br>MPLINK <sup>TM</sup> Object Linker | >         | >        | >        | >        | ^         | ~         | >         | >         | >                     | >        | >         | >        | >         | >        | >        | >                         | >     |         |         |

| MPLAB® ICE In-Circuit Emulator                                        | ~         | ~        | >        | >        | ~         | ×*`       | >         | >         | >                     | ~        | >         | >        | >         | ~        | ~        |                           |       |         |         |

| ICEPIC <sup>TM</sup> In-Circuit Emulator                              | >         |          | >        | >        | >         |           | >         | >         | >                     |          | >         |          |           |          |          |                           |       |         |         |

| MPLAB® ICD In-Circuit<br>Debugger                                     |           |          |          | *>       |           |           | * >       |           |                       | >        |           |          |           |          | >        |                           |       |         |         |

| PICSTART <sup>®</sup> Plus Entry Level<br>Development Programmer      | >         | >        | >        | >        | >         | **^       | >         | `         | `                     | `        | >         | >        | >         | >        | >        |                           |       |         |         |

| PRO MATE® II<br>Universal Device Programmer                           | >         | >        | >        | >        | >         | **/       | ^         | ^         | ^                     | ^        | >         | >        | >         | >        | >        | >                         | >     |         |         |

| PICDEM <sup>TM</sup> 1 Demonstration<br>Board                         |           |          | >        |          | >         |           | ÷+        |           | >                     |          |           | >        |           |          |          |                           |       |         |         |

| PICDEM <sup>™</sup> 2 Demonstration<br>Board                          |           |          |          | .≁       |           |           | .↓        |           |                       |          |           |          |           | >        | >        |                           |       |         |         |

| PICDEM <sup>TM</sup> 3 Demonstration<br>Board                         |           |          |          |          |           |           |           |           |                       |          | >         |          |           |          |          |                           |       |         |         |

| PICDEM <sup>TM</sup> 14A Demonstration<br>Board                       |           | >        |          |          |           |           |           |           |                       |          |           |          |           |          |          |                           |       |         |         |

| PICDEM <sup>TM</sup> 17 Demonstration<br>Board                        |           |          |          |          |           |           |           |           |                       |          |           |          | >         |          |          |                           |       |         |         |

| KEELoQ <sup>®</sup> Evaluation Kit                                    |           |          |          |          |           |           |           |           |                       |          |           |          |           |          |          |                           | >     |         |         |

| KEELoq® Transponder Kit                                               |           |          |          |          |           |           |           |           |                       |          |           |          |           |          |          |                           | >     |         |         |

| microlD™ Programmer's Kit                                             |           |          |          |          |           |           |           |           |                       |          |           |          |           |          |          |                           |       | ~       |         |

| 125 kHz microlD™<br>Developer's Kit                                   |           |          |          |          |           |           |           |           |                       |          |           |          |           |          |          |                           |       | >       |         |

| 125 kHz Anticollision microlD™<br>Developer's Kit                     |           |          |          |          |           |           |           |           |                       |          |           |          |           |          |          |                           |       | `       |         |

| 13.56 MHz Anticollision<br>microlD <sup>TM</sup> Developer's Kit      |           |          |          |          |           |           |           |           |                       |          |           |          |           |          |          |                           |       | >       |         |

| MCD0610 CAN Barrelande Kit                                            |           |          |          |          |           |           |           |           |                       |          |           |          |           |          |          |                           |       |         | >       |

\*\* Contact Microchip Technology Inc. for availability date.

<sup>†</sup> Development tool is available on select devices.

# PIC16F72

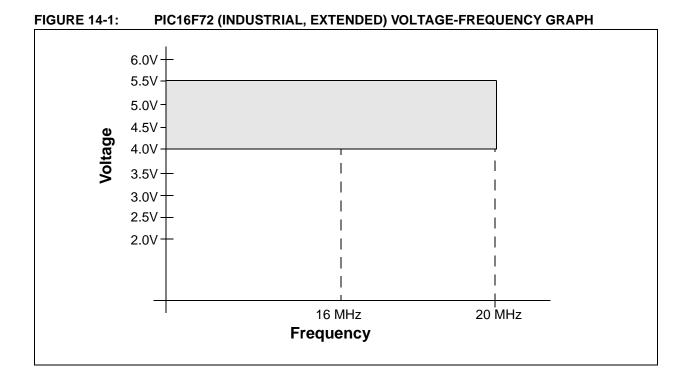

## 14.1 DC Characteristics: PIC16F72 (Industrial, Extended) PIC16LF72 (Industrial)

| PIC16LF72<br>(Industrial)          |      |                                                                  |                   | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial                                                  |                   |             |                                                                                        |  |  |

|------------------------------------|------|------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------|----------------------------------------------------------------------------------------|--|--|

| PIC16F72<br>(Industrial, Extended) |      |                                                                  |                   | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                   |             |                                                                                        |  |  |

| Param<br>No.                       | Sym  | Characteristic                                                   | Min               | Min Typ† Max Units Conditions                                                                                                                                                           |                   |             | Conditions                                                                             |  |  |

|                                    | Vdd  | Supply Voltage                                                   |                   |                                                                                                                                                                                         |                   |             |                                                                                        |  |  |

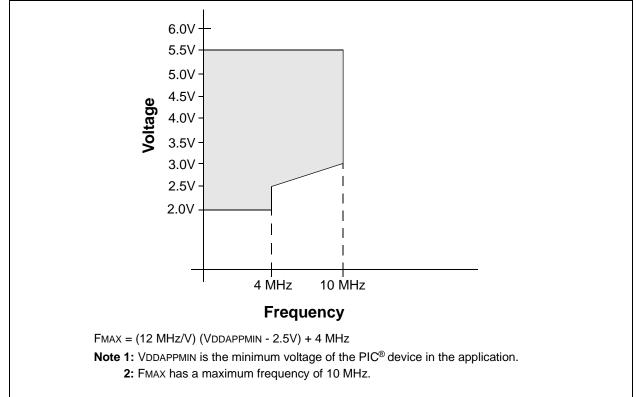

| D001                               |      | PIC16LF72                                                        | 2.0<br>2.5<br>2.2 |                                                                                                                                                                                         | 5.5<br>5.5<br>5.5 | V<br>V<br>V | A/D not used, -40°C to +85°C<br>A/D in use, -40°C to +85°C<br>A/D in use, 0°C to +85°C |  |  |

| D001<br>D001A                      |      | PIC16F72                                                         | 4.0<br>Vbor*      | _                                                                                                                                                                                       | 5.5<br>5.5        | V<br>V      | All configurations<br>BOR enabled <b>(Note 7)</b>                                      |  |  |

| D002*                              | Vdr  | RAM Data Retention<br>Voltage (Note 1)                           | —                 | 1.5                                                                                                                                                                                     | —                 | V           |                                                                                        |  |  |

| D003                               | VPOR | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | —                 | Vss                                                                                                                                                                                     | _                 | V           | See section on Power-on Reset for details                                              |  |  |

| D004*                              | SVDD | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05              | —                                                                                                                                                                                       | _                 | V/ms        | See section on Power-on Reset for details                                              |  |  |

| D005                               | VBOR | Brown-out Reset Voltage                                          | 3.65              | 4.0                                                                                                                                                                                     | 4.35              | V           | BOREN bit in configuration word enabled                                                |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements in active Operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD MCLR = VDD; WDT enabled/disabled as specified.

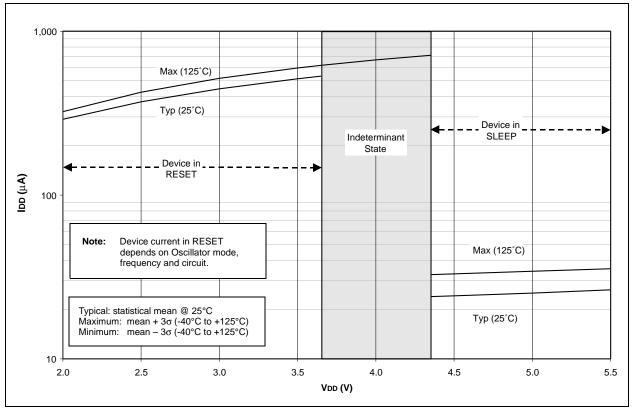

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

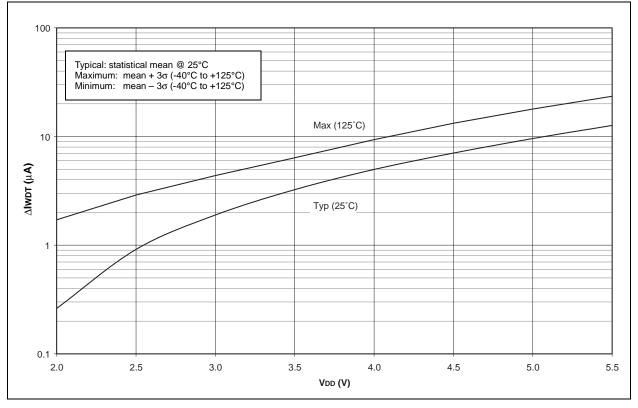

- 6: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

| Param<br>No. | Sym  | Characteristic                                    |           | Min | Тур†   | 「yp† Max |     | Conditions                                                                                                                                                                                                                       |  |

|--------------|------|---------------------------------------------------|-----------|-----|--------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

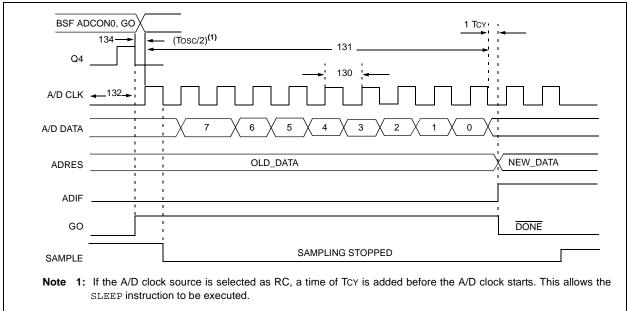

| 130          | Tad  | A/D Clock Period                                  | PIC16F72  | 1.6 | —      | -        | μs  | Tosc based, VREF $\geq$ 3.0V                                                                                                                                                                                                     |  |

|              |      |                                                   | PIC16LF72 | 2.0 | —      | —        | μs  | Tosc based,<br>2.0V ≤ VREF ≤ 5.5V                                                                                                                                                                                                |  |

|              |      |                                                   | PIC16F72  | 2.0 | 4.0    | 6.0      | μs  | A/D RC mode                                                                                                                                                                                                                      |  |

|              |      |                                                   | PIC16LF72 | 3.0 | 6.0    | 9.0      | μs  | A/D RC mode                                                                                                                                                                                                                      |  |

| 131          | TCNV | Conversion Time (not including S/H time) (Note 1) |           | 9   | —      | 9        | TAD |                                                                                                                                                                                                                                  |  |

| 132          | TACQ | Acquisition Time                                  |           | 5*  |        | _        | μs  | The minimum time is the<br>amplifier settling time. This<br>may be used if the "new"<br>input voltage has not<br>changed by more than 1 LSb<br>(i.e., 20.0 mV @ 5.12V) from<br>the last sampled voltage (as<br>stated on CHOLD). |  |

| 134          | TGO  | Q4 to A/D Clock Start                             |           | _   | Tosc/2 | _        |     | If the A/D clock source is<br>selected as RC, a time of Tcy<br>is added before the A/D<br>clock starts. This allows the<br>SLEEP instruction to be<br>executed.                                                                  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** ADRES register may be read on the following TCY cycle.

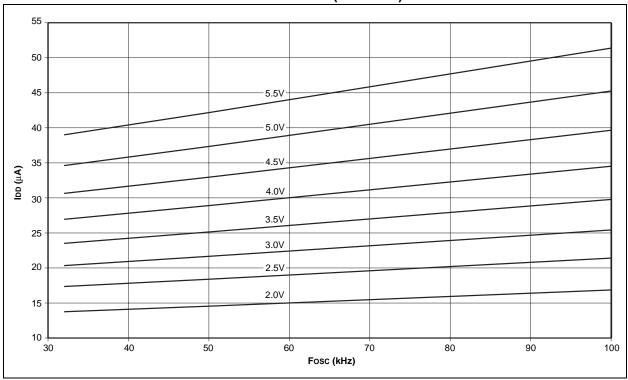

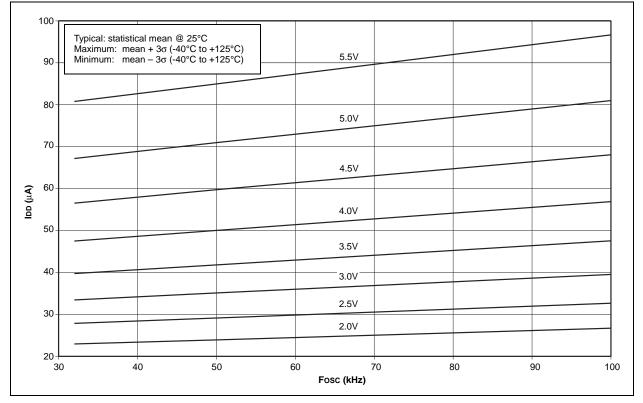

FIGURE 15-5: TYPICAL IDD vs. Fosc OVER VDD (LP MODE)

### FIGURE 15-11: △IBOR vs. VDD OVER TEMPERATURE

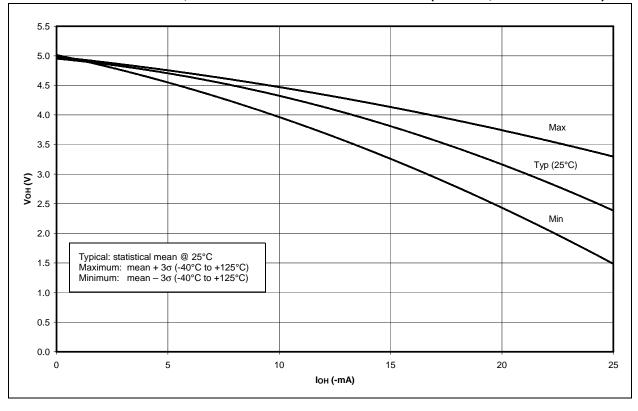

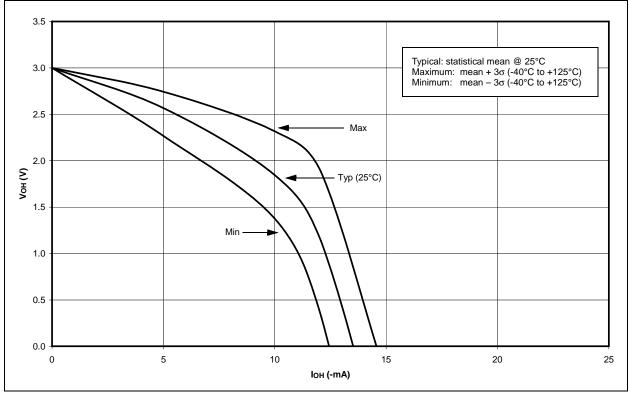

FIGURE 15-15: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD = 5V, -40°C TO +125°C)

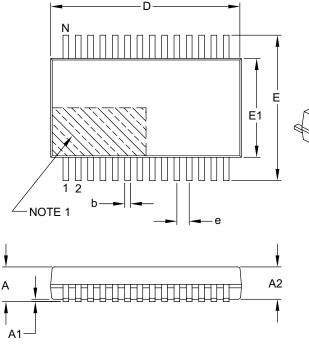

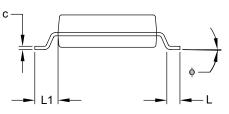

## 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    | MILLIMETERS |       |       |  |

|--------------------------|----------|-------------|-------|-------|--|

| Dimension                | n Limits | MIN         | NOM   | MAX   |  |

| Number of Pins           | Ν        |             | 28    |       |  |