### Microchip Technology - PIC16LF72T-I/SO Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0 0              |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf72t-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.4 PIE1 Register

This register contains the individual enable bits for the peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

- n = Value at POR

#### REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1 (ADDRESS 8Ch)

| ER 2-4: | PIET: PER                                  | IPHERAL      | INTERRU         |               | REGISTI  |             | KE33 00      | n)     |

|---------|--------------------------------------------|--------------|-----------------|---------------|----------|-------------|--------------|--------|

|         | U-0                                        | R/W-0        | U-0             | U-0           | R/W-0    | R/W-0       | R/W-0        | R/W-0  |

|         | —                                          | ADIE         | —               | —             | SSPIE    | CCP1IE      | TMR2IE       | TMR1IE |

|         | bit 7                                      |              |                 |               |          |             |              | bit 0  |

| bit 7   | Unimpleme                                  | ented: Rea   | d as '0'        |               |          |             |              |        |

| bit 6   | •                                          |              | nterrupt Enal   | hla hit       |          |             |              |        |

| DILO    |                                            |              | onverter inter  |               |          |             |              |        |

|         |                                            |              | onverter inte   |               |          |             |              |        |

| bit 5-4 | Unimpleme                                  | ented: Rea   | d as '0'        |               |          |             |              |        |

| bit 3   | SSPIE: Syr                                 | nchronous S  | Serial Port Int | terrupt Enabl | e bit    |             |              |        |

|         | 1 = Enables                                |              |                 |               |          |             |              |        |

|         | 0 = Disable                                | es the SSP i | nterrupt        |               |          |             |              |        |

| bit 2   | CCP1IE: C                                  | CP1 Interru  | pt Enable bit   |               |          |             |              |        |

|         | 1 = Enables                                |              |                 |               |          |             |              |        |

|         | 0 = Disables the CCP1 interrupt            |              |                 |               |          |             |              |        |

| bit 1   | TMR2IE: TI                                 | MR2 to PR2   | 2 Match Inter   | rupt Enable b | oit      |             |              |        |

|         |                                            |              | to PR2 mate     |               |          |             |              |        |

|         | 0 = Disable                                | es the TMR2  | 2 to PR2 mat    | ch interrupt  |          |             |              |        |

| bit 0   | TMR1IE: TMR1 Overflow Interrupt Enable bit |              |                 |               |          |             |              |        |

|         | 1 = Enables the TMR1 overflow interrupt    |              |                 |               |          |             |              |        |

|         | 0 = Disable                                | es the TMR1  | l overflow int  | terrupt       |          |             |              |        |

|         | Legend:                                    |              |                 |               |          |             |              |        |

|         | R = Readab                                 | ole bit      | W = W           | /ritable bit  | U = Unim | plemented I | oit, read as | '0'    |

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

#### 2.2.2.5 PIR1 Register

This register contains the individual flag bits for the Peripheral interrupts.

- n = Value at POR

| EGISTER 2-5: | PIR1: PEI                             | RIPHERAL                                          | INTERRUI                                                           | PT FLAG R              | EGISTER       | 1 (ADDRE      | SS 0Ch)      |        |

|--------------|---------------------------------------|---------------------------------------------------|--------------------------------------------------------------------|------------------------|---------------|---------------|--------------|--------|

|              | U-0                                   | R/W-0                                             | U-0                                                                | U-0                    | R/W-0         | R/W-0         | R/W-0        | R/W-0  |

|              |                                       | ADIF                                              | —                                                                  | —                      | SSPIF         | CCP1IF        | TMR2IF       | TMR1IF |

|              | bit 7                                 |                                                   |                                                                    |                        |               |               |              | bit 0  |

|              |                                       |                                                   |                                                                    |                        |               |               |              |        |

| bit 7        | Unimplem                              | ented: Read                                       | d as '0'                                                           |                        |               |               |              |        |

| bit 6        |                                       |                                                   | nterrupt Flag                                                      | bit                    |               |               |              |        |

|              |                                       | ) conversion<br>/D conversio                      | completed                                                          | olete                  |               |               |              |        |

| bit 5-4      | Unimplem                              | ented: Read                                       | d as '0'                                                           |                        |               |               |              |        |

| bit 3        | SSPIF: Sy                             | nchronous S                                       | Serial Port (S                                                     | SP) Interrupt          | Flag bit      |               |              |        |

|              | from th<br>The co<br>0 = No SS        | ne Interrupt S<br>onditions that<br>P interrupt c | condition has<br>Service Routi<br>t will set this<br>condition has | ine.<br>bit are a tran |               |               |              | Ū      |

| bit 2        | bit 2 CCP1IF: CCP1 Interrupt Flag bit |                                                   |                                                                    |                        |               |               |              |        |

|              |                                       | R1 register ca                                    | apture occurr<br>capture occu                                      |                        | cleared in s  | oftware)      |              |        |

|              |                                       | R1 register co                                    | ompare matc<br>compare mat                                         |                        | must be clea  | ared in softv | vare)        |        |

|              | <u>PWM mod</u><br>Unused in           |                                                   |                                                                    |                        |               |               |              |        |

| bit 1        | TMR2IF: T                             | MR2 to PR2                                        | 2 Match Inter                                                      | rupt Flag bit          |               |               |              |        |

|              |                                       |                                                   | ch occurred (<br>natch occurr                                      |                        | ared in softw | /are)         |              |        |

| bit 0        | TMR1IF: T                             | MR1 Overflo                                       | ow Interrupt                                                       | Flag bit               |               |               |              |        |

|              | 1 = TMR1                              | register ove                                      | rflowed (mus<br>not overflow                                       | -                      | in software)  | )             |              |        |

|              | Legend:                               |                                                   |                                                                    |                        |               |               |              | ]      |

|              | R = Reada                             | ble bit                                           | W = W                                                              | ritable bit            | U = Unim      | plemented     | bit, read as | '0'    |

|              | 1                                     |                                                   |                                                                    |                        |               |               |              |        |

'1' = Bit is set

x = Bit is unknown

'0' = Bit is cleared

### 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the Application Note, *"Implementing a Table Read"* (AN556).

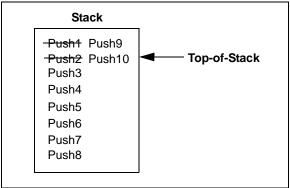

### 2.3.2 STACK

The stack allows a combination of up to eight program calls and interrupts to occur. The stack contains the return address from this branch in program execution.

Mid-range devices have an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSH'd onto the stack when a CALL instruction is executed, or an interrupt causes a branch. The stack is POP'd in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not modified when the stack is PUSH'd or POP'd.

After the stack has been PUSH'd eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on). An example of the overwriting of the stack is shown in Figure 2-4.

#### FIGURE 2-4: STACK MODIFICATION

Note 1: There are no status bits to indicate stack overflow or stack underflow conditions.

2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

# 2.4 Program Memory Paging

The CALL and GOTO instructions provide 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper two bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the return instructions (which POPs the address from the stack).

| Note: | The PIC16F72 device ignores the paging      |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | bit PCLATH<4:3>. The use of                 |  |  |  |  |  |

|       | PCLATH<4:3> as a general purpose read/      |  |  |  |  |  |

|       | write bit is not recommended, since this    |  |  |  |  |  |

|       | may affect upward compatibility with future |  |  |  |  |  |

|       | products.                                   |  |  |  |  |  |

# 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-1.

| EXAMPLE 2-1: | INDIRECT | ADDRESSING |

|--------------|----------|------------|

|              |          |            |

| NEXT     | movwf<br>clrf<br>incf<br>btfss | FSR<br>INDF<br>FSR<br>FSR,4 | <pre>;initialize pointer ;to RAM ;clear INDF register ;inc pointer ;all done? ;NO, clear next</pre> |

|----------|--------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------|

| CONTINUE | :                              |                             | ;YES, continue                                                                                      |

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-5.

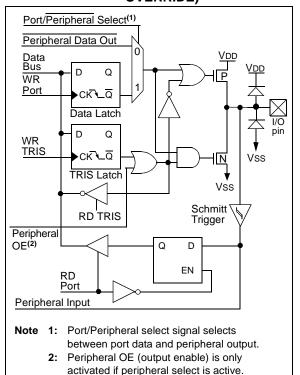

### 3.3 PORTC and the TRISC Register

PORTC is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

PORTC is multiplexed with several peripheral functions (Table 3-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

EXAMPLE 3-3: INITIALIZING PORTC

| BANKSEL | PORTC | ; Select Bank for PORTC |

|---------|-------|-------------------------|

|         |       |                         |

| CLRF    | PORTC | ; Initialize PORTC by   |

|         |       | ; clearing output       |

|         |       | ; data latches          |

| BANKSEL | TRISC | ; Select Bank for TRISC |

| MOVLW   | 0xCF  | ; Value used to         |

|         |       | ; initialize data       |

|         |       | ; direction             |

| MOVWF   | TRISC | ; Set RC<3:0> as inputs |

|         |       | ; RC<5:4> as outputs    |

|         |       | ; RC<7:6> as inputs     |

|         |       |                         |

# FIGURE 3-5:

#### PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

# 7.0 READING PROGRAM MEMORY

The FLASH Program Memory is readable during normal operation over the entire VDD range. It is indirectly addressed through Special Function Registers (SFR). Up to 14-bit wide numbers can be stored in memory for use as calibration parameters, serial numbers, packed 7-bit ASCII, etc. Executing a program memory location containing data that forms an invalid instruction results in a NOP.

There are five SFRs used to read the program and memory:

- PMCON1

- PMDATL

- PMDATH

- PMADRL

- PMADRH

The program memory allows word reads. Program memory access allows for checksum calculation and reading calibration tables.

When interfacing to the program memory block, the PMDATH:PMDATL registers form a two-byte word, which holds the 14-bit data for reads. The PMADRH:PMADRL registers form a two-byte word, which holds the 13-bit address of the FLASH location being accessed. This device has up to 2K words of program FLASH, with an address range from 0h to 07FFh. The unused upper bits PMDATH<7:6> and PMADRH<7:5> are not implemented and read as zeros.

R = Readable bit

'1' = Bit is set

# 7.1 PMADR

The address registers can address up to a maximum of 8K words of program FLASH.

When selecting a program address value, the MSByte of the address is written to the PMADRH register and the LSByte is written to the PMADRL register. The upper MSbits of PMADRH must always be clear.

# 7.2 PMCON1 Register

PMCON1 is the control register for memory accesses.

The control bit RD initiates read operations. This bit cannot be cleared, only set, in software. It is cleared in hardware at the completion of the read operation.

#### REGISTER 7-1: PMCON1: PROGRAM MEMORY CONTROL REGISTER 1 (ADDRESS 18Ch)

|                                                                                                                 |             |       | •••••       |              |        |     | ···,  |

|-----------------------------------------------------------------------------------------------------------------|-------------|-------|-------------|--------------|--------|-----|-------|

| R-1                                                                                                             | U-0         | U-0   | U-0         | U-0          | U-0    | U-0 | R/S-0 |

| reserved                                                                                                        | _           | —     | _           | —            | —      | —   | RD    |

| bit 7                                                                                                           |             |       |             |              |        |     | bit 0 |

|                                                                                                                 |             |       |             |              |        |     |       |

| Reserved:                                                                                                       | Read as '1' |       |             |              |        |     |       |

| Unimplemented: Read as '0'                                                                                      |             |       |             |              |        |     |       |

| RD: Read Control bit                                                                                            |             |       |             |              |        |     |       |

| 1 = Initiates a FLASH read, RD is cleared in hardware. The RD bit can only be set (not cleared)<br>in software. |             |       |             |              |        |     |       |

| 0 = Does not initiate a FLASH read                                                                              |             |       |             |              |        |     |       |

|                                                                                                                 |             |       |             |              |        |     |       |

| Legend:                                                                                                         |             |       |             |              |        |     |       |

| W = Writab                                                                                                      | le bit      | U = l | Jnimplement | ed bit, read | as '0' |     |       |

S = Settable bit

'0' = Bit is cleared

bit 7 bit 6-1 bit 0

-n = Value at POR

x = Bit is unknown

# 8.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The CCP (Capture/Compare/PWM) module contains a 16-bit register that can operate as a:

- 16-bit capture register

- 16-bit compare register

- PWM master/slave duty cycle register.

Table 8-1 shows the timer resources of the CCP Module modes.

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable. Additional information on the CCP module is available in the PIC<sup>™</sup> Mid-Range MCU Reference Manual, (DS33023).

# TABLE 8-1:CCP MODE - TIMER<br/>RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

#### **REGISTER 8-1:** CCPCON1: CAPTURE/COMPARE/PWM CONTROL REGISTER 1 (ADDRESS 17h)

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

| —     | _   | CCPxX | CCPxY | CCPxM3 | CCPxM2 | CCPxM1 | CCPxM0 |

| bit 7 |     |       |       |        |        |        | bit 0  |

- bit 7-6 Unimplemented: Read as '0'

- bit 5-4 CCPxX:CCPxY: PWM Least Significant bits Capture mode:

|         | Capture mode:                                                                                                                                                       |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Unused                                                                                                                                                              |

|         | Compare mode:                                                                                                                                                       |

|         | Unused                                                                                                                                                              |

|         | PWM mode:                                                                                                                                                           |

|         | These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                                              |

| bit 3-0 | CCPxM3:CCPxM0: CCPx Mode Select bits                                                                                                                                |

|         | 0000 = Capture/Compare/PWM disabled (resets CCPx module)                                                                                                            |

|         | 0100 = Capture mode, every falling edge                                                                                                                             |

|         | 0101 = Capture mode, every rising edge                                                                                                                              |

|         | 0110 = Capture mode, every 4th rising edge                                                                                                                          |

|         | 0111 = Capture mode, every 16th rising edge                                                                                                                         |

|         | 1000 = Compare mode, set output on match (CCPxIF bit is set)                                                                                                        |

|         | 1001 = Compare mode, clear output on match (CCPxIF bit is set)                                                                                                      |

|         | 1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set,                                                                                       |

|         | CCPx pin is unaffected)                                                                                                                                             |

|         | 1011 = Compare mode, trigger special event (CCPxIF bit is set, CCPx pin is unaffected);<br>CCP1 resets TMR1 and starts an A/D conversion (if A/D module is enabled) |

|         | 11xx = PWM mode                                                                                                                                                     |

|         |                                                                                                                                                                     |

|         |                                                                                                                                                                     |

|         | Legend:                                                                                                                                                             |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

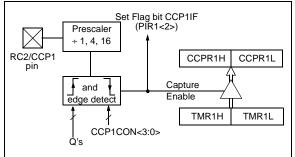

# 8.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as:

- · Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

#### 8.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 is configured as an out-     |

|-------|----------------------------------------------|

|       | put, a write to the port can cause a capture |

|       | condition.                                   |

#### FIGURE 8-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 8.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 8.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF, following any such change in Operating mode.

#### 8.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any RESET will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 8-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 8-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ; Turn CCP module off   |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ; Load the W reg with   |

|       |             | ; the new prescaler     |

|       |             | ; mode value and CCP ON |

| MOVWF | CCP1CON     | ; Load CCP1CON with     |

|       |             | ; this value            |

|       |             |                         |

| Address              | Name    | Bit 7   | Bit 6                                                                       | Bit 5        | Bit 4         | Bit 3         | Bit 2       | Bit 1     | Bit 0  |      | e on<br>BOR | all o | e on<br>other<br>SETS |

|----------------------|---------|---------|-----------------------------------------------------------------------------|--------------|---------------|---------------|-------------|-----------|--------|------|-------------|-------|-----------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE     | PEIE                                                                        | TMR0IE       | INTE          | RBIE          | TMR0IF      | INTF      | RBIF   | 0000 | 000x        | 0000  | 000u                  |

| 0Ch                  | PIR1    | —       | ADIF                                                                        | —            |               | SSPIF         | CCP1IF      | TMR2IF    | TMR1IF | - 0  | 0000        | 0000  | 0000                  |

| 8Ch                  | PIE1    | —       | ADIE                                                                        | —            | _             | SSPIE         | CCP1IE      | TMR2IE    | TMR1IE | - 0  | 0000        | 0000  | 0000                  |

| 87h                  | TRISC   | PORTC   | PORTC Data Direction Register                                               |              |               |               |             |           |        | 1111 | 1111        | 1111  | 1111                  |

| 0Eh                  | TMR1L   | Holding | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |              |               |               |             |           | xxxx   | uuuu | uuuu        |       |                       |

| 0Fh                  | TMR1H   | Holding | Registe                                                                     | er for the M | ost Significa | ant Byte of t | he 16-bit T | MR1 Regis | ster   | xxxx | xxxx        | uuuu  | uuuu                  |

| 10h                  | T1CON   | —       |                                                                             | T1CKPS1      | T1CKPS0       | T1OSCEN       | T1SYNC      | TMR1CS    | TMR10N | 00   | 0000        | uu    | uuuu                  |

| 15h                  | CCPR1L  | Capture | Capture/Compare/PWM Register1 (LSB)                                         |              |               |               |             | uuuu      |        |      |             |       |                       |

| 16h                  | CCPR1H  | Capture | Capture/Compare/PWM Register1 (MSB)                                         |              |               |               |             | uuuu      |        |      |             |       |                       |

| 17h                  | CCP1CON | _       | _                                                                           | CCP1X        | CCP1Y         | CCP1M3        | CCP1M2      | CCP1M1    | CCP1M0 | 00   | 0000        | 00    | 0000                  |

# TABLE 8-2: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.

Maximum PWM resolution (bits) for a given PWM frequency is calculated using Equation 8-3.

#### EQUATION 8-3: PWM MAX RESOLUTION

PWM Maximum Resolution =  $\frac{\log{(\frac{Fosc}{FpWM})}}{\log(2)}$  bits

| Note: | If the PWM duty cycle value is longer than |

|-------|--------------------------------------------|

|       | the PWM period, the CCP1 pin will not be   |

|       | cleared.                                   |

For a sample PWM period and duty cycle calculation, see the PIC<sup>™</sup> Mid-Range MCU Reference Manual (DS33023).

#### 8.3.3 SET-UP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

| <b>TABLE 8-3</b> : | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz |

|--------------------|---------------------------------------------------|

|                    |                                                   |

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

#### TABLE 8-4: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address              | Name    | Bit 7  | Bit 6                               | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   |      | e on<br>BOR |      | e on<br>ther<br>ETS |

|----------------------|---------|--------|-------------------------------------|---------|---------|---------|--------|---------|---------|------|-------------|------|---------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE    | PEIE                                | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000 | 000x        | 0000 | 000u                |

| 0Ch                  | PIR1    | _      | ADIF                                | _       | _       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | - 0  | 0000        | 0000 | 0000                |

| 8Ch                  | PIE1    | —      | ADIE                                | _       | _       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | - 0  | 0000        | 0000 | 0000                |

| 87h                  | TRISC   | PORT   | PORTC Data Direction Register       |         |         |         |        |         |         | 1111 | 1111        | 1111 | 1111                |

| 11h                  | TMR2    | Timer2 | Timer2 Module Register              |         |         |         |        |         |         | 0000 | 0000        | 0000 | 0000                |

| 92h                  | PR2     | Timer2 | Timer2 Module Period Register       |         |         |         |        |         | 1111    | 1111 | 1111        | 1111 |                     |

| 12h                  | T2CON   | _      | TOUTPS3                             | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 | 0000        | -000 | 0000                |

| 15h                  | CCPR1L  | Captur | Capture/Compare/PWM Register1 (LSB) |         |         |         |        |         | xxxx    | uuuu | uuuu        |      |                     |

| 16h                  | CCPR1H  | Captur | Capture/Compare/PWM Register1 (MSB) |         |         |         |        | uuuu    |         |      |             |      |                     |

| 17h                  | CCP1CON | _      | _                                   | CCP1X   | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00   | 0000        | 00   | 0000                |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2.

# 10.5 A/D Operation During SLEEP

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed, the GO/DONE bit will be cleared, and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

Note: For the A/D module to operate in SLEEP, the A/D clock source must be set to RC (ADCS1:ADCS0 = 11). To perform an A/D conversion in SLEEP, ensure the SLEEP instruction immediately follows the instruction that sets the GO/DONE bit.

### 10.6 Effects of a RESET

A device RESET forces all registers to their RESET state. The A/D module is disabled and any conversion in progress is aborted. All A/D input pins are configured as analog inputs.

The ADRES register will contain unknown data after a Power-on Reset.

# 10.7 Use of the CCP Trigger

An A/D conversion can be started by the "special event trigger" of the CCP1 module. This requires that the CCP1M3:CCP1M0 bits (CCP1CON<3:0>) be programmed as 1011 and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving the ADRES to the desired location). The appropriate analog input channel must be selected and the minimum acquisition done\_before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

| Address              | Name   | Bit 7   | Bit 6      | Bit 5   | Bit 4     | Bit 3     | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>RESETS |

|----------------------|--------|---------|------------|---------|-----------|-----------|---------|--------|--------|----------------------|---------------------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON | GIE     | PEIE       | TMR0IE  | INTE      | RBIE      | TMR0IF  | INTF   | RBIF   | 0000 000x            | 0000 000u                       |

| 0Ch                  | PIR1   | —       | ADIF       | _       | —         | SSPIF     | CCP1IF  | TMR2IF | TMR1IF | -0 0000              | -0 0000                         |

| 8Ch                  | PIE1   | —       | ADIE       | _       | _         | SSPIE     | CCP1IE  | TMR2IE | TMR1IE | -0 0000              | -0 0000                         |

| 1Eh                  | ADRES  | A/D Res | ult Regist | er      |           |           |         |        |        | xxxx xxxx            | uuuu uuuu                       |

| 1Fh                  | ADCON0 | ADCS1   | ADCS0      | CHS2    | CHS1      | CHS0      | GO/DONE | —      | ADON   | 0000 00-0            | 0000 00-0                       |

| 9Fh                  | ADCON1 | —       | —          | —       | _         | —         | PCFG2   | PCFG1  | PCFG0  | 000                  | 000                             |

| 05h                  | PORTA  | _       | _          | RA5     | RA4       | RA3       | RA2     | RA1    | RA0    | 0x 0000              | 0u 0000                         |

| 85h                  | TRISA  | _       | _          | PORTA D | Data Dire | ection Re | gister  |        |        | 11 1111              | 11 1111                         |

#### TABLE 10-2: REGISTERS/BITS ASSOCIATED WITH A/D

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

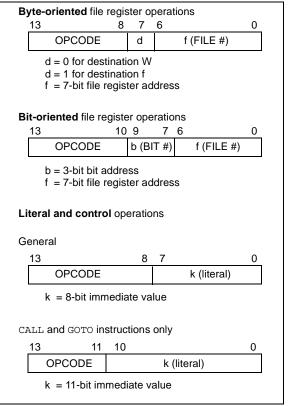

# 12.0 INSTRUCTION SET SUMMARY

Each PIC16F72 instruction is a 14-bit word divided into an OPCODE that specifies the instruction type and one or more operands that further specify the operation of the instruction. The PIC16F72 instruction set summary in Table 12-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 12-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven-bit constant or literal value.

#### TABLE 12-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                            |

| W     | Working register (accumulator)                                                                                                                                                  |

| b     | Bit address within an 8-bit file register                                                                                                                                       |

| k     | Literal field, constant data or label                                                                                                                                           |

| x     | Don't care location (= 0 or 1).<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                   |

| PC    | Program Counter                                                                                                                                                                 |

| TO    | Time-out bit                                                                                                                                                                    |

| PD    | Power-down bit                                                                                                                                                                  |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles, with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Table 12-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

Figure 12-1 shows the general formats that the instructions can have.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

# FIGURE 12-1: GENERAL FORMAT FOR INSTRUCTIONS

A description of each instruction is available in the PIC<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

| SUBLW            | Subtract W from Literal                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                     |

| Operands:        | $0 \le k \le 255$                                                                                                            |

| Operation:       | $k \text{ - (W)} \rightarrow (W)$                                                                                            |

| Status Affected: | C, DC, Z                                                                                                                     |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register. |

| XORLW            | Exclusive OR Literal with W                                                                                                |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] XORLW k                                                                                                            |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                          |  |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                              |  |  |  |  |  |

| Status Affected: | Z                                                                                                                          |  |  |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed in<br>the W register. |  |  |  |  |  |

| SUBWF            | Subtract W from f                                                                                                                                                                         |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SUBWF f,d                                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                     |

| Status Affected: | C, DC, Z                                                                                                                                                                                  |

| Description:     | Subtract (2's complement method)<br>W register from register 'f'. If<br>'d' = '0', the result is stored in the W<br>register. If 'd' = '1', the result is<br>stored back in register 'f'. |

| XORWF            | Exclusive OR W with f                                                                                                                                                         |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] XORWF f,d                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                            |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                     |

| Status Affected: | Z                                                                                                                                                                             |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' = '0', the result is stored in the W register. If 'd' = '1', the result is stored back in register 'f'. |

| SWAPF            | Swap Nibbles in f                                                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>), (f<7:4>) \rightarrow (destination<3:0>)$                                                                               |

| Status Affected: | None                                                                                                                                                             |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' = '0', the result is placed in W register. If 'd' = '1', the result is placed in register 'f'. |

# 14.1 DC Characteristics: PIC16F72 (Industrial, Extended) PIC16LF72 (Industrial)

|                  |                         |                                                                  |                                                                                                                                                                                         |      | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |             |                                                                                        |  |  |  |

|------------------|-------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------|--|--|--|

| PIC16F<br>(Indus | <b>72</b><br>strial, Ex | tended)                                                          | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |                                                                                                                                        |             |                                                                                        |  |  |  |

| Param<br>No.     | Sym                     | Characteristic                                                   | Min                                                                                                                                                                                     | Тур† | Max                                                                                                                                    | Units       | Conditions                                                                             |  |  |  |

|                  | Vdd                     | Supply Voltage                                                   |                                                                                                                                                                                         |      |                                                                                                                                        |             |                                                                                        |  |  |  |

| D001             |                         | PIC16LF72                                                        | 2.0<br>2.5<br>2.2                                                                                                                                                                       |      | 5.5<br>5.5<br>5.5                                                                                                                      | V<br>V<br>V | A/D not used, -40°C to +85°C<br>A/D in use, -40°C to +85°C<br>A/D in use, 0°C to +85°C |  |  |  |

| D001<br>D001A    |                         | PIC16F72                                                         | 4.0<br>Vbor*                                                                                                                                                                            | _    | 5.5<br>5.5                                                                                                                             | V<br>V      | All configurations<br>BOR enabled <b>(Note 7)</b>                                      |  |  |  |

| D002*            | Vdr                     | RAM Data Retention<br>Voltage (Note 1)                           |                                                                                                                                                                                         | 1.5  | —                                                                                                                                      | V           |                                                                                        |  |  |  |

| D003             | VPOR                    | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | _                                                                                                                                                                                       | Vss  | _                                                                                                                                      | V           | See section on Power-on Reset for details                                              |  |  |  |

| D004*            | SVDD                    | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05                                                                                                                                                                                    | —    | _                                                                                                                                      | V/ms        | See section on Power-on Reset for details                                              |  |  |  |

| D005             | VBOR                    | Brown-out Reset Voltage                                          | 3.65                                                                                                                                                                                    | 4.0  | 4.35                                                                                                                                   | V           | BOREN bit in configuration word enabled                                                |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements in active Operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

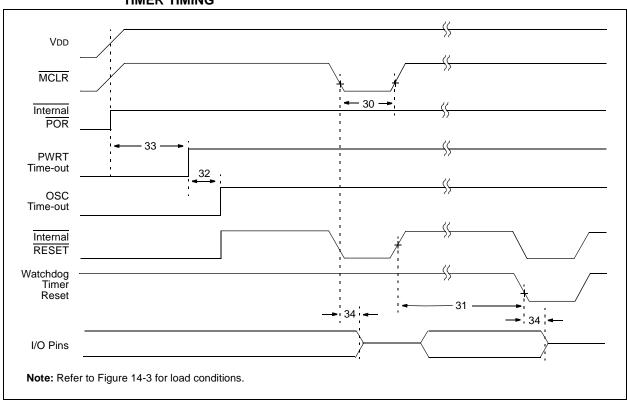

# FIGURE 14-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

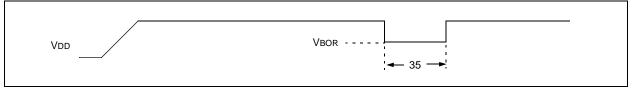

FIGURE 14-7: BROWN-OUT RESET TIMING

# TABLE 14-3:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET REQUIREMENTS

| Parameter No. | Symbol | Characteristic                                         | Min | Тур†      | Max | Units | Conditions               |

|---------------|--------|--------------------------------------------------------|-----|-----------|-----|-------|--------------------------|

| 30            | TmcL   | MCLR Pulse Width (low)                                 | 2   | _         | -   | μs    | VDD = 5V, -40°C to +85°C |

| 31*           | Twdt   | Watchdog Timer Time-out Period<br>(No Prescaler)       | 7   | 18        | 33  | ms    | VDD = 5V, -40°C to +85°C |

| 32            | Tost   | Oscillation Start-up Timer Period                      | _   | 1024 Tosc | _   | —     | Tosc = OSC1 period       |

| 33*           | TPWRT  | Power-up Timer Period                                  | 28  | 72        | 132 | ms    | VDD = 5V, -40°C to +85°C |

| 34            | Tioz   | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | _   | _         | 2.1 | μs    |                          |

| 35            | TBOR   | Brown-out Reset Pulse Width                            | 100 | _         | _   | μs    | $VDD \le VBOR (D005)$    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| Param<br>No. | Sym  | Characte                                          | eristic            | Min        | Тур†       | Мах                | Units    | Conditions                                                                   |

|--------------|------|---------------------------------------------------|--------------------|------------|------------|--------------------|----------|------------------------------------------------------------------------------|

| A01          | Nr   | Resolution                                        | PIC16F72           | _          | _          | 8 bits             | bit      | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$         |

|              |      |                                                   | PIC16LF72          | —          | _          | 8 bits             | bit      | VREF = VDD = 2.2V                                                            |

| A02          | Eabs | Total Absolute Er                                 | ror                | _          | _          | < ± 1              | LSb      | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$         |

| A03          | EIL  | Integral Linearity                                | Error              | —          | _          | < ± 1              | LSb      | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$         |

| A04          | Edl  | Differential Linearity Error                      |                    | —          | _          | < ± 1              | LSb      | $\begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$ |

| A05          | Efs  | Full Scale Error                                  |                    | —          | _          | < ± 1              | LSb      | $\begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$ |

| A06          | EOFF | Offset Error                                      |                    | —          | —          | < ± 1              | LSb      | $\begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$ |

| A10          | —    | Monotonicity (Note 3)                             |                    | —          | guaranteed | —                  | —        | $VSS \leq VAIN \leq VREF$                                                    |

| A20          | Vref | Reference Voltage                                 |                    | 2.5<br>2.2 | _          | Vdd+0.3<br>Vdd+0.3 | V<br>V   | -40°C to +85°C<br>0°C to +85°C                                               |

| A25          | VAIN | Analog Input Volt                                 | age                | Vss - 0.3  | _          | VREF + 0.3         | V        |                                                                              |

| A30          | ZAIN | Recommended Impedance of<br>Analog Voltage Source |                    | —          | _          | 10.0               | kΩ       |                                                                              |

| A40          | IAD  | A/D Conversion                                    | PIC16F72           | —          | 180        | —                  | μΑ       | Average current                                                              |

|              |      | Current (VDD)                                     | PIC16LF72          | —          | 90         | —                  | μA       | consumption when A/D<br>is on <b>(Note 1)</b> .                              |

| A50          | IREF | VREF input currer                                 | nt <b>(Note 2)</b> | N/A<br>—   |            | ± 5<br>500         | μΑ<br>μΑ | During VAIN acquisition.<br>During A/D Conversion<br>cycle.                  |

#### TABLE 14-9: A/D CONVERTER CHARACTERISTICS: PIC16F72 (INDUSTRIAL) PIC16LF72 (INDUSTRIAL)

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from the RA3 pin or the VDD pin, whichever is selected as a reference input.

**3:** The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

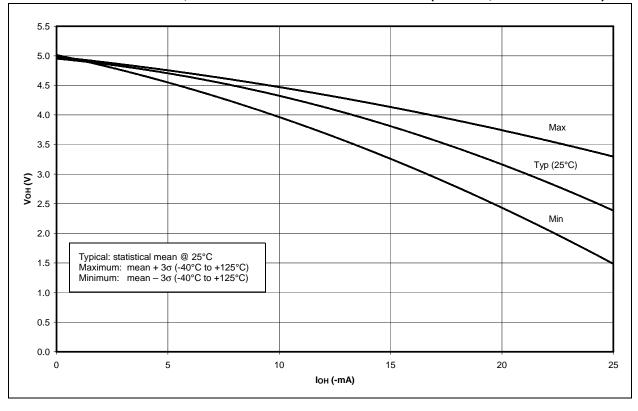

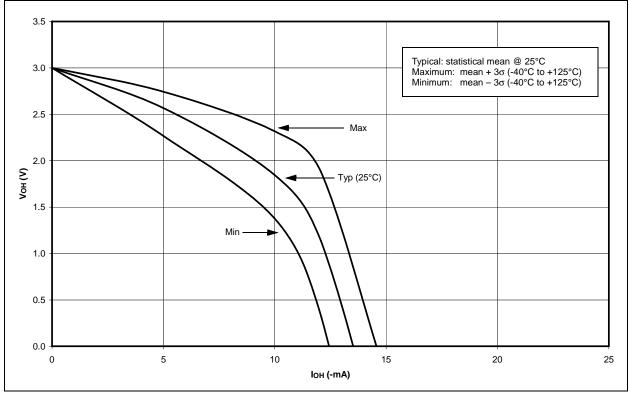

FIGURE 15-15: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD = 5V, -40°C TO +125°C)

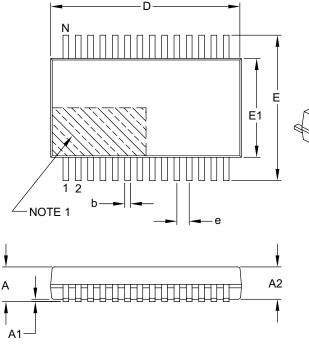

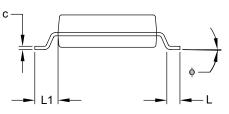

# 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    |          |          | MILLIMETERS |  |  |  |

|--------------------------|----------|----------|----------|-------------|--|--|--|

| Dimension                | n Limits | MIN      | NOM      | MAX         |  |  |  |

| Number of Pins           | Ν        |          | 28       |             |  |  |  |

| Pitch                    | е        |          | 0.65 BSC |             |  |  |  |

| Overall Height           | А        | -        | -        | 2.00        |  |  |  |

| Molded Package Thickness | A2       | 1.65     | 1.75     | 1.85        |  |  |  |

| Standoff                 | A1       | 0.05     | -        | -           |  |  |  |

| Overall Width            | E        | 7.40     | 7.80     | 8.20        |  |  |  |

| Molded Package Width     | E1       | 5.00     | 5.30     | 5.60        |  |  |  |

| Overall Length           | D        | 9.90     | 10.20    | 10.50       |  |  |  |

| Foot Length              | L        | 0.55     | 0.75     | 0.95        |  |  |  |

| Footprint                | L1       | 1.25 REF |          |             |  |  |  |

| Lead Thickness           | с        | 0.09     | -        | 0.25        |  |  |  |

| Foot Angle               | φ        | 0°       | 4°       | 8°          |  |  |  |

| Lead Width               | b        | 0.22     | -        | 0.38        |  |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

# **PIC16F72**

| Oscillator Configuration              | 59, 61     |

|---------------------------------------|------------|

| Crystal Oscillator/Ceramic Resonators | 61         |

| HS                                    | 61, 65     |

| LP                                    | 61, 65     |

| RC                                    | 61, 62, 65 |

| XT                                    | 61, 65     |

| Oscillator, WDT                       | 70         |

# Ρ

| -                              |

|--------------------------------|

| P44                            |

| Package Marking Information117 |

| PCFG0 bit54                    |

| PCFG1 bit                      |

| PCFG2 bit                      |

| PCL Register                   |

| PCLATH Register                |

| PCON Register                  |

| POR bit                        |

| PICDEM 1 Low Cost PIC          |

| Demonstration Board            |

|                                |

| PICDEM 17 Demonstration Board  |

| PICDEM 2 Low Cost PIC16CXX     |

| Demonstration Board83          |

| PICDEM 3 Low Cost PIC16CXXX    |

| Demonstration Board84          |

| PICSTART Plus Entry Level      |

| Development Programmer83       |

| Pin Functions                  |

| MCLR/VPP                       |

| OSC1/CLKI                      |

| OSC2/CLKO                      |

|                                |

| RA0/AN0                        |

| RA1/AN1                        |

| RA2/AN26                       |

| RA3/AN3/VREF6                  |

| RA4/T0CKI                      |

| RA5/AN4/SS6                    |

| RB0/INT6                       |

| RB16                           |

| RB26                           |

| RB3                            |

| RB4                            |

| RB5                            |

| RB6/PGC                        |

|                                |

| RB7/PGD                        |

| RC0/T1OSO/T1CKI                |

| RC1/T10SI6                     |

| RC2/CCP16                      |

| RC3/SCK/SCL6                   |

| RC4/SDI/SDA6                   |

| RC5/SDO6                       |

| RC66                           |

| RC76                           |

| VDD6                           |

| Vss6                           |

| Pinout Descriptions            |

| PIC16F72                       |

| POP                            |

| POP                            |

|                                |

| PORTA                          |

| Associated Registers           |

| Functions22                    |

|                                |

| PORTA Register<br>PORTB                     |       | 9   |

|---------------------------------------------|-------|-----|

| Associated Registers                        |       | 24  |

| Functions                                   |       |     |

| Pull-up Enable (RBPU bit)                   |       | 13  |

| RB0/INT Edge Select (INTEDG bit)            |       | 13  |

| RB0/INT Pin, External                       |       |     |

| RB7:RB4 Interrupt-on-Change Flag (RBIF bit) |       | 14  |

| RB7:RB4 Interrupt-on-Change                 |       | 69  |

| RB7:RB4 Interrupt-on-Change Enable          |       |     |

| (RBIE bit)                                  |       | 69  |

| RB7:RB4 Interrupt-on-Change Flag            |       |     |

| (RBIF bit)                                  | . 14, | 69  |

| PORTB Register                              |       | 9   |

| Associated Registers                        |       | 26  |

| Functions                                   |       | 26  |

| PORTC Register                              |       | 9   |

| Postscaler, WDT                             |       |     |

| Assignment (PSA Bit)                        |       | 13  |

| Rate Select (PS2:PS0 bits)                  |       | 13  |

| Power-down Mode. See SLEEP                  |       |     |

| Power-on Reset (POR) 59, 62, 64             | , 65, | 66  |

| Brown-out Reset (BOR)                       |       | 64  |

| Oscillator Start-up Timer (OST)             | . 59, | 64  |

| POR Status (POR bit)                        |       |     |

| Power Control/Status Register (PCON)        |       | 64  |

| Power-down (PD bit)                         |       |     |

| Power-up Timer (PWRT)                       |       |     |

| Time-out (TO bit)                           |       |     |

| Time-out Sequence                           |       |     |

| PR2 Register                                |       |     |

| Prescaler, Timer0                           |       |     |

| Assignment (PSA bit)                        |       | 13  |

| Rate Select (PS2:PS0 bits)                  |       | 13  |

| PRO MATE II Universal Device Programmer     |       |     |

| Product Identification System               | 1     | 33  |

| Program Counter                             |       |     |

| RESET Conditions                            |       | 65  |

| Program Memory                              |       |     |

| Paging                                      |       | 19  |

| Program Memory Map and Stack                |       | . 7 |

| Program Verification                        |       |     |

| PUSH                                        |       |     |

|                                             |       |     |

# R

| R/W                                   | 44  |

|---------------------------------------|-----|

| R/W bit                               | 49  |

| RBIF bit                              |     |

| Read/Write bit Information, R/W       | 44  |

| Reader Response                       | 132 |

| Reading Program Memory                | 27  |

| PMADR                                 | 27  |

| PMCON1 Register                       | 27  |

| Receive Overflow Indicator bit, SSPOV | 45  |

| Register File Map                     | 8   |

| Registers                                        |            |

|--------------------------------------------------|------------|

| ADCON0 (A/D Control 0)                           |            |

| ADCON1 (A/D Control 1)                           | 54         |

| CCPCON1 (Capture/Compare/PWM Control 1)          | 37         |

| Initialization Conditions (table)                |            |

| INTCON (Interrupt Control)                       |            |

| OPTION                                           |            |

| PCON (Power Control)                             |            |

|                                                  |            |

| PIE1 (Peripheral Interrupt Enable 1)             |            |

| PIR1 (Peripheral Interrupt Flag 1)               |            |

| PMCON1 (Program Memory Control 1)                |            |