Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                     |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20MHz                                                                        |

| Connectivity               | IrDA, SCI                                                                    |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 74                                                                           |

| Program Memory Size        | 128KB (128K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 4K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-BFQFP                                                                    |

| Supplier Device Package    | 100-QFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2144fa20v |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Item                                                                                                                      | Page | Revision (See Manual for Details)                                                                                                                                                                                                     |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 22.4.2 Block Diagram                                                                                                      | 643  | Figure 22.2 amended                                                                                                                                                                                                                   |  |  |  |  |  |

| Figure 22.2 Block<br>Diagram of Flash<br>Memory                                                                           | 643  | Figure 22.2 amended       Internal address bus       Internal data bus (16 bits)       FLMCR1*       Bus interface/controller       Operating mode       Mode pins       EBR1*       Flash memory (128 kbytes/64 kbytes)              |  |  |  |  |  |

| 22.5.3 Erase Block<br>Registers 1 and 2<br>(EBR1, EBR2)                                                                   | 653  | Bit figure amended<br>Read/Write description of bits 7 to 2 (Before) — *2 $\rightarrow$ (After) —                                                                                                                                     |  |  |  |  |  |

| 22.10.1 Programmer<br>Mode Setting                                                                                        | 671  | Note amended<br>In programmer mode, Renesas Technology microcomputer<br>device types with 128-kbyte <sup>*1*3</sup> or 64-kbyte <sup>*2*3</sup> on-chip flash<br>memory<br>Note: 3. Use products other than the A-mask version of the |  |  |  |  |  |

|                                                                                                                           |      | H8S/2148, H8S/2147N, H8S/2144, and H8S/2142                                                                                                                                                                                           |  |  |  |  |  |

| 22.10.4 Memory Read<br>Mode<br>Figure 22.17 Timing<br>Waveforms when<br>Entering Another Mode<br>from Memory Read<br>Mode | 675  | FA17 to FA0<br>We mory read mode<br>CE<br>OE<br>WE<br>FO7 to FO0<br>Data<br>CE<br>CE<br>CE<br>CE<br>CE<br>CE<br>CE<br>CE<br>CE<br>CE                                                                                                  |  |  |  |  |  |

|                     | Pin Name                                |                                         |                                         |                             |  |  |  |  |

|---------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------|--|--|--|--|

| Pin No.             | Expan                                   | ded Modes                               | Single-Chip Modes                       |                             |  |  |  |  |

| FP-100B<br>TFP-100B | Mode 1                                  | Mode 2 (EXPE = 1)<br>Mode 3 (EXPE = 1)  | Mode 2 (EXPE = 0)<br>Mode 3 (EXPE = 0)  | Flash Memory<br>Writer Mode |  |  |  |  |

| 22                  | RD                                      | RD                                      | P93/IOR                                 | WE                          |  |  |  |  |

| 23                  | P92/IRQ0                                | P92/IRQ0                                | P92/IRQ0                                | VSS                         |  |  |  |  |

| 24                  | P91/IRQ1                                | P91/IRQ1                                | P91/IRQ1                                | VCC                         |  |  |  |  |

| 25                  | LWR/P90/IRQ2/<br>ADTRG                  | LWR/P90/IRQ2/<br>ADTRG                  | P90/IRQ2/ADTRG/<br>ECS2                 | VCC                         |  |  |  |  |

| 26                  | P60/FTCI/CIN0/<br>KIN0/TMIX/<br>HFBACKI | P60/FTCI/CIN0/<br>KIN0/TMIX/<br>HFBACKI | P60/FTCI/CIN0/<br>KIN0/TMIX/<br>HFBACKI | NC                          |  |  |  |  |

| 27                  | P61/FTOA/CIN1/<br>KIN1/VSYNCO           | P61/FTOA/CIN1/<br>KIN1/VSYNCO           | P61/FTOA/CIN1/<br>KIN1/VSYNCO           | NC                          |  |  |  |  |

| 28                  | P62/FTIA/CIN2/<br>KIN2/TMIY/<br>VSYNCI  | P62/FTIA/CIN2/<br>KIN2/TMIY/<br>VSYNCI  | P62/FTIA/CIN2/<br>KIN2/TMIY/<br>VSYNCI  | NC                          |  |  |  |  |

| 29                  | P63/FTIB/CIN3/<br>KIN3/VFBACKI          | P63/FTIB/CIN3/<br>KIN3/VFBACKI          | P63/FTIB/CIN3/<br>KIN3/VFBACKI          | NC                          |  |  |  |  |

| 30                  | PA3/CIN11/<br>KIN11/PS2AD               | A19/PA3/CIN11/<br>KIN11/PS2AD           | PA3/CIN11/<br>KIN11/PS2AD               | NC                          |  |  |  |  |

| 31                  | PA2/CIN10/<br>KIN10/PS2AC               | A18/PA2/CIN10/<br>KIN10/PS2AC           | PA2/CIN10/<br>KIN10/PS2AC               | NC                          |  |  |  |  |

| 32                  | P64/FTIC/CIN4/<br>KIN4/CLAMPO           | P64/FTIC/CIN4/<br>KIN4/CLAMPO           | P64/FTIC/CIN4/<br>KIN4/CLAMPO           | NC                          |  |  |  |  |

| 33                  | P65/FTID/CIN5/<br>KIN5                  | P65/FTID/CIN5/<br>KIN5                  | P65/FTID/CIN5/<br>KIN5                  | NC                          |  |  |  |  |

| 34                  | P66/FTOB/CIN6/<br>KIN6/IRQ6             | P66/FTOB/CIN6/<br>KIN6/IRQ6             | P66/FTOB/CIN6/<br>KIN6/IRQ6             | NC                          |  |  |  |  |

| 35                  | P67/TMOX/CIN7/<br>KIN7/IRQ7             | P67/TMOX/CIN7/<br>KIN7/IRQ7             | P67/TMOX/CIN7/<br>KIN7/IRQ7             | VSS                         |  |  |  |  |

| 36                  | AVref                                   | AVref                                   | AVref                                   | VCC                         |  |  |  |  |

| 37                  | AVCC                                    | AVCC                                    | AVCC                                    | VCC                         |  |  |  |  |

| 38                  | P70/AN0                                 | P70/AN0                                 | P70/AN0                                 | NC                          |  |  |  |  |

| 39                  | P71/AN1                                 | P71/AN1                                 | P71/AN1                                 | NC                          |  |  |  |  |

| 40                  | P72/AN2                                 | P72/AN2                                 | P72/AN2                                 | NC                          |  |  |  |  |

| 41                  | P73/AN3                                 | P73/AN3                                 | P73/AN3                                 | NC                          |  |  |  |  |

#### 2.8.6 Power-Down State

The power-down state includes both modes in which the CPU stops operating and modes in which the CPU does not stop. There are five modes in which the CPU stops operating: sleep mode, software standby mode, hardware standby mode, subsleep mode, and watch mode. There are also three other power-down modes: medium-speed mode, module stop mode, and subactive mode. In medium-speed mode, the CPU and other bus masters operate on a medium-speed clock. Module stop mode permits halting of the operation of individual modules, other than the CPU. Subactive mode, subsleep mode, and watch mode are power-down modes that use subclock input. For details, refer to section 25, Power-Down State.

#### **Sleep Mode**

A transition to sleep mode is made if the SLEEP instruction is executed while the software standby bit (SSBY) in the standby control register (SBYCR) and the LSON bit in the low-power control register (LPWRCR) are both cleared to 0. In sleep mode, CPU operations stop immediately after execution of the SLEEP instruction. The contents of CPU registers are retained.

### Software Standby Mode

A transition to software standby mode is made if the SLEEP instruction is executed while the SSBY bit in SBYCR is set to 1 and the LSON bit in LPWRCR and the PSS bit in the WDT1 timer control/status register (TCSR) are both cleared to 0. In software standby mode, the CPU and clock halt and all MCU operations stop. As long as a specified voltage is supplied, the contents of CPU registers and on-chip RAM are retained. The I/O ports also remain in their existing states.

### Hardware Standby Mode

A transition to hardware standby mode is made when the STBY pin goes low. In hardware standby mode, the CPU and clock halt and all MCU operations stop. The on-chip supporting modules are reset, but as long as a specified voltage is supplied, on-chip RAM contents are retained.

# Renesas

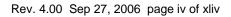

Figure 3.1 H8S/2148 (Except for F-ZTAT A-Mask Version) and H8S/2144 Memory Map in Each Operating Mode (cont)

# 5.3 Interrupt Sources

Interrupt sources comprise external interrupts (NMI and IRQ7 to IRQ0) and internal interrupts.

## 5.3.1 External Interrupts

There are nine external interrupt sources from 25 input pins (23 actual pins): NMI,  $\overline{IRQ7}$  to  $\overline{IRQ0}$ , and  $\overline{KIN15}$  to  $\overline{KIN0}$ . KIN15 to KIN8 share the IRQ7 interrupt source, and KIN7 to KIN0 share the IRQ6 interrupt source. Of these, NMI, IRQ7, IRQ6, and IRQ2 to IRQ0 can be used to restore the H8S/2148 Group or H8S/2144 Group chip from software standby mode.

## **NMI Interrupt**

NMI is the highest-priority interrupt, and is always accepted by the CPU regardless of the interrupt control mode and the status of the CPU interrupt mask bits. The NMIEG bit in SYSCR can be used to select whether an interrupt is requested at a rising edge or a falling edge on the NMI pin.

The vector number for NMI interrupt exception handling is 7.

## **IRQ7 to IRQ0 Interrupts**

Interrupts IRQ7 to IRQ0 are requested by an input signal at pins  $\overline{IRQ7}$  to  $\overline{IRQ0}$ . Interrupts IRQ7 to IRQ0 have the following features:

- Using ISCR, it is possible to select whether an interrupt is generated by a low level, falling edge, rising edge, or both edges, at pins IRQ7 to IRQ0.

- Enabling or disabling of interrupt requests IRQ7 to IRQ0 can be selected with IER.

- The interrupt control level can be set with ICR.

- The status of interrupt requests IRQ7 to IRQ0 is indicated in ISR. ISR flags can be cleared to 0 by software.

A block diagram of interrupts IRQ7 to IRQ0 is shown in figure 5.3.

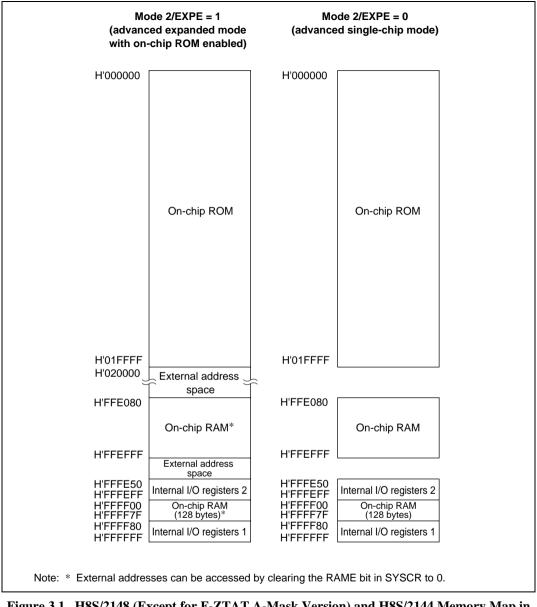

Figure 5.7 Block Diagram of Interrupt Control Operation

### **Interrupt Acceptance Control and 3-Level Control**

In interrupt control modes 0 and 1, interrupt acceptance control and 3-level mask control is performed by means of the I and UI bits in CCR, and ICR (control level).

Table 5.6 shows the interrupts selected in each interrupt control mode.

| Pin         | Selection Method and Pin Functions                                                                                               |                                              |                        |                    |                  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------|--------------------|------------------|--|--|--|

| P94/HWR/IOW | The pin function is switched as shown below according to the combination of operating mode, bit HI12E in SYSCR2, and bit P94DDR. |                                              |                        |                    |                  |  |  |  |

|             | Operating mode                                                                                                                   | Modes 1, 2, 3<br>(EXPE = 1)                  | Мо                     | = 0)               |                  |  |  |  |

|             | HI12E                                                                                                                            |                                              |                        | 0                  | 1                |  |  |  |

|             | P94DDR                                                                                                                           | _                                            | 0                      | 1                  |                  |  |  |  |

|             | Pin function                                                                                                                     | HWR<br>output pin                            | P94<br>input pin       | P94<br>output pin  | IOW<br>input pin |  |  |  |

| P93/RD/IOR  |                                                                                                                                  | on is switched a<br>de, bit HI12E in \$      |                        | according to the o | combination of   |  |  |  |

|             | Operating mode                                                                                                                   | Modes 1, 2, 3<br>(EXPE = 1) Modes 2, 3 (EXPE |                        | des 2, 3 (EXPE :   | = 0)             |  |  |  |

|             | HI12E                                                                                                                            | —                                            |                        | 0                  | 1                |  |  |  |

|             | P93DDR                                                                                                                           | —                                            | 0                      | 0 1                |                  |  |  |  |

|             | Pin function                                                                                                                     | RD output pin                                | P93 input pin          | P93 output pin     | IOR input pin    |  |  |  |

| P92/IRQ0    | P92DDR                                                                                                                           | (                                            | )                      | 1                  |                  |  |  |  |

|             | Pin function                                                                                                                     | P92 in                                       | put pin P92 output pin |                    |                  |  |  |  |

|             |                                                                                                                                  | IRQ0 input pin                               |                        |                    |                  |  |  |  |

|             | When bit IRQ0E in IER is set to 1, this pin is used as the $\overline{IRQ0}$ input pin.                                          |                                              |                        |                    |                  |  |  |  |

| P91/IRQ1    | P91DDR                                                                                                                           | (                                            | )                      | 1                  |                  |  |  |  |

|             | Pin function                                                                                                                     | P91 input pin                                |                        | P91 output pin     |                  |  |  |  |

|             |                                                                                                                                  | IRQ1 input pin                               |                        |                    |                  |  |  |  |

|             | When bit IRQ                                                                                                                     | 1E in IER is set                             | to 1, this pin is u    | sed as the IRQ1    | input pin.       |  |  |  |

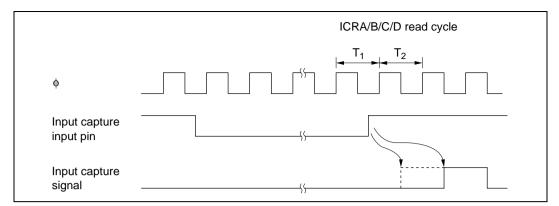

Figure 11.8 Input Capture Signal Timing (Input Capture Input when ICRA/B/C/D Is Read)

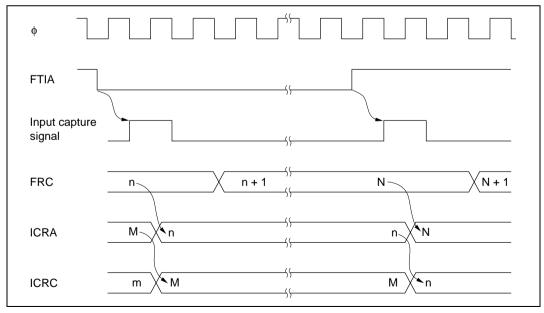

### **Buffered Input Capture Input Timing**

ICRC and ICRD can operate as buffers for ICRA and ICRB.

Figure 11.9 shows how input capture operates when ICRA and ICRC are used in buffer mode and IEDGA and IEDGC are set to different values (IEDGA = 0 and IEDGC = 1, or IEDG A = 1 and IEDGC = 0), so that input capture is performed on both the rising and falling edges of FTIA.

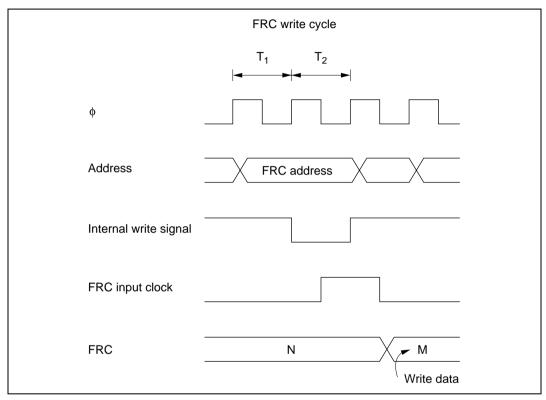

### **Contention between FRC Write and Increment**

If an FRC increment pulse is generated during the state after an FRC write cycle, the write takes priority and FRC is not incremented.

Figure 11.19 shows this type of contention.

Figure 11.19 FRC Write-Increment Contention

### **Contention between OCR Write and Compare-Match**

If a compare-match occurs during the state after an OCRA or OCRB write cycle, the write takes priority and the compare-match signal is inhibited.

Figure 11.20 shows this type of contention.

### Clock

Either an internal clock generated by the built-in baud rate generator or an external clock input at the SCK pin can be selected as the SCI's serial clock, according to the setting of the  $C/\overline{A}$  bit in SMR and the CKE1 and CKE0 bits in SCR. For details of SCI clock source selection, see table 15.9.

When an external clock is input at the SCK pin, the clock frequency should be 16 times the bit rate used.

When the SCI is operated on an internal clock, the clock can be output from the SCK pin. The frequency of the clock output in this case is equal to the bit rate, and the phase is such that the rising edge of the clock is at the center of each transmit data bit, as shown in figure 15.3.

Figure 15.3 Relation between Output Clock and Transfer Data Phase (Asynchronous Mode)

### **Data Transfer Operations**

**SCI Initialization (Asynchronous Mode):** Before transmitting and receiving data, first clear the TE and RE bits in SCR to 0, then initialize the SCI as described below.

When the operating mode, transfer format, etc., is changed, the TE and RE bits must be cleared to 0 before making the change using the following procedure. When the TE bit is cleared to 0, the TDRE flag is set to 1 and TSR is initialized. Note that clearing the RE bit to 0 does not change the contents of the RDRF, PER, FER, and ORER flags, or the contents of RDR.

When an external clock is used the clock should not be stopped during operation, including initialization, since operation is uncertain.

# Renesas

ICDR is an 8-bit readable/writable register that is used as a transmit data register when transmitting and a receive data register when receiving. ICDR is divided internally into a shift register (ICDRS), receive buffer (ICDRR), and transmit buffer (ICDRT). ICDRS cannot be read or written by the CPU, ICDRR is read-only, and ICDRT is write-only. Data transfers among the three registers are performed automatically in coordination with changes in the bus state, and affect the status of internal flags such as TDRE and RDRF.

If IIC is in transmit mode and the next data is in ICDRT (the TDRE flag is 0) following transmission/reception of one frame of data using ICDRS, data is transferred automatically from ICDRT to ICDRS. If IIC is in receive mode and no previous data remains in ICDRR (the RDRF flag is 0) following transmission/reception of one frame of data using ICDRS, data is transferred automatically from ICDRS to ICDRR.

If the number of bits in a frame, excluding the acknowledge bit, is less than 8, transmit data and receive data are stored differently. Transmit data should be written justified toward the MSB side when MLS = 0, and toward the LSB side when MLS = 1. Receive data bits read from the LSB side should be treated as valid when MLS = 0, and bits read from the MSB side when MLS = 1.

ICDR is assigned to the same address as SARX, and can be written and read only when the ICE bit is set to 1 in ICCR.

The value of ICDR is undefined after a reset.

The TDRE and RDRF flags are set and cleared under the conditions shown below. Setting the TDRE and RDRF flags affects the status of the interrupt flags.

## Renesas

Bit 7—Error Stop Condition Detection Flag (ESTP): Indicates that a stop condition has been detected during frame transfer in  $I^2C$  bus format slave mode.

#### Bit 7

| ESTP | Description                                             |                 |

|------|---------------------------------------------------------|-----------------|

| 0    | No error stop condition                                 | (Initial value) |

|      | [Clearing conditions]                                   |                 |

|      | 1. When 0 is written in ESTP after reading ESTP = 1     |                 |

|      | 2. When the IRIC flag is cleared to 0                   |                 |

| 1    | In I <sup>2</sup> C bus format slave mode               |                 |

|      | Error stop condition detected                           |                 |

|      | [Setting condition]                                     |                 |

|      | When a stop condition is detected during frame transfer |                 |

|      | In other modes                                          |                 |

|      | No meaning                                              |                 |

**Bit 6—Normal Stop Condition Detection Flag (STOP):** Indicates that a stop condition has been detected after completion of frame transfer in  $I^2C$  bus format slave mode.

#### Bit 6

| STOP | Description                                                          |

|------|----------------------------------------------------------------------|

| 0    | No normal stop condition (Initial value)                             |

|      | [Clearing conditions]                                                |

|      | 1. When 0 is written in STOP after reading STOP = 1                  |

|      | 2. When the IRIC flag is cleared to 0                                |

| 1    | In I <sup>2</sup> C bus format slave mode                            |

|      | Normal stop condition detected                                       |

|      | [Setting condition]                                                  |

|      | When a stop condition is detected after completion of frame transfer |

|      | In other modes                                                       |

|      | No meaning                                                           |

**Bit 5—I<sup>2</sup>C Bus Interface Continuous Transmission/Reception Interrupt Request Flag** (**IRTR**): Indicates that the I<sup>2</sup>C bus interface has issued an interrupt request to the CPU, and the source is completion of reception/transmission of one frame in continuous transmission/reception for which DTC activation is possible. When the IRTR flag is set to 1, the IRIC flag is also set to 1 at the same time.

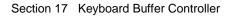

Figure 17.4 Receive Timing

## 17.3.2 Transmit Operation

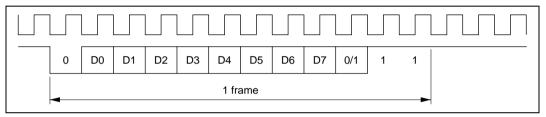

In a transmit operation, KCLK (clock) is an output on the keyboard side, and KD (data) is an output on the H8S/2148 Group and H8S/2147N chip (system) side. KD outputs a start bit, 8 data bits (LSB-first), an odd parity bit, and a stop bit, in that order. The KD value is valid when KCLK is high. A sample transmit processing flowchart is shown in figure 17.5, and the transmit timing in figure 17.6.

# 26.2 Electrical Characteristics of H8S/2148 F-ZTAT

### 26.2.1 Absolute Maximum Ratings

Table 26.2 lists the absolute maximum ratings.

### Table 26.2 Absolute Maximum Ratings

| Item                                                              | Symbol            | Value                                                                 | Unit |

|-------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------|------|

| Power supply voltage*                                             | V <sub>cc</sub>   | -0.3 to +7.0                                                          | V    |

| Input/output buffer power supply<br>(power supply for the port A) | V <sub>cc</sub> B | -0.3 to +7.0                                                          | V    |

| Input voltage (except ports 6, 7, and A)                          | $V_{in}$          | –0.3 to $V_{cc}$ +0.3                                                 | V    |

| Input voltage (CIN input not selected for port 6)                 | $V_{in}$          | –0.3 to $V_{cc}$ +0.3                                                 | V    |

| Input voltage (CIN input not selected for port A)                 | $V_{in}$          | -0.3 to V <sub>cc</sub> B +0.3                                        | V    |

| Input voltage (CIN input selected for port 6)                     | $V_{in}$          | –0.3 V to lower of voltages $V_{\rm cc}$ +0.3 and AV_{\rm cc} +0.3    | V    |

| Input voltage (CIN input selected for port A)                     | $V_{in}$          | –0.3 V to lower of voltages $V_{\rm cc}B$ +0.3 and $AV_{\rm cc}$ +0.3 | V    |

| Input voltage (port 7)                                            | V <sub>in</sub>   | –0.3 to AV <sub>cc</sub> +0.3                                         | V    |

| Reference supply voltage                                          | $AV_{ref}$        | –0.3 to AV <sub>cc</sub> +0.3                                         | V    |

| Analog power supply voltage                                       | $AV_{cc}$         | -0.3 to +7.0                                                          | V    |

| Analog input voltage                                              | V <sub>AN</sub>   | –0.3 to AV <sub>cc</sub> +0.3                                         | V    |

| Operating temperature                                             | T <sub>opr</sub>  | Regular specifications: -20 to +75                                    | °C   |

|                                                                   |                   | Wide-range specifications: -40 to +85                                 | °C   |

| Operating temperature (flash                                      | T <sub>opr</sub>  | Regular specifications: 0 to +75                                      | °C   |

| memory programming/erasing)                                       |                   | Wide-range specifications: 0 to +85                                   | °C   |

| Storage temperature                                               | T <sub>stg</sub>  | –55 to +125                                                           | °C   |

|                                                                   |                   |                                                                       |      |

Caution: Permanent damage to the chip may result if absolute maximum ratings are exceeded. Note: \* Power supply voltage for VCC1 and VCC2 pins.

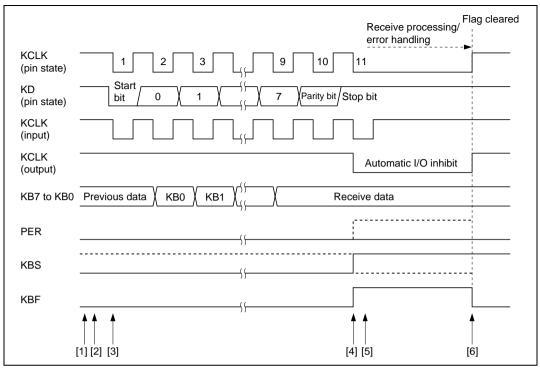

Figure 26.1 Darlington Pair Drive Circuit (Example)

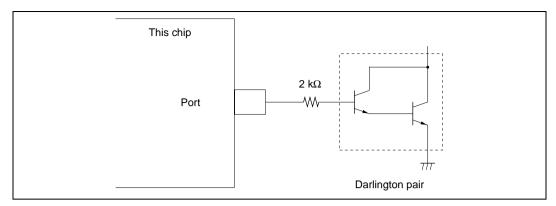

Figure 26.2 LED Drive Circuit (Example)

| ltem       |                      | Symbol                     | Value                                                                                                               | Unit |

|------------|----------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------|------|

|            | temperature (flash   | T <sub>opr</sub>           | Regular specifications: -20 to +75                                                                                  | °C   |

| memory p   | programming/erasing) |                            | Wide-range specifications: -40 to +85                                                                               | °C   |

| Storage te | emperature           | $T_{_{stg}}$               | –55 to +125                                                                                                         | °C   |

| Caution:   | exceeded.            | than 7.0 V to              | o may result if absolute maximum ratings are<br>o any of the pins of the 5- or 4-V version or<br>of the 3-V version |      |

|            |                      | ximum rating<br>C1 and VCL | g of $V_{_{\rm CL}}$ in the low-power version (3-V versio pins are connected to the $V_{_{\rm CC}}$ power supply    |      |

Never apply power supply voltage to the VCL pin in the 5- or 4-V version. Always connect an external capacitor between the VCL pin and ground for internal voltage stabilization.

### 26.3.2 DC Characteristics

Table 26.17 lists the DC characteristics. Permitted output current values and bus drive characteristics are shown in tables 26.18 and 26.19, respectively.

### Table 26.17 DC Characteristics (1)

Conditions:  $V_{cc} = 5.0 V \pm 10\%$ ,  $V_{cc}B = 5.0 V \pm 10\%$ ,  $AV_{cc}^{*1} = 5.0 V \pm 10\%$ ,  $AV_{ref}^{*1} = 4.5 V$  to  $AV_{cc}$ ,  $V_{ss} = AV_{ss}^{*1} = 0 V$ ,  $T_a = -20$  to  $+75^{\circ}C$  (regular specifications),  $T_a = -40$  to  $+85^{\circ}C$  (wide-range specifications)

| ltem                  |                                                                              |     | Symbol                            | Min                  | Тур | Мах                                          | Unit | Test<br>Conditions |

|-----------------------|------------------------------------------------------------------------------|-----|-----------------------------------|----------------------|-----|----------------------------------------------|------|--------------------|

|                       | P67 to<br>P60(KWUL =<br>$00)^{*2*6}$ ,<br>KIN15 to<br>KIN8 <sup>*7*8</sup> , | (1) | V <sub>T</sub> <sup>-</sup>       | 1.0                  | _   |                                              | V    |                    |

| voltage               |                                                                              |     | $V_{T}^{+}$                       | _                    | —   | $V_{cc} \times 0.7$<br>$V_{cc} B \times 0.7$ |      |                    |

|                       | $\overline{\text{IRQ2}}$ to $\overline{\text{IRQ0}}^{*3}$ ,<br>IRQ5 to IRQ3  |     | $V_{T}^{+} - V_{T}^{-}$           | 0.4                  | —   | _                                            | _    |                    |

| Schmitt               | P67 to P60                                                                   | -   | V <sub>T</sub>                    | $V_{cc} 	imes 0.3$   |     | _                                            | V    |                    |

| trigger input voltage | (KWUL = 01)                                                                  |     | $V_{T}^{+}$                       | _                    |     | $V_{cc} 	imes 0.7$                           | =    |                    |

| (in level             |                                                                              | _   | $V_{_{T}}^{^{+}}-V_{_{T}}^{^{-}}$ | $V_{cc} 	imes 0.05$  | —   |                                              | _    |                    |

| switching)*6          | P67 to P60                                                                   |     | $V_{T}^{-}$                       | $V_{cc} 	imes 0.4$   |     | _                                            | _    |                    |

|                       | (KWUL = 10)                                                                  |     | $V_{T}^{+}$                       | _                    |     | $V_{cc} 	imes 0.8$                           |      |                    |

|                       |                                                                              | _   | $V_{_{T}}^{^{+}}-V_{_{T}}^{^{-}}$ | $V_{cc} 	imes 0.03$  |     |                                              | _    |                    |

|                       | P67 to P60<br>(KWUL = 11)                                                    |     | $V_{T}^{-}$                       | $V_{cc} 	imes 0.45$  |     | _                                            | _    |                    |

|                       |                                                                              |     | $V_{T}^{+}$                       | _                    |     | $V_{cc} 	imes 0.9$                           | _    |                    |

|                       |                                                                              |     | $V_{T}^{+}-V_{T}^{-}$             | 0.05                 | —   | _                                            |      |                    |

| Input high<br>voltage | RES, STBY,<br>NMI, MD1,<br>MD0                                               | (2) | V <sub>IH</sub>                   | V <sub>cc</sub> –0.7 | _   | V <sub>cc</sub> +0.3                         | V    |                    |

|                       | EXTAL                                                                        | -   |                                   | $V_{cc} 	imes 0.7$   |     | V <sub>cc</sub> +0.3                         | _    |                    |

|                       | PA7 to PA0*7                                                                 | -   |                                   | $V_{cc}B \times 0.7$ |     | V <sub>cc</sub> B +0.3                       | -    |                    |

|                       | Port 7                                                                       |     |                                   | 2.0                  | _   | AV <sub>cc</sub> +0.3                        | =    |                    |

|                       | Input pins except<br>(1) and (2)<br>above                                    |     | _                                 | 2.0                  |     | V <sub>cc</sub> +0.3                         | _    |                    |

| IER—IRQ Enable Register |       |                          |       |            | H'FFC2      | 2     | Interrup | t Controller |

|-------------------------|-------|--------------------------|-------|------------|-------------|-------|----------|--------------|

| Bit                     | 7     | 6                        | 5     | 4          | 3           | 2     | 1        | 0            |

|                         | IRQ7E | IRQ6E                    | IRQ5E | IRQ4E      | IRQ3E       | IRQ2E | IRQ1E    | IRQ0E        |

| Initial value           | 0     | 0                        | 0     | 0          | 0           | 0     | 0        | 0            |

| Read/Write              | R/W   | R/W                      | R/W   | R/W        | R/W         | R/W   | R/W      | R/W          |

|                         |       |                          |       |            |             |       |          |              |

|                         |       |                          | IRC   | 27 to IRQ0 | enable      |       |          |              |

|                         |       |                          | 0     | IRQn int   | errupt disa | abled |          |              |

|                         |       | 1 IRQn interrupt enabled |       |            |             |       |          |              |

| (n = 7 to 0)            |       |                          |       |            |             |       |          |              |

contents match TCNT value