Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                            |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                       |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 20MHz                                                                          |

| Connectivity               | Host Interface, I <sup>2</sup> C, IrDA, SCI                                    |

| Peripherals                | POR, PWM, WDT                                                                  |

| Number of I/O              | 74                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                      |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                            |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2148ate20iv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Item                                                                         | Page | Revision (See Manual for Details)                                                                                                    |

|------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------|

| B.3 Functions                                                                | 1077 | TICRR—H'FFF2 TMRX                                                                                                                    |

|                                                                              |      | TICRF—H'FFF3 TMRX                                                                                                                    |

|                                                                              |      | Figure amended                                                                                                                       |

|                                                                              |      | (Before) Stores TCNT value at fall of external trigger input $\rightarrow$ (After) Stores TCNT value at fall of external reset input |

|                                                                              | 1080 | STR1—H'FFF6 HIF                                                                                                                      |

|                                                                              |      | STR2—H'FFFE HIF                                                                                                                      |

|                                                                              |      | Slave R/W description amended                                                                                                        |

|                                                                              |      | Bit 0 (Before) $R \rightarrow$ (After) $R/(W)$                                                                                       |

| C.2 Port 2 Block<br>Diagrams<br>Figure C.4 Port 2 Block<br>Diagram (Pin P27) | 1089 | Figure C.4 amended                                                                                                                   |

| Appendix F Product<br>Code Lineup                                            | 1128 | Package code in table F.1 amended                                                                                                    |

| Table F.1 H8S/2148<br>Group and H8S/2144<br>Group Product Code<br>Lineup     |      | HD64F2144ATE20 (Before) FP-100B $\rightarrow$ (After) TFP-100B<br>HD64F2144AVFA10 (Before) TFP-100B $\rightarrow$ (After) FP-100B    |

| Appendix G Package<br>Dimensions                                             | 1129 | Figure G.1 replaced                                                                                                                  |

| Figure G.1 Package<br>Dimensions (FP-100B)                                   |      |                                                                                                                                      |

| Figure G.2 Package<br>Dimensions (TFP-100B)                                  | 1130 | Figure G.2 replaced                                                                                                                  |

Rev. 4.00 Sep 27, 2006 page xxiv of xliv

| Туре                     | Instruction  | Size <sup>*1</sup> | Function                                                                                                                                                                                                                                                                                                              |

|--------------------------|--------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arithmetic<br>operations | ADD<br>SUB   | B/W/L              | Rd $\pm$ Rs $\rightarrow$ Rd, Rd $\pm$ #IMM $\rightarrow$ Rd<br>Performs addition or subtraction on data in two general<br>registers, or on immediate data and data in a general<br>register. (Immediate byte data cannot be subtracted<br>from byte data in a general register. Use the SUBX or<br>ADD instruction.) |

|                          | ADDX<br>SUBX | В                  | $Rd \pm Rs \pm C \rightarrow Rd$ , $Rd \pm \#IMM \pm C \rightarrow Rd$<br>Performs addition or subtraction with carry on byte data<br>in two general registers, or on immediate data and data<br>in a general register.                                                                                               |

|                          | INC<br>DEC   | B/W/L              | $Rd \pm 1 \rightarrow Rd$ , $Rd \pm 2 \rightarrow Rd$<br>Increments or decrements a general register by 1 or 2.<br>(Byte operands can be incremented or decremented by<br>1 only.)                                                                                                                                    |

|                          | ADDS<br>SUBS | L                  | $Rd \pm 1 \rightarrow Rd$ , $Rd \pm 2 \rightarrow Rd$ , $Rd \pm 4 \rightarrow Rd$<br>Adds or subtracts the value 1, 2, or 4 to or from data in a 32-bit register.                                                                                                                                                     |

|                          | DAA<br>DAS   | В                  | Rd decimal adjust $\rightarrow$ Rd<br>Decimal-adjusts an addition or subtraction result in a<br>general register by referring to the CCR to produce 4-bit<br>BCD data.                                                                                                                                                |

|                          | MULXU        | B/W                | $Rd \times Rs \rightarrow Rd$<br>Performs unsigned multiplication on data in two general<br>registers: either 8 bits $\times$ 8 bits $\rightarrow$ 16 bits or 16 bits $\times$<br>16 bits $\rightarrow$ 32 bits.                                                                                                      |

|                          | MULXS        | B/W                | $Rd \times Rs \rightarrow Rd$<br>Performs signed multiplication on data in two general<br>registers: either 8 bits $\times$ 8 bits $\rightarrow$ 16 bits or 16 bits $\times$<br>16 bits $\rightarrow$ 32 bits.                                                                                                        |

|                          | DIVXU        | B/W                | Rd ÷ Rs → Rd<br>Performs unsigned division on data in two general<br>registers: either 16 bits ÷ 8 bits → 8-bit quotient and 8-bit<br>remainder or 32 bits ÷ 16 bits → 16-bit quotient and 16-<br>bit remainder.                                                                                                      |

## 2.10 Usage Note

#### 2.10.1 TAS Instruction

Only register ER0, ER1, ER4, or ER5 should be used when using the TAS instruction. The TAS instruction is not generated by the Renesas H8S and H8/300 series C/C++ compilers. If the TAS instruction is used as a user-defined intrinsic function, ensure that only register ER0, ER1, ER4, or ER5 is used.

#### 2.10.2 STM/LDM Instruction

ER7 is not used as the register that can be saved (STM)/restored (LDM) when using STM/LDM instruction, because ER7 is the stack pointer. Two, three, or four registers can be saved/restored by one STM/LDM instruction. The following ranges can be specified in the register list.

Two registers: ER0—ER1, ER2—ER3, or ER4—ER5 Three registers: ER0—ER2, or ER4—ER6 Four registers: ER0—ER3

The STM/LDM instruction including ER7 is not generated by the Renesas H8S and H8/300 series C/C++compilers.

#### 5.2.3 IRQ Enable Register (IER)

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

|               | IRQ7E | IRQ6E | IRQ5E | IRQ4E | IRQ3E | IRQ2E | IRQ1E | IRQ0E |

| Initial value | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Read/Write    | R/W   |

IER is an 8-bit readable/writable register that controls enabling and disabling of interrupt requests IRQ7 to IRQ0.

IER is initialized to H'00 by a reset and in hardware standby mode.

**Bits 7 to 0—IRQ7 to IRQ0 Enable (IRQ7E to IRQ0E):** These bits select whether IRQ7 to IRQ0 are enabled or disabled.

#### Bit n

| IRQnE   | Description             |                 |

|---------|-------------------------|-----------------|

| 0       | IRQn interrupt disabled | (Initial value) |

| 1       | IRQn interrupt enabled  |                 |

| Note: n | = 7 to 0                |                 |

#### 5.2.4 IRQ Sense Control Registers H and L (ISCRH, ISCRL)

• ISCRH

| Bit           | 15             | 14      | 13      | 12      | 11      | 10      | 9       | 8       |

|---------------|----------------|---------|---------|---------|---------|---------|---------|---------|

|               | IRQ7SCB        | IRQ7SCA | IRQ6SCB | IRQ6SCA | IRQ5SCB | IRQ5SCA | IRQ4SCB | IRQ4SCA |

| Initial value | 0              | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| Read/Write    | R/W            | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

| ISCRL         |                |         |         |         |         |         |         |         |

| Bit           | 7              | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|               | <b>IRQ3SCB</b> | IRQ3SCA | IRQ2SCB | IRQ2SCA | IRQ1SCB | IRQ1SCA | IRQ0SCB | IRQ0SCA |

| Initial value | 0              | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| Read/Write    | R/W            | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

|        |                  |                                                                                                                                                                                                                                                                               | Expar                                                                                                                                            | nded Modes                                                                                                                                                                                                                       | Single-Chip Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port   | Description      | Pins                                                                                                                                                                                                                                                                          | Mode 1                                                                                                                                           | Mode 2, Mode 3<br>(EXPE = 1)                                                                                                                                                                                                     | Mode 2, Mode 3<br>(EXPE = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Port 4 | • 8-bit I/O port | P47/PWX1<br>P46/PWX0<br>P45/TMRI1/<br>HIRQ12/CSYNCI<br>P44/TMO1/<br>HIRQ1/HSYNCO<br>P43/TMCI1/<br>HIRQ11/HSYNCI<br>P42/TMRI0/<br>SCK2/SDA1<br>P41/TMO0/<br>RxD2/IrRxD<br>P40/TMCI0/<br>TxD2/IrTxD                                                                             | PWM timer out,<br>8-bit timer 0 an<br>(TMCI0, TMRI0,<br>TMRI1, TMO1)<br>input/output (H3<br>HSYNCI), SCI2<br>RxD2, SCK2), I<br>input/output (IrT | hotioning as 14-bit<br>put (PWX1, PWX0),<br>d 1 input/output<br>0, TMO0, TMCI1,<br>, timer connection<br>SYNCO, CSYNCI,<br>2 input/output (TxD2,<br>IrDA interface<br>FxD, IrRxD), and I <sup>2</sup> C<br>(option) input/output | I/O port also functioning as<br>14-bit PWM timer output<br>(PWX1, PWX0), 8-bit timer<br>0 and 1 input/output<br>(TMCI0, TMRI0, TMO0,<br>TMCI1, TMRI1, TMO1),<br>timer connection<br>input/output (HSYNCO,<br>CSYNCI, HSYNCI), host<br>interface host CPU<br>interrupt request output<br>(HIRQ12, HIRQ1,<br>HIRQ11), SCI2 input/<br>output (TxD2, RxD2,<br>SCK2), IrDA interface<br>input/output (IrTxD, IrRxD),<br>and I <sup>2</sup> C bus interface 1<br>(option) input/output<br>(SDA1) |

| Port 5 | • 3-bit I/O port | P52/SCK0/SCL0<br>P51/RxD0<br>P50/TxD0                                                                                                                                                                                                                                         |                                                                                                                                                  |                                                                                                                                                                                                                                  | t/output (TxD0, RxD0,<br>) input/output (SCL0)                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Port 6 | • 8-bit I/O port | P67/IRQ7/TMOX/<br>KIN7/CIN7<br>P66/IRQ6/FTOB/<br>KIN6/CIN6<br>P65/FTID/KIN5/<br>CIN5<br>P64/FTIC/KIN4/<br>CIN4/CLAMPO<br>P63/FTIB/KIN3/<br>CIN3/VFBACKI<br>P62/FTIA/TMIY/<br>KIN2/CIN2/<br>VSYNCI<br>P61/FTOA/KIN1/<br>CIN1/VSYNCO<br>P60/FTCI/TMIX/<br>KIN0/CIN0/<br>HFBACKI | FRT input/outp<br>8-bit timer X an<br>connection inpu<br>VSYNCO, HFB                                                                             | ut (FTCĬ, FTOA, FTIA<br>d Y input/output (TMC<br>ut/output (CLAMPO, V                                                                                                                                                            | errupt input (KIN7 to KIN0),                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         |       | TCR   |       | ST    | CR    |                                                                 |

|---------|-------|-------|-------|-------|-------|-----------------------------------------------------------------|

|         | Bit 2 | Bit 1 | Bit 0 | Bit 1 | Bit 0 |                                                                 |

| Channel | CKS2  | CKS1  | CKS0  | ICKS1 | ICKS0 | Description                                                     |

| Х       | 0     | 0     | 0     | _     | _     | Clock input disabled (Initial value)                            |

|         | 0     | 0     | 1     | _     |       | Counted on $\phi$ internal clock source                         |

|         | 0     | 1     | 0     | _     |       | $\phi/2$ internal clock source, counted on the falling edge     |

|         | 0     | 1     | 1     | —     |       | $\phi\!/\!4$ internal clock source, counted on the falling edge |

|         | 1     | 0     | 0     | _     |       | Clock input disabled                                            |

| Y       | 0     | 0     | 0     | _     | _     | Clock input disabled (Initial value)                            |

|         | 0     | 0     | 1     | —     | —     | $\phi/4$ internal clock source, counted on the falling edge     |

|         | 0     | 1     | 0     | _     | _     | $\phi/256$ internal clock source, counted on the falling edge   |

|         | 0     | 1     | 1     | —     | —     | $\phi/2048$ internal clock source, counted on the falling edge  |

|         | 1     | 0     | 0     | —     | —     | Clock input disabled                                            |

| Common  | 1     | 0     | 1     | _     | —     | External clock source, counted at rising edge                   |

|         | 1     | 1     | 0     | _     |       | External clock source, counted at falling edge                  |

|         | 1     | 1     | 1     | —     | —     | External clock source, counted at both rising and falling edges |

Note: \* If the count input of channel 0 is the TCNT1 overflow signal and that of channel 1 is the TCNT0 compare-match signal, no incrementing clock will be generated. Do not use this setting.

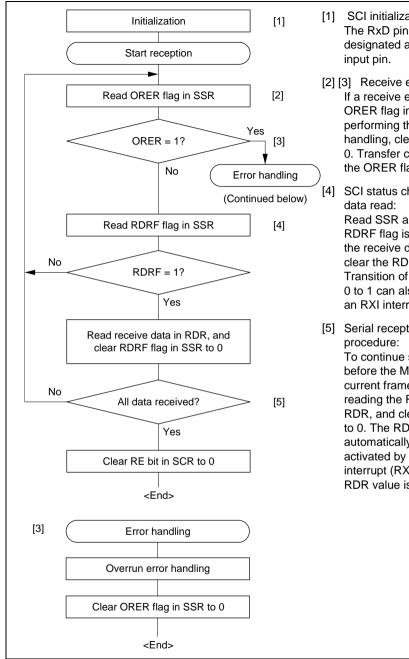

[1] SCI initialization: The RxD pin is automatically designated as the receive data

[2] [3] Receive error handling: If a receive error occurs, read the ORER flag in SSR, and after performing the appropriate error handling, clear the ORER flag to 0. Transfer cannot be resumed if the ORER flag is set to 1.

SCI status check and receive Read SSR and check that the RDRF flag is set to 1, then read the receive data in RDR and clear the RDRF flag to 0. Transition of the RDRF flag from 0 to 1 can also be identified by an RXI interrupt.

- [5] Serial reception continuation

- To continue serial reception, before the MSB (bit 7) of the current frame is received, finish reading the RDRF flag, reading RDR, and clearing the RDRF flag to 0. The RDRF flag is cleared automatically when the DTC is activated by a receive-data-full interrupt (RXI) request and the RDR value is read.

#### Figure 15.18 Sample Serial Reception Flowchart

Rev. 4.00 Sep 27, 2006 page 480 of 1130 REJ09B0327-0400

| HA0 | Data/Command                         | Internal CPU<br>Interrupt Flag | GA20<br>(P81) | Remarks                |

|-----|--------------------------------------|--------------------------------|---------------|------------------------|

| 1   | H'D1 command                         | 0                              | Q             | Turn-on sequence       |

| 0   | 1 data <sup>*1</sup><br>H'FF command | 0                              | 1             |                        |

| 1   |                                      |                                | Q (1)         | - "                    |

| 1   | H'D1 command                         | 0                              | Q             | Turn-off sequence      |

| 0   | 0 data <sup>*2</sup>                 | 0                              | 0             |                        |

|     | H'FF command                         | 0                              | Q (0)         |                        |

| 1   | H'D1 command                         | 0                              | Q             | Turn-on sequence       |

| 0   | 1 data <sup>*1</sup>                 | 0                              | 1             | (abbreviated form)     |

| 1/0 | Command other than H'FF<br>and H'D1  | 1                              | Q (1)         |                        |

| 1   | H'D1 command                         | 0                              | Q             | Turn-off sequence      |

| 0   | 0 data <sup>*2</sup>                 | 0                              | 0             | (abbreviated form)     |

| 1/0 | Command other than H'FF<br>and H'D1  | 1                              | Q (0)         |                        |

| 1   | H'D1 command                         | 0                              | Q             | Cancelled sequence     |

| 1   | Command other than H'D1              | 1                              | Q             |                        |

| 1   | H'D1 command                         | 0                              | Q             | Retriggered sequence   |

| 1   | H'D1 command                         | 0                              | Q             |                        |

| 1   | H'D1 command                         | 0                              | Q             | Consecutively executed |

| 0   | Any data                             | 0                              | 1/0           | sequences              |

| 1   | H'D1 command                         | 0                              | Q(1/0)        |                        |

#### Table 18.7 Fast A20 Gate Output Signal

Notes: 1. Arbitrary data with bit 1 set to 1.

2. Arbitrary data with bit 1 cleared to 0.

#### 18.3.4 Host Interface Pin Shutdown Function

Host interface output can be placed in the high-impedance state according to the state of the HIFSD pin. Setting the SDE bit to 1 in the SYSCR2 register enables the HIFSD pin is slave mode. The HIF constantly monitors the HIFSD pin, and when this pin goes low, places the host interface output pins (HIRQ1, HIRQ11, HIRQ12, HIRQ3, HIRQ4, and GA20) in the high-impedance state. At the same time, the host interface input pins ( $\overline{CS1}$ ,  $\overline{CS2}$  or  $\overline{ECS2}$ ,  $\overline{CS3}$ ,  $\overline{CS4}$ ,  $\overline{IOW}$ ,  $\overline{IOR}$ , and HA0) are disabled (fixed at the high input state internally) regardless of the pin states, and the signals of the multiplexed functions of these pins (input block) are similarly fixed internally. As a result, the host interface I/O pins (HDB7 to HDB0) also go to the high-impedance state.

This state is maintained while the HIFSD pin is low, and when the HIFSD pin returns to the high-level state, the pins are restored to their normal operation as host interface pins.

## Renesas

#### 22.4.4 Pin Configuration

The flash memory is controlled by means of the pins shown in table 22.3.

| Pin Name      | Abbreviation | I/O    | Function                                     |

|---------------|--------------|--------|----------------------------------------------|

| Reset         | RES          | Input  | Reset                                        |

| Mode 1        | MD1          | Input  | Sets MCU operating mode                      |

| Mode 0        | MD0          | Input  | Sets MCU operating mode                      |

| Port 92       | P92          | Input  | Sets MCU operating mode when $MD1 = MD0 = 0$ |

| Port 91       | P91          | Input  | Sets MCU operating mode when $MD1 = MD0 = 0$ |

| Port 90       | P90          | Input  | Sets MCU operating mode when $MD1 = MD0 = 0$ |

| Transmit data | TxD1         | Output | Serial transmit data output                  |

| Receive data  | RxD1         | Input  | Serial receive data input                    |

#### Table 22.3Flash Memory Pins

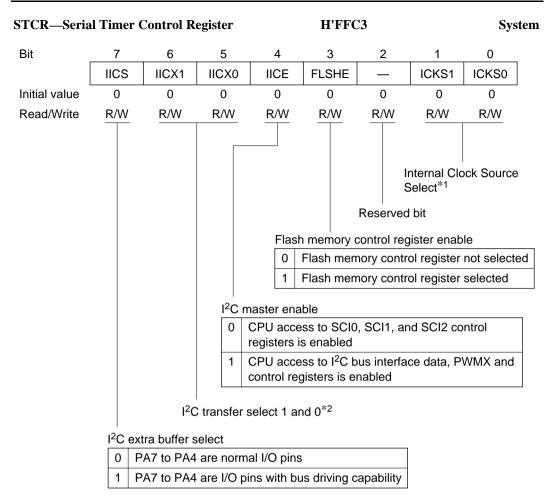

#### 22.4.5 Register Configuration

The registers used to control the on-chip flash memory when enabled are shown in table 22.4. In order for these registers to be accessed, the FLSHE bit must be set to 1 in STCR.

#### Table 22.4Flash Memory Registers

| Register Name                   | Abbreviation         | R/W   | Initial Value      | Address <sup>*1</sup> |

|---------------------------------|----------------------|-------|--------------------|-----------------------|

| Flash memory control register 1 | FLMCR1 <sup>*₅</sup> | R/W*3 | H'80               | H'FF80 <sup>*2</sup>  |

| Flash memory control register 2 | FLMCR2 <sup>*₅</sup> | R/W*3 | H'00 <sup>*4</sup> | H'FF81 <sup>*2</sup>  |

| Erase block register 1          | EBR1 <sup>*₅</sup>   | R/W*3 | H'00 <sup>*4</sup> | H'FF82*2              |

| Erase block register 2          | EBR2 <sup>*5</sup>   | R/W*3 | H'00 <sup>*4</sup> | H'FF83*2              |

| Serial/timer control register   | STCR                 | R/W   | H'00               | H'FFC3                |

Notes: 1. Lower 16 bits of the address.

- 2. Flash memory registers share addresses with other registers. Register selection is performed by the FLSHE bit in the serial/timer control register (STCR).

- 3. In modes in which the on-chip flash memory is disabled, a read will return H'00, and writes are invalid.

- 4. The SWE bit in FLMCR1 is not set, these registers are initialized to H'00.

- 5. FLMCR1, FLMCR2, EBR1, and EBR2 are 8-bit registers. Only byte accesses are valid for these registers, the access requiring 2 states. These registers are used only in the flash memory version. In the mask ROM version, a read at any of these addresses will return an undefined value, and writes are invalid.

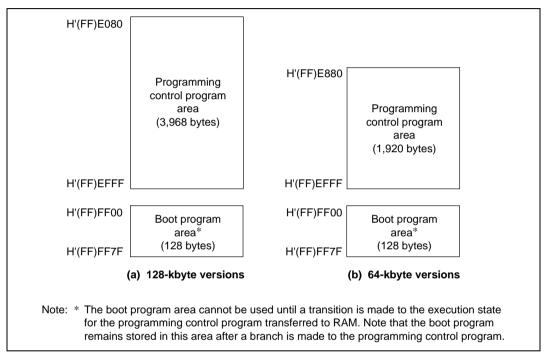

#### **On-Chip RAM Area Divisions in Boot Mode**

In boot mode, the 128-byte area from H'(FF)FF00 to H'(FF)FF7F is reserved for use by the boot program, as shown in figure 22.10. The area to which the programming control program is transferred is H'(FF)E080 to H'(FF)EFFF (3968 bytes) in the 128-kbyte versions, or H'(FF)E880 to H'(FF)EFFF (1920 bytes) in the 64-kbyte versions. The boot program area can be used when the programming control program transferred into RAM enters the execution state. A stack area should be set up as required.

#### Notes on Use of User Mode

- When the chip comes out of reset in boot mode, it measures the low period of the input at the SCI's RxD1 pin. The reset should end with RxD1 high. After the reset ends, it takes about 100 states for the chip to get ready to measure the low period of the RxD1 input.

- In boot mode, if any data has been programmed into the flash memory (if all data is not 1), all flash memory blocks are erased. Boot mode is for use when user program mode is unavailable, such as the first time on-board programming is performed, or if the program activated in user program mode is accidentally erased.

|                            | Pin Names |    |    |             |                   |  |  |

|----------------------------|-----------|----|----|-------------|-------------------|--|--|

| Mode                       | CE        | ŌĒ | WE | FO0 to FO7  | FA0 to FA17       |  |  |

| Read                       | L         | L  | Н  | Data output | Ain               |  |  |

| Output disable             | L         | Н  | Н  | Hi-Z        | Х                 |  |  |

| Command write              | L         | Н  | L  | Data input  | Ain <sup>*2</sup> |  |  |

| Chip disable <sup>*1</sup> | Н         | Х  | Х  | Hi-Z        | Х                 |  |  |

#### Table 23.11 Settings for Each Operating Mode in Programmer Mode

Notes: 1. Chip disable is not a standby state; internally, it is an operation state.

2. Ain indicates that there is also address input in auto-program mode.

#### **Table 23.12 Programmer Mode Commands**

|                   | Number    |       | 1st Cycle |      |       | 2nd Cycle |      |  |  |  |

|-------------------|-----------|-------|-----------|------|-------|-----------|------|--|--|--|

| Command Name      | of Cycles | Mode  | Address   | Data | Mode  | Address   | Data |  |  |  |

| Memory read mode  | 1 + n     | Write | Х         | H'00 | Read  | RA        | Dout |  |  |  |

| Auto-program mode | 129       | Write | Х         | H'40 | Write | WA        | Din  |  |  |  |

| Auto-erase mode   | 2         | Write | Х         | H'20 | Write | Х         | H'20 |  |  |  |

| Status read mode  | 2         | Write | Х         | H'71 | Write | Х         | H'71 |  |  |  |

Notes: 1. In auto-program mode. 129 cycles are required for command writing by a simultaneous 128-byte write.

2. In memory read mode, the number of cycles depends on the number of address write cycles (n).

#### 23.10.4 Memory Read Mode

- After the end of an auto-program, auto-erase, or status read operation, the command wait state is entered. To read memory contents, a transition must be made to memory read mode by means of a command write before the read is executed.

- Command writes can be performed in memory read mode, just as in the command wait state.

- Once memory read mode has been entered, consecutive reads can be performed.

- After power-on, memory read mode is entered.

# Notes: 1. Do not leave the AVCC, AV<sub>ref</sub>, and AVSS pins open even if the A/D converter and D/A converter are not used.

Even if the A/D converter and D/A converter are not used, apply a value in the range 2.0 V to 5.5 V to AVCC and AV<sub>ref</sub> pins by connection to the power supply (V<sub>cc</sub>), or some other method. Ensure that AV<sub>ref</sub>  $\leq$  AV<sub>cc</sub>.

- 2. P67 to P60 include supporting module inputs multiplexed on those pins.

- 3. IRQ2 includes the ADTRG signal multiplexed on that pin.

- In the H8S/2148 Group, P52/SCK0/SCL0 and P97/SDA0 are NMOS push-pull outputs. An external pull-up resistor is necessary to provide high-level output from SCL0 and SDA0 (ICE = 1).

In the H8S/2148 Group, P52/SCK0 and P97 (ICE = 0) high levels are driven by NMOS.

- 5. When IICS = 0, ICE = 0, and KBIOE = 0. Low-level output when the bus drive function is selected is determined separately.

- 6. The upper limit of the port 6 applied voltage is V<sub>cc</sub> +0.3 V when CIN input is not selected, and the lower of V<sub>cc</sub> +0.3 V and AV<sub>cc</sub> +0.3 V when CIN input is selected. When a pin is in output mode, the output voltage is equivalent to the applied voltage.

- 7. The upper limit of the port A applied voltage is  $V_{cc}B$  +0.3 V when CIN input is not selected, and the lower of  $V_{cc}B$  +0.3 V and  $AV_{cc}$  +0.3 V when CIN input is selected. When a pin is in output mode, the output voltage is equivalent to the applied voltage.

- 8. The port A characteristics depend on  $V_{\rm cc}B$ , and the other pins characteristics depend on  $V_{\rm cc}.$

- 9. Current dissipation values are for  $V_{\mu}$  min =  $V_{cc}$  –0.5 V,  $V_{cc}B$  –0.5 V, and  $V_{\mu}$  max = 0.5 V with all output pins unloaded and the on-chip pull-up MOSs in the off state.

- 10. The values are for V\_{\_{RAM}} \le V\_{\_{CC}} < 4.0 V, V  $_{_{IH}}$  min = V  $_{_{CC}}$   $\times$  0.9, V  $_{_{CC}}$  B  $\times$  0.9, and V  $_{_{IL}}$  max = 0.3 V.

- 11. For flash memory program/erase operations, the applicable ranges are  $V_{cc}$  = 4.5 V to 5.5 V and  $T_a$  = 0 to +75°C (regular specifications) or  $T_a$  = 0 to +85°C (wide-range specifications).

#### (1) Clock Timing

Table 26.6 shows the clock timing. The clock timing specified here covers clock ( $\phi$ ) output and clock pulse generator (crystal) and external clock input (EXTAL pin) oscillation settling times. For details of external clock input (EXTAL pin and EXCL pin) timing, see section 24, Clock Pulse Generator.

#### Table 26.6Clock Timing

- Condition A:  $V_{cc} = 5.0 \text{ V} \pm 10\%$ ,  $V_{cc}B = 5.0 \text{ V} \pm 10\%$ ,  $V_{ss} = 0 \text{ V}$ ,  $\phi = 2 \text{ MHz}$  to maximum operating frequency,  $T_a = -20$  to  $+75^{\circ}C$  (regular specifications),  $T_a = -40$  to  $+85^{\circ}C$  (wide-range specifications)

- Condition B:  $V_{cc} = 4.0 \text{ V to } 5.5 \text{ V}, V_{cc}B = 4.0 \text{ V to } 5.5 \text{ V}, V_{ss} = 0 \text{ V}, \phi = 2 \text{ MHz to maximum}$ operating frequency,  $T_a = -20 \text{ to } +75^{\circ}\text{C}$  (regular specifications),  $T_a = -40 \text{ to } +85^{\circ}\text{C}$  (wide-range specifications)

- Condition C:  $V_{cc} = 3.0 \text{ V}$  to 5.5 V,  $V_{cc}B = 3.0 \text{ V}$  to 5.5 V,  $V_{ss} = 0 \text{ V}$ ,  $\phi = 2 \text{ MHz}$  to maximum operating frequency,  $T_a = -20$  to  $+75^{\circ}\text{C}$

|                                                               |                   | Cond | dition A | Cond | dition B | Con | dition C |      |                            |

|---------------------------------------------------------------|-------------------|------|----------|------|----------|-----|----------|------|----------------------------|

|                                                               |                   | 20   | MHz      | 16   | MHz      | 10  | MHz      |      | Test                       |

| ltem                                                          | Symbol            | Min  | Max      | Min  | Max      | Min | Max      | Unit | Conditions                 |

| Clock cycle time                                              | t <sub>cyc</sub>  | 50   | 500      | 62.5 | 500      | 100 | 500      | ns   | Figure 26.5                |

| Clock high pulse width                                        | t <sub>сн</sub>   | 17   | _        | 20   | _        | 30  | _        | ns   | Figure 26.5                |

| Clock low pulse width                                         | t <sub>cL</sub>   | 17   | —        | 20   | —        | 30  | —        | ns   | _                          |

| Clock rise time                                               | t <sub>cr</sub>   | _    | 8        | _    | 10       | _   | 20       | ns   |                            |

| Clock fall time                                               | t <sub>cf</sub>   | _    | 8        | —    | 10       | _   | 20       | ns   |                            |

| Oscillation settling<br>time at reset<br>(crystal)            | t <sub>osc1</sub> | 10   | _        | 10   | _        | 20  | _        | ms   | Figure 26.6<br>Figure 26.7 |

| Oscillation settling<br>time in software<br>standby (crystal) | t <sub>osc2</sub> | 8    | _        | 8    | _        | 8   | _        | ms   | _                          |

| External clock<br>output stabilization<br>delay time          | t <sub>dext</sub> | 500  | _        | 500  | _        | 500 | —        | μs   |                            |

### Renesas

#### 26.5.4 A/D Conversion Characteristics

Tables 26.52 and 26.53 list the A/D conversion characteristics.

#### Table 26.52 A/D Conversion Characteristics (AN7 to AN0 Input: 134/266-State Conversion)

- Condition A:  $V_{cc} = 5.0 V \pm 10\%$ ,  $AV_{cc} = 5.0 V \pm 10\%$ ,  $AV_{ref} = 4.5 V$  to  $AV_{cc}$ ,  $V_{ss} = AV_{ss} = 0 V$ ,  $\phi = 2$  MHz to maximum operating frequency,  $T_a = -20$  to  $+75^{\circ}C$  (regular specifications),  $T_a = -40$  to  $+85^{\circ}C$  (wide-range specifications)

- $\begin{array}{ll} \text{Condition B:} \quad V_{\text{cc}} = 4.0 \text{ V to } 5.5 \text{ V}, \text{AV}_{\text{cc}} = 4.0 \text{ V to } 5.5 \text{ V}, \text{AV}_{\text{ref}} = 4.0 \text{ V to } \text{AV}_{\text{cc}}, \text{V}_{\text{ss}} = \text{AV}_{\text{ss}} = 0 \text{ V}, \varphi = 2 \text{ MHz to maximum operating frequency}, \text{T}_{a} = -20 \text{ to } +75^{\circ}\text{C} \text{ (regular specifications)}, \text{T}_{a} = -40 \text{ to } +85^{\circ}\text{C} \text{ (wide-range specifications)} \end{array}$

- Condition C (mask ROM version):  $V_{cc} = 2.7$  V to 5.5 V,  $AV_{cc} = 2.7$  V to 5.5 V,  $AV_{ref} = 2.7$  V to  $AV_{cc}$ ,  $V_{ss} = AV_{ss} = 0$  V,  $\phi = 2$  MHz to maximum operating frequency,  $T_a = -20$  to  $+75^{\circ}$ C

Condition C (F-ZTAT version):  $V_{cc} = 3.0$  V to 5.5 V,  $AV_{cc} = 3.0$  V to 5.5 V,  $AV_{ref} = 3.0$  V to  $AV_{cc}$ ,  $V_{ss} = AV_{ss} = 0$  V,  $\phi = 2$  MHz to maximum operating frequency,  $T_a = -20$  to  $+75^{\circ}C$

|                                         |     | Conditio | on A                                |     | Conditio | on B                                |     | Conditio | on C                                |      |  |  |  |

|-----------------------------------------|-----|----------|-------------------------------------|-----|----------|-------------------------------------|-----|----------|-------------------------------------|------|--|--|--|

|                                         |     | 20 MH    | lz                                  |     | 16 MH    | lz                                  |     | 10 MH    | lz                                  | -    |  |  |  |

| Item                                    | Min | Тур      | Max                                 | Min | Тур      | Max                                 | Min | Тур      | Max                                 | Unit |  |  |  |

| Resolution                              | 10  | 10       | 10                                  | 10  | 10       | 10                                  | 10  | 10       | 10                                  | Bits |  |  |  |

| Conversion time*5                       | —   | _        | 6.7                                 | _   | —        | 8.4                                 | _   | _        | 13.4                                | μs   |  |  |  |

| Analog input capacitance                | —   | —        | 20                                  | —   | —        | 20                                  | —   | —        | 20                                  | pF   |  |  |  |

| Permissible signal-<br>source impedance | —   | —        | 10 <sup>*3</sup><br>5 <sup>*4</sup> |     | _        | 10 <sup>*3</sup><br>5 <sup>*4</sup> | _   | —        | 10 <sup>*1</sup><br>5 <sup>*2</sup> | kΩ   |  |  |  |

| Nonlinearity error                      | —   | —        | ±3.0                                | _   | —        | ±3.0                                | _   | —        | ±7.0                                | LSB  |  |  |  |

| Offset error                            | —   | —        | ±3.5                                | _   | —        | ±3.5                                | _   | —        | ±7.5                                | LSB  |  |  |  |

| Full-scale error                        | —   | —        | ±3.5                                | —   | —        | ±3.5                                | —   | —        | ±7.5                                | LSB  |  |  |  |

| Quantization error                      | —   | —        | ±0.5                                | —   | —        | ±0.5                                | —   | —        | ±0.5                                | LSB  |  |  |  |

| Absolute accuracy                       | —   | —        | ±4.0                                | _   | —        | ±4.0                                | _   | —        | ±8.0                                | LSB  |  |  |  |

|                                         |     |          |                                     |     |          |                                     |     |          |                                     |      |  |  |  |

Notes: 1. When 4.0 V  $\leq$  AV  $_{cc}$   $\leq$  5.5 V

- 2. When 2.7 V  $\leq$  AV<sub>cc</sub> < 4.0 V (mask ROM version) or when 3.0 V  $\leq$  AV<sub>cc</sub> < 4.0 V (F-ZTAT version)

- 3. When conversion time  $\geq$  11. 17  $\mu s$  (CKS = 1 and  $\phi \leq$  12 MHz, or CKS = 0)

- 4. When conversion time < 11. 17  $\mu$ s (CKS = 1 and  $\phi$  > 12 MHz)

- 5. In single mode and  $\phi$  = maximum operating frequency.

## Renesas

#### 26.6.2 **DC Characteristics**

Table 26.57 lists the DC characteristics. Permitted output current values and bus drive characteristics are shown in tables 26.58 and 26.59, respectively.

#### Table 26.57 DC Characteristics (1)

Conditions:  $V_{cc} = 5.0 \text{ V} \pm 10\%$ ,  $AV_{cc}^{*1} = 5.0 \text{ V} \pm 10\%$ ,  $AV_{ref}^{*1} = 4.5 \text{ V}$  to  $AV_{cc}$ ,  $V_{ss} = AV_{ss}^{*1} = 0 V, T_a = -20 \text{ to } +75^{\circ}C \text{ (regular specifications),}$  $T_{o} = -40$  to  $+85^{\circ}C$  (wide-range specifications)

| ltem                     |                                                                                                                                            |     | Symbol                          | Min                  | Тур | Max                   | Unit | Test<br>Conditions        |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------|----------------------|-----|-----------------------|------|---------------------------|

| Schmitt                  | P67 to P60 <sup>*2*5</sup> ,                                                                                                               | (1) | V <sub>T</sub> <sup>-</sup>     | 1.0                  | _   | _                     | V    |                           |

| trigger input<br>voltage | $\frac{\overline{\text{KIN15}} \text{ to } \overline{\text{KIN8}}^{*5},}{\overline{\text{IRQ2}} \text{ to } \overline{\text{IRQ0}}^{*3},}$ |     | $V_{T}^{+}$                     | _                    | _   | $V_{cc} 	imes 0.7$    | V    |                           |

| ronago                   | IRQ5 to IRQ3                                                                                                                               |     | $V_{\rm T}^{^+}-V_{\rm T}^{^-}$ | 0.4                  | —   | _                     | V    | _                         |

| Input high<br>voltage    | RES, STBY,<br>NMI, MD1,<br>MD0                                                                                                             | (2) | V <sub>IH</sub>                 | V <sub>cc</sub> –0.7 | _   | V <sub>cc</sub> +0.3  | V    |                           |

|                          | EXTAL,<br>PA7 to PA0 <sup>*5</sup>                                                                                                         | _   |                                 | $V_{cc} \times 0.7$  | —   | V <sub>cc</sub> +0.3  | V    | _                         |

|                          | Port 7                                                                                                                                     | -   |                                 | 2.0                  | —   | AV <sub>cc</sub> +0.3 | V    | _                         |

| _                        | Input pins except<br>(1) and (2)<br>above                                                                                                  |     | _                               | 2.0                  | —   | V <sub>cc</sub> +0.3  | V    |                           |

| Input low<br>voltage     | RES, STBY,<br>MD1, MD0                                                                                                                     | (3) | V                               | -0.3                 | —   | 0.5                   | V    |                           |

|                          | PA7 to PA0                                                                                                                                 | -   |                                 | -0.3                 | —   | 1.0                   | V    |                           |

|                          | NMI, EXTAL,<br>input pins except<br>(1) and (3)<br>above                                                                                   |     | _                               | -0.3                 | _   | 0.8                   | V    | _                         |

|                          | All output pins*4                                                                                                                          |     | V <sub>OH</sub>                 | V <sub>cc</sub> –0.5 | —   | _                     | V    | I <sub>oH</sub> = -200 μA |

| voltage                  |                                                                                                                                            |     |                                 | 3.5                  | _   | _                     | V    | I <sub>он</sub> = —1 mA   |

| Output low voltage       | All output pins<br>(except RESO)*4                                                                                                         |     | V <sub>ol</sub>                 | _                    | —   | 0.4                   | V    | I <sub>oL</sub> = 1.6 mA  |

|                          | Ports 1 to 3                                                                                                                               |     |                                 | _                    | _   | 1.0                   | V    | I <sub>oL</sub> = 10 mA   |

|                          | RESO                                                                                                                                       |     |                                 | _                    | —   | 0.4                   | V    | I <sub>oL</sub> = 2.6 mA  |

|       |                |             |     |    |      |          |             |     | e an<br>(By |        | ) |             | Condition Code |   |    |    |   |    | No.<br>Stat | . of<br>tes <sup>*1</sup> |

|-------|----------------|-------------|-----|----|------|----------|-------------|-----|-------------|--------|---|-------------|----------------|---|----|----|---|----|-------------|---------------------------|

|       | Mnemonic       | Size        | XX# | Rn | @ERn | @(d,ERn) | @-ERn/@ERn+ | @aa | @(d,PC)     | @ @ aa | 1 | Operation   | I              | н | N  | z  | v | с  | Normal      | Advanced                  |

| ROTXR | ROTXR.B Rd     | В           |     | 2  |      |          |             |     |             |        |   |             | _              | — | ¢  | \$ | 0 | ¢  | ,           | 1                         |

|       | ROTXR.B #2,Rd  | 3 #2,Rd B 2 |     | _  | —    | ¢        | \$          | 0   | \$          |        | 1 |             |                |   |    |    |   |    |             |                           |

|       | ROTXR.W Rd     | w           |     | 2  |      |          |             |     |             |        |   | MSB - LSB C | _              | — | ¢  | \$ | 0 | \$ |             | 1                         |

|       | ROTXR.W #2,Rd  | W           |     | 2  |      |          |             |     |             |        |   |             | _              |   | ¢  | ¢  | 0 | ¢  |             | 1                         |

|       | ROTXR.L ERd    | L           |     | 2  |      |          |             |     |             |        |   |             | _              | — | \$ | \$ | 0 | ¢  |             | 1                         |

|       | ROTXR.L #2,ERd | L           |     | 2  |      |          |             |     |             |        |   |             | _              | — | \$ | \$ | 0 | \$ | ,           | 1                         |

| ROTL  | ROTL.B Rd      | В           |     | 2  |      |          |             |     |             |        |   |             | _              | — | \$ | \$ | 0 | \$ | ,           | 1                         |

|       | ROTL.B #2,Rd   | В           |     | 2  |      |          |             |     |             |        |   |             | _              |   | ¢  | ¢  | 0 | \$ | ,           | 1                         |

|       | ROTL.W Rd      | W           |     | 2  |      |          |             |     |             |        |   |             | _              |   | ¢  | ¢  | 0 | ¢  | ,           | 1                         |

|       | ROTL.W #2,Rd   | w           |     | 2  |      |          |             |     |             |        |   | C MSB - LSB | _              | _ | ¢  | ¢  | 0 | ¢  |             | 1                         |

|       | ROTL.L ERd     | L           |     | 2  |      |          |             |     |             |        |   |             | _              | _ | ¢  | ¢  | 0 | ¢  |             | 1                         |

|       | ROTL.L #2,ERd  | L           |     | 2  |      |          |             |     |             |        |   |             | _              | _ | ¢  | ¢  | 0 | ¢  |             | 1                         |

| ROTR  | ROTR.B Rd      | В           |     | 2  |      |          |             |     |             |        |   |             | _              | _ | \$ | \$ | 0 | ¢  |             | 1                         |

|       | ROTR.B #2,Rd   | В           |     | 2  |      |          |             |     |             |        |   |             | _              | _ | \$ | \$ | 0 | ¢  | -           | 1                         |

|       | ROTR.W Rd      | w           |     | 2  |      |          |             |     |             |        |   |             | _              | _ | \$ | \$ | 0 | ¢  | -           | 1                         |

|       | ROTR.W #2,Rd   | w           |     | 2  |      |          |             |     |             |        |   |             | _              | _ | \$ | \$ | 0 | \$ |             | 1                         |

|       | ROTR.L ERd     | L           |     | 2  |      |          |             |     |             |        |   | MSB         | _              | _ | \$ | \$ | 0 | \$ |             | 1                         |

|       | ROTR.L #2,ERd  | L           |     | 2  |      |          |             |     |             |        |   |             | _              | _ | ¢  | ¢  | 0 | ¢  |             | 1                         |

| Address | Register<br>Name | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Module<br>Name | Bus<br>Width |

|---------|------------------|--------|--------|--------|--------|---------|--------|--------|--------|----------------|--------------|

| H'FFA2  | SCR2             | TIE    | RIE    | TE     | RE     | MPIE    | TEIE   | CKE1   | CKE0   | SCI2           | 8            |

| H'FFA3  | TDR2             |        |        |        |        |         |        |        |        |                |              |

| H'FFA4  | SSR2             | TDRE   | RDRF   | ORER   | FER    | PER     | TEND   | MPB    | MPBT   |                |              |

| H'FFA5  | RDR2             |        |        |        |        |         |        |        |        |                |              |

| H'FFA6  | SCMR2            | _      | _      | _      | _      | SDIR    | SINV   | _      | SMIF   |                |              |

|         | DADRBH           | DA13   | DA12   | DA11   | DA10   | DA9     | DA8    | DA7    | DA6    | PWMX           | 8            |

|         | DACNTH           |        |        |        |        |         |        |        |        |                |              |

| H'FFA7  | DADRBL           | DA5    | DA4    | DA3    | DA2    | DA1     | DA0    | CFS    | REGS   |                |              |

|         | DACNTL           |        |        |        |        |         |        | _      | REGS   |                |              |

| H'FFA8  | TCSR0            | OVF    | WT/IT  | TME    | RSTS   | RST/NMI | CKS2   | CKS1   | CKS0   | WDT0           | 16           |

|         | TCNT0<br>(write) |        |        |        |        |         |        |        |        |                |              |

| H'FFA9  | TCNT0<br>(read)  |        |        |        |        |         |        |        |        |                |              |

| H'FFAA  | PAODR            | PA7ODR | PA6ODR | PA5ODR | PA40DR | PA3ODR  | PA2ODR | PA10DR | PA0ODR | Ports          | 8            |

| H'FFAB  | PAPIN<br>(read)  | PA7PIN | PA6PIN | PA5PIN | PA4PIN | PA3PIN  | PA2PIN | PA1PIN | PA0PIN |                |              |

|         | PADDR<br>(write) | PA7DDR | PA6DDR | PA5DDR | PA4DDR | PA3DDR  | PA2DDR | PA1DDR | PA0DDR |                |              |

| H'FFAC  | P1PCR            | P17PCR | P16PCR | P15PCR | P14PCR | P13PCR  | P12PCR | P11PCR | P10PCR |                |              |

| H'FFAD  | P2PCR            | P27PCR | P26PCR | P25PCR | P24PCR | P23PCR  | P22PCR | P21PCR | P20PCR |                |              |

| H'FFAE  | P3PCR            | P37PCR | P36PCR | P35PCR | P34PCR | P33PCR  | P32PCR | P31PCR | P30PCR |                |              |

| H'FFB0  | P1DDR            | P17DDR | P16DDR | P15DDR | P14DDR | P13DDR  | P12DDR | P11DDR | P10DDR |                |              |

| H'FFB1  | P2DDR            | P27DDR | P26DDR | P25DDR | P24DDR | P23DDR  | P22DDR | P21DDR | P20DDR |                |              |

| H'FFB2  | P1DR             | P17DR  | P16DR  | P15DR  | P14DR  | P13DR   | P12DR  | P11DR  | P10DR  |                |              |

| H'FFB3  | P2DR             | P27DR  | P26DR  | P25DR  | P24DR  | P23DR   | P22DR  | P21DR  | P20DR  |                |              |

| H'FFB4  | P3DDR            | P37DDR | P36DDR | P35DDR | P34DDR | P33DDR  | P32DDR | P31DDR | P30DDR |                |              |

| H'FFB5  | P4DDR            | P47DDR | P46DDR | P45DDR | P44DDR | P43DDR  | P42DDR | P41DDR | P40DDR |                |              |

| H'FFB6  | P3DR             | P37DR  | P36DR  | P35DR  | P34DR  | P33DR   | P32DR  | P31DR  | P30DR  |                |              |

| H'FFB7  | P4DR             | P47DR  | P46DR  | P45DR  | P44DR  | P43DR   | P42DR  | P41DR  | P40DR  |                |              |

| H'FFB8  | P5DDR            | _      | _      | _      | _      | _       | P52DDR | P51DDR | P50DDR |                |              |

| H'FFB9  | P6DDR            | P67DDR | P66DDR | P65DDR | P64DDR | P63DDR  | P62DDR | P61DDR | P60DDR |                |              |

| H'FFBA  | P5DR             | _      | _      | _      | _      | _       | P52DR  | P51DR  | P50DR  |                |              |

| H'FFBB  | P6DR             | P67DR  | P66DR  | P65DR  | P64DR  | P63DR   | P62DR  | P61DR  | P60DR  |                |              |

| H'FFBC  | PBODR            | PB7ODR | PB60DR | PB50DR | PB40DR | PB30DR  | PB2ODR | PB10DR | PB00DR |                |              |

| H'FFBD  | PBPIN<br>(read)  | PB7PIN | PB6PIN | PB5PIN | PB4PIN | PB3PIN  | PB2PIN | PB1PIN | PB0PIN |                |              |

|         | P8DDR<br>(write) | _      | P86DDR | P85DDR | P84DDR | P83DDR  | P82DDR | P81DDR | P80DDR |                |              |

| STR3—Status<br>STR4—Status |                                                    |          |           | H'FE86<br>H'FE8E |     |           |                                           |                                                                                                              |                                                               |    |  |

|----------------------------|----------------------------------------------------|----------|-----------|------------------|-----|-----------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----|--|

| Bit                        | 7                                                  | 6        | 5         | 4                |     | 3         | 2                                         | 1                                                                                                            | 0                                                             |    |  |

|                            | DBU                                                | DBU      | DBU       | DBU              |     | C/D       | DBU                                       | IBF                                                                                                          | OBF                                                           |    |  |

| Initial value              | 0                                                  | 0        | 0         | 0                |     | 0         | 0                                         | 0                                                                                                            | 0                                                             | _  |  |

| Slave R/W                  | R/W                                                | R/W      | R/W       | R/W              |     | R         | R/W                                       | R                                                                                                            | R/(W)                                                         |    |  |

| Host R/W                   | R                                                  | R        | R         | R                |     | R         | R                                         | R                                                                                                            | R                                                             |    |  |

|                            |                                                    |          |           |                  |     |           |                                           |                                                                                                              |                                                               |    |  |

|                            |                                                    | User-def | ïned bits |                  | Inp | ut buffer | Wh<br>read<br>writ<br>1 [Se<br>Wh<br>writ | uffer full<br>earing con<br>en the hos<br>ds ODR o<br>es 0 in the<br>tting condi<br>en the slav<br>es to ODF | st process<br>r the slave<br>e OBF bit<br>ition]<br>ve proces | e  |  |

|                            |                                                    |          |           |                  | 0   |           | ng conditi<br>the slave                   | on]<br>processor                                                                                             | reads ID                                                      | R  |  |

|                            |                                                    |          |           |                  | 1   |           | g condition<br>the host p                 | n]<br>rocessor v                                                                                             | writes to I                                                   | DR |  |

| Command/data               |                                                    |          |           |                  |     |           |                                           |                                                                                                              |                                                               |    |  |

|                            | 0 Contents of input data register (IDR) are data   |          |           |                  |     |           |                                           |                                                                                                              |                                                               |    |  |

|                            | 1 Contents of input data register (IDR) are a comm |          |           |                  |     |           |                                           |                                                                                                              |                                                               |    |  |

- Notes: 1. Used for 8-bit timer input clock selection. For details, see section 12.2.4, Timer Control Register (TCR).

- Used for I<sup>2</sup>C bus interface transfer clock selection. For details, see section 16.2.4, I<sup>2</sup>C Bus Mode Register (ICMR).

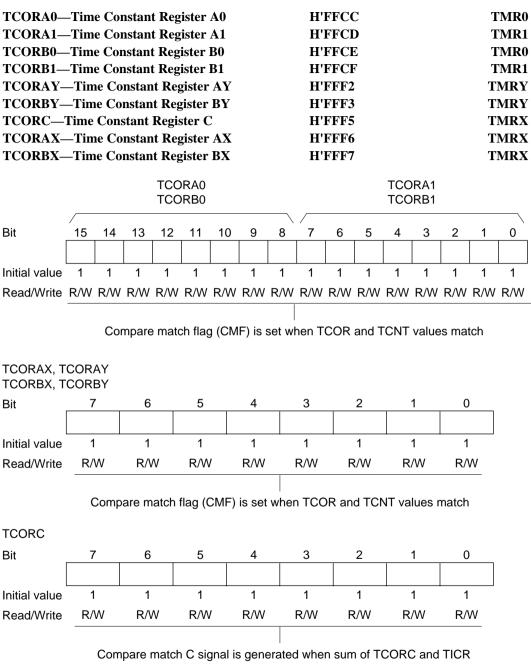

contents match TCNT value