#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                       |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 10MHz                                                                          |

| Connectivity               | Host Interface (LPC), I <sup>2</sup> C, IrDA, SCI, X-Bus                       |

| Peripherals                | PWM, WDT                                                                       |

| Number of I/O              | 74                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                    |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                            |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2148bvte10v |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Item                                                    | Specifications                                                                                                      |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Bus controller                                          | 2-state or 3-state access space can be designated for external                                                      |

|                                                         | expansion areas                                                                                                     |

|                                                         | Number of program wait states can be set for external expansion areas                                               |

| Data transfer                                           | Can be activated by internal interrupt or software                                                                  |

| controller (DTC)<br>(H8S/2148 Group)                    | <ul> <li>Multiple transfers or multiple types of transfer possible for one<br/>activation source</li> </ul>         |

|                                                         | Transfer possible in repeat mode, block transfer mode, etc.                                                         |

|                                                         | Request can be sent to CPU for interrupt that activated DTC                                                         |

| 16-bit free-running<br>timer module                     | <ul> <li>One 16-bit free-running counter (also usable for external event counting)</li> </ul>                       |

| (FRT: 1 channel)                                        | Two output compare outputs                                                                                          |

|                                                         | Four input capture inputs (with buffer operation capability)                                                        |

| 8-bit timer module                                      | Each channel has:                                                                                                   |

| (2 channels: TMR0,<br>TMR1)                             | One 8-bit up-counter (also usable for external event counting)                                                      |

|                                                         | Two timer constant registers                                                                                        |

|                                                         | The two channels can be connected                                                                                   |

| Timer connection and                                    | Input/output and FRT, TMR1, TMRX, TMRY can be interconnected                                                        |

| 8-bit timer module<br>(TMR) (2 channels:<br>TMRX, TMRY) | <ul> <li>Measurement of input signal or frequency-divided waveform pulse<br/>width and cycle (FRT, TMR1)</li> </ul> |

| (Timer connection and TMRX provided in                  | • Output of waveform obtained by modification of input signal edge (FRT, TMR1)                                      |

| H8S/2148 Group)                                         | Determination of input signal duty cycle (TMRX)                                                                     |

|                                                         | <ul> <li>Output of waveform synchronized with input signal (FRT, TMRX,<br/>TMRY)</li> </ul>                         |

|                                                         | Automatic generation of cyclical waveform (FRT, TMRY)                                                               |

| Watchdog timer                                          | Watchdog timer or interval timer function selectable                                                                |

| module<br>(WDT: 2 channels)                             | Subclock operation capability (channel 1 only)                                                                      |

| 8-bit PWM timer                                         | Up to 16 outputs                                                                                                    |

| (PWM)<br>(H8S/2148 Group and                            | Pulse duty cycle settable from 0 to 100%                                                                            |

| H8S/2147N)                                              | Resolution: 1/256                                                                                                   |

|                                                         | 1.25 MHz maximum carrier frequency (20-MHz operation)                                                               |

|            |                    | Addressing Modes |    |      |             |              |             |       |        |        |        |            |             |         |    |

|------------|--------------------|------------------|----|------|-------------|--------------|-------------|-------|--------|--------|--------|------------|-------------|---------|----|

| Function   | Instruction        | ***              | Rn | @ERn | @(d:16,ERn) | @(d:32, ERn) | @-ERn/@ERn+ | @aa:8 | @aa:16 | @aa:24 | @aa:32 | @(d:8, PC) | @(d:16, PC) | @ @aa:8 |    |

| System     | TRAPA              | _                | _  | _    | _           | _            | _           | _     | _      | —      | _      | _          | —           | _       | 0  |

| control    | RTE                | _                | _  | —    | _           | _            | _           | —     | —      | —      | —      | —          | —           | —       | 0  |

|            | SLEEP              | _                | _  | _    | _           | _            | _           | _     | _      | _      | _      | _          | _           | _       | 0  |

|            | LDC                | В                | В  | W    | W           | W            | W           | _     | W      | —      | W      | _          | —           | _       | -  |

|            | STC                | —                | В  | W    | W           | W            | W           | _     | W      | —      | W      | _          | —           | _       | -  |

|            | ANDC, ORC,<br>XORC | В                | -  | _    | -           | -            | _           | _     | _      | _      | _      | _          | —           | _       | —  |

|            | NOP                | -                | -  | —    | -           | -            | -           | —     | _      | —      | —      | _          | —           | —       | 0  |

| Block data | transfer           | -                | -  | —    | -           | -            | -           | —     | _      | _      | —      | _          | _           | —       | BW |

Legend:

B: Byte

W: Word

L: Longword

Notes: 1. Cannot be used in this LSI.

- 2. Only register ER0, ER1, ER4, or ER5 should be used when using the TAS instruction.

- 3. Only registers ER0 to ER6 should be used when using the STM/LDM instruction.

#### 5.2.6 Keyboard Matrix Interrupt Mask Register (KMIMR)

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

|               | KMIMR7 | KMIMR6 | KMIMR5 | KMIMR4 | KMIMR3 | KMIMR2 | KMIMR1 | KMIMR0 |

| Initial value | 1      | 0      | 1      | 1      | 1      | 1      | 1      | 1      |

| Read/Write    | R/W    |

KMIMR is an 8-bit readable/writable register that performs mask control for the keyboard matrix interrupt inputs (pins  $\overline{\text{KIN7}}$  to  $\overline{\text{KIN0}}$ ). To enable key-sense input interrupts from multiple pin inputs in keyboard matrix scanning/sensing, clear the corresponding mask bits to 0.

KMIMR is initialized to H'BF by a reset and in hardware standby mode and only  $\overline{IRQ6}$  ( $\overline{KIN6}$ ) input is enabled.

**Bits 7 to 0—Keyboard Matrix Interrupt Mask (KMIMR7 to KMIMR0):** These bits control key-sense input interrupt requests (KIN7 to KIN0).

#### Bits 7 to 0

| KMIMR7 to<br>KMIMR0 | Description                                                                                                                                 |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 0                   | Key-sense input interrupt requests enabled                                                                                                  |

| 1                   | Key-sense input interrupt requests disabled (Initial value)*                                                                                |

| Note: *             | However, the initial value of KMIMR6 is 0 because the KMIMR6 bit controls both IRQ6 interrupt request masking and key-sense input enabling. |

#### 5.2.7 Keyboard Matrix Interrupt Mask Register (KMIMRA)

| Bit           | 7       | 6       | 5       | 4       | 3       | 2       | 1      | 0      |

|---------------|---------|---------|---------|---------|---------|---------|--------|--------|

|               | KMIMR15 | KMIMR14 | KMIMR13 | KMIMR12 | KMIMR11 | KMIMR10 | KMIMR9 | KMIMR8 |

| Initial value | 1       | 1       | 1       | 1       | 1       | 1       | 1      | 1      |

| Read/Write    | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W    | R/W    |

KMIMRA is an 8-bit readable/writable register that performs mask control for the keyboard matrix interrupt inputs (pins  $\overline{\text{KIN15}}$  to  $\overline{\text{KIN8}}$ ). To enable key-sense input interrupts from multiple pin inputs in keyboard matrix scanning/sensing, clear the corresponding mask bits to 0.

KMIMRA is initialized to H'FF by a reset and in hardware standby mode.

#### 5.5.4 Interrupt Exception Handling Sequence

Figure 5.11 shows the interrupt exception handling sequence. The example shown is for the case where interrupt control mode 0 is set in advanced mode, and the program area and stack area are in on-chip memory.

#### 8.4.2 Register Configuration

Table 8.8 shows the port 3 register configuration.

#### Table 8.8Port 3 Registers

| Name                                | Abbreviation | R/W | Initial Value | Address* |

|-------------------------------------|--------------|-----|---------------|----------|

| Port 3 data direction register      | P3DDR        | W   | H'00          | H'FFB4   |

| Port 3 data register                | P3DR         | R/W | H'00          | H'FFB6   |

| Port 3 MOS pull-up control register | P3PCR        | R/W | H'00          | H'FFAE   |

Note: \* Lower 16 bits of the address.

#### Port 3 Data Direction Register (P3DDR)

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

|               | P37DDR | P36DDR | P35DDR | P34DDR | P33DDR | P32DDR | P31DDR | P30DDR |

| Initial value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| Read/Write    | W      | W      | W      | W      | W      | W      | W      | W      |

P3DDR is an 8-bit write-only register, the individual bits of which specify input or output for the pins of port 3. P3DDR cannot be read; if it is, an undefined value will be returned.

P3DDR is initialized to H'00 by a reset and in hardware standby mode. It retains its prior state in software standby mode.

• Modes 1, 2, and 3 (EXPE = 1)

The input/output direction specified by P3DDR is ignored, and pins automatically function as data I/O pins.

After a reset, and in hardware standby mode or software standby mode, the data I/O pins go to the high-impedance state.

• Modes 2 and 3 (EXPE = 0)

The corresponding port 3 pins are output ports when P3DDR bits are set to 1, and input ports when cleared to 0.

#### 8.11.2 Register Configuration

Table 8.22 summarizes the port A registers.

#### Table 8.22 Port A Registers

| Name                           | Abbreviation | R/W | Initial Value | Address <sup>*1</sup> |

|--------------------------------|--------------|-----|---------------|-----------------------|

| Port A data direction register | PADDR        | W   | H'00          | H'FFAB <sup>*2</sup>  |

| Port A output data register    | PAODR        | R/W | H'00          | H'FFAA                |

| Port A input data register     | PAPIN        | R   | Undefined     | H'FFAB <sup>*2</sup>  |

Notes: 1. Lower 16 bits of the address.

2. PADDR and PAPIN have the same address.

#### Port A Data Direction Register (PADDR)

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

|               | PA7DDR | PA6DDR | PA5DDR | PA4DDR | PA3DDR | PA2DDR | PA1DDR | PA0DDR |

| Initial value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| Read/Write    | W      | W      | W      | W      | W      | W      | W      | W      |

PADDR is an 8-bit write-only register, the individual bits of which specify input or output for the pins of port A.

Setting a PADDR bit to 1 makes the corresponding port A pin an output pin, while clearing the bit to 0 makes the pin an input pin.

PADDR is initialized to H'00 by a reset and in hardware standby mode. It retains its prior state in software standby mode.

#### Port A Output Data Register (PAODR)

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

|               | PA7ODR | PA6ODR | PA5ODR | PA4ODR | PA3ODR | PA2ODR | PA10DR | PA0ODR |

| Initial value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| Read/Write    | R/W    |

PAODR is an 8-bit readable/writable register that stores output data for the port A pins (PA7 to PA0). PAODR can always be read or written to, regardless of the contents of PADDR.

#### 9.1.3 Pin Configuration

Table 9.1 shows the PWM output pin.

#### Table 9.1Pin Configuration

| Name                   | Abbreviation | I/O    | Function                       |

|------------------------|--------------|--------|--------------------------------|

| PWM output pin 0 to 15 | PW0 to PW15  | Output | PWM timer pulse output 0 to 15 |

#### 9.1.4 Register Configuration

Table 9.2 lists the registers of the PWM timer module.

#### Table 9.2 PWM Timer Module Registers

| Name                             | Abbreviation       | R/W | Initial Value | Address <sup>*1</sup> |

|----------------------------------|--------------------|-----|---------------|-----------------------|

| PWM register select              | PWSL               | R/W | H'20          | H'FFD6                |

| PWM data registers 0 to 15       | PWDR0 to<br>PWDR15 | R/W | H'00          | H'FFD7                |

| PWM data polarity register A     | PWDPRA             | R/W | H'00          | H'FFD5                |

| PWM data polarity register B     | PWDPRB             | R/W | H'00          | H'FFD4                |

| PWM output enable register A     | PWOERA             | R/W | H'00          | H'FFD3                |

| PWM output enable register B     | PWOERB             | R/W | H'00          | H'FFD2                |

| Port 1 data direction register   | P1DDR              | W   | H'00          | H'FFB0                |

| Port 2 data direction register   | P2DDR              | W   | H'00          | H'FFB1                |

| Port 1 data register             | P1DR               | R/W | H'00          | H'FFB2                |

| Port 2 data register             | P2DR               | R/W | H'00          | H'FFB3                |

| Peripheral clock select register | PCSR               | R/W | H'00          | H'FF82*2              |

| Module stop control register     | MSTPCRH            | R/W | H'3F          | H'FF86                |

|                                  | MSTPCRL            | R/W | H'FF          | H'FF87                |

Note: 1. Lower 16 bits of the address.

2. Some registers in the 8-bit timer are assigned in the addresses as other registers. In this case, register selection is performed by the FLSHE bit in the serial timer control register (STCR).

#### 14.5.3 Switching between Watchdog Timer Mode and Interval Timer Mode

If the mode is switched from watchdog timer to interval timer, or vice versa, while the WDT is operating, errors could occur in the incrementation. Software must stop the watchdog timer (by clearing the TME bit to 0) before switching the mode.

#### 14.5.4 System Reset by **RESO** Signal

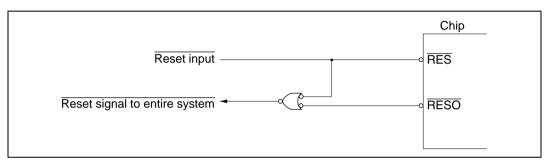

If the  $\overline{\text{RESO}}$  output signal is input to the chip's  $\overline{\text{RES}}$  pin, the chip will not be initialized correctly. Ensure that the  $\overline{\text{RESO}}$  signal is not logically input to the chip's  $\overline{\text{RES}}$  pin. When resetting the entire system with the  $\overline{\text{RESO}}$  signal, use a circuit such as that shown in figure 14.8.

Figure 14.8 Sample Circuit for System Reset by RESO Signal

# 14.5.5 Counter Value in Transitions between High-Speed Mode, Subactive Mode, and Watch Mode

If the mode is switched between high-speed mode and subactive mode or between high-speed mode and watch mode when WDT1 is used as a realtime clock counter, an error will occur in the counter value when the internal clock is switched.

When the mode is switched from high-speed mode to subactive mode or watch mode, the increment timing is delayed by approximately 2 or 3 clock cycles when the WDT1 control clock is switched from the main clock to the subclock.

Also, since the main clock oscillator is halted during subclock operation, when the mode is switched from watch mode or subactive mode to high-speed mode, the clock is not supplied until internal oscillation stabilizes. As a result, after oscillation is started, counter incrementing is halted during the oscillation stabilization time set by bits STS2 to STS0 in SBYCR, and there is a corresponding discrepancy in the counter value.

## Renesas

#### **Break Detection and Processing**

When a framing error (FER) is detected, a break can be detected by reading the RxD pin value directly. In a break, the input from the RxD pin becomes all 0s, and so the FER flag is set, and the parity error flag (PER) may also be set.

Note that, since the SCI continues the receive operation after receiving a break, even if the FER flag is cleared to 0, it will be set to 1 again.

#### Sending a Break

The TxD pin has a dual function as an I/O port whose direction (input or output) is determined by DR and DDR. This feature can be used to send a break.

Between serial transmission initialization and setting of the TE bit to 1, the mark state is replaced by the value of DR (the pin does not function as the TxD pin until the TE bit is set to 1). Consequently, DDR and DR for the port corresponding to the TxD pin should first be set to 1.

To send a break during serial transmission, first clear DR to 0, then clear the TE bit to 0.

When the TE bit is cleared to 0, the transmitter is initialized regardless of the current transmission state, the TxD pin becomes an I/O port, and 0 is output from the TxD pin.

#### **Receive Error Flags and Transmit Operations (Synchronous Mode Only)**

Transmission cannot be started when a receive error flag (ORER, PER, or FER) is set to 1, even if the TDRE flag is cleared to 0. Be sure to clear the receive error flags to 0 before starting transmission.

Note also that receive error flags cannot be cleared to 0 even if the RE bit is cleared to 0.

#### Receive Data Sampling Timing and Reception Margin in Asynchronous Mode

In asynchronous mode, the SCI operates on a base clock with a frequency of 16 times the transfer rate.

In reception, the SCI samples the falling edge of the start bit using the base clock, and performs internal synchronization. Receive data is latched internally at the rising edge of the 8th pulse of the base clock. This is illustrated in figure 15.23.

## Section 16 I<sup>2</sup>C Bus Interface [Option]

A two-channel  $I^2C$  bus interface is available as an option in the H8S/2148 Group and H8S/2147N. The  $I^2C$  bus interface is not available for the H8S/2144 Group. Observe the following notes when using this option.

1. For mask-ROM versions, a W is added to the part number in products in which this optional function is used.

Examples: HD6432147SWFA

2. The product number is identical for F-ZTAT versions. However, be sure to inform your Renesas sales representative if you will be using this option.

## 16.1 Overview

A two-channel I<sup>2</sup>C bus interface is available for the H8S/2148 Group and H8S/2147N as an option. The I<sup>2</sup>C bus interface conforms to and provides a subset of the Philips I<sup>2</sup>C bus (inter-IC bus) interface functions. The register configuration that controls the I<sup>2</sup>C bus differs partly from the Philips configuration, however.

Each I<sup>2</sup>C bus interface channel uses only one data line (SDA) and one clock line (SCL) to transfer data, saving board and connector space.

#### 16.1.1 Features

- Selection of addressing format or non-addressing format

- I<sup>2</sup>C bus format: addressing format with acknowledge bit, for master/slave operation

- Serial format: non-addressing format without acknowledge bit, for master operation only

- Conforms to Philips I<sup>2</sup>C bus interface (I<sup>2</sup>C bus format)

- Two ways of setting slave address (I<sup>2</sup>C bus format)

- Start and stop conditions generated automatically in master mode (I<sup>2</sup>C bus format)

- Selection of acknowledge output levels when receiving (I<sup>2</sup>C bus format)

- Automatic loading of acknowledge bit when transmitting (I<sup>2</sup>C bus format)

- Wait function in master mode (I<sup>2</sup>C bus format)

A wait can be inserted by driving the SCL pin low after data transfer, excluding acknowledgement. The wait can be cleared by clearing the interrupt flag.

• Wait function in slave mode (I<sup>2</sup>C bus format)

A wait request can be generated by driving the SCL pin low after data transfer, excluding acknowledgement. The wait request is cleared when the next transfer becomes possible.

- Three interrupt sources

- Data transfer end (including transmission mode transition with I<sup>2</sup>C bus format and address reception after loss of master arbitration)

- Address match: when any slave address matches or the general call address is received in slave receive mode (I<sup>2</sup>C bus format)

- Stop condition detection

- Selection of 16 internal clocks (in master mode)

- Direct bus drive (with SCL and SDA pins)

- Two pins—P52/SCL0 and P97/SDA0—(normally NMOS push-pull outputs) function as NMOS open-drain outputs when the bus drive function is selected.

- Two pins—P86/SCL1 and P42/SDA1—(normally CMOS pins) function as NMOS-only outputs when the bus drive function is selected.

- Automatic switching from formatless mode to I<sup>2</sup>C bus format (channel 0 only)

- Formatless operation (no start/stop conditions, non-addressing mode) in slave mode

- Operation using a common data pin (SDA) and independent clock pins (VSYNCI, SCL)

- Automatic switching from formatless mode to I<sup>2</sup>C bus format on the fall of the SCL pin

#### 16.1.2 Block Diagram

Figure 16.1 shows a block diagram of the  $I^2C$  bus interface.

Figure 16.2 shows an example of I/O pin connections to external circuits. Channel 0 I/O pins and channel 1 I/O pins differ in structure, and have different specifications for permissible applied voltages. For details, see section 26, Electrical Characteristics.

### **19.2** Register Descriptions

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               |     |     |     |     |     |     |     |     |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read/Write    | R/W |

#### 19.2.1 D/A Data Registers 0 and 1 (DADR0, DADR1)

D/A data registers 0 and 1 (DADR0 and DADR1) are 8-bit readable/writable registers that store data to be converted. When analog output is enabled, the value in the D/A data register is converted and output continuously at the analog output pin.

The D/A data registers are initialized to H'00 by a reset and in hardware standby mode.

#### 19.2.2 D/A Control Register (DACR)

| Bit           | 7     | 6     | 5   | 4 | 3 | 2 | 1 | 0 |

|---------------|-------|-------|-----|---|---|---|---|---|

|               | DAOE1 | DAOE0 | DAE | _ | _ | _ | _ | _ |

| Initial value | 0     | 0     | 0   | 1 | 1 | 1 | 1 | 1 |

| Read/Write    | R/W   | R/W   | R/W | _ | _ | _ | _ | _ |

DACR is an 8-bit readable/writable register that controls the operation of the D/A converter module.

DACR is initialized to H'1F by a reset and in hardware standby mode.

Bit 7—D/A Output Enable 1 (DAOE1): Controls D/A conversion and analog output.

Bit 7

| DAOE1 | Description                                                         |                 |

|-------|---------------------------------------------------------------------|-----------------|

| 0     | Analog output DA1 is disabled                                       | (Initial value) |

| 1     | D/A conversion is enabled on channel 1. Analog output DA1 is enable | d               |

Bit 7—A/D End Flag (ADF): Status flag that indicates the end of A/D conversion.

#### Bit 7

| ADF | Description                                                                 |  |  |  |  |  |  |

|-----|-----------------------------------------------------------------------------|--|--|--|--|--|--|

| 0   | [Clearing conditions] (Initial value)                                       |  |  |  |  |  |  |

|     | <ul> <li>When 0 is written in the ADF flag after reading ADF = 1</li> </ul> |  |  |  |  |  |  |

|     | When the DTC is activated by an ADI interrupt and ADDR is read              |  |  |  |  |  |  |

| 1   | [Setting conditions]                                                        |  |  |  |  |  |  |

|     | Single mode: When A/D conversion ends                                       |  |  |  |  |  |  |

|     | Scan mode: When A/D conversion ends on all specified channels               |  |  |  |  |  |  |

**Bit 6—A/D Interrupt Enable (ADIE):** Selects enabling or disabling of interrupt (ADI) requests at the end of A/D conversion.

Bit 6

| ADIE | Description                                            |                 |

|------|--------------------------------------------------------|-----------------|

| 0    | A/D conversion end interrupt (ADI) request is disabled | (Initial value) |

| 1    | A/D conversion end interrupt (ADI) request is enabled  |                 |

**Bit 5—A/D Start (ADST):** Selects starting or stopping of A/D conversion. Holds a value of 1 during A/D conversion.

The ADST bit can be set to 1 by software, a timer conversion start trigger, or the A/D external trigger input pin ( $\overline{ADTRG}$ ).

#### Bit 5

| ADST | Description   |                                                                                                                                                     |                      |

|------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 0    | A/D conversio | n stopped                                                                                                                                           | (Initial value)      |

| 1    | Single mode:  | A/D conversion is started. Cleared to 0 automatica<br>on the specified channel ends                                                                 | ally when conversion |

|      | Scan mode:    | A/D conversion is started. Conversion continues s selected channels until ADST is cleared to 0 by so transition to standby mode or module stop mode |                      |

**Bit 4—Scan Mode (SCAN):** Selects single mode or scan mode as the A/D conversion operating mode. See section 20.4, Operation, for single mode and scan mode operation. Only set the SCAN bit while conversion is stopped.

## Section 21 RAM

## 21.1 Overview

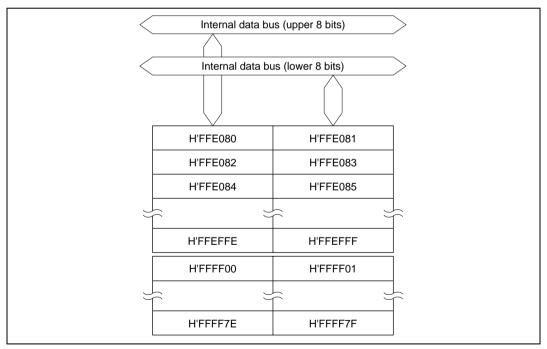

The H8S/2148, H8S/2144, and H8S/2143 have 4 kbytes of on-chip high-speed static RAM, and the H8S/2147, H8S/2147N, and H8S/2142 have 2 kbytes. The on-chip RAM is connected to the CPU by a 16-bit data bus, enabling both byte data and word data to be accessed in one state. This makes it possible to perform fast word data transfer.

The on-chip RAM can be enabled or disabled by means of the RAM enable bit (RAME) in the system control register (SYSCR).

#### 21.1.1 Block Diagram

Figure 21.1 shows a block diagram of the on-chip RAM.

Figure 21.1 Block Diagram of RAM (H8S/2148, H8S/2144, H8S/2143)

## Renesas

#### Notes on Use of Auto-Erase-Program Mode

- Auto-erase mode supports only entire memory erasing.

- Do not perform a command write during auto-erasing.

- Confirm normal end of auto-erasing by checking FO6. Alternatively, status read mode can also be used for this purpose (FO7 status polling uses the auto-erase operation end identification pin).

- The status polling FO6 and FO7 pin information is retained until the next command write. Until the next command write is performed, reading is possible by enabling  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$ .

#### 23.10.7 Status Read Mode

- Status read mode is used to identify what type of abnormal end has occurred. Use this mode when an abnormal end occurs in auto-program mode or auto-erase mode.

- The return code is retained until a command write for other than status read mode is performed.

#### Table 23.18 AC Characteristics in Status Read Mode

Conditions:  $V_{cc} = 3.3 \text{ V} \pm 0.3 \text{ V}$ ,  $V_{ss} = 0 \text{ V}$ ,  $T_a = 25^{\circ}\text{C} \pm 5^{\circ}\text{C}$

| Item                 | Symbol            | Min | Max | Unit |

|----------------------|-------------------|-----|-----|------|

| Command write cycle  | t <sub>nxtc</sub> | 20  | _   | μs   |

| CE hold time         | t <sub>ceh</sub>  | 0   | _   | ns   |

| CE setup time        | t <sub>ces</sub>  | 0   |     | ns   |

| Data hold time       | t <sub>dh</sub>   | 50  | —   | ns   |

| Data setup time      | t <sub>ds</sub>   | 50  | —   | ns   |

| Write pulse width    | t <sub>wep</sub>  | 70  |     | ns   |

| OE output delay time | t <sub>oe</sub>   | _   | 150 | ns   |

| Disable delay time   | t <sub>df</sub>   | _   | 100 | ns   |

| CE output delay time | t <sub>ce</sub>   | _   | 150 | ns   |

| WE rise time         | t <sub>r</sub>    |     | 30  | ns   |

| WE fall time         | t <sub>r</sub>    | —   | 30  | ns   |

## Renesas

| Register | Bit     | Module                                                                                                                                                       |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSTPCRH  | MSTP15  | _                                                                                                                                                            |

|          | MSTP14* | Data transfer controller (DTC)                                                                                                                               |

|          | MSTP13  | 16-bit free-running timer (FRT)                                                                                                                              |

|          | MSTP12  | 8-bit timer (TMR0, TMR1)                                                                                                                                     |

|          | MSTP11  | 8-bit PWM timer (PWM), 14-bit PWM timer (PWMX)                                                                                                               |

|          | MSTP10  | D/A converter                                                                                                                                                |

|          | MSTP9   | A/D converter                                                                                                                                                |

|          | MSTP8   | 8-bit timers (TMRX, TMRY), timer connection                                                                                                                  |

| MSTPCRL  | MSTP7   | Serial communication interface 0 (SCI0)                                                                                                                      |

|          | MSTP6   | Serial communication interface 1 (SCI1)                                                                                                                      |

|          | MSTP5   | Serial communication interface 2 (SCI2)                                                                                                                      |

|          | MSTP4*  | I <sup>2</sup> C bus interface (IIC) channel 0 (option)                                                                                                      |

|          | MSTP3*  | I <sup>2</sup> C bus interface (IIC) channel 1 (option)                                                                                                      |

|          | MSTP2   | Host interface (HIF), keyboard matrix interrupt mask register (KMIMR, KMIMRA), port 6 MOS pull-up control register (KMPCR), keyboard buffer controller (PS2) |

|          | MSTP1*  | _                                                                                                                                                            |

|          | MSTP0*  | -                                                                                                                                                            |

#### Table 25.4 MSTP Bits and Corresponding On-Chip Supporting Modules

Notes: Do not set bit 15 to 1. Bits 1 and 0 can be read or written to, but do not affect operation.

\* Must be set to 1 in the H8S/2144 Group and H8S/2147N.

#### 25.5.2 Usage Note

If there is conflict between DTC module stop mode setting and a DTC bus request, the bus request has priority and the MSTP bit will not be set to 1.

Write 1 to the MSTP bit again after the DTC bus cycle.

When using the H8S/2144 Group and H8S/2147N, the MSTP bits for nonexistent modules must be set to 1.

| IDR3—Input D<br>IDR4—Input D | H'FE84<br>H'FE8C |      |      |      | HIF<br>HIF |      |      |      |   |

|------------------------------|------------------|------|------|------|------------|------|------|------|---|

| Bit                          | 7                | 6    | 5    | 4    | 3          | 2    | 1    | 0    | _ |

|                              | IDR7             | IDR6 | IDR5 | IDR4 | IDR3       | IDR2 | IDR1 | IDR0 |   |

| Initial value                | _                |      | _    |      | _          |      | _    |      | - |

| Slave R/W                    | R                | R    | R    | R    | R          | R    | R    | R    |   |

| Host R/W                     | W                | W    | W    | W    | W          | W    | W    | W    |   |

|                              |                  |      |      |      |            |      |      |      |   |

Stores host data bus contents at rise of  $\overline{\text{IOW}}$  when  $\overline{\text{CS}}$  is low

| ODR3—Output Data Register 3<br>ODR4—Output Data Register 4 |      |      |      | H'FE85<br>H'FE8D |      |      |      |      | HIF<br>HIF |  |

|------------------------------------------------------------|------|------|------|------------------|------|------|------|------|------------|--|

| Bit                                                        | 7    | 6    | 5    | 4                | 3    | 2    | 1    | 0    | _          |  |

|                                                            | ODR7 | ODR6 | ODR5 | ODR4             | ODR3 | ODR2 | ODR1 | ODR0 |            |  |

| Initial value                                              |      |      |      |                  | _    |      |      |      | _          |  |

| Slave R/W                                                  | R/W  | R/W  | R/W  | R/W              | R/W  | R/W  | R/W  | R/W  |            |  |

| Host R/W                                                   | R    | R    | R    | R                | R    | R    | R    | R    |            |  |

|                                                            |      |      |      |                  |      |      |      |      |            |  |

ODR contents are output to the host data bus when HA0 is low,  $\overline{\text{CS}}$  is low, and  $\overline{\text{IOR}}$  is low

| ICDR1—I <sup>2</sup> C B<br>ICDR0—I <sup>2</sup> C B |             |        |        |        | IC1<br>IC0 |        |          |        |   |

|------------------------------------------------------|-------------|--------|--------|--------|------------|--------|----------|--------|---|

| Bit                                                  | 7           | 6      | 5      | 4      | 3          | 2      | 1        | 0      |   |

|                                                      | ICDR7       | ICDR6  | ICDR5  | ICDR4  | ICDR3      | ICDR2  | ICDR1    | ICDR0  |   |

| Initial value                                        | _           |        | —      |        |            |        |          | _      | 1 |

| Read/Write                                           | R/W         | R/W    | R/W    | R/W    | R/W        | R/W    | R/W      | R/W    |   |

| ICDRR                                                |             |        |        |        |            |        |          |        |   |

| Bit                                                  | 7           | 6      | 5      | 4      | 3          | 2      | 1        | 0      | , |

|                                                      | ICDRR7      | ICDRR6 | ICDRR5 | ICDRR4 | ICDRR3     | ICDRR2 | ICDRR1   | ICDRR0 |   |

| Initial value                                        | —           | —      | —      | —      | —          | —      | —        | —      |   |

| Read/Write                                           | R           | R      | R      | R      | R          | R      | R        | R      |   |

| ICDRS                                                |             |        |        |        |            |        |          |        |   |

| Bit                                                  | 7           | 6      | 5      | 4      | 3          | 2      | 1        | 0      | 1 |

|                                                      | ICDRS7      | ICDRS6 | ICDRS5 | ICDRS4 | ICDRS3     | ICDRS2 | ICDRS1   | ICDRS0 |   |

| Initial value                                        | —           | _      | —      | —      | —          | —      | —        | —      |   |

| Read/Write                                           | —           | —      | —      | —      | —          | —      | —        | —      |   |

| ICDRT                                                |             |        |        |        |            |        |          |        |   |

| Bit                                                  | 7           | 6      | 5      | 4      | 3          | 2      | 1        | 0      | 1 |

|                                                      | ICDRT7      | ICDRT6 | ICDRT5 | ICDRT4 | ICDRT3     | ICDRT2 | ICDRT1   | ICDRT0 |   |

| Initial value                                        | —           | —      | —      | —      | —          | —      | —        | —      |   |

| Read/Write                                           | W           | W      | W      | W      | W          | W      | W        | W      |   |

| TDRE, RDRI                                           | - (internal | flags) |        |        |            |        |          |        |   |

| Bit                                                  |             |        |        |        |            |        | <u> </u> | _      | 1 |

|                                                      |             |        |        |        |            |        | TDRE     | RDRF   | ] |

| Initial value<br>Read/Write                          |             |        |        |        |            |        | 0        | 0      |   |

| Read/write                                           |             |        |        |        |            |        | _        | _      |   |

Note: For details, see section 16.2.1, I<sup>2</sup>C Bus Data Register (ICDR).

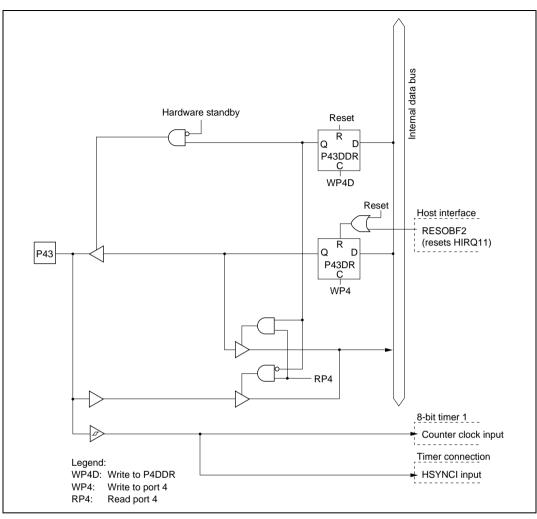

Figure C.9 Port 4 Block Diagram (Pin P43)

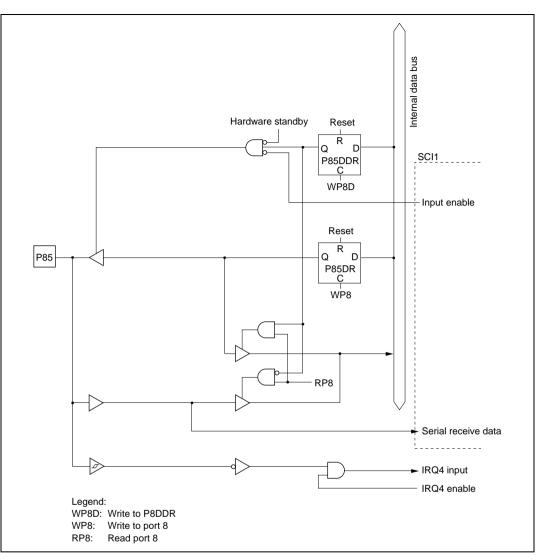

Figure C.27 Port 8 Block Diagram (Pin P85)