# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8A                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 16MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 16                                                                    |

| Program Memory Size        | 8KB (8K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 640 x 8                                                               |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 5x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                       |

| Supplier Device Package    | 20-TSSOP                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af6223pcu |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.13 Analog-to-digital converter (ADC1)

The STM8AF6213, STM8AF6223, STM8AF6223A and STM8AF6226 products contain a 10-bit successive approximation A/D converter (ADC1) with up to 7 external and 1 internal multiplexed input channels and the following main features:

- Input voltage range: 0 to V<sub>DD</sub>

- Input voltage range: 0 to V<sub>DDA</sub>

- Conversion time: 14 clock cycles

- Single and continuous and buffered continuous conversion modes

- Buffer size (n x 10 bits) where n = number of input channels

- Scan mode for single and continuous conversion of a sequence of channels

- Analog watchdog capability with programmable upper and lower thresholds

- Internal reference voltage on channel AIN7

- Analog watchdog interrupt

- External trigger input

- Trigger from TIM1 TRGO

- End of conversion (EOC) interrupt

Note: Additional AIN12 analog input is not selectable in ADC scan mode or with analog watchdog. Values converted from AIN12 are stored only into the ADC\_DRH/ADC\_DRL registers.

#### Internal bandgap reference voltage

Channel AIN7 is internally connected to the internal bandgap reference voltage. The internal bandgap reference is constant and can be used, for example, to monitor  $V_{DD}$ . It is independent of variations in  $V_{DD}$  and ambient temperature  $T_A$ .

# 4.14 Communication interfaces

The following communication interfaces are implemented:

- LINUART: Full feature UART, synchronous mode, SPI master mode, Smartcard mode, IrDA mode, single wire mode, LIN2.2 capability

- SPI: full and half-duplex, 8 Mbit/s

- I<sup>2</sup>C: up to 400 Kbit/s

Some peripheral names differ between the datasheet and STM8S series and STM8AF series 8-bit microcontrollers reference manual, RM0016 (see *Table 4*).

| Table 4. Communication | peripheral | naming | correspondence |

|------------------------|------------|--------|----------------|

|------------------------|------------|--------|----------------|

| Peripheral name in datasheet | Peripheral name in reference manual<br>(RM0016) |

|------------------------------|-------------------------------------------------|

| LINUART                      | UART4                                           |

#### Asynchronous communication (UART mode)

- Full duplex communication NRZ standard format (mark/space)

- Programmable transmit and receive baud rates up to 1 Mbit/s (f<sub>CPU</sub>/16) and capable of following any standard baud rate regardless of the input frequency

- Separate enable bits for transmitter and receiver

- Two receiver wakeup modes:

- Address bit (MSB)

- Idle line (interrupt)

- Transmission error detection with interrupt generation

- Parity control

#### Synchronous communication

- Full duplex synchronous transfers

- SPI master operation

- 8-bit data communication

- Maximum speed: 1 Mbit/s at 16 MHz (f<sub>CPU</sub>/16)

### 4.14.2 Serial peripheral interface (SPI)

- Maximum speed: 8 Mbit/s (f<sub>MASTER</sub>/2) both for master and slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on two lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- CRC calculation

- 1 byte Tx and Rx buffer

- Slave /master selection input pin

### 4.14.3 Inter integrated circuit (I<sup>2</sup>C) interface

- I<sup>2</sup>C master features:

- Clock generation

- Start and stop generation

- I<sup>2</sup>C slave features:

- Programmable I<sup>2</sup>C address detection

- Stop bit detection

- Generation and detection of 7-bit/10-bit addressing and general call

- Supports different communication speeds:

- Standard speed (up to 100 kHz),

- Fast speed (up to 400 kHz)

# 5 Pinout and pin description

The following table presents the meaning of the abbreviations in use in the pin description tables in this section.

| Туре             | I= input, O                                                                                                                                                   | = input, O = output, S = power supply                                                                                                                                                                 |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Level            | Input                                                                                                                                                         | CM = CMOS (standard for all I/Os)                                                                                                                                                                     |  |  |  |  |  |  |

|                  | Output                                                                                                                                                        | HS = High sink                                                                                                                                                                                        |  |  |  |  |  |  |

| Output speed     | O2 = Fast (<br>O3 = Fast/s                                                                                                                                    | O1 = Slow (up to 2 MHz)<br>O2 = Fast (up to 10 MHz)<br>O3 = Fast/slow programmability with slow as default state after reset<br>O4 = Fast/slow programmability with fast as default state after reset |  |  |  |  |  |  |

| Port and control | Input                                                                                                                                                         | float = floating, wpu = weak pull-up                                                                                                                                                                  |  |  |  |  |  |  |

| configuration    | Output                                                                                                                                                        | T = true open drain, OD = open drain, PP = push pull                                                                                                                                                  |  |  |  |  |  |  |

| Reset state      | Bold X (pin state after internal reset release).<br>Unless otherwise specified, the pin state is the same during the reset patter the internal reset release. |                                                                                                                                                                                                       |  |  |  |  |  |  |

| Table 5. Legend/abbreviations | for pinout tables |

|-------------------------------|-------------------|

|-------------------------------|-------------------|

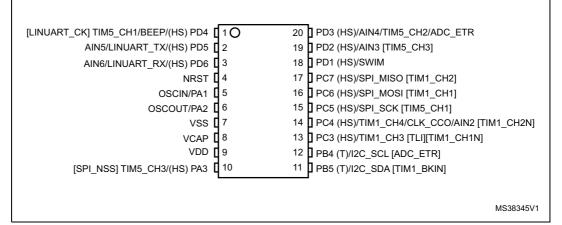

# 5.1 TSSOP20 pinouts and pin descriptions

#### Figure 3. STM8AF6213/STM8AF6223 TSSOP20 pinout

1. (HS) high sink capability.

2. (T) true open drain (P-buffer and protection diode to  $V_{\text{DD}}$  not implemented).

3. [] alternate function remapping option (if the same alternate function is shown twice, it indicates an exclusive choice not a duplication of the function).

|       |                                                |      |          | Input | t              |                          | Out   | put              |    |                                   |                                                             |                                                                                |

|-------|------------------------------------------------|------|----------|-------|----------------|--------------------------|-------|------------------|----|-----------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------|

| TSSOP | Pin name                                       | Туре | floating | ndm   | Ext. interrupt | High sink <sup>(1)</sup> | Speed | OD               | ЪР | Main<br>function<br>(after reset) | Default<br>alternate<br>function                            | Alternate<br>function<br>after remap<br>[option bit]                           |

| 10    | PA3/ TIM5_CH3<br>[SPI_NSS]                     | I/O  | x        | x     | х              | HS                       | O3    | x                | х  | Port A3                           | Timer 5<br>channel 3                                        | SPI master/<br>slave select<br>[AFR1]                                          |

| 11    | PB5/ I2C_SDA<br>[TIM1_BKIN]                    | I/O  | x        | -     | х              | -                        | 01    | T <sup>(3)</sup> | -  | Port B5                           | I2C data                                                    | Timer 1 -<br>break input<br>[AFR4]                                             |

| 12    | PB4/ I2C_SCL<br>[ADC_ETR]                      | I/O  | x        | -     | х              | -                        | O1    | T <sup>(3)</sup> | -  | Port B4                           | I2C clock                                                   | ADC<br>external<br>trigger<br>[AFR4]                                           |

| 13    | PC3/<br>TIM1_CH3/[TLI]/[<br>TIM1_CH1N]         | I/O  | X        | x     | x              | HS                       | O3    | x                | x  | Port C3                           | Timer 1 -<br>channel 3                                      | Top level<br>interrupt<br>[AFR3]<br>Timer 1<br>inverted<br>channel 1<br>[AFR7] |

| 14    | PC4/ TIM1_CH4/<br>CLK_CCO/AIN2/[<br>TIM1_CH2N] | I/O  | x        | x     | x              | HS                       | O3    | x                | x  | Port C4                           | Timer 1 -<br>channel 4<br>/configurabl<br>e clock<br>output | Analog<br>input 2<br>[AFR2]Time<br>r 1 inverted<br>channel 2<br>[AFR7]         |

| 15    | PC5/SPI_SCK<br>[TIM5_CH1]                      | I/O  | X        | x     | х              | HS                       | O3    | x                | х  | Port C5                           | SPI clock                                                   | Timer 5<br>channel 1<br>[AFR0]                                                 |

| 16    | PC6/ SPI_MOSI<br>[TIM1_CH1]                    | I/O  | x        | x     | х              | HS                       | O3    | x                | х  | Port C6                           | PI master<br>out/slave in                                   | Timer 1<br>channel 1<br>[AFR0]                                                 |

| 17    | PC7/ SPI_MISO<br>[TIM1_CH2]                    | I/O  | x        | х     | х              | HS                       | O3    | x                | х  | Port C7                           | SPI master<br>in/ slave out                                 | Timer 1<br>channel<br>2[AFR0]                                                  |

| 18    | PD1/ SWIM <sup>(4)</sup>                       | I/O  | X        | х     | х              | HS                       | 04    | х                | х  | Port D1                           | SWIM data interface                                         | -                                                                              |

### Table 6. STM8AF6213/STM8AF6223 TSSOP20 pin description (continued)

|                   |                                           |      |          | Inpu | t              |                          | Ou    | tput |    |                                   |                                                                         |                                                               |

|-------------------|-------------------------------------------|------|----------|------|----------------|--------------------------|-------|------|----|-----------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------|

| LQFP32<br>VFQPN32 | Pin name                                  | Туре | floating | ndw  | Ext. interrupt | High sink <sup>(1)</sup> | Speed | QD   | dd | Main<br>function<br>(after reset) | Default<br>alternate<br>function                                        | Alternate<br>function<br>after remap<br>[option bit]          |

| 27                | PD2/[AIN3]<br>[TIM5_CH3]                  | I/O  | x        | x    | x              | HS                       | O3    | х    | x  | Port D2                           | -                                                                       | Analog input<br>3 [AFR2]<br>Timer 52 -<br>channel 3<br>[AFR1] |

| 28                | PD3/ AIN4/<br>TIM5_CH2/<br>ADC_ETR        | I/O  | X        | x    | x              | HS                       | O3    | х    | x  | Port D3                           | Analog input<br>4 Timer 52 -<br>channel<br>2/ADC<br>external<br>trigger | -                                                             |

| 29                | PD4/<br>TIM5_CH1/<br>BEEP<br>[LINUART_CK] | I/O  | x        | x    | x              | HS                       | O3    | х    | x  | Port D4                           | Timer 5 -<br>channel<br>1/BEEP<br>output                                | LINUART<br>clock [AFR2]                                       |

| 30                | PD5/ AIN5/<br>LINUART_TX                  | I/O  | x        | x    | х              | HS                       | О3    | х    | x  | Port D5                           | Analog input<br>5/ LINUART<br>data transmit                             | -                                                             |

| 31                | PD6/ AIN6/<br>LINUART_RX                  | I/O  | x        | x    | x              | нs                       | О3    | х    | x  | Port D6                           | Analog input<br>6/ LINUART<br>data receive                              | -                                                             |

| 32                | PD7/ TLI<br>[TIM1_CH4]                    | I/O  | x        | x    | х              | HS                       | О3    | х    | x  | Port D7                           | Top level<br>interrupt                                                  | Timer 1 -<br>channel 4<br>[AFR6]                              |

#### Table 8. STM8AF6226 LQFP32/VFQPN32 pin description (continued)

1. I/O pins used simultaneously for high current source/sink must be uniformly spaced around the package. In addition, the total driven current must respect the absolute maximum ratings (see *Section 9.2: Absolute maximum ratings*).

2. When the MCU is in Halt/Active-halt mode, PA1 is automatically configured in input weak pull-up and cannot be used for waking up the device. In this mode, the output state of PA1 is not driven. It is recommended to use PA1 only in input mode if Halt/Active-halt is used in the application.

3. In the open-drain output column, 'T' defines a true open-drain I/O (P-buffer, weak pull-up, and protection diode to VDD are not implemented).

4. The PD1 pin is in input pull-up during the reset phase and after internal reset release.

# 5.3 Alternate function remapping

As shown in the rightmost column of *Table 6*, *Table 7* and *Table 8* some alternate functions can be remapped at different I/O ports by programming one of eight AFR (alternate function remap) option bits. Refer to *Section 8: Option bytes on page 46*. When the remapping option is active, the default alternate function is no longer available.

To use an alternate function, the corresponding peripheral must be enabled in the peripheral registers.

Alternate function remapping does not effect GPIO capabilities of the I/O ports (see the GPIO section of STM8S series and STM8AF series 8-bit microcontrollers reference manual, RM0016).

| Address                   | Block   | Register label          | Register name                | Reset<br>status |  |  |  |  |  |  |

|---------------------------|---------|-------------------------|------------------------------|-----------------|--|--|--|--|--|--|

| 0x00 5230                 |         | UART4_SR                | LINUART status register      | 0xC0            |  |  |  |  |  |  |

| 0x00 5231                 |         | UART4_DR                | LINUART data register        | 0xXX            |  |  |  |  |  |  |

| 0x00 5232                 |         | UART4_BRR1              | LINUART baud rate register 1 | 0x00            |  |  |  |  |  |  |

| 0x00 5233                 |         | UART4_BRR2              | LINUART baud rate register 2 | 0x00            |  |  |  |  |  |  |

| 0x00 5234                 |         | UART4_CR1               | LINUART control register 1   | 0x00            |  |  |  |  |  |  |

| 0x00 5235                 |         | UART4_CR2               | LINUART control register 2   | 0x00            |  |  |  |  |  |  |

| 0x00 5236                 | LINUART | UART4_CR3               | LINUART control register 3   | 0x00            |  |  |  |  |  |  |

| 0x00 5237                 |         | UART4_CR4               | LINUART control register 4   | 0x00            |  |  |  |  |  |  |

| 0x00 5238                 |         |                         | Reserved                     |                 |  |  |  |  |  |  |

| 0x00 5239                 |         | UART4_CR6               | LINUART control register 6   | 0x00            |  |  |  |  |  |  |

| 0x00 523A                 |         | UART4_GTR               | LINUART guard time register  | 0x00            |  |  |  |  |  |  |

| 0x00 523B                 |         | UART4_PSCR              | LINUART prescaler            | 0x00            |  |  |  |  |  |  |

| 0x00 523C to<br>0x00 523F |         | Reserved area (20 byte) |                              |                 |  |  |  |  |  |  |

| Table 11. Gener | al hardware red | nister map | (continued) |

|-----------------|-----------------|------------|-------------|

|                 | ur maranare reg | giotor mup | (continueu) |

# 6.2.2 CPU/SWIM/debug module/interrupt controller registers

| Address                   | Block              | Register label | Register name                          | Reset<br>status      |      |

|---------------------------|--------------------|----------------|----------------------------------------|----------------------|------|

| 0x00 7F00                 |                    | А              | Accumulator                            | 0x00                 |      |

| 0x00 7F01                 | CPU <sup>(1)</sup> | PCE            | Program counter extended               | 0x00                 |      |

| 0x00 7F02                 |                    |                | PCH                                    | Program counter high | 0x00 |

| 0x00 7F03                 |                    | PCL            | Program counter low                    | 0x00                 |      |

| 0x00 7F04                 |                    | ХН             | X index register high                  | 0x00                 |      |

| 0x00 7F05                 |                    | XL             | X index register low                   | 0x00                 |      |

| 0x00 7F06                 |                    | YH             | Y index register high                  | 0x00                 |      |

| 0x00 7F07                 |                    | YL             | Y index register low                   | 0x00                 |      |

| 0x00 7F08                 |                    | SPH            | Stack pointer high                     | 0x03                 |      |

| 0x00 7F09                 |                    | SPL            | Stack pointer low                      | 0xFF                 |      |

| 0x00 7F0A                 |                    | CCR            | Condition code register                | 0x28                 |      |

| 0x00 7F0B to<br>0x00 7F5F |                    |                | Reserved area (85 byte)                | ·                    |      |

| 0x00 7F60                 | CPU                | CFG_GCR        | Global configuration register          | 0x00                 |      |

| 0x00 7F70                 |                    | ITC_SPR1       | Interrupt software priority register 1 | 0xFF                 |      |

| 0x00 7F71                 |                    | ITC_SPR2       | Interrupt software priority register 2 | 0xFF                 |      |

| 0x00 7F72                 |                    | ITC_SPR3       | Interrupt software priority register 3 | 0xFF                 |      |

| 0x00 7F73                 | ITC                | ITC_SPR4       | Interrupt software priority register 4 | 0xFF                 |      |

| 0x00 7F74                 | ne                 | ITC_SPR5       | Interrupt software priority register 5 | 0xFF                 |      |

| 0x00 7F75                 |                    | ITC_SPR6       | Interrupt software priority register 6 | 0xFF                 |      |

| 0x00 7F76                 |                    | ITC_SPR7       | Interrupt software priority register 7 | 0xFF                 |      |

| 0x00 7F77                 |                    | ITC_SPR8       | Interrupt software priority register 8 | 0xFF                 |      |

| 0x00 7F78 to<br>0x00 7F79 |                    |                | Reserved area (2 byte)                 |                      |      |

| 0x00 7F80                 | SWIM               | SWIM_CSR       | SWIM control status register           | 0x00                 |      |

| 0x00 7F81 to<br>0x00 7F8F |                    |                | Reserved area (15 byte)                |                      |      |

#### Table 12. CPU/SWIM/debug module/interrupt controller registers

# 8 Option bytes

Option bytes contain configurations for device hardware features as well as the memory protection of the device. Except for the ROP (read-out protection) byte, each option byte has to be stored twice, in a regular form (OPTx) and a complemented one (NOPTx) for redundancy.

Option bytes can be modified in ICP mode (via SWIM) by accessing the EEPROM address shown in *Table 14: Option bytes* below.

Option bytes can also be modified 'on the fly' by the application in IAP mode, except the ROP and UBC options that can only be modified in ICP mode (via SWIM).

Refer to the STM8 Flash programming manual (PM0051) and STM8 SWIM communication protocol and debug module user manual (UM0470) for information on SWIM programming procedures.

| A al al a    | Option                          | Option   |       | Option bits    |        |              |             |               |              |               |                    |  |

|--------------|---------------------------------|----------|-------|----------------|--------|--------------|-------------|---------------|--------------|---------------|--------------------|--|

| Addr.        | name                            | byte no. | 7     | 6              | 5      | 4            | 3           | 2             | 1            | 0             | default<br>setting |  |

| 0x00<br>4800 | Read-out<br>protection<br>(ROP) | OPT0     |       | ROP[7:0]       |        |              |             |               |              |               | 0x00               |  |

| 0x00<br>4801 | User boot                       | OPT1     |       | UBC[7:0]       |        |              |             |               |              |               |                    |  |

| 0x00<br>4802 | code (UBC)                      | NOPT1    |       | NUBC[7:0]      |        |              |             |               |              | 0xFF          |                    |  |

| 0x00<br>4803 | Alternate<br>function           | OPT2     | AFR7  | AFR7 AFR6 AFR5 |        |              | AFR3        | AFR2          | AFR1         | AFR0          | 0x00               |  |

| 0x00<br>4804 | remapping<br>(AFR)              | NOPT2    | NAFR7 | NAFR6          | NAFR 5 | NAFR 4       | NAFR 3      | NAFR 2        | NAFR 1       | NAFR 0        | 0xFF               |  |

| 0x00<br>4805 | Miscell.                        | OPT3     |       | Reserved       |        | HSI<br>TRIM  | LSI<br>_EN  | IWDG<br>_HW   | WWDG<br>_HW  | WWDG<br>_HALT | 0x00               |  |

| 0x00<br>4806 | option                          | NOPT3    |       | Reserved       |        | NHSI<br>TRIM | NLSI<br>_EN | NIWDG<br>_HW  | NWWDG<br>_HW | NWWG<br>_HALT | 0xFF               |  |

| 0x00<br>4807 | Clock option                    | OPT4     |       | Re             | served |              | EXT<br>CLK  | CKAWU<br>SEL  | PRS<br>C1    | PRS<br>C0     | 0x00               |  |

| 0x00<br>4808 |                                 | NOPT4    |       | Re             | served |              | NEXT<br>CLK | NCKAWU<br>SEL | NPRS<br>C1   | NPRS<br>C0    | 0xFF               |  |

| 0x00<br>4809 | HSE clock                       | OPT5     |       | HSECNT[7:0]    |        |              |             |               |              | 0x00          |                    |  |

| 0x00<br>480A | startup                         | NOPT5    |       |                |        | NHSE         | CNT[7:0]    |               |              |               | 0xFF               |  |

#### Table 14. Option bytes

| Symbol               | Parameter                                                     | Conc                                                        | Тур                                   | Max  | Unit               |    |

|----------------------|---------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------|------|--------------------|----|

|                      | Supply current                                                |                                                             | HSE crystal osc. (16 MHz)             |      |                    |    |

|                      | in run mode, code executed                                    | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz             | HSE user ext. clock (16 MHz)          | 4.3  | 4.75               |    |

|                      | from Flash                                                    |                                                             | HSI RC osc. (16 MHz)                  | 3.7  | 4.5 <sup>(1)</sup> |    |

| I <sub>DD(RUN)</sub> | Supply current<br>in run mode,<br>code executed<br>from Flash | f <sub>CPU</sub> = f <sub>MASTER</sub> = 2 MHz              | HSI RC osc. (16 MHz/8) <sup>(2)</sup> | 0.84 | 2 <sup>(1)</sup>   | mA |

| DD(RON)              |                                                               | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 125 kHz       | HSI RC osc. (16 MHz)                  | 0.72 | 0.9                |    |

|                      |                                                               | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 =<br>15.625 kHz | HSI RC osc. (16 MHz/8)                | 0.46 | 0.58               |    |

|                      |                                                               | f <sub>CPU</sub> = f <sub>MASTER</sub> = 128 kHz            | LSI RC osc. (128 kHz)                 | 0.42 | 0.57               |    |

# Table 28. Total current consumption with code execution in run mode at $V_{DD}$ = 5 V (continued)

1. Tested in production.

2. Default clock configuration measured with all peripherals off.

| Symbol   | Parameter                   | Cond                                                                            | itions                                | Тур  | Max <sup>(1)</sup> | Unit |

|----------|-----------------------------|---------------------------------------------------------------------------------|---------------------------------------|------|--------------------|------|

|          |                             |                                                                                 | HSE crystal osc. (16 MHz)             | 1.8  | -                  |      |

|          |                             | f <sub>CPU</sub> = f <sub>MASTER</sub> =16 MHz                                  | HSE user ext. clock (16 MHz)          | 2    | 2.3                |      |

|          | Supply current              |                                                                                 | HSI RC osc. (16 MHz)                  | 1.5  | 2                  |      |

|          | in run mode,                | run mode,<br>ode executed f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 125 kHz | HSE user ext. clock (16 MHz)          | 0.81 | -                  |      |

|          | code executed from RAM      |                                                                                 | HSI RC osc. (16 MHz)                  | 0.7  | 0.87               |      |

|          |                             | f <sub>CPU</sub> = f <sub>MASTER</sub> / 128 =<br>15.625 kHz                    | HSI RC osc. (16 MHz/8)                | 0.46 | 0.58               |      |

|          |                             | f <sub>CPU</sub> = f <sub>MASTER</sub> =128 kHz                                 | LSI RC osc. (128 kHz)                 | 0.41 | 0.55               | mA   |

| IDD(RUN) |                             | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz                                 | HSE crystal osc. (16 MHz)             | 4    | -                  | ША   |

|          |                             |                                                                                 | HSE user ext. clock (16 MHz)          | 3.9  | 4.7                |      |

|          | Supply current              |                                                                                 | HSI RC osc. (16 MHz)                  | 3.7  | 4.5                |      |

|          | in run mode,                | f <sub>CPU</sub> = f <sub>MASTER</sub> =2 MHz                                   | HSI RC osc. (16 MHz/8) <sup>(2)</sup> | 0.84 | 1.05               |      |

|          | code executed<br>from Flash | f <sub>CPU</sub> = f <sub>MASTER</sub> / 128 = 125 kHz                          | HSI RC osc. (16 MHz)                  | 0.72 | 0.9                |      |

|          |                             | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 =<br>15.625 kHz                     | HSI RC osc. (16 MHz/8)                | 0.46 | 0.58               |      |

|          |                             | f <sub>CPU</sub> = f <sub>MASTER</sub> =128 kHz                                 | LSI RC osc. (128 kHz)                 | 0.42 | 0.57               |      |

### Table 29. Total current consumption with code execution in run mode at $V_{DD}$ = 3.3 V

1. Guaranteed by characterization results.

2. Default clock configuration measured with all peripherals off.

47/

#### Total current consumption in wait mode

Unless otherwise specified, data based are on characterization results, and not tested in production.

| Symbol                                                 | Parameter                                       | Conditions                                            |                                                             |                                       | Max                | Unit |  |

|--------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------|---------------------------------------|--------------------|------|--|

|                                                        |                                                 |                                                       | HSE crystal osc. (16 MHz)                                   | 1.6                                   | -                  |      |  |

| I <sub>DD(WFI)</sub><br>Supply current<br>in wait mode | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz | HSE user ext. clock (16 MHz)                          | 1.1                                                         | 1.3                                   |                    |      |  |

|                                                        | O                                               |                                                       | HSI RC osc. (16 MHz)                                        | 0.89                                  | 1.5 <sup>(1)</sup> |      |  |

|                                                        |                                                 | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 125 kHz | HSI RC osc. (16 MHz)                                        | 0.7                                   | 0.88               | mA   |  |

|                                                        |                                                 |                                                       | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 =<br>15.625 kHz | HSI RC osc. (16 MHz/8) <sup>(2)</sup> | 0.45               | 0.57 |  |

|                                                        |                                                 | f <sub>CPU</sub> = f <sub>MASTER</sub> = 128 kHz      | LSI RC osc. (128 kHz)                                       | 0.4                                   | 0.54               |      |  |

| Table 30. Total current consumption in wait mode at $V_{DD}$ = 5 V | Table 30. | Total curren | t consumption i | in wait mode | at V <sub>DD</sub> = 5 V |

|--------------------------------------------------------------------|-----------|--------------|-----------------|--------------|--------------------------|

|--------------------------------------------------------------------|-----------|--------------|-----------------|--------------|--------------------------|

1. Tested in production.

2. Default clock configuration measured with all peripherals off.

| Table 31. Total current consumption in wait mode at $v_{DD} = 3.5 v$ |                |                                                             |                                       |      |                    |      |  |

|----------------------------------------------------------------------|----------------|-------------------------------------------------------------|---------------------------------------|------|--------------------|------|--|

| Symbol                                                               | Parameter      | Conditions                                                  |                                       |      | Max <sup>(1)</sup> | Unit |  |

|                                                                      |                |                                                             | HSE crystal osc. (16 MHz)             | 1.1  | -                  |      |  |

| Supply curre<br>I <sub>DD(WFI)</sub> in wait mode                    |                | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz             | HSE user ext. clock (16 MHz)          | 1.1  | 1.3                |      |  |

|                                                                      | Supply ourrest |                                                             | HSI RC osc. (16 MHz)                  | 0.89 | 1.1                |      |  |

|                                                                      | in wait mode   | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 125 kHz       | HSI RC osc. (16 MHz)                  | 0.7  | 0.88               | mA   |  |

|                                                                      |                | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 =<br>15.625 kHz | HSI RC osc. (16 MHz/8) <sup>(2)</sup> | 0.45 | 0.57               |      |  |

|                                                                      |                | f <sub>CPU</sub> = f <sub>MASTER</sub> = 128 kHz            | LSI RC osc. (128 kHz)                 | 0.4  | 0.54               |      |  |

Table 31. Total current consumption in wait mode at  $V_{DD}$  = 3.3 V

1. Guaranteed by characterization results.

2. Default clock configuration measured with all peripherals off.

#### Total current consumption and timing in forced reset state

| Symbol               | Parameter                                    | Conditions              | Тур | Max <sup>(1)</sup> | Unit |

|----------------------|----------------------------------------------|-------------------------|-----|--------------------|------|

|                      | Supply current in reset state <sup>(2)</sup> | V <sub>DD</sub> = 5 V   | 400 | -                  |      |

| DD(R)                | Supply current in reset state.               | V <sub>DD</sub> = 3.3 V | 300 | -                  | μA   |

| t <sub>RESETBL</sub> | Reset pin release to vector<br>fetch         | -                       | _   | 150                | μs   |

| Table 37. Total current consumption and timing in forced res | et state |

|--------------------------------------------------------------|----------|

|--------------------------------------------------------------|----------|

1. Guaranteed by design.

2. Characterized with all I/Os tied to  $V_{SS}$ .

#### Current consumption for on-chip peripherals

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}.$

HSI internal RC/f<sub>CPU</sub> =  $f_{MASTER}$  = 16 MHz,  $V_{DD}$  = 5 V

#### Table 38. Peripheral current consumption

| Symbol                 | Parameter                             | Тур  | Unit |

|------------------------|---------------------------------------|------|------|

| I <sub>DD(TIM1)</sub>  | TIM1 supply current <sup>(1)</sup>    | 210  |      |

| I <sub>DD(TIM5)</sub>  | TIM5 supply current <sup>(1)</sup>    | 130  |      |

| I <sub>DD(TIM6)</sub>  | TIM6 supply current <sup>(1)</sup>    | 50   |      |

| I <sub>DD(UART1)</sub> | LINUART supply current <sup>(2)</sup> | 120  | μA   |

| I <sub>DD(SPI)</sub>   | SPI supply current <sup>(2)</sup>     | 45   |      |

| I <sub>DD(I2C)</sub>   | I2C supply current <sup>(2)</sup>     | 65   |      |

| I <sub>DD(ADC1)</sub>  | ADC1 supply current <sup>(3)</sup>    | 1000 | ſ    |

Data based on a differential I<sub>DD</sub> measurement between reset configuration and timer counter running at 16 MHz. No IC/OC programmed (no I/O pads toggling). Not tested in production.

Data based on a differential I<sub>DD</sub> measurement between the on-chip peripheral when kept under reset and not clocked and the on-chip peripheral when clocked and not kept under reset. No I/O pads toggling. Not tested in production.

Data based on a differential I<sub>DD</sub> measurement between reset configuration and continuous A/D conversions. Not tested in production.

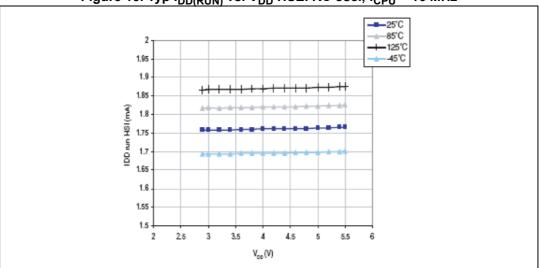

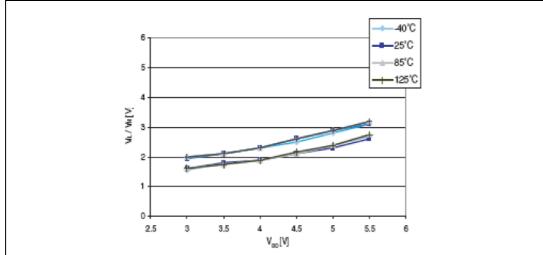

Figure 13. Typ  $I_{DD(RUN)}$  vs.  $V_{DD}$  HSEI RC osc.,  $f_{CPU}$  = 16 MHz

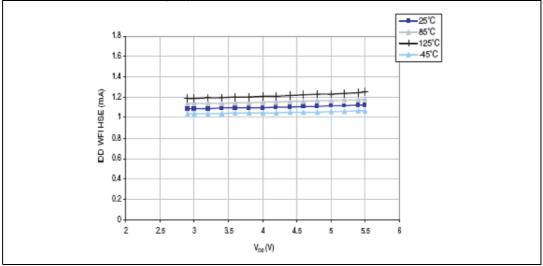

Figure 14. Typ  $I_{DD(WFI)}$  vs.  $V_{DD}$  HSE user external clock,  $f_{CPU}$  = 16 MHz

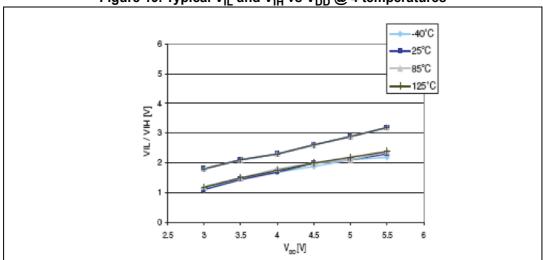

Figure 19. Typical  $V_{IL}$  and  $V_{IH}$  vs  $V_{DD}$  @ 4 temperatures

## 9.3.7 Reset pin characteristics

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}$  unless otherwise specified.

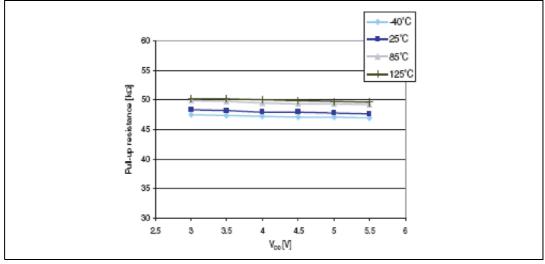

| Symbol                  | Parameter                                             | Conditions             | Min                         | Тур | Max                   | Unit |

|-------------------------|-------------------------------------------------------|------------------------|-----------------------------|-----|-----------------------|------|

| V <sub>IL(NRST)</sub>   | NRST input low level voltage <sup>(1)</sup>           | -                      | -0.3                        | -   | $0.3 \times V_{DD}$   |      |

| V <sub>IH(NRST)</sub>   | NRST input high level voltage <sup>(1)</sup>          | I <sub>OL</sub> = 2 mA | $0.7 	ext{ x V}_{	ext{DD}}$ | -   | V <sub>DD</sub> + 0.3 | V    |

| V <sub>OL(NRST)</sub>   | NRST output low level voltage <sup>(1)</sup>          | -                      | -                           | -   | 0.5                   |      |

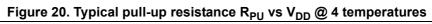

| R <sub>PU(NRST)</sub>   | NRST pull-up resistor <sup>(2)</sup>                  | -                      | 30                          | 55  | 80                    | kΩ   |

| t <sub>IFP(NRST)</sub>  | NRST input filtered pulse <sup>(3)</sup>              | -                      | -                           | -   | 75                    |      |

| t <sub>INFP(NRST)</sub> | NRST Input not filtered pulse duration <sup>(3)</sup> | -                      | 500                         | -   | -                     | ns   |

| t <sub>OP(NRST)</sub>   | NRST output pulse <sup>(3)</sup>                      | -                      | 20                          | -   | -                     | μs   |

| Table 5 | 1. NRST | pin c | haracteristics |

|---------|---------|-------|----------------|

|         |         |       |                |

1. Guaranteed by characterization results.

2. The R<sub>PU</sub> pull-up equivalent resistor is based on a resistive transistor.

3. Guaranteed by design.

| Symbol                            | Parameter             | Conditions <sup>(1)</sup>          | Min | Max | Unit |

|-----------------------------------|-----------------------|------------------------------------|-----|-----|------|

| t <sub>h(SO)</sub> <sup>(2)</sup> |                       | Slave mode<br>(after enable edge)  | 27  | -   | ns   |

| t <sub>h(MO)</sub> <sup>(2)</sup> | Data output hold time | Master mode<br>(after enable edge) | 11  | -   | 115  |

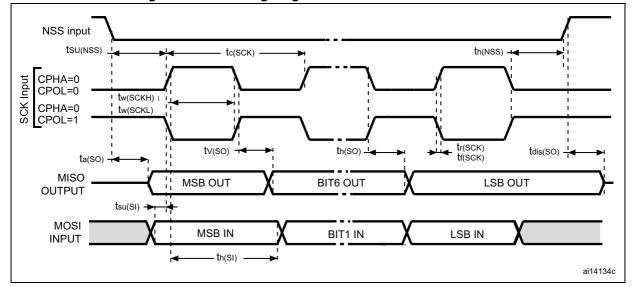

#### Table 52. SPI characteristics (continued)

1. Parameters are given by selecting 10 MHz I/O output frequency.

2. Values based on design simulation and/or characterization results, and not tested in production.

3. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

4. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z.

#### Figure 36. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are made at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}$

#### **Electromagnetic interference (EMI)**

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm IEC 61967-2 which specifies the board and the loading of each pin.

| Symbol           |                                                                                   | Conditions                                |                   |                     |                   |       |  |

|------------------|-----------------------------------------------------------------------------------|-------------------------------------------|-------------------|---------------------|-------------------|-------|--|

|                  | Parameter                                                                         |                                           | Monitored         | Max f <sub>HS</sub> | Unit              |       |  |

|                  |                                                                                   | General conditions                        | frequency band    | 16 MHz/<br>8 MHz    | 16 MHz/<br>16 MHz |       |  |

|                  | Peak level $V_{DD} = 5 V$ ,<br>$T_A = 25 °C$ ,<br>LQFP32 package<br>conforming to | 0.1 MHz to 30 MHz                         | 5                 | 5                   |                   |       |  |

| 6                |                                                                                   | T <sub>A</sub> = 25 °C,<br>LQFP32 package | 30 MHz to 130 MHz | 4                   | 5                 | dBµV  |  |

| S <sub>EMI</sub> |                                                                                   |                                           | 130 MHz to 1 GHz  | 5                   | 5                 |       |  |

|                  | EMI level                                                                         | IEC 61967-2                               |                   | 2.5                 | 2.5               | level |  |

| Table | 58. | EMI | data |

|-------|-----|-----|------|

|       |     |     |      |

1. Guaranteed by characterization results.

#### Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, DLU and LU) using specific measurement methods, the product is stressed to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

#### Electrostatic discharge (ESD)

Electrostatic discharges (one positive then one negative pulses separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). One model can be simulated: Human body model. This test conforms to the JESD22-A114A/A115A standard. For more details, refer to the application note AN1181.

| Symbol                | Ratings                                               | Conditions                                          | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|-----------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage<br>(Human body model) | $T_A = 25^{\circ}C$ , conforming to JESD22-A114     | 3A    | 4000                            |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (Charge device model) | T <sub>A</sub> = 25°C, conforming to<br>JESD22-C101 | 3     | 500                             | V    |

| V <sub>ESD(MM)</sub>  | Electrostatic discharge voltage (Machine model)       | T <sub>A</sub> = 25°C, conforming to<br>JESD22-A115 | В     | 200                             |      |

Table 59. ESD absolute maximum ratings

1. Guaranteed by characterization results.

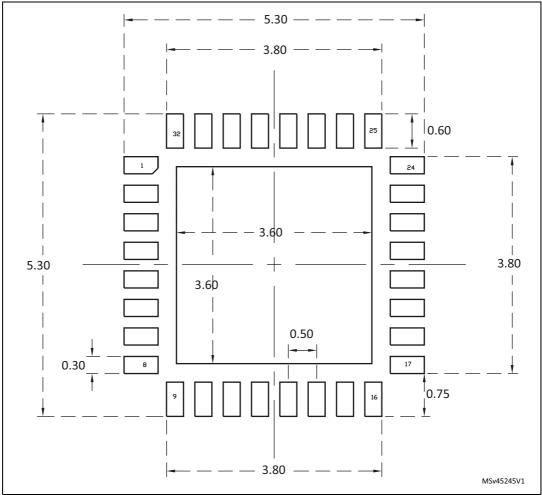

Figure 49. VFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch very thin profile fine pitch quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax}$ = 75 °C (measured according to JESD51-2), I<sub>DDmax</sub> = 8 mA, V<sub>DD</sub> = 5 V Maximum 20 I/Os used at the same time in output at low level with:

Maximum 20 I/Os used at the same time in output at low level with:

$I_{OL}$  = 8 mA,  $V_{OL}$  = 0.4 V

P<sub>INTmax</sub> = 8 mA x 5 V= 400 mW

$P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{ V} = 64 \text{ mW}$

This gives: P<sub>INTmax</sub> = 400 mW and P<sub>IOmax</sub> 64 mW:

P<sub>Dmax</sub> = 400 mW + 64 mW

Thus: P<sub>Dmax</sub> = 464 mW.

Using the values obtained in Table 64: Thermal characteristics on page 101  $T_{Jmax}$  is calculated as follows:

For LQFP32 60 °C/W

T<sub>Jmax</sub> = 75 °C + (60 °C/W x464 mW) = 75 °C + 27.8 °C = 102.8 °C

This is within the range of the suffix C version parts (-40 <  $T_J$  < 125 °C).

Parts must be ordered at least with the temperature range suffix C.

# 13 Revision history

| Date          | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11-Oct-2013   | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 16-Dec-2013   | 2        | Changed the document status to Production data.<br>Updated <i>Figure: STM8AF6223PxAx TSSOP20 pinout</i> to<br>add SPI_NSS to PD4, TLI to PD2, and change remap<br>function on PB5 from TIM5_BKIn to TIM1_BKIN.<br>Updated <i>Table: STM8AF6223PxAx TSSOP20 pin</i><br><i>description</i> to add SPI_NSS to PD4 and TLI to PD2.<br>Updated <i>Table: STM8AF6223 TSSOP20 pin description</i><br>and <i>Table: LQFP32 pin description</i> .<br>Updated AFR2 definition in <i>Table: STM8AF6223PxAx</i><br><i>alternate function remapping bits</i> [7:2] for 20-pin<br><i>packages</i> .<br>Removed the remapping option on PA3 for AFR[1:0]=10<br>in <i>Table: STM8AF6223PxAx alternate function</i><br><i>remapping bits</i> [1:0] for 20-pin packages.<br>Added note and removed remapping option on PA3 for<br>AFR[1:0]=11 in <i>Table: STM8AF6223 alternate function</i><br><i>remapping bits</i> [1:0] for 20-pin packages. Updated AFR2<br>definition in STM8AF6223 alternate function remapping<br>bits [7:2] for 20-pin packages.<br>Added the note below <i>Table: STM8AF6226T alternate</i><br><i>function remapping bits</i> [1:0] for 32-pin packages.<br>Updated <i>Table: I2C characteristics</i> to modify t <sub>h(SDA)</sub> and<br>add t <sub>SP</sub> .<br>Updated <i>Section: C assembly toolchains</i> . |

| 03-Apr-2014 3 |          | Replaced STM8AF6226T by STM8AF6226 part number.Added STM8AF6223A part number to coverSTM8AF6223PxAx order codes.Removed LINUART alternate function for PA3 in Table:STM8AF6223PxAx TSSOP20 pin description.Removed note 3 for $I_{DD(AH)}$ in Table: Total currentconsumption in active halt mode at VDD = 5 V.Updated the remapping option on PA3 for AFR[1:0]=11in Table: STM8AF6223 alternate function remapping bits[1:0] for 20-pin packages.Updated notes related to $t_{RET}$ minimum value in Table:Data memory.Updated Table: ESD absolute maximum ratings.Added notes related to protrusions and gate burrs for Dand E1 dimensions in Table: 20-pin, 4.40 mm body, 0.65mm pitch mechanical data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### Table 66. Document revision history