# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                    |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | STM8A                                                                  |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 16                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 640 x 8                                                                |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | A/D 7x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                        |

| Supplier Device Package    | 20-TSSOP                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af6223pdax |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

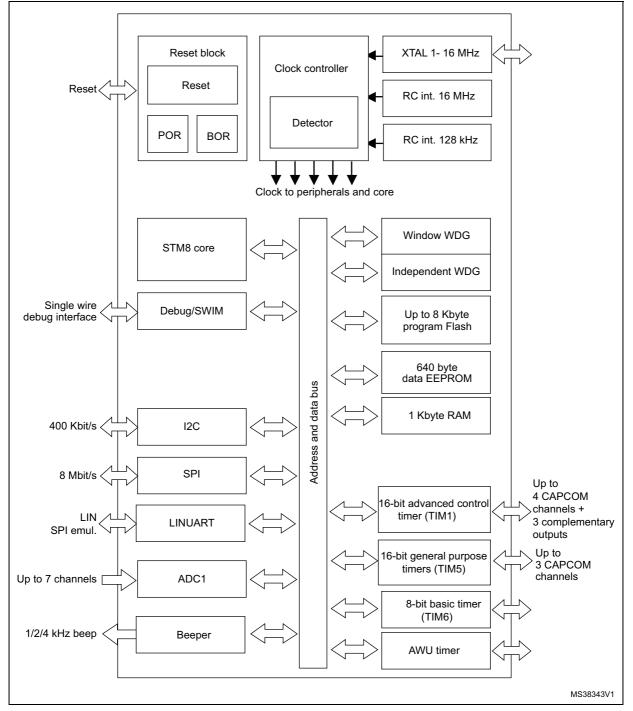

# 3 Block diagram

Legend: ADC (Analog-to-digital converter), beCAN (Controller area network), BOR (Brownout reset), I<sup>2</sup>C (Inter-integrated circuit multimaster interface),IWDG (Independent window watchdog), LINUART (Local interconnect network universal asynchronous receiver transmitter), POR (Power on reset), SPI (Serial peripheral interface), SWIM (Single wire interface module), USART (Universal synchronous asynchronous receiver transmitter), Window WDG (Window watchdog).

DocID025118 Rev 6

## 4.13 Analog-to-digital converter (ADC1)

The STM8AF6213, STM8AF6223, STM8AF6223A and STM8AF6226 products contain a 10-bit successive approximation A/D converter (ADC1) with up to 7 external and 1 internal multiplexed input channels and the following main features:

- Input voltage range: 0 to V<sub>DD</sub>

- Input voltage range: 0 to V<sub>DDA</sub>

- Conversion time: 14 clock cycles

- Single and continuous and buffered continuous conversion modes

- Buffer size (n x 10 bits) where n = number of input channels

- Scan mode for single and continuous conversion of a sequence of channels

- Analog watchdog capability with programmable upper and lower thresholds

- Internal reference voltage on channel AIN7

- Analog watchdog interrupt

- External trigger input

- Trigger from TIM1 TRGO

- End of conversion (EOC) interrupt

Note: Additional AIN12 analog input is not selectable in ADC scan mode or with analog watchdog. Values converted from AIN12 are stored only into the ADC\_DRH/ADC\_DRL registers.

#### Internal bandgap reference voltage

Channel AIN7 is internally connected to the internal bandgap reference voltage. The internal bandgap reference is constant and can be used, for example, to monitor  $V_{DD}$ . It is independent of variations in  $V_{DD}$  and ambient temperature  $T_A$ .

## 4.14 Communication interfaces

The following communication interfaces are implemented:

- LINUART: Full feature UART, synchronous mode, SPI master mode, Smartcard mode, IrDA mode, single wire mode, LIN2.2 capability

- SPI: full and half-duplex, 8 Mbit/s

- I<sup>2</sup>C: up to 400 Kbit/s

Some peripheral names differ between the datasheet and STM8S series and STM8AF series 8-bit microcontrollers reference manual, RM0016 (see *Table 4*).

| Table 4. Communication | peripheral | naming | correspondence |

|------------------------|------------|--------|----------------|

|------------------------|------------|--------|----------------|

| Peripheral name in datasheet | Peripheral name in reference manual<br>(RM0016) |

|------------------------------|-------------------------------------------------|

| LINUART                      | UART4                                           |

## 4.14.1 LINUART

### Main features

- 1 Mbit/s full duplex SCI

- SPI emulation

- High precision baud rate generator

- Smartcard emulation

- IrDA SIR encoder decoder

- LIN mode

- Single wire half duplex mode

#### LIN mode

#### Master mode:

- LIN break and delimiter generation

- LIN break and delimiter detection with separate flag and interrupt source for read back checking.

#### Slave mode:

- Autonomous header handling one single interrupt per valid header

- Mute mode to filter responses

- Identifier parity error checking

- LIN automatic resynchronization, allowing operation with internal RC oscillator (HSI) clock source

- Break detection at any time, even during a byte reception

- Header errors detection:

- Delimiter too short

- Synch field error

- Deviation error (if automatic resynchronization is enabled)

- Framing error in synch field or identifier field

- Header time-out

|       |                                               |      |          | Input    | t              |                          | Out   | tput             |    |                                   |                                                             |                                                            |

|-------|-----------------------------------------------|------|----------|----------|----------------|--------------------------|-------|------------------|----|-----------------------------------|-------------------------------------------------------------|------------------------------------------------------------|

| TSSOP | Pin name                                      | Туре | floating | ndm      | Ext. interrupt | High sink <sup>(1)</sup> | Speed | OD               | РР | Main<br>function<br>(after reset) | Default<br>alternate<br>function                            | Alternate<br>function<br>after remap<br>[option bit]       |

| 3     | PD6/ AIN6/<br>LINUART_RX                      | I/O  | X        | x        | x              | HS                       | O3    | x                | х  | Port D6                           | Analog<br>input 6/<br>LINUART<br>data receive               | -                                                          |

| 4     | NRST                                          | I/O  | -        | <u>X</u> | -              | -                        | -     | -                | -  | Re                                | set                                                         | -                                                          |

| 5     | PA1/ OSCIN <sup>(2)</sup>                     | I/O  | <u>x</u> | х        | х              | -                        | 01    | х                | х  | Port A1                           | Resonator/<br>crystal in                                    | -                                                          |

| 6     | PA2/ OSCOUT                                   | I/O  | X        | х        | х              | -                        | 01    | х                | х  | Port A2                           | Resonator/<br>crystal out                                   | -                                                          |

| 7     | VSS                                           | S    | -        | -        | -              | -                        | -     | -                | -  | Digital                           | ground                                                      | -                                                          |

| 8     | VCAP                                          | S    | -        | -        | -              | -                        | -     | -                | -  | 1.8 V regula                      | tor capacitor                                               | -                                                          |

| 9     | VDD                                           | S    | -        | -        | -              | -                        | -     | -                | -  | Digital power supply              |                                                             | -                                                          |

| 10    | PB5/ I2C_SDA<br>[TIM1_BKIN]                   | I/O  | X        | -        | x              | -                        | 01    | T <sup>(3)</sup> | -  | Port B5                           | I2C data                                                    | Timer 1 -<br>break input<br>[AFR4]                         |

| 11    | PB4/ I2C_SCL<br>[ADC_ETR]                     | I/O  | X        | -        | x              | -                        | O1    | T <sup>(3)</sup> | -  | Port B4                           | I2C clock                                                   | ADC<br>external<br>trigger<br>[AFR4]                       |

| 12    | PB1/<br>TIM1_CH2N/<br>AIN1                    | I/O  | X        | x        | x              | HS                       | O3    | х                | х  | Port B1                           | Timer 1 -<br>inverted<br>channel<br>2/Analog<br>input 1     | -                                                          |

| 13    | PB0/<br>TIM1_CH1N/AIN0                        | I/O  | X        | x        | x              | HS                       | O3    | х                | х  | Port B0                           | Timer 1 -<br>inverted<br>channel<br>1/Analog<br>input 0     | -                                                          |

| 14    | PC4/ TIM1_CH4/<br>CLK_CCO/AIN2/[<br>TIM1_CH2] | I/O  | X        | x        | x              | HS                       | O3    | х                | х  | Port C4                           | Timer 1 -<br>channel 4<br>/configurabl<br>e clock<br>output | Analog<br>input 2<br>[AFR2]Time<br>r 1 channel<br>2 [AFR7] |

| 15    | PC5/SPI_SCK<br>[TIM5_CH1]                     | I/O  | X        | x        | x              | HS                       | O3    | х                | х  | Port C5                           | SPI clock                                                   | Timer 5<br>channel 1<br>[AFR0]                             |

|                           | Table 11. General naroware register map (continued) |                        |                                    |                 |  |  |  |

|---------------------------|-----------------------------------------------------|------------------------|------------------------------------|-----------------|--|--|--|

| Address                   | Block                                               | Register label         | Register name                      | Reset<br>status |  |  |  |

| 0x00 5200                 |                                                     | SPI_CR1                | SPI control register 1             | 0x00            |  |  |  |

| 0x00 5201                 |                                                     | SPI_CR2                | SPI control register 2             | 0x00            |  |  |  |

| 0x00 5202                 |                                                     | SPI_ICR                | SPI interrupt control register     | 0x00            |  |  |  |

| 0x00 5203                 | SPI                                                 | SPI_SR                 | SPI status register                | 0x02            |  |  |  |

| 0x00 5204                 |                                                     | SPI_DR                 | SPI data register                  | 0x00            |  |  |  |

| 0x00 5205                 |                                                     | SPI_CRCPR              | SPI CRC polynomial register        | 0x07            |  |  |  |

| 0x00 5206                 |                                                     | SPI_RXCRCR             | SPI Rx CRC register                | 0xFF            |  |  |  |

| 0x00 5207                 |                                                     | SPI_TXCRCR             | SPI Tx CRC register                | 0xFF            |  |  |  |

| 0x00 5208 to<br>0x00 520F |                                                     | Reserved area (8 byte) |                                    |                 |  |  |  |

| 0x00 5210                 |                                                     | I2C_CR1                | I2C control register 1             | 0x00            |  |  |  |

| 0x00 5211                 |                                                     | I2C_CR2                | I2C control register 2             | 0x00            |  |  |  |

| 0x00 5212                 |                                                     | I2C_FREQR              | I2C frequency register             | 0x00            |  |  |  |

| 0x00 5213                 |                                                     | I2C_OARL               | I2C own address register low       | 0x00            |  |  |  |

| 0x00 5214                 |                                                     | I2C_OARH               | I2C own address register high      | 0x00            |  |  |  |

| 0x00 5215                 |                                                     |                        | Reserved area (1 byte)             |                 |  |  |  |

| 0x00 5216                 |                                                     | I2C_DR                 | I2C data register                  | 0x00            |  |  |  |

| 0x00 5217                 | I2C                                                 | I2C_SR1                | I2C status register 1              | 0x00            |  |  |  |

| 0x00 5218                 |                                                     | I2C_SR2                | I2C status register 2              | 0x00            |  |  |  |

| 0x00 5219                 |                                                     | I2C_SR3                | I2C status register 3              | 0x00            |  |  |  |

| 0x00 521A                 |                                                     | I2C_ITR                | I2C interrupt control register     | 0x00            |  |  |  |

| 0x00 521B                 |                                                     | I2C_CCRL               | I2C clock control register low     | 0x00            |  |  |  |

| 0x00 521C                 |                                                     | I2C_CCRH               | I2C clock control register high    | 0x00            |  |  |  |

| 0x00 521D                 |                                                     | I2C_TRISER             | I2C TRISE register                 | 0x02            |  |  |  |

| 0x00 521E                 |                                                     | I2C_PECR               | I2C packet error checking register | 0x00            |  |  |  |

| 0x00 521F to<br>0x00 522F |                                                     |                        |                                    |                 |  |  |  |

Table 11. General hardware register map (continued)

## 6.2.2 CPU/SWIM/debug module/interrupt controller registers

| Address                   | Block              | Register label | Register name                          | Reset<br>status |

|---------------------------|--------------------|----------------|----------------------------------------|-----------------|

| 0x00 7F00                 |                    | А              | Accumulator                            | 0x00            |

| 0x00 7F01                 |                    | PCE            | Program counter extended               | 0x00            |

| 0x00 7F02                 |                    | PCH            | Program counter high                   | 0x00            |

| 0x00 7F03                 | •                  | PCL            | Program counter low                    | 0x00            |

| 0x00 7F04                 |                    | ХН             | X index register high                  | 0x00            |

| 0x00 7F05                 | CPU <sup>(1)</sup> | XL             | X index register low                   | 0x00            |

| 0x00 7F06                 |                    | YH             | Y index register high                  | 0x00            |

| 0x00 7F07                 |                    | YL             | Y index register low                   | 0x00            |

| 0x00 7F08                 |                    | SPH            | Stack pointer high                     | 0x03            |

| 0x00 7F09                 |                    | SPL            | Stack pointer low                      | 0xFF            |

| 0x00 7F0A                 |                    | CCR            | Condition code register                | 0x28            |

| 0x00 7F0B to<br>0x00 7F5F |                    |                | Reserved area (85 byte)                | ·               |

| 0x00 7F60                 | CPU                | CFG_GCR        | Global configuration register          | 0x00            |

| 0x00 7F70                 |                    | ITC_SPR1       | Interrupt software priority register 1 | 0xFF            |

| 0x00 7F71                 |                    | ITC_SPR2       | Interrupt software priority register 2 | 0xFF            |

| 0x00 7F72                 |                    | ITC_SPR3       | Interrupt software priority register 3 | 0xFF            |

| 0x00 7F73                 | ITC                | ITC_SPR4       | Interrupt software priority register 4 | 0xFF            |

| 0x00 7F74                 | ne                 | ITC_SPR5       | Interrupt software priority register 5 | 0xFF            |

| 0x00 7F75                 |                    | ITC_SPR6       | Interrupt software priority register 6 | 0xFF            |

| 0x00 7F76                 |                    | ITC_SPR7       | Interrupt software priority register 7 | 0xFF            |

| 0x00 7F77                 |                    | ITC_SPR8       | Interrupt software priority register 8 | 0xFF            |

| 0x00 7F78 to<br>0x00 7F79 |                    |                | Reserved area (2 byte)                 |                 |

| 0x00 7F80                 | SWIM               | SWIM_CSR       | SWIM control status register           | 0x00            |

| 0x00 7F81 to<br>0x00 7F8F |                    |                | Reserved area (15 byte)                |                 |

#### Table 12. CPU/SWIM/debug module/interrupt controller registers

| Address                   | Block                  | Register label | Register name                               | Reset<br>status |  |  |

|---------------------------|------------------------|----------------|---------------------------------------------|-----------------|--|--|

| 0x00 7F90                 |                        | DM_BK1RE       | DM breakpoint 1 register extended byte      | 0xFF            |  |  |

| 0x00 7F91                 |                        | DM_BK1RH       | DM_BK1RH DM breakpoint 1 register high byte |                 |  |  |

| 0x00 7F92                 |                        | DM_BK1RL       | DM_BK1RL DM breakpoint 1 register low byte  |                 |  |  |

| 0x00 7F93                 |                        | DM_BK2RE       | DM breakpoint 2 register extended byte      | 0xFF            |  |  |

| 0x00 7F94                 |                        | DM_BK2RH       | DM breakpoint 2 register high byte          | 0xFF            |  |  |

| 0x00 7F95                 | DM                     | DM_BK2RL       | DM_BK2RL DM breakpoint 2 register low byte  |                 |  |  |

| 0x00 7F96                 |                        | DM_CR1         | DM_CR1 DM debug module control register 1   |                 |  |  |

| 0x00 7F97                 |                        | DM_CR2         | DM_CR2 DM debug module control register 2   |                 |  |  |

| 0x00 7F98                 |                        | DM_CSR1        | DM debug module control/status register 1   | 0x10            |  |  |

| 0x00 7F99                 |                        | DM_CSR2        | DM debug module control/status register 2   | 0x00            |  |  |

| 0x00 7F9A                 |                        | DM_ENFCTR      | DM enable function register                 | 0xFF            |  |  |

| 0x00 7F9B to<br>0x00 7F9F | Reserved area (5 byte) |                |                                             |                 |  |  |

Table 12. CPU/SWIM/debug module/interrupt controller registers (continued)

1. Accessible by debug module only

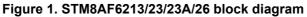

Figure 9.  $f_{CPUmax}$  versus  $V_{DD}$

| Symbol                | Parameter                                     | Conditions             | Min                | Тур               | Max                | Unit  |

|-----------------------|-----------------------------------------------|------------------------|--------------------|-------------------|--------------------|-------|

| +                     | V <sub>DD</sub> rise time rate                | -                      | 2 <sup>(1)</sup>   | -                 | ∞                  | µs/V  |

| t <sub>VDD</sub>      | V <sub>DD</sub> fall time rate <sup>(2)</sup> | -                      | 2 <sup>(1)</sup>   | -                 | 8                  | μ5/ ν |

| t <sub>TEMP</sub>     | Reset release delay                           | V <sub>DD</sub> rising | -                  | -                 | 1.7                | ms    |

| V <sub>IT+</sub>      | Power-on reset<br>threshold <sup>(3)</sup>    | -                      | 2.6 <sup>(1)</sup> | 2.7               | 2.85               | V     |

| V <sub>IT-</sub>      | Brown-out reset<br>threshold                  | -                      | 2.5                | 2.65              | 2.8 <sup>(1)</sup> | v     |

| V <sub>HYS(BOR)</sub> | Brown-out reset<br>hysteresis                 | -                      | -                  | 70 <sup>(1)</sup> | -                  | mV    |

1. Guaranteed by design.

2. Reset is always generated after a  $t_{\mbox{TEMP}}$  delay. The application must ensure that  $V_{\mbox{DD}}$  is still above the minimum operating voltage (V\_{\mbox{DD}} min) when the  $t_{\mbox{TEMP}}$  delay has elapsed.

3. There is inrush current into V<sub>DD</sub> present after device power on to charge C<sub>EXT</sub> capacitor. This inrush energy depends from C<sub>EXT</sub> capacitor value. For example, a C<sub>EXT</sub> of 1µF requires Q=1 µF x 1.8V = 1.8 µC.

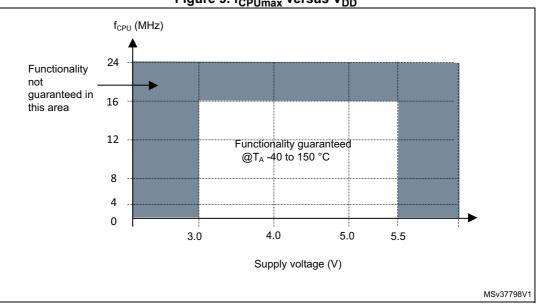

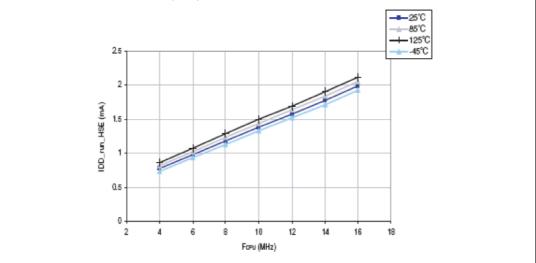

### **Current consumption curves**

The following figures show typical current consumption measured with code executing in RAM.

Figure 11. Typ I<sub>DD(RUN)</sub> vs. V<sub>DD</sub> HSE user external clock, f<sub>CPU</sub> = 16 MHz

Figure 12. Typ  $I_{DD(RUN)}$  vs.  $f_{CPU}$  HSE user external clock,  $V_{DD}$  = 5 V

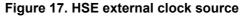

## 9.3.3 External clock sources and timing characteristics

## HSE user external clock

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}.$

| Table 39 | . HSE user | <sup>•</sup> external | clock | characteristics |

|----------|------------|-----------------------|-------|-----------------|

|----------|------------|-----------------------|-------|-----------------|

| Symbol                           | Parameter                               | Conditions                 | Min                   | Тур | Мах                     | Unit |

|----------------------------------|-----------------------------------------|----------------------------|-----------------------|-----|-------------------------|------|

| f <sub>HSE_ext</sub>             | User external clock source<br>frequency | -                          | 0                     | -   | 16                      | MHz  |

| V <sub>HSEH</sub> <sup>(1)</sup> | OSCIN input pin high level voltage      | -                          | 0.7 x V <sub>DD</sub> | -   | V <sub>DD</sub> + 0.3 V | V    |

| V <sub>HSEL</sub> <sup>(1)</sup> | OSCIN input pin low level voltage       | -                          | V <sub>SS</sub>       | -   | 0.3 x V <sub>DD</sub>   | v    |

| I <sub>LEAK_HSE</sub>            | OSCIN input leakage<br>current          | $V_{SS} < V_{IN} < V_{DD}$ | -1                    | -   | +1                      | μΑ   |

1. Guaranteed by characterization results.

| Symbol           | Parameter                                                          | Condition              | Min  | Max | Unit   |

|------------------|--------------------------------------------------------------------|------------------------|------|-----|--------|

| T <sub>WE</sub>  | Temperature for writing and erasing                                | -                      | -40  | 150 | °C     |

| N <sub>WE</sub>  | Flash program memory endurance (erase/write cycles) <sup>(1)</sup> | T <sub>A</sub> = 25 °C | 1000 | -   | cycles |

| t                | Data retention time                                                | T <sub>A</sub> = 25 °C | 40   | -   | veare  |

| t <sub>RET</sub> |                                                                    | T <sub>A</sub> = 55 °C | 20   | -   | years  |

#### Table 45. Flash program memory

1. The physical granularity of the memory is 4 byte, so cycling is performed on 4 byte even when a write/erase operation addresses a single byte.

| Symbol           | Parameter                                                    | Condition                      | Min                  | Max | Unit   |  |

|------------------|--------------------------------------------------------------|--------------------------------|----------------------|-----|--------|--|

| T <sub>WE</sub>  | Temperature for writing and erasing                          | -                              | -40                  | 150 | °C     |  |

| N                | Data memory endurance <sup>(1)</sup><br>(erase/write cycles) | T <sub>A</sub> = 25 °C         | 300 k                | -   | cycles |  |

|                  |                                                              | $T_A = -40^{\circ}C$ to 125 °C | 100 k <sup>(2)</sup> | -   |        |  |

| +                | Data retention time                                          | T <sub>A</sub> = 25 °C         | 40 <sup>(3)</sup>    | -   | years  |  |

| <sup>I</sup> RET |                                                              | T <sub>A</sub> = 55 °C         | 20 <sup>(2)(3)</sup> | -   |        |  |

1. The physical granularity of the memory is 4 byte, so cycling is performed on 4 byte even when a write/erase operation addresses a single byte.

2. More information on the relationship between data retention time and number of write/erase cycles is available in a separate technical document.

3. Retention time for 256B of data memory after up to 1000 cycles at 125  $^\circ\text{C}.$

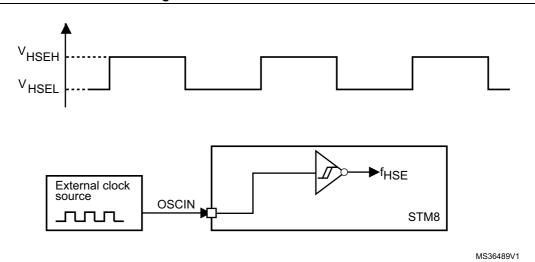

Figure 35. Recommended reset pin protection

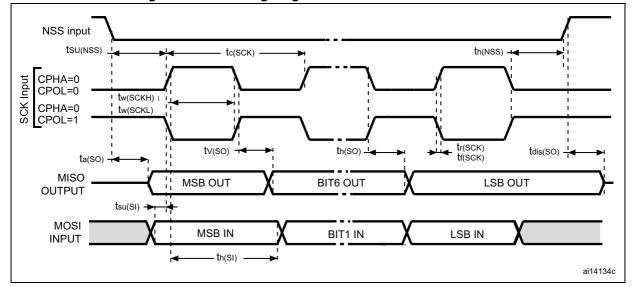

## 9.3.8 SPI serial peripheral interface

Unless otherwise specified, the parameters given in *Table 52* are derived from tests performed under ambient temperature,  $f_{MASTER}$  frequency and  $V_{DD}$  supply voltage conditions.  $t_{MASTER} = 1/f_{MASTER}$ .

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                               | Parameter                    | Conditions <sup>(1)</sup>          | Min                      | Max                      | Unit    |  |

|------------------------------------------------------|------------------------------|------------------------------------|--------------------------|--------------------------|---------|--|

| f <sub>SCK</sub>                                     | SDI clock froguency          | Master mode                        | 0                        | 8                        | MHz     |  |

| 1/t <sub>c(SCK)</sub>                                | SPI clock frequency          | Slave mode                         | 0                        | 6                        | - IVIHZ |  |

| t <sub>r(SCK</sub> )<br>t <sub>f(SCK)</sub>          | SPI clock rise and fall time | Capacitive load:<br>C = 30 pF      | -                        | 25                       |         |  |

| t <sub>su(NSS)</sub> <sup>(2)</sup>                  | NSS setup time               | Slave mode                         | 4 * t <sub>MASTER</sub>  | -                        |         |  |

| t <sub>h(NSS)</sub> <sup>(2)</sup>                   | NSS hold time                | Slave mode                         | 70                       | -                        |         |  |

| t <sub>w(SCKH)</sub> (2)<br>t <sub>w(SCKL)</sub> (2) | SCK high and low time        | Master mode                        | t <sub>SCK</sub> /2 - 15 | t <sub>SCK</sub> /2 + 15 |         |  |

| t <sub>su(MI)</sub> (2)                              | Data input setup time        | Master mode                        | 5                        | -                        |         |  |

| t <sub>su(MI)</sub> (2)<br>t <sub>su(SI)</sub> (2)   |                              | Slave mode                         | 5                        | -                        | ns      |  |

| t <sub>h(MI)</sub> <sup>(2)</sup>                    | Data input hold time         | Master mode                        | 7                        | -                        | 115     |  |

| t <sub>h(MI)</sub> (2)<br>t <sub>h(SI)</sub> (2)     |                              | Slave mode                         | 10                       | -                        |         |  |

| t <sub>a(SO)</sub> <sup>(2)(3)</sup>                 | Data output access time      | Slave mode                         | -                        | 3* t <sub>MASTER</sub>   |         |  |

| t <sub>dis(SO)</sub> <sup>(2)(4)</sup>               | Data output disable time     | Slave mode                         | 25                       | -                        |         |  |

| $t_{v(SO)}^{(2)}$                                    | Data output valid time       | Slave mode<br>(after enable edge)  | -                        | 65                       |         |  |

| t <sub>v(MO)</sub> <sup>(2)</sup>                    | Data output valid time       | Master mode<br>(after enable edge) | -                        | 36                       |         |  |

Table 52. SPI characteristics

| Symbol                            | Parameter             | Conditions <sup>(1)</sup>          | Min | Max | Unit |

|-----------------------------------|-----------------------|------------------------------------|-----|-----|------|

| t <sub>h(SO)</sub> <sup>(2)</sup> | Data output hold time | Slave mode<br>(after enable edge)  | 27  | -   |      |

| t <sub>h(MO)</sub> <sup>(2)</sup> |                       | Master mode<br>(after enable edge) | 11  | -   | ns   |

#### Table 52. SPI characteristics (continued)

1. Parameters are given by selecting 10 MHz I/O output frequency.

2. Values based on design simulation and/or characterization results, and not tested in production.

3. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

4. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z.

#### Figure 36. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are made at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}$

# 9.3.9 I<sup>2</sup>C interface characteristics

| Symbol                                     | Parameter                                            | Standard           | mode I <sup>2</sup> C | Fast mod           | Unit                     |      |  |

|--------------------------------------------|------------------------------------------------------|--------------------|-----------------------|--------------------|--------------------------|------|--|

| Symbol                                     | Falameter                                            | Min <sup>(2)</sup> | Max <sup>(2)</sup>    | Min <sup>(2)</sup> | Max <sup>(2)</sup>       | Unit |  |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                                   | 4.7                | -                     | 1.3                | -                        | 110  |  |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                                  | 4.0                | -                     | 0.6                | -                        | μs   |  |

| t <sub>su(SDA)</sub>                       | SDA setup time                                       | 250                | -                     | 100                | -                        |      |  |

| t <sub>h(SDA)</sub>                        | SDA data hold time                                   | 0 <sup>(3)</sup>   | 3450                  | 0 <sup>(4)</sup>   | 900 <sup>(3)</sup>       |      |  |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                                | -                  | 1000                  | -                  | 300 <sup>ns</sup><br>300 |      |  |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                                | -                  | 300                   | -                  |                          |      |  |

| t <sub>h(STA)</sub>                        | START condition hold time                            | 4.0                | -                     | 0.6                | -                        |      |  |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time                  | 4.7                | -                     | 0.6                | -                        |      |  |

| t <sub>su(STO)</sub>                       | STOP condition setup time                            | 4.0                | -                     | 0.6                | -                        | μs   |  |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free)              | 4.7                | -                     | 1.3                | -                        |      |  |

| t <sub>SP</sub>                            | Pulse width of spikes suppressed by the input filter | 0                  | 50 <sup>(5)</sup>     | 0                  | 50                       | ns   |  |

| Cb                                         | Capacitive load for each bus line                    | -                  | 400                   | -                  | 400                      | pF   |  |

## Table 53. I<sup>2</sup>C characteristics

1.  $f_{MASTER}$ , must be at least 8 MHz to achieve max fast I<sup>2</sup>C speed (400 kHz)

2. Data based on standard I<sup>2</sup>C protocol requirement, not tested in production

3. The maximum hold time of the start condition has only to be met if the interface does not stretch the low time

4. The device must internally provide a hold time of at least 300 ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL

5. The minimum width of the spikes filtered by the analog filter is above  $t_{SP(max)}$

## 9.3.10 10-bit ADC characteristics

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{MASTER}},$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol             | Parameter                             | Conditions                     | Min                 | Тур  | Max                 | Unit  |  |

|--------------------|---------------------------------------|--------------------------------|---------------------|------|---------------------|-------|--|

| £                  |                                       | V <sub>DD</sub> = 3 to 5.5 V   | 1                   | -    | 4                   | MHz   |  |

| f <sub>ADC</sub>   | ADC clock frequency                   | V <sub>DD</sub> = 4.5 to 5.5 V | 1                   | -    | 6                   | IVITZ |  |

| V <sub>AIN</sub>   | Conversion voltage -                  |                                | V <sub>SS</sub>     | -    | V <sub>DD</sub>     | V     |  |

| V <sub>BGREF</sub> | Internal bandgap<br>reference voltage | V <sub>DD</sub> = 3 to 5.5 V   | 1.19 <sup>(2)</sup> | 1.22 | 1.25 <sup>(2)</sup> | V     |  |

| C <sub>ADC</sub>   | Internal sample and hold capacitor    | -                              | -                   | 3    | -                   | pF    |  |

| ts <sup>(1)</sup>  | Minimum sampling time                 | f <sub>ADC</sub> = 4MHz        | -                   | 0.75 | -                   |       |  |

| LS, Y              | Minimum sampling une                  | f <sub>ADC</sub> = 6 MHz       | -                   | 0.5  | -                   | μs    |  |

| t <sub>STAB</sub>  | Wakeup time from standby              | -                              | -                   | 7    | -                   |       |  |

|                    | Minimum total conversion              | f <sub>ADC</sub> = 4 Hz        |                     | 3.5  |                     |       |  |

| t <sub>CONV</sub>  | time including sampling               | f <sub>ADC</sub> = 6 MHz       |                     | 2.33 |                     | μs    |  |

|                    | time, 10-bit resolution               | -                              | 14                  |      | 1/f <sub>ADC</sub>  |       |  |

| Table | 54. | ADC | characteristics |

|-------|-----|-----|-----------------|

|-------|-----|-----|-----------------|

During the sample time the input capacitance C<sub>AIN</sub> (3 pF max) can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>S</sub>. After the end of the sample time t<sub>S</sub>, changes of the analog input voltage have no effect on the conversion result. Values for the sample clock t<sub>S</sub> depend on programming.

2. Tested in production.

#### **Electromagnetic interference (EMI)**

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm IEC 61967-2 which specifies the board and the loading of each pin.

| Symbol           |                       | Conditions                                                           |                   |                     |                   |       |

|------------------|-----------------------|----------------------------------------------------------------------|-------------------|---------------------|-------------------|-------|

|                  | Parameter             |                                                                      | Monitored         | Max f <sub>HS</sub> | Unit              |       |

|                  |                       | General conditions                                                   | frequency band    | 16 MHz/<br>8 MHz    | 16 MHz/<br>16 MHz |       |

|                  |                       | $V_{DD} = 5 V,$<br>$T_A = 25 °C,$<br>LQFP32 package<br>conforming to | 0.1 MHz to 30 MHz | 5                   | 5                 |       |

| 6                | Peak level            |                                                                      | 30 MHz to 130 MHz | 4                   | 5                 | dBµV  |

| S <sub>EMI</sub> |                       |                                                                      | 130 MHz to 1 GHz  | 5                   | 5                 |       |

|                  | EMI level IEC 61967-2 |                                                                      |                   | 2.5                 | 2.5               | level |

| Table | 58. | EMI | data |

|-------|-----|-----|------|

|       |     |     |      |

1. Guaranteed by characterization results.

#### Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, DLU and LU) using specific measurement methods, the product is stressed to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

#### Electrostatic discharge (ESD)

Electrostatic discharges (one positive then one negative pulses separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). One model can be simulated: Human body model. This test conforms to the JESD22-A114A/A115A standard. For more details, refer to the application note AN1181.

| Symbol                | Ratings                                               | Conditions                                          | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|-----------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage<br>(Human body model) | $T_A = 25^{\circ}C$ , conforming to JESD22-A114     | 3A    | 4000                            |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (Charge device model) | T <sub>A</sub> = 25°C, conforming to<br>JESD22-C101 | 3     | 500                             | V    |

| V <sub>ESD(MM)</sub>  | Electrostatic discharge voltage (Machine model)       | T <sub>A</sub> = 25°C, conforming to<br>JESD22-A115 | В     | 200                             |      |

Table 59. ESD absolute maximum ratings

1. Guaranteed by characterization results.

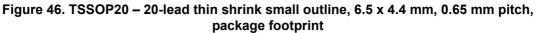

# Table 62. TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, package mechanical data (continued)

| Symbol | millimeters |      |       | inches <sup>(1)</sup> |      |        |

|--------|-------------|------|-------|-----------------------|------|--------|

|        | Min.        | Тур. | Max.  | Min.                  | Тур. | Max.   |

| k      | 0°          | -    | 8°    | 0°                    | -    | 8°     |

| aaa    | -           | -    | 0.100 | -                     | -    | 0.0039 |

1. Values in inches are converted from mm and rounded to four decimal digits.

2. Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15mm per side.

3. Dimension "E1" does not include interlead flash or protrusions. Interlead flash or protrusions shall not exceed 0.25mm per side.

<sup>1.</sup> Dimensions are expressed in millimeters.

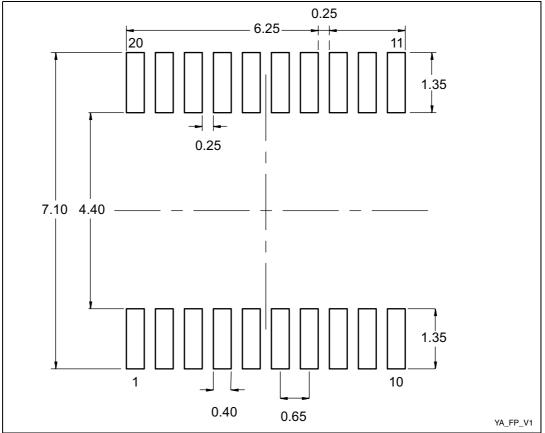

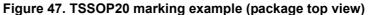

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

1. Parts marked as "ES" or "E" are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity.

#### 10.4 Thermal characteristics

The maximum chip junction temperature (T<sub>Jmax</sub>) must never exceed the values given in Table 26: General operating conditions.

T<sub>.lmax</sub>, in degrees Celsius, may be calculated using the following equation:

$$T_{Jmax} = T_{Amax} + (P_{Dmax} \times \Theta_{JA})$$

Where:

- TAmax is the maximum ambient temperature in °C \_

- $\Theta_{IA}$  is the package junction-to-ambient thermal resistance in  $^\circ$  C/W

- $P_{Dmax}$  is the sum of  $P_{INTmax}$  and  $P_{I/Omax}$  ( $P_{Dmax} = P_{INTmax} + P_{I/Omax}$ )

- $\mathsf{P}_{\mathsf{INTmax}}$  is the product of  $\mathsf{I}_{\mathsf{DD}}$  and  $\mathsf{V}_{\mathsf{DD}},$  expressed in Watts. This is the maximum chip internal power.

- P<sub>I/Omax</sub> represents the maximum power dissipation on output pins Where:

$$\label{eq:P_I/Omax} \begin{split} &\mathsf{P}_{\mathsf{I}/\mathsf{Omax}} = \Sigma \; (\mathsf{V}_{\mathsf{OL}} * \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) * \mathsf{I}_{\mathsf{OH}}), \\ & \mathsf{taking into account the actual V_{\mathsf{OL}}/\mathsf{I}_{\mathsf{OL}} \; \mathsf{and V}_{\mathsf{OH}}/\mathsf{I}_{\mathsf{OH}} \; \mathsf{of the I}/\mathsf{Os at low and high level} \end{split}$$

in the application.

| Symbol          | Parameter                                                  | Value | Unit |

|-----------------|------------------------------------------------------------|-------|------|

| Θ <sub>JA</sub> | Thermal resistance junction-ambient<br>TSSOP20 - 4 x 4 mm  | 110   | °C/W |

|                 | Thermal resistance junction-ambient<br>LQFP 32 - 7 x 7 mm  | 60    |      |

|                 | Thermal resistance junction-ambient<br>VFQFPN32 - 5 x 5 mm | TBD   |      |

#### Table 64. Thermal characteristics<sup>(1)</sup>

1. Thermal resistances are based on JEDEC JESD51-2 with 4-layer PCB in a natural convection environment.

#### 10.4.1 **Reference document**

JESD51-2 integrated circuits thermal test method environment conditions - natural convection (still air). Available from www.jedec.org.

#### 10.4.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the order code (see Section 11: Ordering information).

The following example shows how to calculate the temperature range needed for a given application.

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics – All rights reserved

DocID025118 Rev 6