Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8A                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 16MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 28                                                                    |

| Program Memory Size        | 8KB (8K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 640 x 8                                                               |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 7x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | 32-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af6226tay |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.6 **Power management**

For efficient power management, the application can be put in one of four different lowpower modes. Users can configure each mode to obtain the best compromise between lowest power consumption, fastest start-up time and available wakeup sources.

- **Wait mode**: in this mode, the CPU is stopped but peripherals are kept running. The wakeup is performed by an internal or external interrupt or reset.

- Active-halt mode with regulator on: in this mode, the CPU and peripheral clocks are stopped. An internal wakeup is generated at programmable intervals by the auto wake up unit (AWU). The main voltage regulator is kept powered on, so current consumption is higher than in Active-halt mode with regulator off, but the wakeup time is faster. Wakeup is triggered by the internal AWU interrupt, external interrupt or reset.

- Active-halt mode with regulator off: this mode is the same as Active-halt with regulator on, except that the main voltage regulator is powered off, so the wake up time is slower.

- **Halt mode**: in this mode the microcontroller uses the least power. The CPU and peripheral clocks are stopped, the main voltage regulator is powered off. Wakeup is triggered by external event or reset.

# 4.7 Watchdog timers

The watchdog system is based on two independent timers providing maximum security to the applications.

Activation of the watchdog timers is controlled by option bytes or by software. Once activated, the watchdogs cannot be disabled by the user program without performing a reset.

### Window watchdog timer

The window watchdog is used to detect the occurrence of a software fault, usually generated by external interferences or by unexpected logical conditions, which cause the application program to abandon its normal sequence.

The window function can be used to trim the watchdog behavior to match the application timing perfectly. The application software must refresh the counter before time-out and during a limited time window.

A reset is generated in two situations:

- 1. Timeout: at 16 MHz CPU clock the time-out period can be adjusted between 75  $\mu$ s up to 64 ms.

- 2. Refresh out of window: the downcounter is refreshed before its value is lower than the one stored in the window register.

#### Independent watchdog timer

The independent watchdog peripheral can be used to resolve processor malfunctions due to hardware or software failures.

It is clocked by the 128 kHz LSI internal RC clock source, and thus stays active even in case of a CPU clock failure.

The IWDG time base spans from 60 µs to 1 s

## 4.8 Auto wakeup counter

- Used for auto wakeup from active halt mode

- Clock source: Internal 128 kHz internal low frequency RC oscillator or external clock

- LSI clock can be internally connected to TIM1 input capture channel 1 for calibration

### 4.9 Beeper

The beeper function outputs a signal on the BEEP pin for sound generation. The signal is in the range of 1, 2 or 4 kHz.

The beeper output port is only available through the alternate function remap option bit AFR7.

## 4.10 TIM1 - 16-bit advanced control timer

This is a high-end timer designed for a wide range of control applications. With its complementary outputs, dead-time control and center-aligned PWM capability, the field of applications is extended to motor control, lighting and half-bridge driver.

- 16-bit up, down and up/down auto-reload counter with 16-bit fractional prescaler.

- Four independent capture/compare channels (CAPCOM) configurable as input capture, output compare, PWM generation (edge and center aligned mode) and single pulse mode output.

- Synchronization module to control the timer with external signals or to synchronise with TIM5 or TIM6

- Break input to force the timer outputs into a defined state

- Three complementary outputs with adjustable dead time

- Encoder mode

- Interrupt sources: 3 x input capture/output compare, 1 x overflow/update, 1 x break

# 5.3 Alternate function remapping

As shown in the rightmost column of *Table 6*, *Table 7* and *Table 8* some alternate functions can be remapped at different I/O ports by programming one of eight AFR (alternate function remap) option bits. Refer to *Section 8: Option bytes on page 46*. When the remapping option is active, the default alternate function is no longer available.

To use an alternate function, the corresponding peripheral must be enabled in the peripheral registers.

Alternate function remapping does not effect GPIO capabilities of the I/O ports (see the GPIO section of STM8S series and STM8AF series 8-bit microcontrollers reference manual, RM0016).

| Address                   | Block                             | Block Register label Register name     |                                            | Reset<br>status     |  |  |

|---------------------------|-----------------------------------|----------------------------------------|--------------------------------------------|---------------------|--|--|

| 0x00 50B3                 | RST                               | RST_SR                                 | Reset status register                      | 0xXX <sup>(1)</sup> |  |  |

| 0x00 50B4 to<br>0x00 50BF |                                   | Re                                     | Reserved area (12 byte)                    |                     |  |  |

| 0x00 50C0                 | CLK                               | CLK_ICKR                               | Internal clock control register            | 0x01                |  |  |

| 0x00 50C1                 | ULK                               | CLK_ECKR                               | External clock control register            | 0x00                |  |  |

| 0x00 50C2                 |                                   | R                                      | eserved area (1 byte)                      |                     |  |  |

| 0x00 50C3                 |                                   | CLK_CMSR                               | Clock master status register               | 0xE1                |  |  |

| 0x00 50C4                 |                                   | CLK_SWR                                | Clock master switch register               | 0xE1                |  |  |

| 0x00 50C5                 |                                   | CLK_SWCR Clock switch control register |                                            |                     |  |  |

| 0x00 50C6                 | CLK_CKDIVR Clock divider register |                                        | 0x18                                       |                     |  |  |

| 0x00 50C7                 | ULK                               | CLK_PCKENR1                            | Peripheral clock gating register 1         | 0xFF                |  |  |

| 0x00 50C8                 |                                   | CLK_CSSR                               | Clock security system register             | 0x00                |  |  |

| 0x00 50C9                 |                                   | CLK_CCOR                               | Configurable clock control register        | 0x00                |  |  |

| 0x00 50CA                 |                                   | CLK_PCKENR2                            | Peripheral clock gating register 2         | 0xFF                |  |  |

| 0x00 50CB                 |                                   | R                                      | eserved area (1 byte)                      |                     |  |  |

| 0x00 50CC                 |                                   | CLK_HSITRIMR                           | HSI clock calibration trimming register    | 0x00                |  |  |

| 0x00 50CD                 | CLK                               | CLK_SWIMCCR                            | SWIM clock control register                | 0bXXXX<br>XXX0      |  |  |

| 0x00 50CE<br>to 0x00 50D0 |                                   | Reserved area (3 byte)                 |                                            |                     |  |  |

| 0x00 50D1                 | WWDG                              | WWDG_CR                                | WWDG control register                      | 0x7F                |  |  |

| 0x00 50D2                 | WWDG                              | WWDG_WR                                | WWDR window register                       | 0x7F                |  |  |

| 0x00 50D3 to<br>0x00 50DF |                                   | Re                                     | eserved area (13 byte)                     |                     |  |  |

| 0x00 50E0                 |                                   | IWDG_KR                                | IWDG key register                          | 0xXX <sup>(2)</sup> |  |  |

| 0x00 50E1                 | IWDG                              | IWDG_PR                                | IWDG prescaler register                    | 0x00                |  |  |

| 0x00 50E2                 |                                   | IWDG_RLR                               | IWDG reload register                       | 0xFF                |  |  |

| 0x00 50E3 to<br>0x00 50EF |                                   | Re                                     | eserved area (13 byte)                     |                     |  |  |

| 0x00 50F0                 |                                   | AWU_CSR1                               | AWU control/status register 1              | 0x00                |  |  |

| 0x00 50F1                 | AWU                               | AWU_APR                                | AWU asynchronous prescaler buffer register | 0x3F                |  |  |

| 0x00 50F2                 |                                   | AWU_TBR                                | AWU timebase selection register            | 0x00                |  |  |

| 0x00 50F3                 | BEEP                              | BEEP_CSR                               | BEEP control/status register               | 0x1F                |  |  |

| 0x00 50F4 to<br>0x00 50FF |                                   | Re                                     | eserved area (12 byte)                     |                     |  |  |

| Table 11. | General | hardware     | register | map   | (continued) | 1 |

|-----------|---------|--------------|----------|-------|-------------|---|

|           | General | indi di di c | register | map ( | continueu   |   |

| Priority | Source<br>block | Description                     | Wakeup from<br>halt mode | Wakeup from<br>active-halt<br>mode | Interrupt vector<br>address |

|----------|-----------------|---------------------------------|--------------------------|------------------------------------|-----------------------------|

| 23       | TIM6            | TIM6<br>update/overflow/trigger | -                        | -                                  | 0x00 8064                   |

| 24       | Flash           | EOP/WR_PG_DIS                   | -                        | -                                  | 0x00 8068                   |

Table 13. Interrupt mapping (continued)

1. Except PA1.

# 8.1 Option byte description

| Table | 15. | Option | bvte | description |

|-------|-----|--------|------|-------------|

| Iabio |     | option | ~ ,  | accomption  |

| Option byte no. | Description                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPT0            | ROP[7:0]: Memory readout protection (ROP)<br>0xAA: Enable readout protection (write access via SWIM protocol)<br>Note: Refer to STM8S series and STM8AF series 8-bit microcontrollers<br>reference manual (RM0016) section on Flash/EEPROM memory<br>readout protection for details.                                                                                            |

| OPT1            | UBC[7:0]: User boot code area<br>0x00: No UBC, no write-protection<br>0x01: Page 0 defined as UBC, memory write-protected<br>0x02: Page 0 to 1 defined as UBC, memory write-protected<br>Pages 0 and 1 contain the interrupt vectors.<br><br>0x7F: Pages 0 to 126 defined as UBC, memory write-protected<br>Other values: Page 0 to 127 defined as UBC, memory write-protected. |

|                 | Note: Refer to STM8S series and STM8AF series 8-bit microcontrollers reference manual (RM0016) section on Flash/EEPROM write protection for more details.                                                                                                                                                                                                                       |

| OPT2            | <b>AFR[7:0]</b><br>Refer to the following sections for the alternate function remapping descriptions of bits [7:2] and [1:0] respectively.                                                                                                                                                                                                                                      |

|                 | HSITRIM: high-speed internal clock trimming register size<br>0: 3-bit trimming supported in CLK_HSITRIMR register<br>1: 4-bit trimming supported in CLK_HSITRIMR register                                                                                                                                                                                                       |

|                 | LSI_EN: low-speed internal clock enable<br>0: LSI clock is not available as CPU clock source<br>1: LSI clock is available as CPU clock source                                                                                                                                                                                                                                   |

| OPT3            | IWDG_HW: Independent watchdog<br>0: IWDG independent watchdog activated by software<br>1: IWDG independent watchdog activated by hardware                                                                                                                                                                                                                                       |

|                 | WWDG_HW: Window watchdog activation<br>0: WWDG window watchdog activated by software<br>1: WWDG window watchdog activated by hardware                                                                                                                                                                                                                                           |

|                 | WWDG_HALT: Window watchdog reset on Halt<br>0: No reset generated on Halt if WWDG active<br>1: Reset generated on Halt if WWDG active                                                                                                                                                                                                                                           |

| AFR1 option bit value | AFR0 option bit value | I/O port                                                                                | Alternate function<br>mapping |  |

|-----------------------|-----------------------|-----------------------------------------------------------------------------------------|-------------------------------|--|

| 0                     | 0                     | AFR1 and AFR0 remapping options inactive:<br>Default alternate functions <sup>(1)</sup> |                               |  |

|                       |                       | PC5                                                                                     | TIM5_CH1                      |  |

| 0                     | 1                     | PC6                                                                                     | TIM1_CH1                      |  |

|                       |                       | PC7                                                                                     | TIM1_CH2                      |  |

| 1                     | 0                     | PA3                                                                                     | SPI_NSS                       |  |

| I                     |                       | PD2                                                                                     | TIM5_CH3                      |  |

|                       | 1 <sup>(2)</sup>      | PD2                                                                                     | TIM5_CH3                      |  |

|                       |                       | PC5                                                                                     | TIM5_CH1                      |  |

|                       |                       | PC6                                                                                     | TIM1_CH1                      |  |

|                       |                       | PC7                                                                                     | TIM1_CH2                      |  |

| 1 <sup>(2)</sup>      |                       | PC2                                                                                     | TIM1_CH3N                     |  |

|                       |                       | PC1                                                                                     | TIM1_CH2N                     |  |

|                       |                       | PE5                                                                                     | TIM1_CH1N                     |  |

|                       |                       | PA3                                                                                     | LINUART_TX                    |  |

|                       |                       | PF4                                                                                     | LINUART_RX                    |  |

Table 19. STM8AF6226 alternate function remapping bits [1:0] for 32-pin packages

1. Refer to the pin descriptions.

If both AFR1 and AFR0 option bits are set, the SPI hardware NSS management feature is no more available. If this remapping option is selected and the SPI is enabled, the SSM bit must be configured in the SPI\_CR2 register to select software NSS management.

| Table 20. STM8AF6213/STM8AF6223 alternate function remapping bits [1:0] |

|-------------------------------------------------------------------------|

| for 20-pin packages                                                     |

| 101 20-pini packages  |                       |                                                                                         |                               |  |  |

|-----------------------|-----------------------|-----------------------------------------------------------------------------------------|-------------------------------|--|--|

| AFR1 option bit value | AFR0 option bit value | I/O port                                                                                | Alternate function<br>mapping |  |  |

| 0                     | 0                     | AFR1 and AFR0 remapping options inactive:<br>Default alternate functions <sup>(1)</sup> |                               |  |  |

| 0                     | 1                     | PC5                                                                                     | TIM5_CH1                      |  |  |

|                       |                       | PC6                                                                                     | TIM1_CH1                      |  |  |

|                       |                       | PC7                                                                                     | TIM1_CH2                      |  |  |

| 1                     | 0                     | PA3                                                                                     | SPI_NSS                       |  |  |

|                       |                       | PD2                                                                                     | TIM5_CH3                      |  |  |

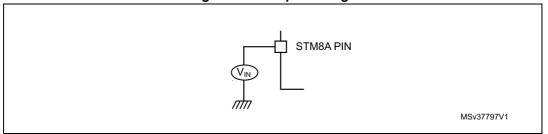

### 9.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 8.

#### Figure 8. Pin input voltage

# 9.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 22: Voltage characteristics*, *Table 23: Current characteristics* and *Table 24: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect the device's reliability.

Device mission profile (application conditions) is compliant with JEDEC JESD47 Qualification Standard, extended mission profiles are available on demand.

| Symbol                             | Ratings                                                           | Min                                                                  | Max                   | Unit  |  |

|------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------|-------|--|

| $V_{DDx}$ - $V_{SS}$               | Supply voltage (including $V_{DDA and} V_{DDIO}$ ) <sup>(1)</sup> | -0.3                                                                 | 6.5                   | V     |  |

| V                                  | Input voltage on true open drain pins <sup>(2)</sup>              | V <sub>SS</sub> - 0.3                                                | 6.5                   | V     |  |

| V <sub>IN</sub>                    | Input voltage on any other pin <sup>(2)</sup>                     | V <sub>SS</sub> - 0.3                                                | V <sub>DD</sub> + 0.3 | v     |  |

| V <sub>DDx</sub> - V <sub>DD</sub> | Variations between different power pins                           | -                                                                    | 50                    | m\/   |  |

| $ V_{SSx} - V_{SS} $               | Variations between all the different ground pins                  | -                                                                    | 50                    | 50 mV |  |

| V <sub>ESD</sub>                   | Electrostatic discharge voltage                                   | see Absolute maximum ratin<br>(electrical sensitivity) on<br>page 89 |                       | _     |  |

1. All power (V<sub>DD</sub>) and ground (V<sub>SS</sub>) pins must always be connected to the external power supply

2. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected

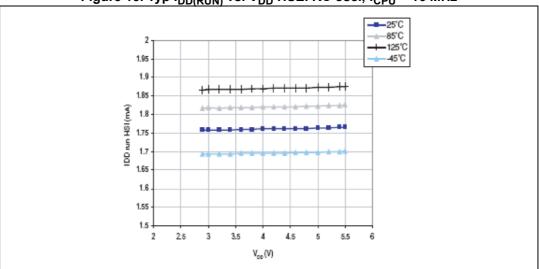

Figure 13. Typ  $I_{DD(RUN)}$  vs.  $V_{DD}$  HSEI RC osc.,  $f_{CPU}$  = 16 MHz

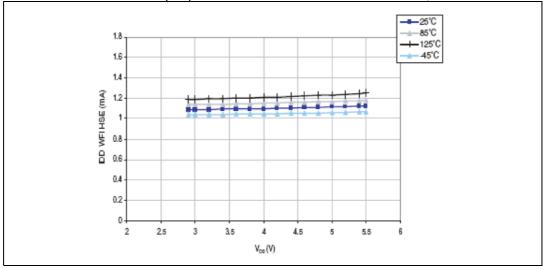

Figure 14. Typ  $I_{DD(WFI)}$  vs.  $V_{DD}$  HSE user external clock,  $f_{CPU}$  = 16 MHz

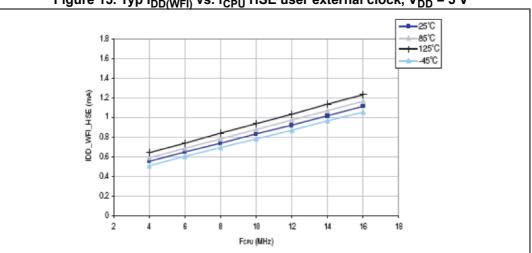

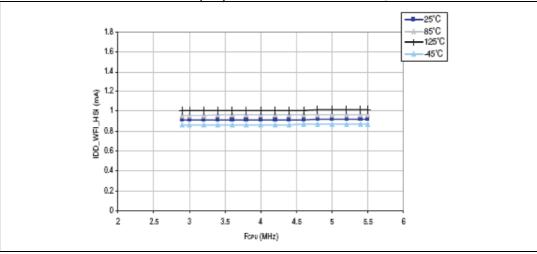

Figure 15. Typ  $I_{DD(WFI)}$  vs.  $f_{CPU}$  HSE user external clock,  $V_{DD}$  = 5 V

Figure 16. Typ I<sub>DD(WFI)</sub> vs. V<sub>DD</sub> HSI RC osc.,  $f_{CPU}$  = 16 MHz

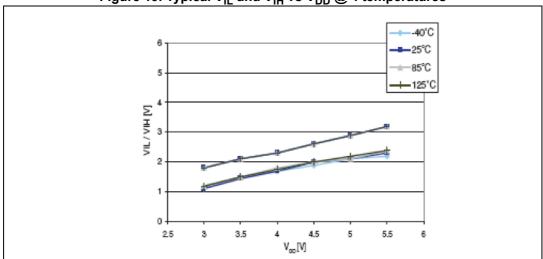

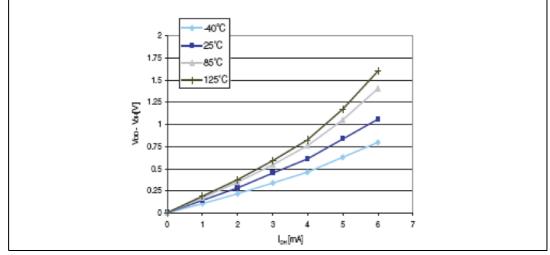

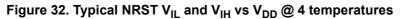

Figure 19. Typical  $V_{IL}$  and  $V_{IH}$  vs  $V_{DD}$  @ 4 temperatures

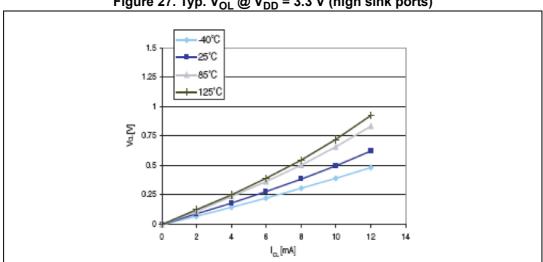

Figure 27. Typ. V<sub>OL</sub> @ V<sub>DD</sub> = 3.3 V (high sink ports)

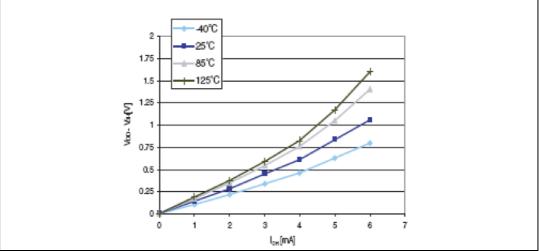

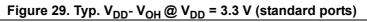

Figure 28. Typ.  $V_{DD}$ -  $V_{OH} @ V_{DD}$  = 5 V (standard ports)

DocID025118 Rev 6

# 9.3.7 Reset pin characteristics

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol                  | Parameter                                             | Conditions             | Min                         | Тур | Max                   | Unit |

|-------------------------|-------------------------------------------------------|------------------------|-----------------------------|-----|-----------------------|------|

| V <sub>IL(NRST)</sub>   | NRST input low level voltage <sup>(1)</sup>           | -                      | -0.3                        | -   | $0.3 \times V_{DD}$   |      |

| V <sub>IH(NRST)</sub>   | NRST input high level voltage <sup>(1)</sup>          | I <sub>OL</sub> = 2 mA | $0.7 	ext{ x V}_{	ext{DD}}$ | -   | V <sub>DD</sub> + 0.3 | V    |

| V <sub>OL(NRST)</sub>   | NRST output low level voltage <sup>(1)</sup>          | -                      | -                           | -   | 0.5                   |      |

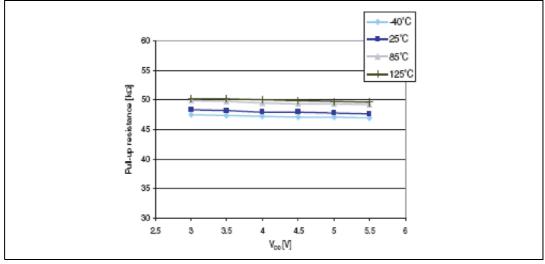

| R <sub>PU(NRST)</sub>   | NRST pull-up resistor <sup>(2)</sup>                  | -                      | 30                          | 55  | 80                    | kΩ   |

| t <sub>IFP(NRST)</sub>  | NRST input filtered pulse <sup>(3)</sup>              | -                      | -                           | -   | 75                    |      |

| t <sub>INFP(NRST)</sub> | NRST Input not filtered pulse duration <sup>(3)</sup> | -                      | 500                         | -   | -                     | ns   |

| t <sub>OP(NRST)</sub>   | NRST output pulse <sup>(3)</sup>                      | -                      | 20                          | -   | -                     | μs   |

| Table 51 | . NRST | pin ( | characteristics |

|----------|--------|-------|-----------------|

|          |        | PILL  | onunuotoristios |

1. Guaranteed by characterization results.

2. The R<sub>PU</sub> pull-up equivalent resistor is based on a resistive transistor.

3. Guaranteed by design.

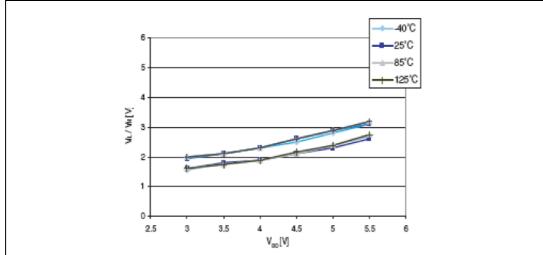

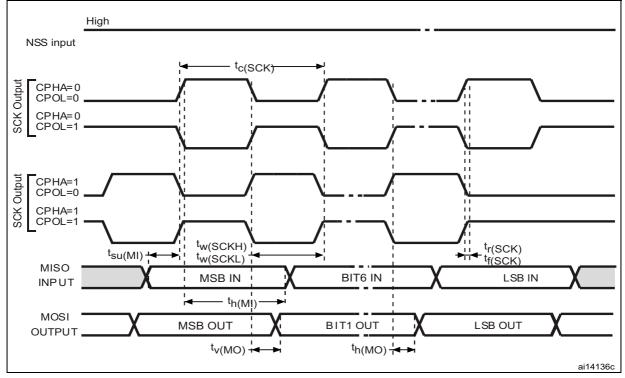

Figure 37. SPI timing diagram - slave mode and CPHA = 1

1. Measurement points are at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$

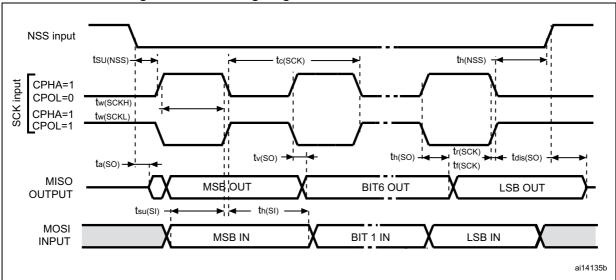

### Figure 38. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$

### 9.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

### Functional EMS (electromagnetic susceptibility)

While executing a simple application (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- **FESD**: Functional electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be recovered by applying a low state on the NRST pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see the application note reference AN1015).

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                                                                                                                                | Level/class        |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $\label{eq:VDD} \begin{array}{l} V_{DD} = 3.3 \text{ V},  \text{T}_{\text{A}} = 25 \ ^{\circ}\text{C}, \\ \text{f}_{\text{MASTER}} = 16 \text{ MHz} \text{ (HSI clock)}, \\ \text{Conforms to IEC 61000-4-2} \end{array}$ | 2/B <sup>(1)</sup> |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, $T_A$ = 25 °C,<br>$f_{MASTER}$ = 16 MHz (HSI clock),<br>Conforms to IEC 61000-4-4                                                                                                                       | 4/A                |

#### Table 57. EMS data

Data obtained with HSI clock configuration, after applying hardware recommendations described in AN2860 (EMC guidelines for STM8S microcontrollers).

| Currence of | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|-------------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol      | Min         | Тур   | Мах   | Min                   | Тур    | Max    |

| А           | -           | -     | 1.600 | -                     | -      | 0.0630 |

| A1          | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2          | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b           | 0.300       | 0.370 | 0.450 | 0.0118                | 0.0146 | 0.0177 |

| С           | 0.090       | -     | 0.200 | 0.0035                | -      | 0.0079 |

| D           | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| D1          | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| D3          | -           | 5.600 | -     | -                     | 0.2205 | -      |

| E           | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| E1          | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| E3          | -           | 5.600 | -     | -                     | 0.2205 | -      |

| е           | -           | 0.800 | -     | -                     | 0.0315 | -      |

| L           | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1          | -           | 1.000 | -     | -                     | 0.0394 | -      |

| k           | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| CCC         | -           | -     | 0.100 | -                     | -      | 0.0039 |

| Table 61. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package |

|-------------------------------------------------------------------|

| mechanical data                                                   |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

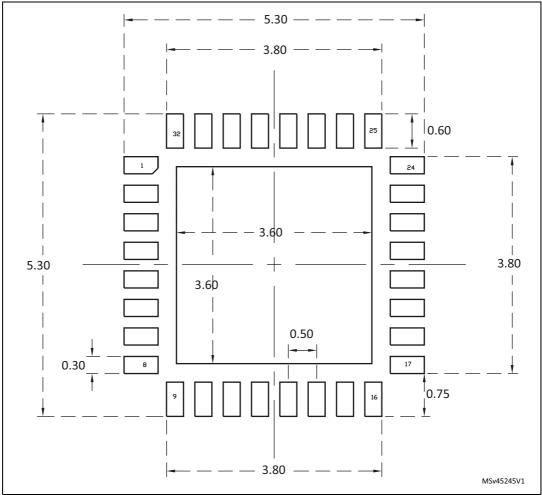

Figure 49. VFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch very thin profile fine pitch quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

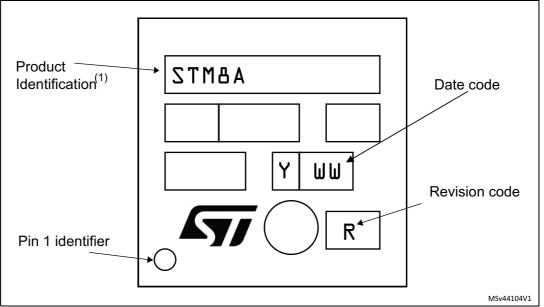

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Parts marked as "ES" or "E" are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity.

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax}$ = 75 °C (measured according to JESD51-2), I<sub>DDmax</sub> = 8 mA, V<sub>DD</sub> = 5 V Maximum 20 I/Os used at the same time in output at low level with:

Maximum 20 I/Os used at the same time in output at low level with:

$I_{OL}$  = 8 mA,  $V_{OL}$  = 0.4 V

P<sub>INTmax</sub> = 8 mA x 5 V= 400 mW

$P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{ V} = 64 \text{ mW}$

This gives: P<sub>INTmax</sub> = 400 mW and P<sub>IOmax</sub> 64 mW:

P<sub>Dmax</sub> = 400 mW + 64 mW

Thus: P<sub>Dmax</sub> = 464 mW.

Using the values obtained in Table 64: Thermal characteristics on page 101  $T_{Jmax}$  is calculated as follows:

For LQFP32 60 °C/W

T<sub>Jmax</sub> = 75 °C + (60 °C/W x464 mW) = 75 °C + 27.8 °C = 102.8 °C

This is within the range of the suffix C version parts (-40 <  $T_J$  < 125 °C).

Parts must be ordered at least with the temperature range suffix C.

# 13 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 11-Oct-2013 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 16-Dec-2013 | 2        | <ul> <li>Changed the document status to Production data.</li> <li>Updated <i>Figure: STM8AF6223PxAx TSSOP20 pinout</i> to add SPI_NSS to PD4, TLI to PD2, and change remap function on PB5 from TIM5_BKIn to TIM1_BKIN.</li> <li>Updated <i>Table: STM8AF6223PxAx TSSOP20 pin description</i> to add SPI_NSS to PD4 and TLI to PD2.</li> <li>Updated <i>Table: STM8AF6223 TSSOP20 pin description</i> and <i>Table: LQFP32 pin description</i>.</li> <li>Updated AFR2 definition in <i>Table: STM8AF6223PxAx alternate function remapping bits</i> [7:2] for 20-pin <i>packages</i>.</li> <li>Removed the remapping option on PA3 for AFR[1:0]=10 in <i>Table: STM8AF6223PxAx alternate function remapping bits</i> [1:0] for 20-pin <i>packages</i>.</li> <li>Added note and removed remapping option on PA3 for AFR[1:0]=11 in <i>Table: STM8AF6223 alternate function remapping bits</i> [7:2] for 20-pin packages.</li> <li>Added the note below <i>Table: STM8AF6226T alternate function remapping bits</i> [1:0] for 32-pin packages.</li> <li>Updated <i>Table: I2C characteristics</i> to modify t<sub>h(SDA)</sub> and add t<sub>SP</sub>.</li> <li>Updated <i>Section: C assembly toolchains</i>.</li> </ul> |  |

| 03-Apr-2014 | 3        | Replaced STM8AF6226T by STM8AF6226 part number.Added STM8AF6223A part number to coverSTM8AF6223PxAx order codes.Removed LINUART alternate function for PA3 in Table:STM8AF6223PxAx TSSOP20 pin description.Removed note 3 for $I_{DD(AH)}$ in Table: Total currentconsumption in active halt mode at VDD = 5 V.Updated the remapping option on PA3 for AFR[1:0]=11in Table: STM8AF6223 alternate function remapping bits[1:0] for 20-pin packages.Updated notes related to $t_{RET}$ minimum value in Table:Data memory.Updated Table: ESD absolute maximum ratings.Added notes related to protrusions and gate burrs for Dand E1 dimensions in Table: 20-pin, 4.40 mm body, 0.65mm pitch mechanical data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

### Table 66. Document revision history