Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Core ProcessorSTM8ACore Size8-BitSpeed16MHzConnectivityIPC, LINbus, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O28Program Memory Size8KB (8K × 8)Program Memory TypeFLASHEEPROM Size640 × 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 5x10bOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case32-LQFP (7x7)                                |                            |                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------|

| Core Size8-BitCore Size16MHzSpeed16MHzConnectivityPC, LINbus, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O28Program Memory Size8KB (8K x 8)Program Memory TypeFLASHEEPROM Size640 x 8RAM Size1K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 5x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case32-LQFP (7x7) | Product Status             | Not For New Designs                                                   |

| Speed16MHzConnectivityIPC, LINbus, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O28Program Memory Size8KB (8K x 8)Program Memory TypeFLASHEEPROM Size640 x 8RAM Size1K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 5x10bOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case32-LQFP (7x7)                                                   | Core Processor             | STM8A                                                                 |

| ConnectivityIPC, LINbus, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O28Program Memory SizeBKB (8K x 8)Program Memory TypeFLASHEEPROM Size640 x 8RAM SizeIK x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 5x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case32-LQFP (7x7)                                      | Core Size                  | 8-Bit                                                                 |

| PeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O28Program Memory Size8KB (8K x 8)Program Memory TypeFLASHEEPROM Size640 x 8RAM Size1K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 5x10bOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case32-LQFP (7x7)                                                                                                     | Speed                      | 16MHz                                                                 |

| Number of I/O28Program Memory Size8KB (8K x 8)Program Memory TypeFLASHEEPROM Size640 x 8RAM Size1K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 5x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case32-LQFP (7x7)                                                                                                                              | Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                             |

| Program Memory Size8KB (8K x 8)Program Memory TypeFLASHEEPROM Size640 x 8RAM Size1K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 5x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case32-LQFP (7x7)                                                                                                                                             | Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Program Memory TypeFLASHEEPROM Size640 x 8RAM Size1K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 5x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case32-LQFP (7x7)                                                                                                                                                                            | Number of I/O              | 28                                                                    |

| EEPROM Size640 x 8RAM Size1K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 5x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case32-LQFPSupplier Device Package32-LQFP (7x7)                                                                                                                                                                      | Program Memory Size        | 8KB (8K x 8)                                                          |

| RAM Size1K × 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 5x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case32-LQFPSupplier Device Package32-LQFP (7x7)                                                                                                                                                                                        | Program Memory Type        | FLASH                                                                 |

| Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 5x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case32-LQFPSupplier Device Package32-LQFP (7x7)                                                                                                                                                                                                      | EEPROM Size                | 640 x 8                                                               |

| Data ConvertersA/D 5x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case32-LQFPSupplier Device Package32-LQFP (7x7)                                                                                                                                                                                                                                         | RAM Size                   | 1K x 8                                                                |

| Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case32-LQFPSupplier Device Package32-LQFP (7x7)                                                                                                                                                                                                                                                                 | Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Operating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case32-LQFPSupplier Device Package32-LQFP (7x7)                                                                                                                                                                                                                                                                                        | Data Converters            | A/D 5x10b                                                             |

| Mounting Type     Surface Mount       Package / Case     32-LQFP       Supplier Device Package     32-LQFP (7x7)                                                                                                                                                                                                                                                                                                  | Oscillator Type            | Internal                                                              |

| Package / Case     32-LQFP       Supplier Device Package     32-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                        | Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Supplier Device Package32-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                              | Mounting Type              | Surface Mount                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                   | Package / Case             | 32-LQFP                                                               |

| Purchase URL https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af6226tcy                                                                                                                                                                                                                                                                                                                                | Supplier Device Package    | 32-LQFP (7x7)                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                   | Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af6226tcy |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Intro | duction                                                      |

|---|-------|--------------------------------------------------------------|

| 2 | Desc  | ription                                                      |

| 3 | Bloc  | k diagram                                                    |

| 4 | Prod  | uct overview                                                 |

|   | 4.1   | Central processing unit (CPU) 12                             |

|   |       | 4.1.1 Architecture and registers                             |

|   |       | 4.1.2 Addressing                                             |

|   |       | 4.1.3 Instruction set                                        |

|   | 4.2   | Single wire interface module (SWIM) and debug module (DM) 13 |

|   |       | 4.2.1 SWIM                                                   |

|   |       | 4.2.2 Debug module                                           |

|   | 4.3   | Interrupt controller                                         |

|   | 4.4   | Flash program and data EEPROM memory    13                   |

|   |       | 4.4.1 Write protection (WP)                                  |

|   |       | 4.4.2 Read-out protection (ROP)                              |

|   | 4.5   | Clock controller                                             |

|   |       | 4.5.1 Features                                               |

|   | 4.6   | Power management                                             |

|   | 4.7   | Watchdog timers                                              |

|   | 4.8   | Auto wakeup counter                                          |

|   | 4.9   | Beeper                                                       |

|   | 4.10  | TIM1 - 16-bit advanced control timer 17                      |

|   | 4.11  | TIM5 - 16-bit general purpose timer                          |

|   | 4.12  | TIM6 - 8-bit basic timer                                     |

|   | 4.13  | Analog-to-digital converter (ADC1) 19                        |

|   | 4.14  | Communication interfaces                                     |

|   |       | 4.14.1 LINUART                                               |

|   |       | 4.14.2 Serial peripheral interface (SPI)                     |

|   |       | 4.14.3 Inter integrated circuit (I <sup>2</sup> C) interface |

# 1 Introduction

The datasheet contains the description of STM8AF6213, STM8AF6223, STM8AF6223A and STM8AF6226 features, pinout, electrical characteristics, mechanical data and ordering information.

- For complete information on the STM8A microcontroller memory, registers and peripherals, please refer to STM8S series and STM8AF series 8-bit microcontrollers reference manual (RM0016).

- For information on programming, erasing and protection of the internal Flash memory please refer to the STM8 Flash programming manual (PM0051).

- For information on the debug and SWIM (single wire interface module) refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).

- For information on the STM8 core, please refer to the STM8 CPU programming manual (PM0044).

# 2 Description

The STM8AF6213, STM8AF6223, STM8AF6223A and STM8AF6226 automotive 8-bit microcontrollers offer 4 to 8 Kbytes of Flash program memory, plus integrated true data EEPROM. The STM8S series and STM8AF series 8-bit microcontrollers reference manual (RM0016) refers to devices in this family as low-density. They provide the following benefits: performance, robustness and reduced system cost.

Device performance and robustness are ensured by advanced core and peripherals made in a state-of-the-art technology, a 16 MHz clock frequency, robust I/Os, independent watchdogs with separate clock source, and a clock security system.

The system cost is reduced thanks to an integrated true data EEPROM for up to 300 kwrite/erase cycles and a high system integration level with internal clock oscillators, watchdog, and brown-out reset.

Full documentation is offered as well as a wide choice of development tools.

| Device                                  | STM8AF6226                                                                                                              | STM8AF6223 | STM8AF6223A      | STM8AF6213 |  |  |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------|------------------|------------|--|--|

| Pin count                               | 32                                                                                                                      |            | 20               |            |  |  |

| Max. number of GPIOs                    | 28 including 21<br>high-sink I/Os                                                                                       |            |                  |            |  |  |

| Ext. interrupt pins                     | 28                                                                                                                      |            | 16               |            |  |  |

| Timer CAPCOM channels                   | 6                                                                                                                       | 7          | 6                | 7          |  |  |

| Timer complementary<br>outputs          | 3                                                                                                                       | 1          | 2                | 1          |  |  |

| A/D converter channels                  | 7                                                                                                                       | 5          | 7                | 5          |  |  |

| Low-density Flash program memory (byte) |                                                                                                                         | 8 K        |                  | 4 K        |  |  |

| Data EEPROM (byte)                      |                                                                                                                         | 64         | 0 <sup>(1)</sup> |            |  |  |

| RAM (byte)                              | 1 K                                                                                                                     |            |                  |            |  |  |

| Peripheral set                          | Multipurpose timer (TIM1), SPI, I2C, LINUART, window WDG,<br>independent WDG, ADC, PWM timer (TIM5), 8-bit timer (TIM6) |            |                  |            |  |  |

Table 1. STM8AF6213/23/23A/26 features

1. No read-while-write (RWW) capability

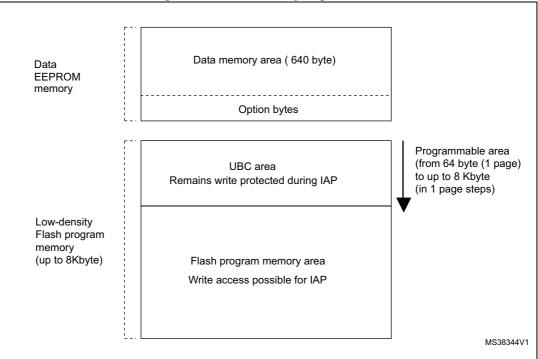

The size of the UBC is programmable through the UBC option byte, in increments of 1 page (64-byte block) by programming the UBC option byte in ICP mode.

This divides the program memory into two areas:

- Main program memory: up to 8 Kbyte minus UBC

- User-specific boot code (UBC): configurable up to 8 Kbyte

The UBC area remains write-protected during in-application programming. This means that the MASS keys do not unlock the UBC area. It protects the memory used to store the boot program, specific code libraries, reset and interrupt vectors, the reset routine and usually the IAP and communication routines.

### Figure 2. Flash memory organization

### 4.4.2 Read-out protection (ROP)

The read-out protection blocks reading and writing the Flash program memory and data EEPROM memory in ICP mode (and debug mode). Once the read-out protection is activated, any attempt to toggle its status triggers a global erase of the program and data memory. Even if no protection can be considered as totally unbreakable, the feature provides a very high level of protection for a general purpose microcontroller.

### Asynchronous communication (UART mode)

- Full duplex communication NRZ standard format (mark/space)

- Programmable transmit and receive baud rates up to 1 Mbit/s (f<sub>CPU</sub>/16) and capable of following any standard baud rate regardless of the input frequency

- Separate enable bits for transmitter and receiver

- Two receiver wakeup modes:

- Address bit (MSB)

- Idle line (interrupt)

- Transmission error detection with interrupt generation

- Parity control

### Synchronous communication

- Full duplex synchronous transfers

- SPI master operation

- 8-bit data communication

- Maximum speed: 1 Mbit/s at 16 MHz (f<sub>CPU</sub>/16)

## 4.14.2 Serial peripheral interface (SPI)

- Maximum speed: 8 Mbit/s (f<sub>MASTER</sub>/2) both for master and slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on two lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- CRC calculation

- 1 byte Tx and Rx buffer

- Slave /master selection input pin

## 4.14.3 Inter integrated circuit (I<sup>2</sup>C) interface

- I<sup>2</sup>C master features:

- Clock generation

- Start and stop generation

- I<sup>2</sup>C slave features:

- Programmable I<sup>2</sup>C address detection

- Stop bit detection

- Generation and detection of 7-bit/10-bit addressing and general call

- Supports different communication speeds:

- Standard speed (up to 100 kHz),

- Fast speed (up to 400 kHz)

# 5 Pinout and pin description

The following table presents the meaning of the abbreviations in use in the pin description tables in this section.

| Туре             | I= input, O                                                                                                                                                             | I= input, O = output, S = power supply                                                                                                                                                                |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Level            | Input                                                                                                                                                                   | Input CM = CMOS (standard for all I/Os)                                                                                                                                                               |  |  |  |  |  |  |

|                  | Output                                                                                                                                                                  | t HS = High sink                                                                                                                                                                                      |  |  |  |  |  |  |

| Output speed     | O2 = Fast (<br>O3 = Fast/s                                                                                                                                              | O1 = Slow (up to 2 MHz)<br>O2 = Fast (up to 10 MHz)<br>O3 = Fast/slow programmability with slow as default state after reset<br>O4 = Fast/slow programmability with fast as default state after reset |  |  |  |  |  |  |

| Port and control | Input                                                                                                                                                                   | float = floating, wpu = weak pull-up                                                                                                                                                                  |  |  |  |  |  |  |

| configuration    | Output                                                                                                                                                                  | Output T = true open drain, OD = open drain, PP = push pull                                                                                                                                           |  |  |  |  |  |  |

| Reset state      | Bold X (pin state after internal reset release).<br>Unless otherwise specified, the pin state is the same during the reset phase a<br>after the internal reset release. |                                                                                                                                                                                                       |  |  |  |  |  |  |

| Table 5. Legend/abbreviations | for pinout tables |

|-------------------------------|-------------------|

|-------------------------------|-------------------|

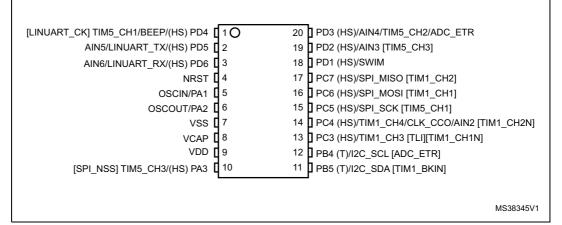

# 5.1 TSSOP20 pinouts and pin descriptions

### Figure 3. STM8AF6213/STM8AF6223 TSSOP20 pinout

1. (HS) high sink capability.

2. (T) true open drain (P-buffer and protection diode to  $V_{\text{DD}}$  not implemented).

3. [] alternate function remapping option (if the same alternate function is shown twice, it indicates an exclusive choice not a duplication of the function).

|       | Input                                          |      |          | Out | put            |                          |       |                  |    |                                   |                                                             |                                                                                |

|-------|------------------------------------------------|------|----------|-----|----------------|--------------------------|-------|------------------|----|-----------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------|

| TSSOP | Pin name                                       | Туре | floating | ndm | Ext. interrupt | High sink <sup>(1)</sup> | Speed | OD               | РР | Main<br>function<br>(after reset) | Default<br>alternate<br>function                            | Alternate<br>function<br>after remap<br>[option bit]                           |

| 10    | PA3/ TIM5_CH3<br>[SPI_NSS]                     | I/O  | x        | x   | х              | HS                       | O3    | x                | х  | Port A3                           | Timer 5<br>channel 3                                        | SPI master/<br>slave select<br>[AFR1]                                          |

| 11    | PB5/ I2C_SDA<br>[TIM1_BKIN]                    | I/O  | x        | -   | х              | -                        | 01    | T <sup>(3)</sup> | -  | Port B5                           | I2C data                                                    | Timer 1 -<br>break input<br>[AFR4]                                             |

| 12    | PB4/ I2C_SCL<br>[ADC_ETR]                      | I/O  | x        | -   | х              | -                        | O1    | T <sup>(3)</sup> | -  | Port B4                           | I2C clock                                                   | ADC<br>external<br>trigger<br>[AFR4]                                           |

| 13    | PC3/<br>TIM1_CH3/[TLI]/[<br>TIM1_CH1N]         | I/O  | X        | x   | x              | HS                       | O3    | x                | x  | Port C3                           | Timer 1 -<br>channel 3                                      | Top level<br>interrupt<br>[AFR3]<br>Timer 1<br>inverted<br>channel 1<br>[AFR7] |

| 14    | PC4/ TIM1_CH4/<br>CLK_CCO/AIN2/[<br>TIM1_CH2N] | I/O  | x        | x   | x              | HS                       | O3    | x                | x  | Port C4                           | Timer 1 -<br>channel 4<br>/configurabl<br>e clock<br>output | Analog<br>input 2<br>[AFR2]Time<br>r 1 inverted<br>channel 2<br>[AFR7]         |

| 15    | PC5/SPI_SCK<br>[TIM5_CH1]                      | I/O  | x        | x   | х              | HS                       | O3    | x                | х  | Port C5                           | SPI clock                                                   | Timer 5<br>channel 1<br>[AFR0]                                                 |

| 16    | PC6/ SPI_MOSI<br>[TIM1_CH1]                    | I/O  | x        | x   | х              | HS                       | O3    | x                | х  | Port C6                           | PI master<br>out/slave in                                   | Timer 1<br>channel 1<br>[AFR0]                                                 |

| 17    | PC7/ SPI_MISO<br>[TIM1_CH2]                    | I/O  | x        | х   | х              | HS                       | O3    | x                | х  | Port C7                           | SPI master<br>in/ slave out                                 | Timer 1<br>channel<br>2[AFR0]                                                  |

| 18    | PD1/ SWIM <sup>(4)</sup>                       | I/O  | X        | х   | х              | HS                       | 04    | х                | х  | Port D1                           | SWIM data interface                                         | -                                                                              |

## Table 6. STM8AF6213/STM8AF6223 TSSOP20 pin description (continued)

|       |                                    |      |          | Input | t              |                          | Out   | put |    |                                   |                                                                            |                                                                 |

|-------|------------------------------------|------|----------|-------|----------------|--------------------------|-------|-----|----|-----------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------|

| TSSOP | Pin name                           | Туре | floating | ndm   | Ext. interrupt | High sink <sup>(1)</sup> | Speed | QО  | ЬР | Main<br>function<br>(after reset) | Default<br>alternate<br>function                                           | Alternate<br>function<br>after remap<br>[option bit]            |

| 16    | PC6/ SPI_MOSI<br>[TIM1_CH1]        | I/O  | x        | x     | x              | HS                       | O3    | х   | х  | Port C6                           | PI master<br>out/slave in                                                  | Timer 1<br>channel 1<br>[AFR0]                                  |

| 17    | PC7/ SPI_MISO<br>[TIM1_CH2]        | I/O  | x        | х     | х              | HS                       | O3    | х   | х  | Port C7                           | SPI master<br>in/ slave out                                                | Timer 1<br>channel<br>2[AFR0]                                   |

| 18    | PD1/ SWIM <sup>(4)</sup>           | I/O  | <u>x</u> | х     | х              | HS                       | 04    | х   | х  | Port D1                           | SWIM data<br>interface                                                     | -                                                               |

| 19    | PD2/AIN3/<br>TLI[TIM5_CH3]         | I/O  | X        | х     | x              | HS                       | O3    | x   | x  | Port D2                           | -                                                                          | Analog<br>input 3<br>[AFR2]<br>Timer 5 -<br>channel 3<br>[AFR1] |

| 20    | PD3/ AIN4/<br>TIM5_CH2/<br>ADC_ETR | I/O  | X        | x     | x              | HS                       | O3    | x   | x  | Port D3                           | Analog<br>input 4<br>Timer 52 -<br>channel<br>2/ADC<br>external<br>trigger | -                                                               |

### Table 7. STM8AF6223A TSSOP20 pin description (continued)

1. I/O pins used simultaneously for high current source/sink must be uniformly spaced around the package. In addition, the total driven current must respect the absolute maximum ratings (see *Section 9.2: Absolute maximum ratings*).

When the MCU is in Halt/Active-halt mode, PA1 is automatically configured in input weak pull-up and cannot be used for waking up the device. In this mode, the output state of PA1 is not driven. It is recommended to use PA1 only in input mode if Halt/Active-halt is used in the application.

3. In the open-drain output column, 'T' defines a true open-drain I/O (P-buffer, weak pull-up, and protection diode to VDD are not implemented).

4. The PD1 pin is in input pull-up during the reset phase and after internal reset release.

| Flash program<br>memory size | Flash program<br>memory end<br>address | RAM size | RAM end address | Stack roll-over<br>address |

|------------------------------|----------------------------------------|----------|-----------------|----------------------------|

| 8 K                          | 0x00 9FFF                              | 1 K      | 0x00 03FF       | 0x00 0200                  |

| 4 K                          | 0x00 8FFF                              |          | 0000 0311       | 0,00 0200                  |

Table 9. Memory model for the devices covered in this datasheet

# 6.2 Register map

## 6.2.1 I/O port hardware register map

| Address   | Block  | Register label Register name |                                   | Reset<br>status     |

|-----------|--------|------------------------------|-----------------------------------|---------------------|

| 0x00 5000 |        | PA_ODR                       | Port A data output latch register | 0x00                |

| 0x00 5001 |        | PA_IDR                       | Port A input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5002 | Port A | PA_DDR                       | Port A data direction register    | 0x00                |

| 0x00 5003 |        | PA_CR1                       | Port A control register 1         | 0x00                |

| 0x00 5004 |        | PA_CR2                       | Port A control register 2         | 0x00                |

| 0x00 5005 |        | PB_ODR                       | Port B data output latch register | 0x00                |

| 0x00 5006 |        | PB_IDR                       | Port B input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5007 | Port B | PB_DDR                       | Port B data direction register    | 0x00                |

| 0x00 5008 |        | PB_CR1                       | Port B control register 1         | 0x00                |

| 0x00 5009 |        | PB_CR2                       | Port B control register 2         | 0x00                |

| 0x00 500A |        | PC_ODR                       | Port C data output latch register | 0x00                |

| 0x00 500B |        | PB_IDR                       | Port C input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 500C | Port C | PC_DDR                       | Port C data direction register    | 0x00                |

| 0x00 500D |        | PC_CR1                       | Port C control register 1         | 0x00                |

| 0x00 500E |        | PC_CR2                       | Port C control register 2         | 0x00                |

| 0x00 500F |        | PD_ODR                       | Port D data output latch register | 0x00                |

| 0x00 5010 |        | PD_IDR                       | Port D input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5011 | Port D | PD_DDR                       | Port D data direction register    | 0x00                |

| 0x00 5012 |        | PD_CR1                       | Port D control register 1         | 0x02                |

| 0x00 5013 |        | PD_CR2                       | Port D control register 2         | 0x00                |

| Option byte number | Description <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPT2               | <ul> <li>AFR7: Alternate function remapping option 7</li> <li>0: AFR7 remapping option inactive: default alternate function <sup>(2)</sup></li> <li>1: Port C3 alternate function = TIM1_CH1N; port C4 alternate function remapping option 6</li> <li>Reserved</li> <li>AFR6: Alternate function remapping option 5</li> <li>Reserved</li> <li>AFR4: Alternate function remapping option 4</li> <li>0: AFR4 remapping option inactive: default alternate function <sup>(2)</sup>.</li> <li>1: Port B4 alternate function = ADC_ETR; port B5 alternate function = TIM1_BKIN.</li> <li>AFR3: Alternate function remapping option 3</li> <li>0: AFR3 remapping option inactive: default alternate function <sup>(2)</sup></li> <li>1: Port C3 alternate function = TLI</li> <li>AFR2: Alternate function = TLI</li> <li>AFR2: Alternate function remapping option 2</li> <li>0: AFR2 remapping option inactive: default alternate function <sup>(2)</sup></li> <li>1: Port C3 alternate function = LINUART CK</li> </ul> |

# Table 17. STM8AF6213 and STM8AF6223 alternate function remapping bits [7:2] for 20-pin packages

1. Do not use more than one remapping option in the same port.

2. Refer to the pin description.

### Table 18. STM8AF6223A alternate function remapping bits [7:2] for 20-pin packages

| Option byte number | Description <sup>(1)</sup>                                                                                                                                                                  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | AFR7: Alternate function remapping option 7                                                                                                                                                 |

|                    | 0: AFR7 remapping option inactive: default alternate function <sup>(2)</sup><br>1: Port C4 alternate function = TIM1_CH2N                                                                   |

|                    | AFR6: Alternate function remapping option 6                                                                                                                                                 |

|                    | Reserved                                                                                                                                                                                    |

|                    | AFR5: Alternate function remapping option 5                                                                                                                                                 |

|                    | Reserved                                                                                                                                                                                    |

| OPT2               | AFR4: Alternate function remapping option 4                                                                                                                                                 |

|                    | <ul> <li>0: AFR4 remapping option inactive: default alternate function <sup>(2)</sup>.</li> <li>1: Port B4 alternate function = ADC_ETR; port B5 alternate function = TIM1_BKIN.</li> </ul> |

|                    | AFR3: Alternate function remapping option 3                                                                                                                                                 |

|                    | Reserved.                                                                                                                                                                                   |

|                    | AFR2: Alternate function remapping option 2                                                                                                                                                 |

|                    | 0: AFR2 remapping option inactive: default alternate function <sup>(2)</sup><br>1: Port D4 alternate function = LINUART_CK                                                                  |

1. Do not use more than one remapping option in the same port.

2. Refer to the pin description.

| AFR1 option bit value | AFR0 option bit value | I/O port                              | Alternate function<br>mapping                           |

|-----------------------|-----------------------|---------------------------------------|---------------------------------------------------------|

| 0                     | 0                     | AFR1 and AFR0 rema<br>Default alterna | pping options inactive:<br>ate functions <sup>(1)</sup> |

|                       |                       | PC5                                   | TIM5_CH1                                                |

| 0                     | 1                     | PC6                                   | TIM1_CH1                                                |

|                       |                       | PC7                                   | TIM1_CH2                                                |

| 1                     | 0                     | PA3                                   | SPI_NSS                                                 |

|                       |                       | PD2                                   | TIM5_CH3                                                |

|                       |                       | PD2                                   | TIM5_CH3                                                |

|                       |                       | PC5                                   | TIM5_CH1                                                |

|                       |                       | PC6                                   | TIM1_CH1                                                |

|                       | 1 <sup>(2)</sup>      | PC7                                   | TIM1_CH2                                                |

| 1 <sup>(2)</sup>      |                       | PC2                                   | TIM1_CH3N                                               |

|                       |                       | PC1                                   | TIM1_CH2N                                               |

|                       |                       | PE5                                   | TIM1_CH1N                                               |

|                       |                       | PA3                                   | LINUART_TX                                              |

|                       |                       | PF4                                   | LINUART_RX                                              |

Table 19. STM8AF6226 alternate function remapping bits [1:0] for 32-pin packages

1. Refer to the pin descriptions.

If both AFR1 and AFR0 option bits are set, the SPI hardware NSS management feature is no more available. If this remapping option is selected and the SPI is enabled, the SSM bit must be configured in the SPI\_CR2 register to select software NSS management.

| Table 20. STM8AF6213/STM8AF6223 alternate function remapping bits [1:0] |

|-------------------------------------------------------------------------|

| for 20-pin packages                                                     |

| 101 20-0111 packages  |                       |          |                                                         |  |  |

|-----------------------|-----------------------|----------|---------------------------------------------------------|--|--|

| AFR1 option bit value | AFR0 option bit value | I/O port | Alternate function<br>mapping                           |  |  |

| 0                     | 0                     |          | pping options inactive:<br>ate functions <sup>(1)</sup> |  |  |

|                       | 1                     | PC5      | TIM5_CH1                                                |  |  |

| 0                     |                       | PC6      | TIM1_CH1                                                |  |  |

|                       |                       | PC7      | TIM1_CH2                                                |  |  |

| 1                     | 1 0                   | PA3      | SPI_NSS                                                 |  |  |

| 1                     |                       | PD2      | TIM5_CH3                                                |  |  |

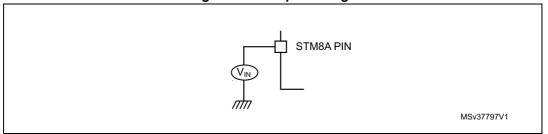

## 9.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 8.

### Figure 8. Pin input voltage

## 9.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 22: Voltage characteristics*, *Table 23: Current characteristics* and *Table 24: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect the device's reliability.

Device mission profile (application conditions) is compliant with JEDEC JESD47 Qualification Standard, extended mission profiles are available on demand.

| Symbol                             | Ratings                                                           |                       | Max                                        | Unit |

|------------------------------------|-------------------------------------------------------------------|-----------------------|--------------------------------------------|------|

| $V_{DDx}$ - $V_{SS}$               | Supply voltage (including $V_{DDA and} V_{DDIO}$ ) <sup>(1)</sup> | -0.3                  | 6.5                                        | V    |

| V                                  | Input voltage on true open drain pins <sup>(2)</sup>              | V <sub>SS</sub> - 0.3 | 6.5                                        | V    |

| V <sub>IN</sub>                    | Input voltage on any other pin <sup>(2)</sup>                     | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> + 0.3                      | v    |

| V <sub>DDx</sub> - V <sub>DD</sub> | V <sub>DD</sub> Variations between different power pins           |                       | 50                                         | mV   |

| V <sub>SSx</sub> - V <sub>SS</sub> | Variations between all the different ground pins                  | -                     | 50                                         | IIIV |

| V <sub>ESD</sub>                   | Electrostatic discharge voltage                                   |                       | ite maximum<br>cal sensitivity)<br>page 89 | _    |

### Table 22. Voltage characteristics

1. All power (V<sub>DD</sub>) and ground (V<sub>SS</sub>) pins must always be connected to the external power supply

2. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected

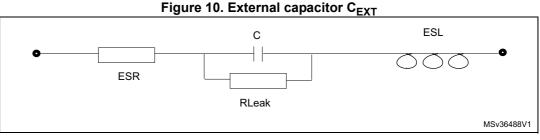

## 9.3.1 VCAP external capacitor

Stabilization for the main regulator is achieved connecting an external capacitor  $C_{EXT}$  to the  $V_{CAP}$  pin.  $C_{EXT}$  is specified in *Table 26*. Care should be taken to limit the series inductance to less than 15 nH.

1. Legend: ESR is the equivalent series resistance and ESL is the equivalent inductance.

## 9.3.2 Supply current characteristics

The current consumption is measured as described in Section 4.3: Interrupt controller.

### Total current consumption in run mode

The MCU is placed under the following conditions:

- All I/O pins in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled (clock stopped by peripheral clock gating registers) except if explicitly mentioned.

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

Unless otherwise specified, data are based on characterization results, and not tested in production.

| Table 28. Total current consumption with code execution in run mode at $V_{DD}$ = 5 V |

|---------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------|

| Symbol                                                      | Parameter                                                  | Conc                                            | litions                | Тур              | Max  | Unit |

|-------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------|------------------------|------------------|------|------|

| Supply current<br>in run mode,<br>code executed<br>from RAM |                                                            | HSE crystal osc. (16 MHz)                       | 2.3                    | -                |      |      |

|                                                             | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz            | HSE user ext. clock (16 MHz)                    | 2                      | 2.35             |      |      |

|                                                             |                                                            | HSI RC osc. (16 MHz)                            | 1.7                    | 2 <sup>(1)</sup> |      |      |

|                                                             | f <sub>CPU</sub> = f <sub>MASTER</sub> /128= 125 kHz       | HSE user ext. clock (16 MHz)                    | 0.86                   | -                | mA   |      |

|                                                             |                                                            | HSI RC osc. (16 MHz)                            | 0.7                    | 0.87             |      |      |

|                                                             | f <sub>CPU</sub> = f <sub>MASTER</sub> /128=<br>15.625 kHz |                                                 | HSI RC osc. (16 MHz/8) | 0.46             | 0.58 |      |

|                                                             |                                                            | f <sub>CPU</sub> = f <sub>MASTER</sub> = 28 kHz | LSI RC osc. (128 kHz)  | 0.41             | 0.55 |      |

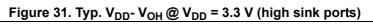

| Symbol          | Parameter                                | Conditions                                       | Min                                            | Мах                | Unit |

|-----------------|------------------------------------------|--------------------------------------------------|------------------------------------------------|--------------------|------|

|                 | Output low level with 8 pins sunk        | I <sub>IO</sub> = 10 mA, V <sub>DD</sub> = 5 V   | -                                              | 0.8                |      |

| V <sub>OL</sub> | Output low level with 4 pins sunk        | I <sub>IO</sub> = 10 mA, V <sub>DD</sub> = 3.3 V | -                                              | 1.0 <sup>(1)</sup> |      |

|                 |                                          | I <sub>IO</sub> = 20 mA, V <sub>DD</sub> = 5 V   |                                                | 1.5 <sup>(1)</sup> | V    |

|                 | Output high level with<br>8 pins sourced | I <sub>IO</sub> = 10 mA, V <sub>DD</sub> = 5 V   | 4.0                                            | -                  | v    |

| V <sub>OH</sub> | Output high level with                   | I <sub>IO</sub> = 10 mA, V <sub>DD</sub> = 3.3 V | 2.1 <sup>(1)</sup>                             | -                  |      |

|                 |                                          | 4 pins sourced                                   | I <sub>IO</sub> = 20 mA, V <sub>DD</sub> = 5 V | 3.3 <sup>(1)</sup> | -    |

| Table 50 | . Output | driving | current | (high | sink po | rts) |

|----------|----------|---------|---------|-------|---------|------|

|----------|----------|---------|---------|-------|---------|------|

1. Guaranteed by characterization results.

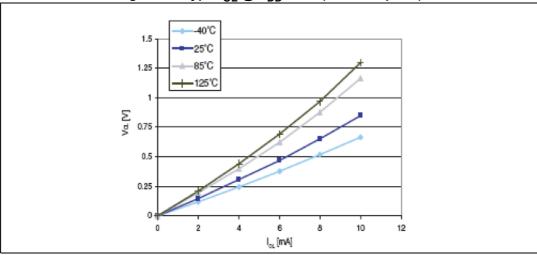

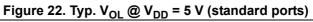

## Figure 23. Typ. V<sub>OL</sub> @ V<sub>DD</sub> = 3.3 V (standard ports)

DocID025118 Rev 6

Figure 30. Typ.  $V_{DD}$ -  $V_{OH} @ V_{DD}$  = 5 V (high sink ports)

# 9.3.9 I<sup>2</sup>C interface characteristics

| Symbol                                     | Parameter                                            | Standard mode I <sup>2</sup> C |                    | Fast mode I <sup>2</sup> C <sup>(1)</sup> |                    | Unit |

|--------------------------------------------|------------------------------------------------------|--------------------------------|--------------------|-------------------------------------------|--------------------|------|

| Symbol                                     |                                                      | Min <sup>(2)</sup>             | Max <sup>(2)</sup> | Min <sup>(2)</sup>                        | Max <sup>(2)</sup> | Unit |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                                   | 4.7                            | -                  | 1.3                                       | -                  | 110  |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                                  | 4.0                            | -                  | 0.6                                       | -                  | μs   |

| t <sub>su(SDA)</sub>                       | SDA setup time                                       | 250                            | -                  | 100                                       | -                  |      |

| t <sub>h(SDA)</sub>                        | SDA data hold time                                   | 0 <sup>(3)</sup>               | 3450               | 0 <sup>(4)</sup>                          | 900 <sup>(3)</sup> |      |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                                | -                              | 1000               | -                                         | 300                | ns   |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                                | -                              | 300                | -                                         | 300                |      |

| t <sub>h(STA)</sub>                        | START condition hold time                            | 4.0                            | -                  | 0.6                                       | -                  |      |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time                  | 4.7                            | -                  | 0.6                                       | -                  |      |

| t <sub>su(STO)</sub>                       | STOP condition setup time                            | 4.0                            | -                  | 0.6                                       | -                  | μs   |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free)              | 4.7                            | -                  | 1.3                                       | -                  |      |

| t <sub>SP</sub>                            | Pulse width of spikes suppressed by the input filter | 0                              | 50 <sup>(5)</sup>  | 0                                         | 50                 | ns   |

| Cb                                         | Capacitive load for each bus line                    | -                              | 400                | -                                         | 400                | pF   |

## Table 53. I<sup>2</sup>C characteristics

1.  $f_{MASTER}$ , must be at least 8 MHz to achieve max fast I<sup>2</sup>C speed (400 kHz)

2. Data based on standard I<sup>2</sup>C protocol requirement, not tested in production

3. The maximum hold time of the start condition has only to be met if the interface does not stretch the low time

4. The device must internally provide a hold time of at least 300 ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL

5. The minimum width of the spikes filtered by the analog filter is above  $t_{SP(max)}$

| Symbol         | Parameter                                   | Conditions               | Тур | Max <sup>(1)</sup> | Unit |

|----------------|---------------------------------------------|--------------------------|-----|--------------------|------|

|                |                                             | f <sub>ADC</sub> = 2 MHz | 1.6 | 3.5                |      |

| E <sub>T</sub> | Total unadjusted error <sup>(2)</sup>       | f <sub>ADC</sub> = 4 MHz | 2.2 | 4                  |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz | 2.4 | 4.5                |      |

|                |                                             | f <sub>ADC</sub> = 2 MHz | 1.1 | 2.5                |      |

| E <sub>O</sub> | Offset error <sup>(2)</sup>                 | f <sub>ADC</sub> = 4 MHz | 1.5 | 3                  |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz | 1.8 | 3                  |      |

|                | Gain error <sup>(2)</sup>                   | f <sub>ADC</sub> = 2 MHz | 1.5 | 3                  |      |

| E <sub>G</sub> |                                             | f <sub>ADC</sub> = 4 MHz | 2.1 | 3                  | LSB  |

|                |                                             | f <sub>ADC</sub> = 6 MHz | 2.2 | 4                  |      |

|                |                                             | f <sub>ADC</sub> = 2 MHz | 0.7 | 1.5                |      |

| E <sub>D</sub> | Differential linearity error <sup>(2)</sup> | f <sub>ADC</sub> = 4 MHz | 0.7 | 1.5                |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz | 0.7 | 1.5                |      |

| E <sub>L</sub> |                                             | f <sub>ADC</sub> = 2 MHz | 0.6 | 1.5                |      |

|                | Integral linearity error <sup>(2)</sup>     | f <sub>ADC</sub> = 4 MHz | 0.8 | 2                  |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz | 0.8 | 2                  |      |

Table 55. ADC accuracy with RAIN < 10 k $\Omega$ , V<sub>DD</sub> = 5 V

1. Max value is based on characterization, not tested in production.

2. ADC accuracy vs. negative injection current: Injecting negative current on any of the analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current. Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in the I/O port pin characteristics section does not affect the ADC accuracy.

| Table 50. ADC accuracy with KAIN $< 10 \text{ k}_{22}, \text{ v}_{DD} = 5.3 \text{ v}_{DD}$ |                               |                          |     |                    |      |  |

|---------------------------------------------------------------------------------------------|-------------------------------|--------------------------|-----|--------------------|------|--|

| Symbol                                                                                      | Parameter                     | Conditions               | Тур | Max <sup>(1)</sup> | Unit |  |

|                                                                                             | Total upadjusted error        | f <sub>ADC</sub> = 2 MHz | 1.6 | 3.5                |      |  |

| E <sub>T</sub>                                                                              | Total unadjusted error        | f <sub>ADC</sub> = 4 MHz | 1.9 | 4                  |      |  |

|                                                                                             | E <sub>O</sub>   Offset error | f <sub>ADC</sub> = 2 MHz | 1   | 2.5                |      |  |

| ⊏o                                                                                          |                               | f <sub>ADC</sub> = 4 MHz | 1.5 | 2.5                |      |  |

|                                                                                             | E <sub>G</sub> Gain error     | f <sub>ADC</sub> = 2 MHz | 1.3 | 3                  | LSB  |  |

| E <sub>G</sub>                                                                              |                               | f <sub>ADC</sub> = 4 MHz | 2   | 3                  | LOD  |  |

|                                                                                             |                               | f <sub>ADC</sub> = 2 MHz | 0.7 | 1                  |      |  |

| E <sub>D</sub>   Differential li                                                            | Differential linearity error  | f <sub>ADC</sub> = 4 MHz | 0.7 | 1.5                |      |  |

|                                                                                             | Integral linearity error      | f <sub>ADC</sub> = 2 MHz | 0.6 | 1.5                |      |  |

| E <sub>L</sub>                                                                              | Integral linearity error      | f <sub>ADC</sub> = 4 MHz | 0.8 | 2                  |      |  |

Table 56. ADC accuracy with RAIN < 10 k $\Omega$ , V<sub>DD</sub> = 3.3 V

1. Max value is based on characterization, not tested in production.

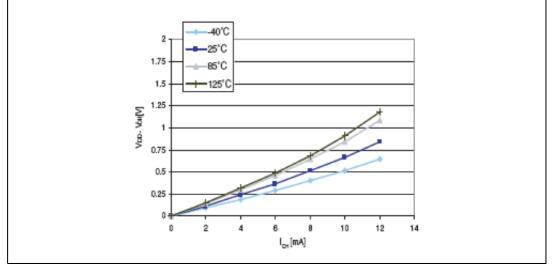

# **10** Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

## 10.1 LQFP32 package information

Figure 42. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

DocID025118 Rev 6

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax}$ = 75 °C (measured according to JESD51-2), I<sub>DDmax</sub> = 8 mA, V<sub>DD</sub> = 5 V Maximum 20 I/Os used at the same time in output at low level with:

Maximum 20 I/Os used at the same time in output at low level with:

I<sub>OL</sub> = 8 mA, V<sub>OL</sub>= 0.4 V

P<sub>INTmax</sub> = 8 mA x 5 V= 400 mW

$P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{ V} = 64 \text{ mW}$

This gives: P<sub>INTmax</sub> = 400 mW and P<sub>IOmax</sub> 64 mW:

P<sub>Dmax</sub> = 400 mW + 64 mW

Thus: P<sub>Dmax</sub> = 464 mW.

Using the values obtained in Table 64: Thermal characteristics on page 101  $T_{Jmax}$  is calculated as follows:

For LQFP32 60 °C/W

T<sub>Jmax</sub> = 75 °C + (60 °C/W x464 mW) = 75 °C + 27.8 °C = 102.8 °C

This is within the range of the suffix C version parts (-40 <  $T_J$  < 125 °C).

Parts must be ordered at least with the temperature range suffix C.

### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics – All rights reserved

DocID025118 Rev 6