Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                    |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | STM8A                                                                  |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                     |

| Program Memory Size        | 16KB (16K × 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 512 x 8                                                                |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | A/D 7x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-LQFP                                                                |

| Supplier Device Package    | 32-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8af6246itcx |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 47. | I/O static characteristics                                                |

|-----------|---------------------------------------------------------------------------|

| Table 48. | Output driving current (standard ports)                                   |

| Table 49. | Output driving current (true open drain ports)                            |

| Table 50. | Output driving current (high sink ports)                                  |

| Table 51. | NRST pin characteristics                                                  |

| Table 52. | SPI characteristics                                                       |

| Table 53. | I <sup>2</sup> C characteristics                                          |

| Table 54. | ADC characteristics                                                       |

| Table 55. | ADC accuracy with RAIN < 10 k $\Omega$ , V <sub>DD</sub> = 5 V            |

| Table 56. | ADC accuracy with RAIN < 10 k $\Omega$ , V <sub>DD</sub> = 3.3 V          |

| Table 57. | EMS data                                                                  |

| Table 58. | EMI data                                                                  |

| Table 59. | ESD absolute maximum ratings                                              |

| Table 60. | Electrical sensitivities                                                  |

| Table 61. | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package                   |

|           | mechanical data                                                           |

| Table 62. | TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, |

|           | package mechanical data                                                   |

| Table 63. | VFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch very thin profile fine pitch      |

|           | quad flat package mechanical data                                         |

| Table 64. | Thermal characteristics                                                   |

| Table 65. | STM8AF6213/23/23A/26 ordering information scheme                          |

| Table 66. | Document revision history                                                 |

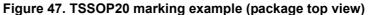

| Figure 47   | package footprint                                                    |     |

|-------------|----------------------------------------------------------------------|-----|

| •           | VFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch very thin profile fine pitch |     |

| i iguro ro. | quad flat package outline                                            | 97  |

| Figure 49.  | VFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch very thin profile fine pitch |     |

| -           | quad flat package recommended footprint                              | 99  |

| Figure 50.  | VFQFPN32 marking example (package top view)                          | 100 |

# 1 Introduction

The datasheet contains the description of STM8AF6213, STM8AF6223, STM8AF6223A and STM8AF6226 features, pinout, electrical characteristics, mechanical data and ordering information.

- For complete information on the STM8A microcontroller memory, registers and peripherals, please refer to STM8S series and STM8AF series 8-bit microcontrollers reference manual (RM0016).

- For information on programming, erasing and protection of the internal Flash memory please refer to the STM8 Flash programming manual (PM0051).

- For information on the debug and SWIM (single wire interface module) refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).

- For information on the STM8 core, please refer to the STM8 CPU programming manual (PM0044).

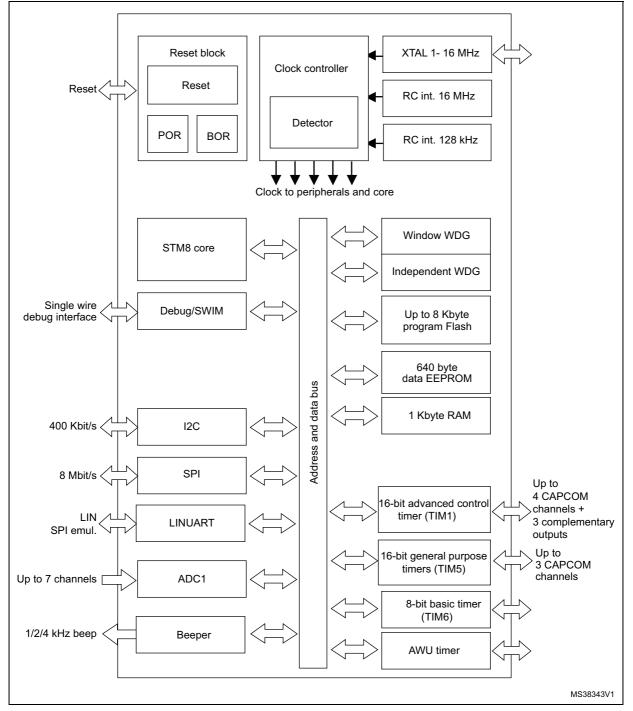

# 3 Block diagram

Legend: ADC (Analog-to-digital converter), beCAN (Controller area network), BOR (Brownout reset), I<sup>2</sup>C (Inter-integrated circuit multimaster interface),IWDG (Independent window watchdog), LINUART (Local interconnect network universal asynchronous receiver transmitter), POR (Power on reset), SPI (Serial peripheral interface), SWIM (Single wire interface module), USART (Universal synchronous asynchronous receiver transmitter), Window WDG (Window watchdog).

DocID025118 Rev 6

### Independent watchdog timer

The independent watchdog peripheral can be used to resolve processor malfunctions due to hardware or software failures.

It is clocked by the 128 kHz LSI internal RC clock source, and thus stays active even in case of a CPU clock failure.

The IWDG time base spans from 60 µs to 1 s

# 4.8 Auto wakeup counter

- Used for auto wakeup from active halt mode

- Clock source: Internal 128 kHz internal low frequency RC oscillator or external clock

- LSI clock can be internally connected to TIM1 input capture channel 1 for calibration

# 4.9 Beeper

The beeper function outputs a signal on the BEEP pin for sound generation. The signal is in the range of 1, 2 or 4 kHz.

The beeper output port is only available through the alternate function remap option bit AFR7.

# 4.10 TIM1 - 16-bit advanced control timer

This is a high-end timer designed for a wide range of control applications. With its complementary outputs, dead-time control and center-aligned PWM capability, the field of applications is extended to motor control, lighting and half-bridge driver.

- 16-bit up, down and up/down auto-reload counter with 16-bit fractional prescaler.

- Four independent capture/compare channels (CAPCOM) configurable as input capture, output compare, PWM generation (edge and center aligned mode) and single pulse mode output.

- Synchronization module to control the timer with external signals or to synchronise with TIM5 or TIM6

- Break input to force the timer outputs into a defined state

- Three complementary outputs with adjustable dead time

- Encoder mode

- Interrupt sources: 3 x input capture/output compare, 1 x overflow/update, 1 x break

# 4.14.1 LINUART

## Main features

- 1 Mbit/s full duplex SCI

- SPI emulation

- High precision baud rate generator

- Smartcard emulation

- IrDA SIR encoder decoder

- LIN mode

- Single wire half duplex mode

## LIN mode

## Master mode:

- LIN break and delimiter generation

- LIN break and delimiter detection with separate flag and interrupt source for read back checking.

## Slave mode:

- Autonomous header handling one single interrupt per valid header

- Mute mode to filter responses

- Identifier parity error checking

- LIN automatic resynchronization, allowing operation with internal RC oscillator (HSI) clock source

- Break detection at any time, even during a byte reception

- Header errors detection:

- Delimiter too short

- Synch field error

- Deviation error (if automatic resynchronization is enabled)

- Framing error in synch field or identifier field

- Header time-out

|       |                                    |      |          | Input | t              |                          | Out   | put |    |                                   |                                                                            |                                                                  |

|-------|------------------------------------|------|----------|-------|----------------|--------------------------|-------|-----|----|-----------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------|

| TSSOP | Pin name                           | Туре | floating | ndw   | Ext. interrupt | High sink <sup>(1)</sup> | Speed | QO  | РР | Main<br>function<br>(after reset) | Default<br>alternate<br>function                                           | Alternate<br>function<br>after remap<br>[option bit]             |

| 19    | PD2/AIN3<br>[TIM5_CH3]             | I/O  | X        | x     | x              | HS                       | O3    | x   | x  | Port D2                           | -                                                                          | Analog<br>input 3<br>[AFR2]<br>Timer 52 -<br>channel 3<br>[AFR1] |

| 20    | PD3/ AIN4/<br>TIM5_CH2/<br>ADC_ETR | I/O  | X        | x     | x              | HS                       | O3    | x   | x  | Port D3                           | Analog<br>input 4<br>Timer 52 -<br>channel<br>2/ADC<br>external<br>trigger | -                                                                |

### Table 6. STM8AF6213/STM8AF6223 TSSOP20 pin description (continued)

1. I/O pins used simultaneously for high current source/sink must be uniformly spaced around the package. In addition, the total driven current must respect the absolute maximum ratings (see *Section 9.2: Absolute maximum ratings*).

2. When the MCU is in Halt/Active-halt mode, PA1 is automatically configured in input weak pull-up and cannot be used for waking up the device. In this mode, the output state of PA1 is not driven. It is recommended to use PA1 only in input mode if Halt/Active-halt is used in the application.

3. In the open-drain output column, 'T' defines a true open-drain I/O (P-buffer, weak pull-up, and protection diode to VDD are not implemented)

4. The PD1 pin is in input pull-up during the reset phase and after internal reset release.

|       |                                                |      |          | Input | Input          |                          | Output |    |    |                                   |                                                   |                                                      |

|-------|------------------------------------------------|------|----------|-------|----------------|--------------------------|--------|----|----|-----------------------------------|---------------------------------------------------|------------------------------------------------------|

| TSSOP | Pin name                                       | Туре | floating | ndm   | Ext. interrupt | High sink <sup>(1)</sup> | Speed  | OD | РР | Main<br>function<br>(after reset) | Default<br>alternate<br>function                  | Alternate<br>function<br>after remap<br>[option bit] |

| 1     | PD4/ TIM5_CH1/<br>BEEP/SPI_NSS<br>[LINUART_CK] | I/O  | x        | x     | x              | HS                       | O3     | x  | х  | Port D4                           | Timer 5 -<br>channel<br>1/BEEP<br>output          | LINUART<br>clock<br>[AFR2]                           |

| 2     | PD5/ AIN5/<br>LINUART_TX                       | I/O  | x        | х     | х              | HS                       | O3     | х  | x  | Port D5                           | Analog<br>input 5/<br>LINUART<br>data<br>transmit | -                                                    |

### Table 7. STM8AF6223A TSSOP20 pin description

| Address                   | Block                   | Register label | Register name                | Reset<br>status |  |

|---------------------------|-------------------------|----------------|------------------------------|-----------------|--|

| 0x00 5230                 |                         | UART4_SR       | LINUART status register      | 0xC0            |  |

| 0x00 5231                 |                         | UART4_DR       | LINUART data register        | 0xXX            |  |

| 0x00 5232                 |                         | UART4_BRR1     | LINUART baud rate register 1 | 0x00            |  |

| 0x00 5233                 |                         | UART4_BRR2     | LINUART baud rate register 2 | 0x00            |  |

| 0x00 5234                 |                         | UART4_CR1      | LINUART control register 1   | 0x00            |  |

| 0x00 5235                 |                         | UART4_CR2      | LINUART control register 2   | 0x00            |  |

| 0x00 5236                 | LINUART                 | UART4_CR3      | LINUART control register 3   | 0x00            |  |

| 0x00 5237                 |                         | UART4_CR4      | LINUART control register 4   | 0x00            |  |

| 0x00 5238                 |                         |                | Reserved                     |                 |  |

| 0x00 5239                 |                         | UART4_CR6      | LINUART control register 6   | 0x00            |  |

| 0x00 523A                 |                         | UART4_GTR      | LINUART guard time register  | 0x00            |  |

| 0x00 523B                 |                         | UART4_PSCR     | LINUART prescaler            | 0x00            |  |

| 0x00 523C to<br>0x00 523F | Reserved area (20 byte) |                |                              |                 |  |

| Table 11. Gener | al hardware red    | nister map | (continued) |

|-----------------|--------------------|------------|-------------|

|                 | ur mur a mur e reg | giotor mup | (continueu) |

| Table 11. General hardware register map (continued) |       |                |                                        |                 |  |  |

|-----------------------------------------------------|-------|----------------|----------------------------------------|-----------------|--|--|

| Address                                             | Block | Register label | Register name                          | Reset<br>status |  |  |

| 0x00 5300                                           |       | TIM5_CR1       | TIM5 control register 1                | 0x00            |  |  |

| 0x00 5301                                           |       | TIM5_CR2       | TIM5 control register 2                | 0x00            |  |  |

| 0x00 5302                                           |       | TIM5_SMCR      | TIM5 slave mode control register       | 0x00            |  |  |

| 0x00 5303                                           |       | TIM5_IER       | TIM5 interrupt enable register         | 0x00            |  |  |

| 0x00 5304                                           |       | TIM5_SR1       | TIM5 status register 1                 | 0x00            |  |  |

| 0x00 5305                                           |       | TIM5_SR2       | TIM5 status register 2                 | 0x00            |  |  |

| 0x00 5306                                           |       | TIM5_EGR       | TIM5 event generation register         | 0x00            |  |  |

| 0x00 5307                                           |       | TIM5_CCMR1     | TIM5 capture/compare mode register 1   | 0x00            |  |  |

| 0x00 5308                                           |       | TIM5_CCMR2     | TIM5 capture/compare mode register 2   | 0x00            |  |  |

| 0x00 5309                                           |       | TIM5_CCMR3     | TIM5 capture/compare mode register 3   | 0x00            |  |  |

| 0x00 530A                                           |       | TIM5_CCER1     | TIM5 capture/compare enable register 1 | 0x00            |  |  |

| 0x00 530B                                           | TIM5  | TIM5_CCER2     | TIM5 capture/compare enable register 2 | 0x00            |  |  |

| 00 530C0x                                           |       | TIM5_CNTRH     | TIM5 counter high                      | 0x00            |  |  |

| 0x00 530D                                           |       | TIM5_CNTRL     | TIM5 counter low                       | 0x00            |  |  |

| 0x00 530E                                           |       | TIM5_PSCR      | TIM5 prescaler register                | 0x00            |  |  |

| 0x00 530F                                           |       | TIM5_ARRH      | TIM5 auto-reload register high         | 0xFF            |  |  |

| 0x00 5310                                           |       | TIM5_ARRL      | TIM5 auto-reload register low          | 0xFF            |  |  |

| 0x00 5311                                           |       | TIM5_CCR1H     | TIM5 capture/compare register 1 high   | 0x00            |  |  |

| 0x00 5312                                           |       | TIM5_CCR1L     | TIM5 capture/compare register 1 low    | 0x00            |  |  |

| 0x00 5313                                           |       | TIM5_CCR2H     | TIM5 capture/compare reg. 2 high       | 0x00            |  |  |

| 0x00 5314                                           |       | TIM5_CCR2L     | TIM5 capture/compare register 2 low    | 0x00            |  |  |

| 0x00 5315                                           |       | TIM5_CCR3H     | TIM5 capture/compare register 3 high   | 0x00            |  |  |

| 0x00 5316                                           |       | TIM5_CCR3L     | TIM5 capture/compare register 3 low    | 0x00            |  |  |

| 0x00 5317 to<br>0x00 533F                           |       | R              | eserved area (43 byte)                 |                 |  |  |

| 0x00 5340                                           |       | TIM6_CR1       | TIM6 control register 1                | 0x00            |  |  |

| 0x00 5341                                           |       | TIM6_CR2       | TIM6 control register 2                | 0x00            |  |  |

| 0x00 5342                                           |       | TIM6_SMCR      | TIM6 slave mode control register       | 0x00            |  |  |

| 0x00 5343                                           |       | TIM6_IER       | TIM6 interrupt enable register         | 0x00            |  |  |

| 0x00 5344                                           | TIM6  | TIM6_SR        | TIM6 status register                   | 0x00            |  |  |

| 0x00 5345                                           |       | TIM6_EGR       | TIM6 event generation register         | 0x00            |  |  |

| 0x00 5346                                           |       | TIM6_CNTR      | TIM6 counter                           | 0x00            |  |  |

| 0x00 5347                                           |       | TIM6_PSCR      | TIM6 prescaler register                | 0x00            |  |  |

| 0x00 5348                                           |       | TIM6 ARR       | TIM6 auto-reload register              | 0xFF            |  |  |

| Option byte no. | Description                                                                                                                                           |  |  |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| OPT4            | EXTCLK: External clock selection<br>0: External crystal connected to OSCIN/OSCOUT<br>1: External clock signal on OSCIN                                |  |  |  |  |  |  |

|                 | CKAWUSEL: Auto-wakeup unit/clock<br>0: LSI clock source selected for AWU<br>1: HSE clock with prescaler selected as clock source for AWU              |  |  |  |  |  |  |

|                 | PRSC[1:0]: AWU clock prescaler<br>0x: 16 MHz to 128 kHz prescaler<br>10: 8 MHz to 128 kHz prescaler<br>11: 4 MHz to 128 kHz prescaler                 |  |  |  |  |  |  |

| OPT5            | HSECNT[7:0]: HSE crystal oscillator stabilization time<br>0x00: 2048 HSE cycles<br>0xB4: 128 HSE cycles<br>0xD2: 8 HSE cycles<br>0xE1: 0.5 HSE cycles |  |  |  |  |  |  |

### Table 15. Option byte description (continued)

# 8.2 STM8AF6213/23/23A/26 alternate function remapping bits

| Option byte number | Description <sup>(1)</sup>                                                                                                                                                                                            |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | AFR7: Alternate function remapping option 7<br>0: AFR7 remapping option inactive: default alternate function <sup>(2)</sup><br>1: Port C3 alternate function = = TIM1_CH1N;<br>port C4 alternate function = TIM1_CH2N |

|                    | AFR6: Alternate function remapping option 6                                                                                                                                                                           |

|                    | 0: AFR6 remapping option inactive: default alternate function <sup>(2)</sup><br>1: Port D7 alternate function = TIM1_CH4.                                                                                             |

|                    | AFR5: Alternate function remapping option 5                                                                                                                                                                           |

|                    | 0: AFR5 remapping option inactive: default alternate function <sup>(2)</sup> .<br>1: Port D0 alternate function = CLK_CCO.                                                                                            |

| OPT2               | AFR4: Alternate function remapping option 4                                                                                                                                                                           |

|                    | 0: AFR4 remapping option inactive: default alternate function <sup>(2)</sup> .<br>1: Port B4 alternate function = ADC_ETR; port B5 alternate function = TIM1_BKIN.                                                    |

|                    | AFR3: Alternate function remapping option 3                                                                                                                                                                           |

|                    | 0: AFR3 remapping option inactive: default alternate function <sup>(2)</sup><br>1: Port C3 alternate function = TLI                                                                                                   |

|                    | AFR2: Alternate function remapping option 2                                                                                                                                                                           |

|                    | 0: AFR2 remapping option inactive: default alternate function <sup>(2)</sup><br>1: Port C4 alternate function = AIN2; port D2 alternate function = AIN3;<br>port D4 alternate function = LINUART_CK                   |

1. Do not use more than one remapping option in the same port.

2. Refer to the pin description.

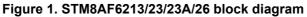

Figure 9.  $f_{CPUmax}$  versus  $V_{DD}$

| Symbol                | Parameter                                     | Conditions             | Min                | Тур               | Max                | Unit |

|-----------------------|-----------------------------------------------|------------------------|--------------------|-------------------|--------------------|------|

| t <sub>VDD</sub>      | V <sub>DD</sub> rise time rate                | -                      | 2 <sup>(1)</sup>   | -                 | ∞                  | μs/V |

|                       | V <sub>DD</sub> fall time rate <sup>(2)</sup> | -                      | 2 <sup>(1)</sup>   | -                 | 8                  |      |

| t <sub>TEMP</sub>     | Reset release delay                           | V <sub>DD</sub> rising | -                  | -                 | 1.7                | ms   |

| V <sub>IT+</sub>      | Power-on reset<br>threshold <sup>(3)</sup>    | -                      | 2.6 <sup>(1)</sup> | 2.7               | 2.85               | V    |

| V <sub>IT-</sub>      | Brown-out reset<br>threshold                  | -                      | 2.5                | 2.65              | 2.8 <sup>(1)</sup> | v    |

| V <sub>HYS(BOR)</sub> | Brown-out reset<br>hysteresis                 | -                      | -                  | 70 <sup>(1)</sup> | -                  | mV   |

1. Guaranteed by design.

2. Reset is always generated after a  $t_{\mbox{TEMP}}$  delay. The application must ensure that  $V_{\mbox{DD}}$  is still above the minimum operating voltage (V\_{\mbox{DD}} min) when the  $t_{\mbox{TEMP}}$  delay has elapsed.

3. There is inrush current into V<sub>DD</sub> present after device power on to charge C<sub>EXT</sub> capacitor. This inrush energy depends from C<sub>EXT</sub> capacitor value. For example, a C<sub>EXT</sub> of 1µF requires Q=1 µF x 1.8V = 1.8 µC.

## Total current consumption and timing in forced reset state

| Symbol               | Parameter                                    | Conditions              | Тур | Max <sup>(1)</sup> | Unit |

|----------------------|----------------------------------------------|-------------------------|-----|--------------------|------|

| I <sub>DD(R)</sub>   | Supply current in reset state <sup>(2)</sup> | V <sub>DD</sub> = 5 V   | 400 | -                  | μA   |

|                      |                                              | V <sub>DD</sub> = 3.3 V | 300 | -                  |      |

| t <sub>RESETBL</sub> | Reset pin release to vector<br>fetch         | -                       | _   | 150                | μs   |

| Table 37. Total current consumption and timing in forced res | et state |

|--------------------------------------------------------------|----------|

|--------------------------------------------------------------|----------|

1. Guaranteed by design.

2. Characterized with all I/Os tied to  $V_{SS}$ .

## Current consumption for on-chip peripherals

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

HSI internal RC/f<sub>CPU</sub> =  $f_{MASTER}$  = 16 MHz,  $V_{DD}$  = 5 V

### Table 38. Peripheral current consumption

| Symbol                 | Parameter                             | Тур  | Unit |

|------------------------|---------------------------------------|------|------|

| I <sub>DD(TIM1)</sub>  | TIM1 supply current <sup>(1)</sup>    | 210  |      |

| I <sub>DD(TIM5)</sub>  | TIM5 supply current <sup>(1)</sup>    | 130  |      |

| I <sub>DD(TIM6)</sub>  | TIM6 supply current <sup>(1)</sup>    | 50   |      |

| I <sub>DD(UART1)</sub> | LINUART supply current <sup>(2)</sup> | 120  | μA   |

| I <sub>DD(SPI)</sub>   | SPI supply current <sup>(2)</sup>     | 45   |      |

| I <sub>DD(I2C)</sub>   | I2C supply current <sup>(2)</sup>     | 65   |      |

| I <sub>DD(ADC1)</sub>  | ADC1 supply current <sup>(3)</sup>    | 1000 | ſ    |

Data based on a differential I<sub>DD</sub> measurement between reset configuration and timer counter running at 16 MHz. No IC/OC programmed (no I/O pads toggling). Not tested in production.

Data based on a differential I<sub>DD</sub> measurement between the on-chip peripheral when kept under reset and not clocked and the on-chip peripheral when clocked and not kept under reset. No I/O pads toggling. Not tested in production.

Data based on a differential I<sub>DD</sub> measurement between reset configuration and continuous A/D conversions. Not tested in production.

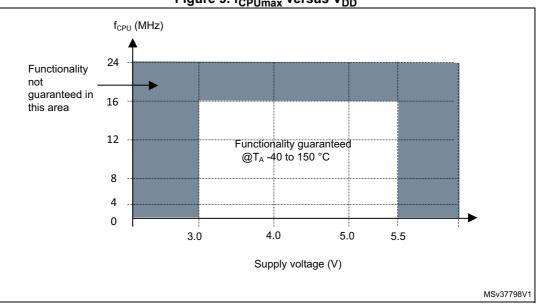

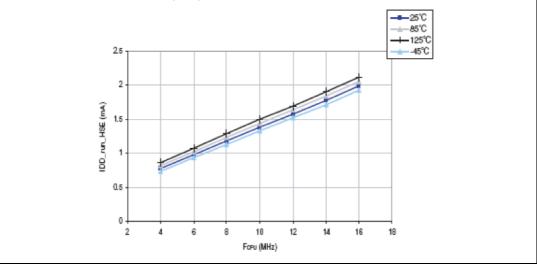

## **Current consumption curves**

The following figures show typical current consumption measured with code executing in RAM.

Figure 11. Typ I<sub>DD(RUN)</sub> vs. V<sub>DD</sub> HSE user external clock, f<sub>CPU</sub> = 16 MHz

Figure 12. Typ  $I_{DD(RUN)}$  vs.  $f_{CPU}$  HSE user external clock,  $V_{DD}$  = 5 V

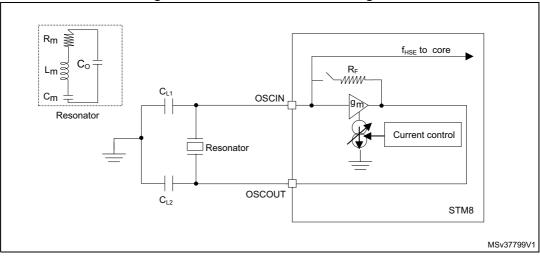

## HSE crystal/ceramic resonator oscillator

The HSE clock can be supplied with a 1 to 16 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol                              | Parameter                                   | Conditions                              | Min | Тур | Мах                                            | Unit |

|-------------------------------------|---------------------------------------------|-----------------------------------------|-----|-----|------------------------------------------------|------|

| f <sub>HSE</sub>                    | External high-speed oscillator<br>frequency | -                                       | 1   | -   | 16                                             | MHz  |

| R <sub>F</sub>                      | Feedback resistor                           | -                                       | -   | 220 | -                                              | kΩ   |

| C <sup>(1)</sup>                    | Recommended load capacitance <sup>(2)</sup> | -                                       | -   | -   | 20                                             | pF   |

| I <sub>DD(HSE)</sub>                | HSE oscillator power consumption            | C = 20 pF,<br>f <sub>OSC</sub> = 16 MHz | -   | -   | 6 (startup)<br>1.6 (stabilized) <sup>(3)</sup> | mA   |

|                                     |                                             | C = 10 pF,<br>f <sub>OSC</sub> = 16 MHz | -   | -   | 6 (startup)<br>1.2 (stabilized) <sup>(3)</sup> | IIIA |

| 9 <sub>m</sub>                      | Oscillator transconductance                 | -                                       | 5   | -   | -                                              | mA/V |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                                | V <sub>DD</sub> is<br>stabilized        | -   | 1   | -                                              | ms   |

1. C is approximately equivalent to 2 x crystal C<sub>LOAD</sub>.

2. The oscillator selection can be optimized in terms of supply current using a high quality resonator with small Rm value. Refer to the crystal manufacturer for more details.

3. Guaranteed by characterization results.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) until a stabilized 16 MHz oscillation is reached. The value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

### Figure 18. HSE oscillator circuit diagram

57

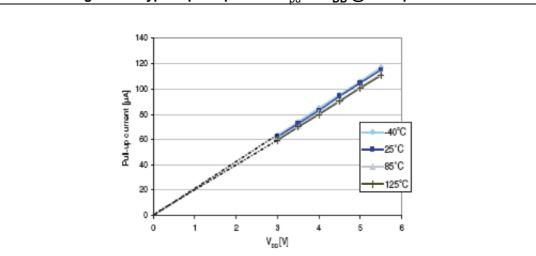

Figure 21. Typical pull-up current  $I_{\text{pu}}$  vs  $V_{\text{DD}}$  @ 4 temperatures

| Symbol          | Parameter                             | Conditions                                         | Min                | Мах                | Unit |  |

|-----------------|---------------------------------------|----------------------------------------------------|--------------------|--------------------|------|--|

| V <sub>OL</sub> | Output low level with 8 pins sunk     | I <sub>IO</sub> = 10 mA,<br>V <sub>DD</sub> = 5 V  | -                  | 2.0                |      |  |

|                 | Output low level with 4 pins sunk     | I <sub>IO</sub> = 4 mA,<br>V <sub>DD</sub> = 3.3 V | -                  | 1.0 <sup>(1)</sup> | V    |  |

| N.              | Output high level with 8 pins sourced | I <sub>IO</sub> = 10 mA,<br>V <sub>DD</sub> = 5 V  | 2.8                | -                  | v    |  |

| V <sub>OH</sub> | Output high level with 4 pins sourced | I <sub>IO</sub> = 4 mA,<br>V <sub>DD</sub> = 3.3 V | 2.1 <sup>(1)</sup> | -                  |      |  |

1. Guaranteed by characterization results.

| Table 49. Output driving | a current ( | (true oi | pen drain p | orts) |

|--------------------------|-------------|----------|-------------|-------|

|                          |             |          |             |       |

| Symbol          | Parameter                         | Conditions                                       | Мах                | Unit |

|-----------------|-----------------------------------|--------------------------------------------------|--------------------|------|

|                 |                                   | I <sub>IO</sub> = 10 mA, V <sub>DD</sub> = 5 V   | 1.0                |      |

| V <sub>OL</sub> | Output low level with 2 pins sunk | I <sub>IO</sub> = 10 mA, V <sub>DD</sub> = 3.3 V | 1.5 <sup>(1)</sup> | V    |

|                 |                                   | $I_{\rm IO}$ = 20 mA, $V_{\rm DD}$ = 5 V         | 2.0 <sup>(1)</sup> |      |

1. Guaranteed by characterization results.

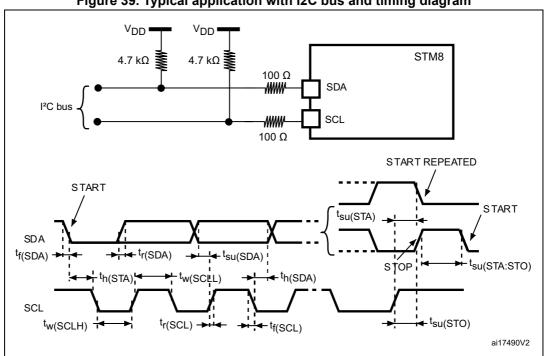

Figure 39. Typical application with I2C bus and timing diagram

1. Measurement points are made at CMOS levels: 0.3 x  $V_{\text{DD}}$  and 0.7 x  $V_{\text{DD}}.$

# 9.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

## Functional EMS (electromagnetic susceptibility)

While executing a simple application (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- **FESD**: Functional electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be recovered by applying a low state on the NRST pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see the application note reference AN1015).

| Symbol            | Parameter Conditions                                                                                                              |                                                                                                                                                                                                                           | Level/class        |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $\label{eq:VDD} \begin{array}{l} V_{DD} = 3.3 \text{ V},  \text{T}_{\text{A}} = 25 \ ^{\circ}\text{C}, \\ \text{f}_{\text{MASTER}} = 16 \text{ MHz} \text{ (HSI clock)}, \\ \text{Conforms to IEC 61000-4-2} \end{array}$ | 2/B <sup>(1)</sup> |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, $T_A$ = 25 °C,<br>$f_{MASTER}$ = 16 MHz (HSI clock),<br>Conforms to IEC 61000-4-4                                                                                                                       | 4/A                |

### Table 57. EMS data

Data obtained with HSI clock configuration, after applying hardware recommendations described in AN2860 (EMC guidelines for STM8S microcontrollers).

## Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage (applied to each power supply pin),

- A current injection (applied to each input, output and configurable I/O pin) are performed on each sample.

This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

| Symbol | Parameter             | Conditions              | Class <sup>(1)</sup> |

|--------|-----------------------|-------------------------|----------------------|

| LU     | Static latch-up class | T <sub>A</sub> = 25 °C  |                      |

|        |                       | T <sub>A</sub> = 85 °C  | ٨                    |

|        |                       | T <sub>A</sub> = 125 °C | A                    |

|        |                       | T <sub>A</sub> = 150 °C |                      |

Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to class A it exceeds the JEDEC standard. B class strictly covers all the JEDEC criteria (international standard).

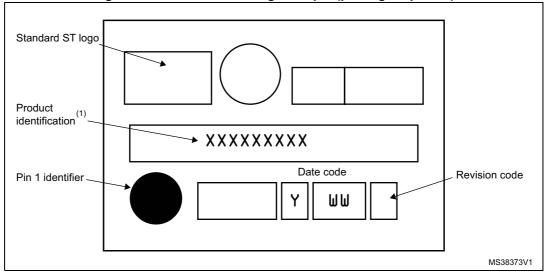

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

1. Parts marked as "ES" or "E" are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity.

Figure 49. VFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch very thin profile fine pitch quad flat package recommended footprint

1. Dimensions are expressed in millimeters.