Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Product Status             | Obsolete                                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | F <sup>2</sup> MC-16FX                                                         |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 56MHz                                                                          |

| Connectivity               | CANbus, LINbus, SCI, UART/USART                                                |

| Peripherals                | DMA, LVD, LVR, POR, PWM, WDT                                                   |

| Number of I/O              | 36                                                                             |

| Program Memory Size        | 160KB (160K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                      |

| Data Converters            | A/D 12x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 48-LQFP                                                                        |

| Supplier Device Package    | 48-LQFP (7x7)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb96f315rsbpmc-gse1 |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Product Lineup

| Featu                   | ures                  | MB96V300C                                          | MB96(F)31x                                                             |

|-------------------------|-----------------------|----------------------------------------------------|------------------------------------------------------------------------|

| Produc                  | t type                | Evaluation sample                                  | Flash product: MB96F31x<br>Mask ROM product: MB9631x                   |

| Product                 | options               |                                                    |                                                                        |

| YS                      |                       | NA                                                 | Low voltage reset persistently on / Single clock devices               |

| R                       | S                     |                                                    | Low voltage reset can be disabled / Single clock devices               |

| Y۷                      | V                     |                                                    | Low voltage reset persistently on / Dual clock devices                 |

| RV                      | N                     |                                                    | Low voltage reset can be disabled / Dual clock devices                 |

| AS                      | S                     |                                                    | No CAN / Low voltage reset can be disabled / Single clock devices      |

| AV                      | V                     |                                                    | No CAN / Low voltage reset can be disabled / Dual clock devices        |

| Flash/ROM               | RAM                   |                                                    |                                                                        |

| 96KB                    | 8KB                   | ROM/Flash memory                                   | MB96F313Y, MB96F313R, MB96F313A                                        |

| 160KB                   | 8KB                   | emulation by external<br>RAM, 92KB internal<br>RAM | MB96F315Y, MB96F315R, MB96F315A                                        |

| Pack                    | age                   | BGA416                                             | FPT-48P-M26                                                            |

| DN                      | 1A                    | 16 channels                                        | 4 channels                                                             |

| USA                     | RT                    | 10 channels                                        | 3 channels                                                             |

| A/D Cor                 | nverter               | 40 channels                                        | 12 channels                                                            |

| A/D Converte<br>Voltage |                       | yes                                                | No                                                                     |

| 16-bit Relo             | oad Timer             | 6 channels + 1<br>channel (for PPG)                | 4 channels + 1 channel (for PPG)                                       |

| 16-bit Free-Ru          | unning Timer          | 4 channels                                         | 4 channels (without external clock input pin)                          |

| 16-bit Outpu            | it Compare            | 12 channels                                        | 2 channels                                                             |

| 16-bit Inpu             | t Capture             | 12 channels                                        | 4 channels (plus 3 channels for LIN USART)                             |

| 16-bit Program<br>Gene  | nmable Pulse<br>rator | 20 channels                                        | 14 channels                                                            |

| CAN Int                 | terface               | 5 channels                                         | 1 channel                                                              |

| External I              | nterrupts             | 16 channels                                        | 11 channels                                                            |

| Non-Maskat              | ole Interrupt         |                                                    | 1 channel                                                              |

| Real Tim                | e Clock               |                                                    | 1                                                                      |

| I/O P                   | orts                  | 136                                                | 34 for part number with suffix "W", 36 for part number with suffix "S" |

| Clock outpu             | ut function           |                                                    | 2 channels                                                             |

| Low volta               | ge reset              |                                                    | Yes                                                                    |

| On-chip RC              | C-oscillator          |                                                    | Yes                                                                    |

|                         |                       |                                                    |                                                                        |

# 4. Pin Function Description

# Pin Function description (1 of 2)

| Pin name         | Feature               | Description                                                   |

|------------------|-----------------------|---------------------------------------------------------------|

| ADTG_R           | ADC                   | Relocated A/D converter trigger input                         |

| ANn              | ADC                   | A/D converter channel n input                                 |

| AV <sub>CC</sub> | Supply                | Analog circuits power supply                                  |

| AVRH             | ADC                   | A/D converter high reference voltage input                    |

| AV <sub>SS</sub> | Supply                | Analog circuits power supply                                  |

| С                | Voltage regulator     | Internally regulated power supply stabilization capacitor pin |

| CKOTn            | Clock output function | Clock Output function n output                                |

| CKOTn_R          | Clock output function | Relocated Clock Output function n output                      |

| CKOTXn           | Clock output function | Clock Output function n inverted output                       |

| INn              | ICU                   | Input Capture Unit n input                                    |

| INTn             | External Interrupt    | External Interrupt n input                                    |

| INTn_R           | External Interrupt    | Relocated External Interrupt n input                          |

| MDn              | Core                  | Input pins for specifying the operating mode.                 |

| NMI              | External Interrupt    | Non-Maskable Interrupt input                                  |

| OUTn             | OCU                   | Output Compare Unit n waveform output                         |

| Pxx_n            | GPIO                  | General purpose IO                                            |

| PPGn             | PPG                   | Programmable Pulse Generator n output                         |

| PPGn_R           | PPG                   | Relocated Programmable Pulse Generator n output               |

| RSTX             | Core                  | Reset input                                                   |

| RXn              | CAN                   | CAN interface n RX input                                      |

| SCKn             | USART                 | USART n serial clock input/output                             |

| SCKn_R           | USART                 | Relocated USART n serial clock input/output                   |

| SINn             | USART                 | USART n serial data input                                     |

| SINn_R           | USART                 | Relocated USART n serial data input                           |

| SOTn             | USART                 | USART n serial data output                                    |

| SOTn_R           | USART                 | Relocated USART n serial data output                          |

| TINn             | Reload Timer          | Reload Timer n event input                                    |

| TINn_R           | Reload Timer          | Relocated Reload Timer n event input                          |

| TOTn             | Reload Timer          | Reload Timer n output                                         |

| TOTn_R           | Reload Timer          | Relocated Reload Timer n output                               |

# 5. Pin Circuit Type

## Pin circuit types

| FPT-48P-M26 |                            |  |  |  |  |

|-------------|----------------------------|--|--|--|--|

| Pin no.     | Circuit type <sup>*1</sup> |  |  |  |  |

| 1           | Supply                     |  |  |  |  |

| 2           | G                          |  |  |  |  |

| 3 to 12     | I                          |  |  |  |  |

| 13, 14      | B <sup>*2</sup>            |  |  |  |  |

| 13, 14      | H <sup>*3</sup>            |  |  |  |  |

| 15 to 17    | C                          |  |  |  |  |

| 18 to 32    | Н                          |  |  |  |  |

| 33          | E                          |  |  |  |  |

| 34, 35      | A                          |  |  |  |  |

| 36, 37      | Supply                     |  |  |  |  |

| 38          | F                          |  |  |  |  |

| 39 to 45    | Н                          |  |  |  |  |

| 46, 47      | I                          |  |  |  |  |

| 48          | Supply                     |  |  |  |  |

\*1: Please refer to "6."I/O Circuit Type"" for details on the I/O circuit types

\*2: Devices with suffix "W"

\*3: Devices without suffix "W"

## 8. RAMSTART Addresses

| Devices       | RAM size | RAMSTART0            |

|---------------|----------|----------------------|

| MB96F313/F315 | 8KByte   | 00:6240 <sub>H</sub> |

# I/O map MB96(F)315x (Sheet 6 of 22)

| Address                                      | Register                                      | Abbreviation<br>8-bit access | Abbreviation<br>16-bit access | Access |

|----------------------------------------------|-----------------------------------------------|------------------------------|-------------------------------|--------|

| 000104 <sub>H</sub>                          | DMA0 - I/O register address pointer low byte  | IOAL0                        | IOA0                          | R/W    |

| 000105 <sub>H</sub>                          | DMA0 - I/O register address pointer high byte | IOAH0                        |                               | R/W    |

| 000106 <sub>H</sub>                          | DMA0 - Data counter low byte                  | DCTL0                        | DCT0                          | R/W    |

| 000107 <sub>H</sub>                          | DMA0 - Data counter high byte                 | DCTH0                        |                               | R/W    |

| 000108 <sub>H</sub>                          | DMA1 - Buffer address pointer low byte        | BAPL1                        |                               | R/W    |

| 000109 <sub>H</sub>                          | DMA1 - Buffer address pointer middle byte     | BAPM1                        |                               | R/W    |

| 00010A <sub>H</sub>                          | DMA1 - Buffer address pointer high byte       | BAPH1                        |                               | R/W    |

| 00010B <sub>H</sub>                          | DMA1 - DMA control register                   | DMACS1                       |                               | R/W    |

| 00010C <sub>H</sub>                          | DMA1 - I/O register address pointer low byte  | IOAL1                        | IOA1                          | R/W    |

| 00010D <sub>H</sub>                          | DMA1 - I/O register address pointer high byte | IOAH1                        |                               | R/W    |

| 00010E <sub>H</sub>                          | DMA1 - Data counter low byte                  | DCTL1                        | DCT1                          | R/W    |

| 00010F <sub>H</sub>                          | DMA1 - Data counter high byte                 | DCTH1                        |                               | R/W    |

| 000110 <sub>H</sub>                          | DMA2 - Buffer address pointer low byte        | BAPL2                        |                               | R/W    |

| 000111 <sub>H</sub>                          | DMA2 - Buffer address pointer middle byte     | BAPM2                        |                               | R/W    |

| 000112 <sub>H</sub>                          | DMA2 - Buffer address pointer high byte       | BAPH2                        |                               | R/W    |

| 000113 <sub>H</sub>                          | DMA2 - DMA control register                   | DMACS2                       |                               | R/W    |

| 000114 <sub>H</sub>                          | DMA2 - I/O register address pointer low byte  | IOAL2                        | IOA2                          | R/W    |

| 000115 <sub>H</sub>                          | DMA2 - I/O register address pointer high byte | IOAH2                        |                               | R/W    |

| 000116 <sub>H</sub>                          | DMA2 - Data counter low byte                  | DCTL2                        | DCT2                          | R/W    |

| 000117 <sub>H</sub>                          | DMA2 - Data counter high byte                 | DCTH2                        |                               | R/W    |

| 000118 <sub>H</sub>                          | DMA3 - Buffer address pointer low byte        | BAPL3                        |                               | R/W    |

| 000119 <sub>H</sub>                          | DMA3 - Buffer address pointer middle byte     | BAPM3                        |                               | R/W    |

| 00011A <sub>H</sub>                          | DMA3 - Buffer address pointer high byte       | BAPH3                        |                               | R/W    |

| 00011B <sub>H</sub>                          | DMA3 - DMA control register                   | DMACS3                       |                               | R/W    |

| 00011C <sub>H</sub>                          | DMA3 - I/O register address pointer low byte  | IOAL3                        | IOA3                          | R/W    |

| 00011D <sub>H</sub>                          | DMA3 - I/O register address pointer high byte | IOAH3                        |                               | R/W    |

| 00011E <sub>H</sub>                          | DMA3 - Data counter low byte                  | DCTL3                        | DCT3                          | R/W    |

| 00011F <sub>H</sub>                          | DMA3 - Data counter high byte                 | DCTH3                        |                               | R/W    |

| 000120 <sub>H</sub> -<br>00017F <sub>H</sub> | Reserved                                      |                              |                               | -      |

## I/O map MB96(F)315x (Sheet 11 of 22)

| Address                                      | Register                                          | Abbreviation<br>8-bit access | Abbreviation<br>16-bit access | Access |

|----------------------------------------------|---------------------------------------------------|------------------------------|-------------------------------|--------|

| 000435 <sub>H</sub>                          | I/O Port P05 - Data Direction Register            | DDR05                        |                               | R/W    |

| 000436 <sub>H</sub>                          | I/O Port P06 - Data Direction Register            | DDR06                        |                               | R/W    |

| 000437 <sub>H</sub>                          | I/O Port P07 - Data Direction Register            | DDR07                        |                               | R/W    |

| 000438 <sub>H</sub> -<br>000443 <sub>H</sub> | Reserved                                          |                              |                               | -      |

| 000444 <sub>H</sub>                          | I/O Port P00 - Port Input Enable Register         | PIER00                       |                               | R/W    |

| 000445 <sub>H</sub>                          | I/O Port P01 - Port Input Enable Register         | PIER01                       |                               | R/W    |

| 000446 <sub>H</sub>                          | I/O Port P02 - Port Input Enable Register         | PIER02                       |                               | R/W    |

| 000447 <sub>H</sub>                          | I/O Port P03 - Port Input Enable Register         | PIER03                       |                               | R/W    |

| 000448 <sub>H</sub>                          | Reserved                                          |                              |                               | -      |

| 000449 <sub>H</sub>                          | I/O Port P05 - Port Input Enable Register         | PIER05                       |                               | R/W    |

| 00044A <sub>H</sub>                          | I/O Port P06 - Port Input Enable Register         | PIER06                       |                               | R/W    |

| 00044B <sub>H</sub>                          | I/O Port P07 - Port Input Enable Register         | PIER07                       |                               | R/W    |

| 00044C <sub>H</sub> -<br>000457 <sub>H</sub> | Reserved                                          |                              |                               | -      |

| 000458 <sub>H</sub>                          | I/O Port P00 - Port Input Level Register          | PILR00                       |                               | R/W    |

| 000459 <sub>H</sub>                          | I/O Port P01 - Port Input Level Register          | PILR01                       |                               | R/W    |

| 00045A <sub>H</sub>                          | I/O Port P02 - Port Input Level Register          | PILR02                       |                               | R/W    |

| 00045B <sub>H</sub>                          | I/O Port P03 - Port Input Level Register          | PILR03                       |                               | R/W    |

| 00045C <sub>H</sub>                          | Reserved                                          |                              |                               | -      |

| 00045D <sub>H</sub>                          | I/O Port P05 - Port Input Level Register          | PILR05                       |                               | R/W    |

| 00045E <sub>H</sub>                          | I/O Port P06 - Port Input Level Register          | PILR06                       |                               | R/W    |

| 00045F <sub>H</sub>                          | I/O Port P07 - Port Input Level Register          | PILR07                       |                               | R/W    |

| 000460 <sub>H</sub> -<br>00046B <sub>H</sub> | Reserved                                          |                              |                               | -      |

| 00046C <sub>H</sub>                          | I/O Port P00 - Extended Port Input Level Register | EPILR00                      |                               | R/W    |

| 00046D <sub>H</sub>                          | I/O Port P01 - Extended Port Input Level Register | EPILR01                      |                               | R/W    |

| 00046E <sub>H</sub>                          | I/O Port P02 - Extended Port Input Level Register | EPILR02                      |                               | R/W    |

| 00046F <sub>H</sub>                          | I/O Port P03 - Extended Port Input Level Register | EPILR03                      |                               | R/W    |

| 000470 <sub>H</sub>                          | Reserved                                          |                              |                               | -      |

| 000471 <sub>H</sub>                          | I/O Port P05 - Extended Port Input Level Register | EPILR05                      |                               | R/W    |

| 000472 <sub>H</sub>                          | I/O Port P06 - Extended Port Input Level Register | EPILR06                      |                               | R/W    |

## I/O map MB96(F)315x (Sheet 18 of 22)

| Address             | Register                             | Abbreviation<br>8-bit access | Abbreviation<br>16-bit access | Access |

|---------------------|--------------------------------------|------------------------------|-------------------------------|--------|

| 0005C2 <sub>H</sub> | PPG16 - Period setting register      |                              | PCSR16                        | W      |

| 0005C3 <sub>H</sub> | PPG16 - Period setting register      |                              |                               | W      |

| 0005C4 <sub>H</sub> | PPG16 - Duty cycle register          |                              | PDUT16                        | W      |

| 0005C5 <sub>H</sub> | PPG16 - Duty cycle register          |                              |                               | W      |

| 0005C6 <sub>H</sub> | PPG16 - Control status register Low  | PCNL16                       | PCN16                         | R/W    |

| 0005C7 <sub>H</sub> | PPG16 - Control status register High | PCNH16                       |                               | R/W    |

| 0005C8 <sub>H</sub> | PPG17 - Timer register               |                              | PTMR17                        | R      |

| 0005C9 <sub>H</sub> | PPG17 - Timer register               |                              |                               | R      |

| 0005CA <sub>H</sub> | PPG17 - Period setting register      |                              | PCSR17                        | W      |

| 0005CB <sub>H</sub> | PPG17 - Period setting register      |                              |                               | W      |

| 0005CC <sub>H</sub> | PPG17 - Duty cycle register          |                              | PDUT17                        | W      |

| 0005CD <sub>H</sub> | PPG17 - Duty cycle register          |                              |                               | W      |

| 0005CE <sub>H</sub> | PPG17 - Control status register Low  | PCNL17                       | PCN17                         | R/W    |

| 0005CF <sub>H</sub> | PPG17 - Control status register High | PCNH17                       |                               | R/W    |

| 0005D0 <sub>H</sub> | PPG18 - Timer register               |                              | PTMR18                        | R      |

| 0005D1 <sub>H</sub> | PPG18 - Timer register               |                              |                               | R      |

| 0005D2 <sub>H</sub> | PPG18 - Period setting register      |                              | PCSR18                        | W      |

| 0005D3 <sub>H</sub> | PPG18 - Period setting register      |                              |                               | W      |

| 0005D4 <sub>H</sub> | PPG18 - Duty cycle register          |                              | PDUT18                        | W      |

| 0005D5 <sub>H</sub> | PPG18 - Duty cycle register          |                              |                               | W      |

| 0005D6 <sub>H</sub> | PPG18 - Control status register Low  | PCNL18                       | PCN18                         | R/W    |

| 0005D7 <sub>H</sub> | PPG18 - Control status register High | PCNH18                       |                               | R/W    |

| 0005D8 <sub>H</sub> | PPG19 - Timer register               |                              | PTMR19                        | R      |

| 0005D9 <sub>H</sub> | PPG19 - Timer register               |                              |                               | R      |

| 0005DA <sub>H</sub> | PPG19 - Period setting register      |                              | PCSR19                        | W      |

| 0005DB <sub>H</sub> | PPG19 - Period setting register      |                              |                               | W      |

| 0005DC <sub>H</sub> | PPG19 - Duty cycle register          |                              | PDUT19                        | W      |

| 0005DD <sub>H</sub> | PPG19 - Duty cycle register          |                              |                               | W      |

| 0005DE <sub>H</sub> | PPG19 - Control status register Low  | PCNL19                       | PCN19                         | R/W    |

| 0005DF <sub>H</sub> | PPG19 - Control status register High | PCNH19                       |                               | R/W    |

## I/O map MB96(F)315x (Sheet 19 of 22)

| Address                                      | Register                                         | Abbreviation<br>8-bit access | Abbreviation<br>16-bit access | Access |

|----------------------------------------------|--------------------------------------------------|------------------------------|-------------------------------|--------|

| 0005E0 <sub>H</sub> -<br>00065F <sub>H</sub> | Reserved                                         |                              |                               | -      |

| 000660 <sub>H</sub>                          | Peripheral Resource Relocation Register 10       | PRRR10                       |                               | R/W    |

| 000661 <sub>H</sub>                          | Peripheral Resource Relocation Register 11       | PRRR11                       |                               | R/W    |

| 000662 <sub>H</sub>                          | Peripheral Resource Relocation Register 12       | PRRR12                       |                               | R/W    |

| 000663 <sub>H</sub>                          | Peripheral Resource Relocation Register 13       | PRRR13                       |                               | W      |

| 000664 <sub>H</sub> -<br>0008FF <sub>H</sub> | Reserved                                         |                              |                               | -      |

| 000900 <sub>H</sub>                          | CAN2 - Control register Low                      | CTRLRL2                      | CTRLR2                        | R/W    |

| 000901 <sub>H</sub>                          | CAN2 - Control register High (reserved)          | CTRLRH2                      |                               | R      |

| 000902 <sub>H</sub>                          | CAN2 - Status register Low                       | STATRL2                      | STATR2                        | R/W    |

| 000903 <sub>H</sub>                          | CAN2 - Status register High (reserved)           | STATRH2                      |                               | R      |

| 000904 <sub>H</sub>                          | CAN2 - Error Counter Low (Transmit)              | ERRCNTL2                     | ERRCNT2                       | R      |

| 000905 <sub>H</sub>                          | CAN2 - Error Counter High (Receive)              | ERRCNTH2                     |                               | R      |

| 000906 <sub>H</sub>                          | CAN2 - Bit Timing Register Low                   | BTRL2                        | BTR2                          | R/W    |

| 000907 <sub>H</sub>                          | CAN2 - Bit Timing Register High                  | BTRH2                        |                               | R/W    |

| 000908 <sub>H</sub>                          | CAN2 - Interrupt Register Low                    | INTRL2                       | INTR2                         | R      |

| 000909 <sub>H</sub>                          | CAN2 - Interrupt Register High                   | INTRH2                       |                               | R      |

| 00090A <sub>H</sub>                          | CAN2 - Test Register Low                         | TESTRL2                      | TESTR2                        | R/W    |

| 00090B <sub>H</sub>                          | CAN2 - Test Register High (reserved)             | TESTRH2                      |                               | R      |

| 00090C <sub>H</sub>                          | CAN2 - BRP Extension register Low                | BRPERL2                      | BRPER2                        | R/W    |

| 00090D <sub>H</sub>                          | CAN2 - BRP Extension register High (reserved)    | BRPERH2                      |                               | R      |

| 00090E <sub>H</sub> -<br>00090F <sub>H</sub> | Reserved                                         |                              |                               | -      |

| 000910 <sub>H</sub>                          | CAN2 - IF1 Command request register Low          | IF1CREQL2                    | IF1CREQ2                      | R/W    |

| 000911 <sub>H</sub>                          | CAN2 - IF1 Command request register High         | IF1CREQH2                    |                               | R/W    |

| 000912 <sub>H</sub>                          | CAN2 - IF1 Command Mask register Low             | IF1CMSKL2                    | IF1CMSK2                      | R/W    |

| 000913 <sub>H</sub>                          | CAN2 - IF1 Command Mask register High (reserved) | IF1CMSKH2                    |                               | R      |

| 000914 <sub>H</sub>                          | CAN2 - IF1 Mask 1 Register Low                   | IF1MSK1L2                    | IF1MSK12                      | R/W    |

| 000915 <sub>H</sub>                          | CAN2 - IF1 Mask 1 Register High                  | IF1MSK1H2                    |                               | R/W    |

| 000916 <sub>H</sub>                          | CAN2 - IF1 Mask 2 Register Low                   | IF1MSK2L2                    | IF1MSK22                      | R/W    |

| 000917 <sub>H</sub>                          | CAN2 - IF1 Mask 2 Register High                  | IF1MSK2H2                    |                               | R/W    |

| Vector<br>number | Offset in vector table | Vector name | Cleared by<br>DMA | Index in ICR to program | Description                        |

|------------------|------------------------|-------------|-------------------|-------------------------|------------------------------------|

| 36               | 36C <sub>H</sub>       |             |                   |                         | Reserved                           |

| 37               | 368 <sub>H</sub>       | PPG3        | Yes               | 37                      | Programmable Pulse Generator 3     |

| 38               | 364 <sub>H</sub>       | PPG4        | Yes               | 38                      | Programmable Pulse Generator 4     |

| 39               | 360                    |             |                   |                         | Reserved                           |

| 40               | 35C <sub>H</sub>       | PPG6        | Yes               | 40                      | Programmable Pulse Generator 6     |

| 41               | 358 <sub>H</sub>       | PPG7        | Yes               | 41                      | Programmable Pulse Generator 7     |

| 42               | 354 <sub>H</sub>       | PPG8        | Yes               | 42                      | Programmable Pulse Generator 8     |

| 43               | 350 <sub>H</sub>       | PPG9        | Yes               | 43                      | Programmable Pulse Generator 9     |

| 44               | 34C <sub>H</sub>       |             |                   |                         | Reserved                           |

| 45               | 348 <sub>H</sub>       |             |                   |                         | Reserved                           |

| 46               | 344 <sub>H</sub>       | PPG12       | Yes               | 46                      | Programmable Pulse Generator 12    |

| 47               | 340 <sub>H</sub>       |             |                   |                         | Reserved                           |

| 48               | 33C <sub>H</sub>       | PPG14       | Yes               | 48                      | Programmable Pulse Generator 14    |

| 49               | 338 <sub>H</sub>       |             |                   |                         | Reserved                           |

| 50               | 334 <sub>H</sub>       | PPG16       | Yes               | 50                      | Programmable Pulse Generator 16    |

| 51               | 330 <sub>H</sub>       | PPG17       | Yes               | 51                      | Programmable Pulse Generator 17    |

| 52               | 32C <sub>H</sub>       | PPG18       | Yes               | 52                      | Programmable Pulse Generator 18    |

| 53               | 328 <sub>H</sub>       | PPG19       | Yes               | 53                      | Programmable Pulse Generator 19    |

| 54               | 324 <sub>H</sub>       | RLT0        | Yes               | 54                      | Reload Timer 0                     |

| 55               | 320 <sub>H</sub>       | RLT1        | Yes               | 55                      | Reload Timer 1                     |

| 56               | 31C <sub>H</sub>       | RLT2        | Yes               | 56                      | Reload Timer 2                     |

| 57               | 318 <sub>H</sub>       | RLT3        | Yes               | 57                      | Reload Timer 3                     |

| 58               | 314 <sub>H</sub>       | PPGRLT      | Yes               | 58                      | Reload Timer 6 - dedicated for PPG |

| 59               | 310 <sub>H</sub>       | ICU0        | Yes               | 59                      | Input Capture Unit 0               |

| 60               | 30C <sub>H</sub>       | ICU1        | Yes               | 60                      | Input Capture Unit 1               |

| 61               | 308 <sub>H</sub>       |             |                   |                         | Reserved                           |

| 62               | 304 <sub>H</sub>       |             |                   |                         | Reserved                           |

| 63               | 300 <sub>H</sub>       | ICU4        | Yes               | 63                      | Input Capture Unit 4               |

| 64               | 2FC <sub>H</sub>       | ICU5        | Yes               | 64                      | Input Capture Unit 5               |

| 65               | 2F8 <sub>H</sub>       | ICU6        | Yes               | 65                      | Input Capture Unit 6               |

| 66               | 2F4 <sub>H</sub>       |             |                   |                         | Reserved                           |

| 67               | 2F0 <sub>H</sub>       |             |                   |                         | Reserved                           |

| 68               | 2EC <sub>H</sub>       | ICU9        | Yes               | 68                      | Input Capture Unit 9               |

| 69               | 2E8 <sub>H</sub>       | ICU10       | Yes               | 69                      | Input Capture Unit 10              |

| 70               | 2E4 <sub>H</sub>       |             |                   |                         | Reserved                           |

| 71               | 2E0 <sub>H</sub>       |             |                   |                         | Reserved                           |

| 72               | 2DC <sub>H</sub>       |             |                   |                         | Reserved                           |

## 13. Handling Devices

#### Special care is required for the following when handling the device:

- Latch-up prevention

- · Unused pins handling

- External clock usage

- · Unused sub clock signal

- Notes on PLL clock mode operation

- Power supply pins (V<sub>CC</sub>/V<sub>SS</sub>)

- Crystal oscillator circuit

- Turn on sequence of power supply to A/D converter and analog inputs

- · Pin handling when not using the A/D converter

- · Notes on energization

- Stabilization of power supply voltage

- · Serial communication

#### 13.1 Latch-up prevention

CMOS IC chips may suffer latch-up under the following conditions:

- A voltage higher than V<sub>CC</sub> or lower than V<sub>SS</sub> is applied to an input or output pin.

- A voltage higher than the rated voltage is applied between V<sub>CC</sub> pins and V<sub>SS</sub> pins.

Latch-up may increase the power supply current dramatically, causing thermal damages to the device.

#### 13.2 Unused pins handling

Unused input pins can be left open when the input is disabled (corresponding bit of Port Input Enable register PIER = 0).

Leaving unused input pins open when the input is enabled may result in misbehavior and possible permanent damage of the device. They must therefore be pulled up or pulled down through resistors. To prevent latch-up, those resistors should be more than 2 k $\Omega$ .

Unused bidirectional pins can be set either to the output state and be then left open, or to the input state with either input disabled or external pull-up/pull-down resistor as described above.

#### 13.3 External clock usage

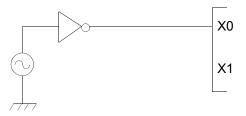

The permitted frequency range of an external clock depends on the oscillator type and configuration. See AC Characteristics for detailed modes and frequency limits. Single and opposite phase external clocks must be connected as follows:

1. Single phase external clock

• When using a single phase external clock, X0 (X0A) pin must be driven and X1 (X1A) pin left open.

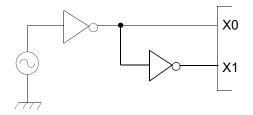

#### 2. Opposite phase external clock

• When using an opposite phase external clock, X1 (X1A) must be supplied with a clock signal which has the opposite phase to the X0 (X0A) pins.

#### 13.4 Unused sub clock signal

If the pins X0A and X1A are not connected to an oscillator, a pull-down resistor must be connected on the X0A pin and the X1A pin must be left open.

#### 13.5 Notes on PLL clock mode operation

If the PLL clock mode is selected and no external oscillator is operating or no external clock is supplied, the microcontroller attempts to work with the free oscillating PLL. Performance of this operation, however, cannot be guaranteed.

### 13.6 Power supply pins (V<sub>CC</sub>/V<sub>SS</sub>)

It is required that all  $V_{CC}$ -level as well as all  $V_{SS}$ -level power supply pins are at the same potential. If there is more than one  $V_{CC}$  or  $V_{SS}$  level, the device may operate incorrectly or be damaged even within the guaranteed operating range.

V<sub>CC</sub> and V<sub>SS</sub> must be connected to the device from the power supply with lowest possible impedance.

As a measure against power supply noise, it is required to connect a bypass capacitor of about 0.1  $\mu$ F between V<sub>CC</sub> and V<sub>SS</sub> as close as possible to V<sub>CC</sub> and V<sub>SS</sub> pins.

#### 13.7 Crystal oscillator and ceramic resonator circuit

Noise at X0, X1 pins or X0A, X1A pins might cause abnormal operation. It is required to provide bypass capacitors with shortest possible distance to X0, X1 pins and X0A, X1A pins, crystal oscillator (or ceramic resonator) and ground lines, and, to the utmost effort, that the lines of oscillation circuit do not cross the lines of other circuits.

It is highly recommended to provide a printed circuit board art work surrounding X0, X1 pins and X0A, X1A pins with a ground area for stabilizing the operation.

It is highly recommended to evaluate the quartz/MCU or resonator/MCU system at the quartz or resonator manufacturer, especially when using low-Q resonators at higher frequencies.

#### 13.8 Turn on sequence of power supply to A/D converter and analog inputs

It is required to turn the A/D converter power supply (AV<sub>CC</sub>, AVRH, AVRL) and analog inputs (ANn) on after turning the digital power supply (V<sub>CC</sub>) on.

It is also required to turn the digital power off after turning the A/D converter supply and analog inputs off. In this case, the voltage must not exceed AVRH or  $AV_{CC}$  (turning the analog and digital power supplies simultaneously on or off is acceptable).

#### 13.9 Pin handling when not using the A/D converter

It is required to connect the unused pins of the A/D converter as  $AV_{CC} = V_{CC}$ ,  $AV_{SS} = AVRH = AVRL = V_{SS}$ .

#### 13.10 Notes on Power-on

To prevent malfunction of the internal voltage regulator, supply voltage profile while turning the power supply on should be slower than  $50\mu s$  from 0.2 V to 2.7 V.

### 13.11 Stabilization of power supply voltage

If the power supply voltage varies acutely even within the operation safety range of the Vcc power supply voltage, a malfunction may occur. The Vcc power supply voltage must therefore be stabilized. As stabilization guidelines, the power supply voltage must be stabilized in such a way that Vcc ripple fluctuations (peak to peak value) in the commercial frequencies (50 to 60 Hz) fall within 10% of the standard Vcc power supply voltage and the transient fluctuation rate becomes 0.1V/µs or less in instantaneous fluctuation for power supply switching.

#### 13.12 Serial communication

There is a possibility to receive wrong data due to noise or other causes on the serial communication.

Therefore, design a printed circuit board so as to avoid noise.

Consider receiving of wrong data when designing the system. For example apply a checksum and retransmit the data if an error occurs.

|                                            |                     |                                                                              |                  | Value     |      |      |         |

|--------------------------------------------|---------------------|------------------------------------------------------------------------------|------------------|-----------|------|------|---------|

| Parameter                                  | Symbol              | Condition (at T <sub>A</sub> )                                               |                  | уа<br>Тур | Max  | Unit | Remarks |

|                                            |                     | PLL Sleep mode with<br>CLKS1/2 = CLKP1 = 16MHz,                              | +25°C            | 4         | 6    | mA   |         |

|                                            |                     | CLKP2 = 8MHz<br>(CLKRC and CLKSC stopped)                                    | +125°C           | 4.7       | 9    |      |         |

|                                            |                     | PLL Sleep mode with<br>CLKS1/2 = CLKP1 = 32MHz,<br>CLKP2 = 16MHz             | +25°C            | 7         | 9.5  | mA   |         |

|                                            |                     | (CLKRC and CLKSC stopped)                                                    | +125°C           | 8         | 12.5 |      |         |

|                                            |                     | PLL Sleep mode with<br>CLKS1/2 = 48MHz,                                      | +25°C            | 7         | 9    | mA   |         |

|                                            | I <sub>CCSPLL</sub> | CLKP1/2 = 24MHz<br>(CLKRC and CLKSC stopped)                                 | +125°C           | 8         | 12   | ША   |         |

|                                            |                     | PLL Sleep mode with<br>CLKS1/2 = CLKP1= 56MHz,<br>CLKP2 = 28MHz              | +25°C            | 11        | 14.5 |      |         |

| Power supply<br>current in<br>Sleep modes* |                     | (CLKRC and CLKSC stopped.<br>Core voltage at 1.9V)                           | +125°C           | 12        | 17.5 | mA   |         |

|                                            |                     | PLL Sleep mode with<br>CLKS1/2 = 96MHz,                                      | CLKS1/2 = 96MHz, |           |      |      |         |

|                                            |                     | CLKP1= 48MHz,<br>CLKP2 = 24MHz                                               |                  |           |      | mA   |         |

|                                            |                     | (CLKRC and CLKSC stopped.<br>Core voltage at 1.9V)                           | +125°C           | 13        | 18   |      |         |

|                                            | ICCSMAIN            | Main Sleep mode with<br>CLKS1/2 = CLKP1/2 = 4MHz                             | +25°C            | 1         | 1.3  | mA   |         |

|                                            |                     | (CLKPLL, CLKSC and CLKRC stopped)                                            | +125°C           | 1.6       | 4.1  | mA   |         |

|                                            | I <sub>CCSRCH</sub> | RC Sleep mode with<br>CLKS1/2 = CLKP1/2 = 2MHz                               | +25°C            | 0.55      | 1.1  | m۸   |         |

|                                            |                     | (CLKMC, CLKPLL and<br>CLKSC stopped)                                         | +125°C           | 1.15      | 3.9  | mA   |         |

|                                            |                     | RC Sleep mode with<br>CLKS1/2 = CLKP1/2 =                                    | +25°C            | 0.08      | 0.2  |      |         |

|                                            |                     | 100kHz,<br>SMCR:LPMSS = 0<br>(CLKMC, CLKPLL and                              | +125°C           | 0.59      | 2.95 | mA   |         |

|                                            | I <sub>CCSRCL</sub> | CLKSC stopped. Voltage<br>regulator in high power mode)                      | 120 0            | 0.00      | 2.55 |      |         |

| Power supply<br>current in<br>Sleep modes* |                     | RC Sleep mode with CLKS1/2<br>= CLKP1/2 = 100kHz,<br>SMCR:LPMSS = 1          | +25°C            | 0.05      | 0.15 |      |         |

|                                            |                     | (CLKMC, CLKPLL and<br>CLKSC stopped. Voltage<br>regulator in low power mode) | +125°C           | 0.56      | 2.9  | mA   |         |

|                                            | 1                   | Sub Sleep mode with<br>CLKS1/2 = CLKP1/2 = 32kHz                             | +25°C            | 0.04      | 0.12 |      |         |

|                                            | ICCSSUB             | (CLKMC, CLKPLL and<br>CLKRC stopped)                                         | +125°C           | 0.54      | 2.9  | mA   |         |

(T<sub>A</sub> = -40°C to 125°C, V<sub>CC</sub> = AV<sub>CC</sub> = 3.0V to 5.5V, V<sub>SS</sub> = AV<sub>SS</sub> = 0V)

| Parameter                                             | Symbol                                          | Condition (at T <sub>A</sub> )                 |        | Va    | ue   | Unit    | Demerke                                                                                                 |

|-------------------------------------------------------|-------------------------------------------------|------------------------------------------------|--------|-------|------|---------|---------------------------------------------------------------------------------------------------------|

| Parameter                                             | Parameter Symbol Condition (at T <sub>A</sub> ) |                                                | Тур    | Max   | Unit | Remarks |                                                                                                         |

|                                                       |                                                 | VRCR:LPMB[2:0] = 110 <sub>B</sub>              | +25°C  | 0.02  | 0.08 | mA      |                                                                                                         |

| Power supply                                          | lagu                                            | (Core voltage at 1.8V)                         | +125°C | 0.52  | 2.8  | ШA      |                                                                                                         |

| current in Stop Mode                                  | I <sub>ССН</sub>                                | VRCR:LPMB[2:0] = 000 <sub>B</sub>              | +25°C  | 0.015 | 0.06 | mA      |                                                                                                         |

|                                                       |                                                 | (Core voltage at 1.2V)                         | +125°C | 0.4   | 2.3  |         |                                                                                                         |

| Power supply<br>current for active                    | ICCLVD                                          | Low voltage detector enabled<br>(RCR:LVDE = 1) | +25°C  | 5     | 10   | μA      | Must be added to all<br>current above                                                                   |

| Low Voltage detector                                  | CCLVD                                           |                                                | +125°C | 7     | 20   |         |                                                                                                         |

| Power supply<br>current for active<br>Clock modulator | I <sub>CCCLOMO</sub>                            | Clock modulator enabled<br>(CMCR:PDX = 1)      | -      | 3     | 4.5  | mA      | Must be added to all current above                                                                      |

| Flash Write/Erase<br>current                          | I <sub>CCFLASH</sub>                            | Current for one Flash module                   | -      | 15    | 40   | mA      | Must be added to all<br>current above                                                                   |

| Input capacitance                                     | C <sub>IN</sub>                                 | -                                              | -      | 5     | 15   | pF      | Other than C, AV <sub>CC</sub> ,<br>AV <sub>SS</sub> , AVRH, AVRL, V <sub>CC</sub> ,<br>V <sub>SS</sub> |

(T<sub>A</sub> = -40°C to 125°C, V<sub>CC</sub> = AV<sub>CC</sub> = 3.0V to 5.5V, V<sub>SS</sub> = AV<sub>SS</sub> = 0V)

\* : The power supply current is measured with a 4MHz external clock connected to the Main oscillator and a 32kHz external clock connected to the Sub oscillator. See chapter "Standby mode and voltage regulator control circuit" of the Hardware Manual for further details about voltage regulator control.

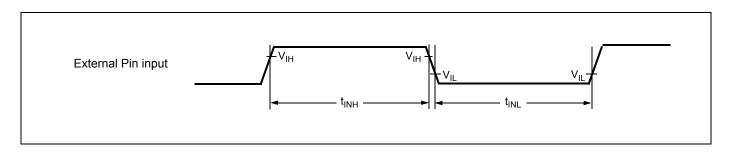

## **External Input timing**

| Parameter            | Symbol                               | Pin      | Condition | Value                                                                     |     | Unit | Used Pin input function |

|----------------------|--------------------------------------|----------|-----------|---------------------------------------------------------------------------|-----|------|-------------------------|

| Falameter            |                                      |          |           | Min                                                                       | Мах |      |                         |

| Input pulse<br>width | t <sub>INH</sub><br>t <sub>INL</sub> | INTn(_R) |           | 200                                                                       | _   | ns   | External Interrupt      |

|                      |                                      | NMI      |           |                                                                           |     |      | NMI                     |

|                      |                                      | Pnn_m    |           | 2*t <sub>CLKP1</sub> + 200<br>(t <sub>CLKP1</sub> =1/f <sub>CLKP1</sub> ) | _   | ns   | General Purpose IO      |

|                      |                                      | TINn     |           |                                                                           |     |      | Reload Timer            |

|                      |                                      | TTGn(_R) |           |                                                                           |     |      | PPG Trigger input       |

|                      |                                      | ADTG_R   |           |                                                                           |     |      | AD Converter Trigger    |

|                      |                                      | INn      |           |                                                                           |     |      | Input Capture           |

(T<sub>A</sub> = -40°C to 125°C, V<sub>CC</sub> = AV<sub>CC</sub> = 3.0V to 5.5V, V<sub>SS</sub> = AV<sub>SS</sub> = 0V)

Note : Relocated Resource Inputs have same characteristics

### **USART timing**

WARNING: The values given below are for an I/O driving strength IO<sub>drive</sub> = 5mA. If IO<sub>drive</sub> is 2mA, all the maximum output timing described in the different tables must then be increased by 10ns.

| Parameter                                                                                           | Symbol             | Pin           | Condition                    | $V_{CC} = AV_{CC} = 4.5V$<br>to 5.5V       |                              | $V_{CC} = AV_{CC} = 3.0V$ to<br>4.5V |                              | Unit |

|-----------------------------------------------------------------------------------------------------|--------------------|---------------|------------------------------|--------------------------------------------|------------------------------|--------------------------------------|------------------------------|------|

|                                                                                                     | Ē                  |               |                              | Min                                        | Max                          | Min                                  | Max                          |      |

| Serial clock cycle time                                                                             | t <sub>SCYCI</sub> | SCKn          |                              | 4 t <sub>CLKP1</sub>                       | —                            | 4 t <sub>CLKP1</sub>                 | -                            | ns   |

| $SCK \downarrow \to SOT \text{ delay time}$                                                         | t <sub>SLOVI</sub> | SCKn,<br>SOTn |                              | -20                                        | +20                          | -30                                  | +30                          | ns   |

| $SOT \to SCK \uparrow delay \text{ time}$                                                           | t <sub>ovshi</sub> | SCKn,<br>SOTn | Internal Shift<br>Clock Mode | N*t <sub>CLKP1</sub><br>- 20 <sup>*1</sup> |                              | N*t <sub>CLKP1</sub> -<br>30 *1      | _                            | ns   |

| Valid SIN $\rightarrow$ SCK $\uparrow$                                                              | t <sub>IVSHI</sub> | SCKn,<br>SINn |                              | t <sub>CLKP1</sub> +<br>45                 | _                            | t <sub>CLKP1</sub> +<br>55           | _                            | ns   |

| $\begin{array}{l} \text{SCK} \uparrow \rightarrow \text{Valid SIN hold} \\ \text{time} \end{array}$ | t <sub>SHIXI</sub> | SCKn,<br>SINn |                              | 0                                          | _                            | 0                                    | _                            | ns   |

| Serial clock "L" pulse width                                                                        | t <sub>SLSHE</sub> | SCKn          |                              | t <sub>CLKP1</sub> +<br>10                 | _                            | t <sub>CLKP1</sub> +<br>10           | _                            | ns   |

| Serial clock "H" pulse width                                                                        | t <sub>SHSLE</sub> | SCKn          |                              | t <sub>CLKP1</sub> +<br>10                 | _                            | t <sub>CLKP1</sub> +<br>10           | _                            | ns   |

| $SCK \downarrow \to SOT \text{ delay time}$                                                         | t <sub>SLOVE</sub> | SCKn,<br>SOTn | External Shift               | _                                          | 2 t <sub>CLKP1</sub><br>+ 45 | _                                    | 2 t <sub>CLKP1</sub><br>+ 55 | ns   |

| Valid SIN $\rightarrow$ SCK $\uparrow$                                                              | t <sub>IVSHE</sub> | SCKn,<br>SINn | Clock Mode                   | t <sub>CLKP1</sub> /2<br>+ 10              | _                            | t <sub>CLKP1</sub> /2 +<br>10        | _                            | ns   |

| $\begin{array}{l} \text{SCK} \uparrow \rightarrow \text{Valid SIN hold} \\ \text{time} \end{array}$ | t <sub>SHIXE</sub> | SCKn,<br>SINn |                              | t <sub>CLKP1</sub> +<br>10                 | _                            | t <sub>CLKP1</sub> +<br>10           | _                            | ns   |

| SCK fall time                                                                                       | t <sub>FE</sub>    | SCKn          | 1                            | —                                          | 20                           | —                                    | 20                           | ns   |

| SCK rise time                                                                                       | t <sub>RE</sub>    | SCKn          | 1                            | —                                          | 20                           | —                                    | 20                           | ns   |

| $(T_A = -40^{\circ}C \text{ to } 125^{\circ}C, V_{CC} = 3.0V \text{ to } 5.5V, V_{CC} = 3.0V \text{ to } 5.5V)$ | $V_{SS} = AV_{SS} = 0V, IO_{drive} = 5mA, C_1 = 50pF)$ |

|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| (·A ··· ··· ··· ··· ··· ··· ··· ··· ···                                                                         |                                                        |

Notes: • AC characteristic in CLK synchronized mode.

• C<sub>L</sub> is the load capacity value of pins when testing.

• Depending on the used machine clock frequency, the maximum possible baud rate can be limited by some parameters. These parameters are shown in "MB96300 Super series Hardware Manual".

• t<sub>CLKP1</sub> is the cycle time of the peripheral clock 1 (CLKP1), Unit : ns

\*1: Parameter N depends on  $t_{SCYCI}$  and can be calculated as follows: • if  $t_{SCYCI} = 2^*k^*t_{CLKP1}$ , then N = k, where k is an integer > 2

- if t<sub>SCYCI</sub> = (2\*k+1)\*t<sub>CLKP1</sub>, then N = k+1, where k is an integer > 1 Examples:

| tscyci                                      | N |

|---------------------------------------------|---|

| 4*t <sub>CLKP1</sub>                        | 2 |

| 5*t <sub>CLKP1</sub> , 6*t <sub>CLKP1</sub> | 3 |

| 7*t <sub>CLKP1</sub> , 8*t <sub>CLKP1</sub> | 4 |

|                                             |   |

### 14.7 FLASH memory program/erase characteristics

# (T<sub>A</sub> = -40°C to 105°C, V<sub>CC</sub> = AV<sub>CC</sub> = 3.0V to 5.5V, V<sub>SS</sub> = AV<sub>SS</sub> = 0V)

| Parameter                            | Value |       |       | Unit  | Remarks                                                                                    |  |

|--------------------------------------|-------|-------|-------|-------|--------------------------------------------------------------------------------------------|--|

| Falanietei                           | Min   | Тур   | Max   | Onit  | Kemarka                                                                                    |  |

| Sector erase time                    | -     | 0.9   | 3.6   | S     | Without erasure pre-programming time                                                       |  |

| Chip erase time                      | -     | n*0.9 | n*3.6 | s     | Without erasure pre-programming<br>time (n is the number of Flash sector<br>of the device) |  |

| Word (16-bit width) programming time | -     | 23    | 370   | us    | Without overhead time for submitting write command                                         |  |

| Program/Erase cycle                  | 10000 | -     | -     | cycle |                                                                                            |  |

| Flash data retention time            | 20    | -     | -     | year  | *1                                                                                         |  |

\*1: This value was converted from the results of evaluating the reliability of the technology (using Arrhenius equation to convert high temperature measurements into normalized value at 85°C)

| Mode name     | Details                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RC Sleep 100k | <ul> <li>RC Sleep mode current I<sub>CCSRCL</sub> with the following settings:</li> <li>RC oscillator set to 100kHz (CKFCR:RCFS = 0)</li> <li>f<sub>CLKS1</sub> = f<sub>CLKS2</sub> = f<sub>CLKP1</sub> = f<sub>CLKP2</sub> = 100kHz</li> <li>Regulator in Low Power Mode A (SMCR:LPMSS = 1)</li> <li>Core voltage at 1.8V (VRCR:LPMA[2:0] = 110<sub>B</sub>)</li> <li>PLL, Main oscillator and Sub oscillator stopped</li> </ul> |

| Sub Sleep     | <ul> <li>Sub Sleep mode current I<sub>CCSSUB</sub> with the following settings:</li> <li>f<sub>CLKS1</sub> = f<sub>CLKS2</sub> = f<sub>CLKP1</sub> = f<sub>CLKP2</sub> = 32kHz</li> <li>Regulator in Low Power Mode A (by hardware)</li> <li>Core voltage at 1.8V (VRCR:LPMA[2:0] = 110<sub>B</sub>)</li> <li>PLL, RC oscillator and Main oscillator stopped</li> </ul>                                                           |

| PLL Timer 48  | <ul> <li>PLL Timer mode current I<sub>CCTPLL</sub> with the following settings:</li> <li>f<sub>CLKS1</sub> = f<sub>CLKS2</sub> = 48MHz</li> <li>Regulator in High Power Mode</li> <li>Core voltage at 1.8V (VRCR:HPM[1:0] = 10<sub>B</sub>)</li> <li>RC oscillator and Sub oscillator stopped</li> </ul>                                                                                                                          |

| Main Timer    | <ul> <li>Main Timer mode current I<sub>CCTMAIN</sub> with the following settings:</li> <li>f<sub>CLKS1</sub> = f<sub>CLKS2</sub> = 4MHz</li> <li>Regulator in Low Power Mode A (SMCR:LPMSS = 1)</li> <li>Core voltage at 1.8V (VRCR:LPMA[2:0] = 110<sub>B</sub>)</li> <li>PLL, RC oscillator and Sub oscillator stopped</li> </ul>                                                                                                |

| RC Timer 2M   | <ul> <li>RC Timer mode current I<sub>CCTRCH</sub> with the following settings:</li> <li>RC oscillator set to 2MHz (CKFCR:RCFS = 1)</li> <li>f<sub>CLKS1</sub> = f<sub>CLKS2</sub> = 2MHz</li> <li>Regulator in Low Power Mode A (SMCR:LPMSS = 1)</li> <li>Core voltage at 1.8V (VRCR:LPMA[2:0] = 110<sub>B</sub>)</li> <li>PLL, Main oscillator and Sub oscillator stopped</li> </ul>                                             |

| RC Timer 100k | <ul> <li>RC Timer mode current I<sub>CCTRCL</sub> with the following settings:</li> <li>RC oscillator set to 100kHz (CKFCR:RCFS = 0)</li> <li>f<sub>CLKS1</sub> = f<sub>CLKS2</sub> = 100kHz</li> <li>Regulator in Low Power Mode A (SMCR:LPMSS = 1)</li> <li>Core voltage at 1.8V (VRCR:LPMA[2:0] = 110<sub>B</sub>)</li> <li>PLL, Main oscillator and Sub oscillator stopped</li> </ul>                                         |

| Sub Timer     | <ul> <li>Sub Timer mode current I<sub>CCTSUB</sub> with the following settings:</li> <li>f<sub>CLKS1</sub> = f<sub>CLKS2</sub> = 32kHz</li> <li>Regulator in Low Power Mode A (by hardware)</li> <li>Core voltage at 1.8V (VRCR:LPMA[2:0] = 110<sub>B</sub>)</li> <li>PLL, RC oscillator and Main oscillator stopped</li> </ul>                                                                                                   |

| Stop 1.8V     | <ul> <li>Stop mode current I<sub>CCH</sub> with the following settings:</li> <li>Regulator in Low Power Mode B (by hardware)</li> <li>Core voltage at 1.8V (VRCR:LPMB[2:0] = 110<sub>B</sub>)</li> </ul>                                                                                                                                                                                                                          |

| Stop 1.2V     | <ul> <li>Stop mode current I<sub>CCH</sub> with the following settings:</li> <li>Regulator in Low Power Mode B (by hardware)</li> <li>Core voltage at 1.2V (VRCR:LPMB[2:0] = 000<sub>B</sub>)</li> </ul>                                                                                                                                                                                                                          |

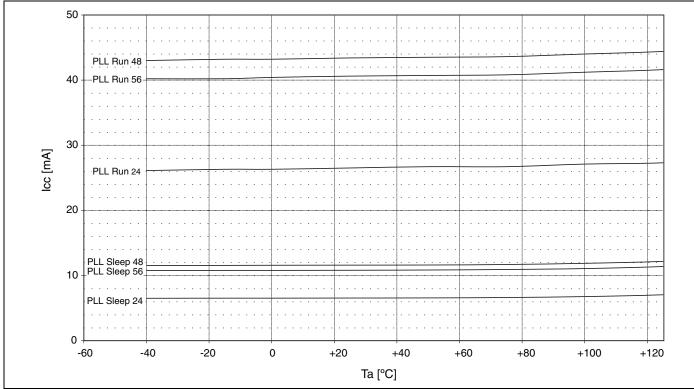

MB96F313/F315 PLL Run and Sleep mode currents

# 17. Ordering Information

### MCU with CAN controller

| Part number                        | Flash/ROM            | Subclock | Persistent<br>Low Voltage<br>Reset | Package                               |

|------------------------------------|----------------------|----------|------------------------------------|---------------------------------------|

| MB96F313YSB PMC-GSE2               |                      |          | Yes                                |                                       |

| MB96F313RSB PMC-GSE1               |                      | No       | No                                 |                                       |

| MB96F313RSB PMC-GSE2               | Flash A (96KB)       |          | No                                 |                                       |

| MB96F313YWB PMC-GSE2               |                      | Yes      | Yes                                | 48 pins Plastic LQFP<br>(FPT-48P-M26) |

| MB96F313RWB PMC-GSE2               |                      |          | No                                 |                                       |

| MB96F315YSB PMC-GSE2               |                      | No       | Yes                                |                                       |

| MB96F315RSB PMC-GSE1               | Flash A (160KB)      |          | No                                 |                                       |

| MB96F315RSB PMC-GSE2               |                      |          | No                                 |                                       |

| MB96F315YWB PMC-GSE2               |                      | Yes      | Yes                                |                                       |

| MB96F315RWB PMC-GSE2               |                      | Tes      | No                                 |                                       |

| MB96V300CRB-ES<br>(for evaluation) | Emulated by ext. RAM | Yes      | No                                 | 416 pin Plastic BGA<br>(BGA-416P-M02) |

### MCU without CAN controller

| Part number          | Flash/ROM       | Subclock | Persistent<br>Low Voltage<br>Reset | Package                               |  |

|----------------------|-----------------|----------|------------------------------------|---------------------------------------|--|

| MB96F313ASB PMC-GSE2 | Flash A (96KB)  | No       | - No                               |                                       |  |

| MB96F313AWB PMC-GSE2 | Flash A (90Kb)  | Yes      |                                    | 48 pins Plastic LQFP<br>(FPT-48P-M26) |  |

| MB96F315ASB PMC-GSE2 |                 | No       |                                    |                                       |  |

| MB96F315AWB PMC-GSE2 | Flash A (160KB) | Yes      |                                    |                                       |  |