#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 1.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                   |

| Data Converters            | A/D 25x12b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                             |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-LQFP                                                        |

| Supplier Device Package    | 32-LQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f541-iq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **List of Tables**

| Table 2.1. Product Selection Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Table 3.1. Pin Definitions for the C8051F54x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 18                                                                                                                                           |

| Table 4.1. QFP-32 Package Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23                                                                                                                                           |

| Table 4.2. QFP-32 Landing Diagram Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24                                                                                                                                           |

| Table 4.3. QFN-32 Package Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                              |

| Table 4.4. QFN-32 Landing Diagram Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 26                                                                                                                                           |

| Table 4.5. QFN-24 Package Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                              |

| Table 4.6. QFN-24 Landing Diagram Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                              |

| Table 6.1. Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                              |

| Table 6.2. Global Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                              |

| Table 6.3. Port I/O DC Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                              |

| Table 6.4. Reset Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                              |

| Table 6.5. Flash Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                              |

| Table 6.6. Internal High-Frequency Oscillator Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                              |

| Table 6.7. Clock Multiplier Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |

| Table 6.8. Voltage Regulator Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                              |

| Table 6.9. ADC0 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                              |

| Table 6.10. Temperature Sensor Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 56                                                                                                                                           |

| Table 6.11. Voltage Reference Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56                                                                                                                                           |

| Table 6.12. Comparator 0 and Comparator 1 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                              |

| Table 10.1. CIP-51 Instruction Set Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11                                                                                                                                           |

| Table 12.1. Special Function Register (SFR) Memory Map for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 100                                                                                                                                          |

| Pages 0x0 and 0xF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                              |

| Table 12.2. Special Function Registers         Table 12.1. Interrupt Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                              |

| Table 13.1. Interrupt Summary         Table 14.1. Elash Security Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                              |

| Table 14.1. Flash Security Summary       *         Table 18.1. Port I/O Assignment for Analog Functions       *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1/0                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                              |

| Table 18.2. Port I/O Assignment for Digital Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 149                                                                                                                                          |

| Table 18.2. Port I/O Assignment for Digital Functions       Table 18.3. Port I/O Assignment for External Digital Event Capture Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 149<br>150                                                                                                                                   |

| Table 18.2. Port I/O Assignment for Digital Functions       7         Table 18.3. Port I/O Assignment for External Digital Event Capture Functions       7         Table 19.1. Baud Rate Calculation Variable Ranges       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 149<br>150<br>171                                                                                                                            |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 149<br>150<br>171<br>173                                                                                                                     |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters Examples                                                                                                                                                                                                                                                                                                                                                                                                                                   | 149<br>150<br>171<br>173<br>174                                                                                                              |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)                                                                                                                                                                                                                                                                                                                                                                                | 149<br>150<br>171<br>173<br>174<br>179                                                                                                       |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source Selection                                                                                                                                                                                                                                                                                                                                        | 149<br>150<br>171<br>173<br>174<br>179<br>191                                                                                                |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source SelectionTable 20.2. Minimum SDA Setup and Hold Times                                                                                                                                                                                                                                                                                            | 149<br>150<br>171<br>173<br>174<br>179<br>191<br>192                                                                                         |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source SelectionTable 20.2. Minimum SDA Setup and Hold TimesTable 20.3. Sources for Hardware Changes to SMB0CN                                                                                                                                                                                                                                          | 149<br>150<br>171<br>173<br>174<br>179<br>191<br>192<br>196                                                                                  |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source SelectionTable 20.2. Minimum SDA Setup and Hold TimesTable 20.4. SMBus Status Decoding                                                                                                                                                                                                                                                           | <ul> <li>149</li> <li>150</li> <li>171</li> <li>173</li> <li>174</li> <li>179</li> <li>191</li> <li>192</li> <li>196</li> <li>202</li> </ul> |

| Table 18.2. Port I/O Assignment for Digital Functions       Table 18.3. Port I/O Assignment for External Digital Event Capture Functions         Table 19.1. Baud Rate Calculation Variable Ranges       Table 19.1. Baud Rate Calculation Variable Ranges         Table 19.2. Manual Baud Rate Parameters Examples       Table 19.3. Autobaud Parameters Examples         Table 19.4. LIN Registers* (Indirectly Addressable)       Table 20.1. SMBus Clock Source Selection         Table 20.2. Minimum SDA Setup and Hold Times       Table 20.3. Sources for Hardware Changes to SMB0CN         Table 20.4. SMBus Status Decoding       Table 21.1. Baud Rate Generator Settings for Standard Baud Rates | 149<br>150<br>171<br>173<br>174<br>179<br>191<br>192<br>196<br>202<br>206                                                                    |

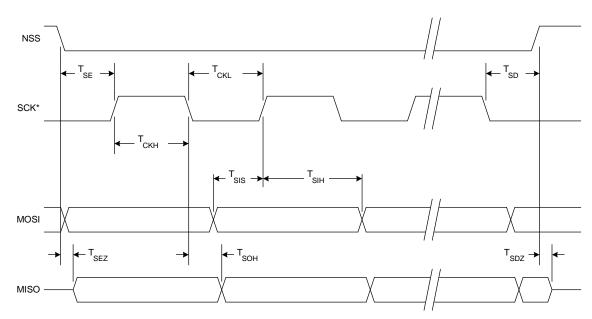

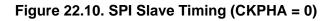

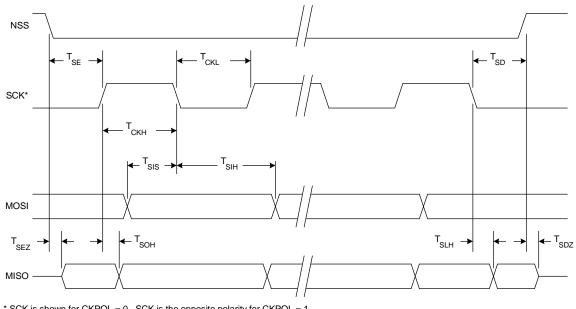

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source SelectionTable 20.2. Minimum SDA Setup and Hold TimesTable 20.3. Sources for Hardware Changes to SMB0CNTable 20.4. SMBus Status DecodingTable 21.1. Baud Rate Generator Settings for Standard Baud RatesTable 22.1. SPI Slave Timing Parameters                                                                                                  | 149<br>150<br>171<br>173<br>174<br>179<br>191<br>192<br>196<br>202<br>206<br>226                                                             |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source SelectionTable 20.2. Minimum SDA Setup and Hold TimesTable 20.3. Sources for Hardware Changes to SMB0CNTable 20.4. SMBus Status DecodingTable 21.1. Baud Rate Generator Settings for Standard Baud RatesTable 22.1. SPI Slave Timing ParametersTable 24.1. PCA Timebase Input Options                                                            | 149<br>150<br>171<br>173<br>174<br>179<br>191<br>192<br>196<br>202<br>206<br>226                                                             |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source SelectionTable 20.2. Minimum SDA Setup and Hold TimesTable 20.3. Sources for Hardware Changes to SMB0CNTable 20.4. SMBus Status DecodingTable 21.1. Baud Rate Generator Settings for Standard Baud RatesTable 22.1. SPI Slave Timing ParametersTable 24.1. PCA Timebase Input OptionsTable 24.2. PCA0CPM and PCA0PWM Bit Settings for            | 149<br>150<br>171<br>173<br>174<br>179<br>191<br>192<br>196<br>202<br>206<br>226<br>226                                                      |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source SelectionTable 20.2. Minimum SDA Setup and Hold TimesTable 20.3. Sources for Hardware Changes to SMB0CNTable 20.4. SMBus Status DecodingTable 21.1. Baud Rate Generator Settings for Standard Baud RatesTable 22.1. SPI Slave Timing ParametersTable 24.1. PCA Timebase Input Options                                                            | 149<br>150<br>171<br>173<br>174<br>179<br>191<br>192<br>202<br>206<br>226<br>250<br>250                                                      |

# 4. Package Specifications

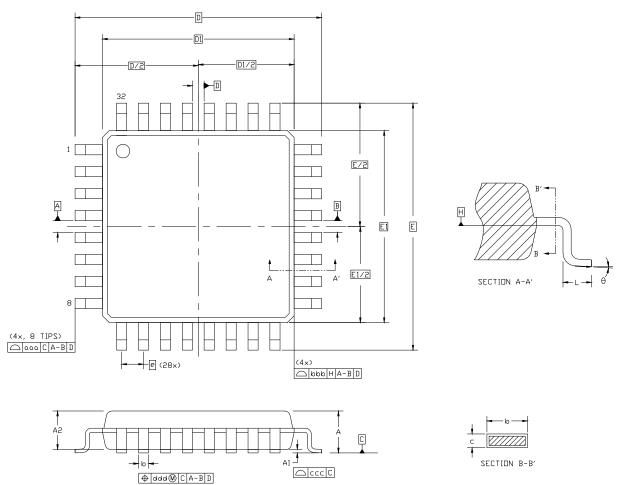

# 4.1. QFP-32 Package Specifications

### Figure 4.1. QFP-32 Package Drawing

### Table 4.1. QFP-32 Package Dimensions

| Dimension | Min         | Тур       | Max  | Dimension | Min  | Тур       | Max  |

|-----------|-------------|-----------|------|-----------|------|-----------|------|

| A         | — — 1.60    |           |      | E         |      | 9.00 BSC. |      |

| A1        | 0.05        | _         | 0.15 | E1        |      | 7.00 BSC. |      |

| A2        | 1.35        | 1.40      | 1.45 | L         | 0.45 | 0.60      | 0.75 |

| b         | 0.30        | 0.37      | 0.45 | aaa       | 0.20 |           |      |

| С         | 0.09 — 0.20 |           |      | bbb       |      | 0.20      |      |

| D         | 9.00 BSC.   |           |      | CCC       |      | 0.10      |      |

| D1        | 7.00 BSC.   |           |      | ddd       |      | 0.20      |      |

| е         |             | 0.80 BSC. |      | θ         | 0°   | 3.5°      | 7°   |

### Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to the JEDEC outline MS-026, variation BBA.

- Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

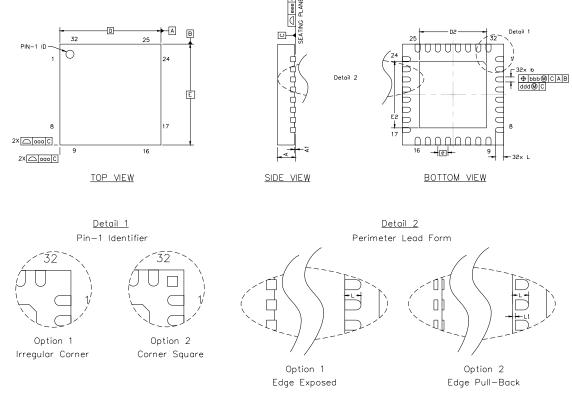

# 4.2. QFN-32 Package Specifications

Figure 4.3. QFN-32 Package Drawing

| Dimension | Min       | Тур       | Max  | Dimension | Min  | Тур  | Max  |

|-----------|-----------|-----------|------|-----------|------|------|------|

| A         | 0.80      | 0.9       | 1.00 | E2        | 3.20 | 3.30 | 3.40 |

| A1        | 0.00      | 0.02      | 0.05 | L         | 0.30 | 0.40 | 0.50 |

| b         | 0.18      | 0.25      | 0.30 | L1        | 0.00 | _    | 0.15 |

| D         | 5.00 BSC. |           |      | aaa       | _    | _    | 0.15 |

| D2        | 3.20      | 3.30      | 3.40 | bbb       | _    | _    | 0.15 |

| е         | 0.50 BSC. |           |      | ddd       | _    | —    | 0.05 |

| E         |           | 5.00 BSC. |      | eee       |      |      | 0.08 |

### Table 4.3. QFN-32 Package Dimensions

Notes:

- **1.** All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- **3.** This drawing conforms to the JEDEC Solid State Outline MO-220, variation VHHD except for custom features D2, E2, and L which are toleranced per supplier designation.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

# C8051F54x

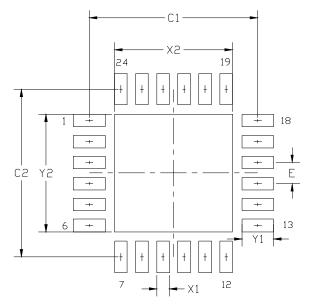

Figure 4.6. QFN-24 Landing Diagram

| Dimension | Min      | Max  | Dimension | Min  | Max  |

|-----------|----------|------|-----------|------|------|

| C1        | 3.90     | 4.00 | X2        | 2.70 | 2.80 |

| C2        | 3.90     | 4.00 | Y1        | 0.65 | 0.75 |

| E         | 0.50 BSC |      | Y2        | 2.70 | 2.80 |

| X1        | 0.20     | 0.30 |           |      |      |

Notes:

General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

Solder Mask Design

**3.** All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

Stencil Design

- **4.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

- **7.** A 2x2 array of 1.10 mm x 1.10 mm openings on a 1.30 mm pitch should be used for the center ground pad.

Card Assembly

- 8. A No-Clean, Type-3 solder paste is recommended.

- **9.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

For example, if ADC0GNH = 0xFC, ADC0GNL = 0x00, and GAINADD = 1, GAIN = 0xFC0 = 4032, and the resulting equation is as follows:

$$GAIN = \left(\frac{4032}{4096}\right) + 1 \times \left(\frac{1}{64}\right) = 0.984 + 0.016 = 1.0$$

The table below equates values in the ADC0GNH, ADC0GNL, and ADC0GNA registers to the equivalent gain using this equation.

| ADC0GNH Value  | ADC0GNL Value  | GAINADD Value | GAIN Value | Equivalent Gain |

|----------------|----------------|---------------|------------|-----------------|

| 0xFC (default) | 0x00 (default) | 1 (default)   | 4032 + 64  | 1.0 (default)   |

| 0x7C           | 0x00           | 1             | 1984 + 64  | 0.5             |

| 0xBC           | 0x00           | 1             | 3008 + 64  | 0.75            |

| 0x3C           | 0x00           | 1             | 960 + 64   | 0.25            |

| 0xFF           | 0xF0           | 0             | 4095 + 0   | ~1.0            |

| 0xFF           | 0xF0           | 1             | 4096 + 64  | 1.016           |

For any desired gain value, the GAIN registers can be calculated by the following:

$$\mathsf{GAIN} = \left(\mathsf{gain} - \mathsf{GAINADD} \times \left(\frac{1}{64}\right)\right) \times 4096$$

# Equation 5.3. Calculating the ADC0GNH and ADC0GNL Values from the Desired Gain

### Where:

*GAIN* is the 12-bit word of ADC0GNH[7:0] and ADC0GNL[7:4] *GAINADD* is the value of the GAINADD bit (ADC0GNA.0)

gain is the equivalent gain value from 0 to 1.016

When calculating the value of GAIN to load into the ADC0GNH and ADC0GNL registers, the GAINADD bit can be turned on or off to reach a value closer to the desired gain value.

For example, the initial example in this section requires a gain of 0.44 to convert 5 V full scale to 2.2 V full scale. Using Equation 5.3:

$$\mathsf{GAIN} = \left(0.44 - \mathsf{GAINADD} \times \left(\frac{1}{64}\right)\right) \times 4096$$

If GAINADD is set to 1, this makes the equation:

$$GAIN = \left(0.44 - 1 \times \left(\frac{1}{64}\right)\right) \times 4096 = 0.424 \times 4096 = 1738 = 0 \times 06CA$$

The actual gain from setting GAINADD to 1 and ADC0GNH and ADC0GNL to 0x6CA is 0.4399. A similar gain can be achieved if GAINADD is set to 0 with a different value for ADC0GNH and ADC0GNL.

#### 5.3.2. Setting the Gain Value

The three programmable gain registers are accessed indirectly using the ADC0H and ADC0L registers when the GAINEN bit (ADC0CF.0) bit is set. ADC0H acts as the address register, and ADC0L is the data register. The programmable gain registers can only be written to and cannot be read. See Gain Register Definition 5.1, Gain Register Definition 5.2, and Gain Register Definition 5.3 for more information.

The gain is programmed using the following steps:

- 1. Set the GAINEN bit (ADC0CF.0)

- 2. Load the ADC0H with the ADC0GNH, ADC0GNL, or ADC0GNA address.

- 3. Load ADC0L with the desired value for the selected gain register.

- 4. Reset the GAINEN bit (ADC0CF.0)

#### Notes:

- 1. An ADC conversion should not be performed while the GAINEN bit is set.

- 2. Even with gain enabled, the maximum input voltage must be less than V<sub>REGIN</sub> and the maximum voltage of the signal after gain must be less than or equal to V<sub>REF</sub>.

In code, changing the value to 0.44 gain from the previous example looks like:

| // in 'C':                                                             |                                                                                                                                                                                    |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC0CF  = 0x01;                                                        | // GAINEN = 1                                                                                                                                                                      |

| ADC0H = 0x04;                                                          | // Load the ADC0GNH address                                                                                                                                                        |

| ADC0L = 0x6C;                                                          | // Load the upper byte of 0x6CA to ADC0GNH                                                                                                                                         |

| ADC0H = 0x07;                                                          | // Load the ADC0GNL address                                                                                                                                                        |

| ADC0L = 0xA0;                                                          | // Load the lower nibble of 0x6CA to ADC0GNL                                                                                                                                       |

| ADC0H = 0x08;                                                          | // Load the ADC0GNA address                                                                                                                                                        |

| ADC0L = 0x01;                                                          | // Set the GAINADD bit                                                                                                                                                             |

| ADC0CF &= ~0x01;                                                       | // GAINEN = 0                                                                                                                                                                      |

|                                                                        |                                                                                                                                                                                    |

| ; in assembly                                                          |                                                                                                                                                                                    |

| ORL ADC0CF,#01H                                                        | ; GAINEN = 1                                                                                                                                                                       |

|                                                                        | , •                                                                                                                                                                                |

| MOV ADC0H,#04H                                                         | ; Load the ADC0GNH address                                                                                                                                                         |

| MOV ADC0H,#04H<br>MOV ADC0L,#06CH                                      | ,                                                                                                                                                                                  |

|                                                                        | ; Load the ADC0GNH address                                                                                                                                                         |

| MOV ADC0L,#06CH                                                        | ; Load the ADC0GNH address<br>; Load the upper byte of 0x6CA to ADC0GNH                                                                                                            |

| MOV ADC0L,#06CH<br>MOV ADC0H,#07H                                      | ; Load the ADC0GNH address<br>; Load the upper byte of 0x6CA to ADC0GNH<br>; Load the ADC0GNL address                                                                              |

| MOV ADC0L,#06CH<br>MOV ADC0H,#07H<br>MOV ADC0L,#0A0H                   | ; Load the ADC0GNH address<br>; Load the upper byte of 0x6CA to ADC0GNH<br>; Load the ADC0GNL address<br>; Load the lower nibble of 0x6CA to ADC0GNL                               |

| MOV ADC0L,#06CH<br>MOV ADC0H,#07H<br>MOV ADC0L,#0A0H<br>MOV ADC0H,#08H | ; Load the ADC0GNH address<br>; Load the upper byte of 0x6CA to ADC0GNH<br>; Load the ADC0GNL address<br>; Load the lower nibble of 0x6CA to ADC0GNL<br>; Load the ADC0GNA address |

# SFR Definition 5.7. ADC0CN: ADC0 Control

| Bit   | 7             | 6                                                                                                                                                                                                                                                                                                                                                          | 5                                                 | 4             | 3         | 2     |          | 1    | 0      |  |

|-------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|---------------|-----------|-------|----------|------|--------|--|

| Nam   | e AD0EN       | BURSTEN                                                                                                                                                                                                                                                                                                                                                    | AD0INT                                            | AD0BUSY       | ADOWINT   | AD0LJ | ST       | AD0C | M[1:0] |  |

| Туре  | e R/W         | R/W R/W R/W R/W R/W                                                                                                                                                                                                                                                                                                                                        |                                                   |               |           |       |          | /W   |        |  |

| Rese  | et 0          | 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                              |                                                   |               |           |       |          | 0    |        |  |

| SFR / | Address = 0xE | 8; SFR Page = 0x00; Bit-Addressable                                                                                                                                                                                                                                                                                                                        |                                                   |               |           |       |          |      |        |  |

| Bit   | Name          | Function                                                                                                                                                                                                                                                                                                                                                   |                                                   |               |           |       |          |      |        |  |

| 7     | AD0EN         | ADC0 Enab                                                                                                                                                                                                                                                                                                                                                  | le Bit.                                           |               |           |       |          |      |        |  |

|       |               | 0: ADC0 Dis<br>1: ADC0 Ena                                                                                                                                                                                                                                                                                                                                 |                                                   | •             |           |       | /ersions | 6.   |        |  |

| 6     | BURSTEN       | ADC0 Burst                                                                                                                                                                                                                                                                                                                                                 | Mode Ena                                          | ble Bit.      |           |       |          |      |        |  |

|       |               |                                                                                                                                                                                                                                                                                                                                                            | 0: Burst Mode Disabled.<br>1: Burst Mode Enabled. |               |           |       |          |      |        |  |

| 5     | AD0INT        | ADC0 Conv                                                                                                                                                                                                                                                                                                                                                  | ersion Con                                        | nplete Interr | upt Flag. |       |          |      |        |  |

|       |               | 0: ADC0 has not completed a data conversion since AD0INT was last cleared.<br>1: ADC0 has completed a data conversion.                                                                                                                                                                                                                                     |                                                   |               |           |       |          |      |        |  |

| 4     | AD0BUSY       | ADC0 Busy                                                                                                                                                                                                                                                                                                                                                  | Bit.                                              | Read:         |           |       | Write:   |      |        |  |

|       |               | 0: ADC0 conversion is not<br>in progress.0: No Effect.1: Initiates ADC0 Conv<br>sion if AD0CM[1:0] = 0<br>progress.                                                                                                                                                                                                                                        |                                                   |               |           |       |          |      |        |  |

| 3     | AD0WINT       | ADC0 Wind                                                                                                                                                                                                                                                                                                                                                  | ow Compa                                          | re Interrupt  | Flag.     |       |          |      |        |  |

|       |               | <ul> <li>This bit must be cleared by software</li> <li>0: ADC0 Window Comparison Data match has not occurred since this flag was last cleared.</li> <li>1: ADC0 Window Comparison Data match has occurred.</li> </ul>                                                                                                                                      |                                                   |               |           |       |          |      |        |  |

| 2     | AD0LJST       | ADC0 Left J                                                                                                                                                                                                                                                                                                                                                | ustify Sele                                       | ct Bit.       |           |       |          |      |        |  |

|       |               | 0: Data in ADC0H:ADC0L registers is right-justified<br>1: Data in ADC0H:ADC0L registers is left-justified. This option should not be used<br>with a repeat count greater than 1 (when AD0RPT[1:0] is 01b, 10b, or 11b).                                                                                                                                    |                                                   |               |           |       |          |      |        |  |

| 1:0   | AD0CM[1:0]    |                                                                                                                                                                                                                                                                                                                                                            |                                                   |               |           |       |          |      |        |  |

|       |               | <ul> <li>ADC0 Start of Conversion Mode Select.</li> <li>00: ADC0 start-of-conversion source is write of 1 to AD0BUSY.</li> <li>01: ADC0 start-of-conversion source is overflow of Timer 1.</li> <li>10: ADC0 start-of-conversion source is rising edge of external CNVSTR.</li> <li>11: ADC0 start-of-conversion source is overflow of Timer 2.</li> </ul> |                                                   |               |           |       |          |      |        |  |

# 10. CIP-51 Microcontroller

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. The CIP-51 also includes on-chip debug hardware (see description in Section 25), and interfaces directly with the analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 10.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 50 MIPS Peak Throughput with 50 MHz Clock

- 0 to 50 MHz Clock Frequency

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

# 10.1. Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute, and usually have a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

# Table 10.1. CIP-51 Instruction Set Summary

| Mnemonic              | Description                              | Bytes | Clock<br>Cycles |

|-----------------------|------------------------------------------|-------|-----------------|

| Arithmetic Operations |                                          |       | 1               |

| ADD A, Rn             | Add register to A                        | 1     | 1               |

| ADD A, direct         | Add direct byte to A                     | 2     | 2               |

| ADD A, @Ri            | Add indirect RAM to A                    | 1     | 2               |

| ADD A, #data          | Add immediate to A                       | 2     | 2               |

| ADDC A, Rn            | Add register to A with carry             | 1     | 1               |

| ADDC A, direct        | Add direct byte to A with carry          | 2     | 2               |

| ADDC A, @Ri           | Add indirect RAM to A with carry         | 1     | 2               |

| ADDC A, #data         | Add immediate to A with carry            | 2     | 2               |

| SUBB A, Rn            | Subtract register from A with borrow     | 1     | 1               |

| SUBB A, direct        | Subtract direct byte from A with borrow  | 2     | 2               |

| SUBB A, @Ri           | Subtract indirect RAM from A with borrow | 1     | 2               |

| SUBB A, #data         | Subtract immediate from A with borrow    | 2     | 2               |

| INC A                 | Increment A                              | 1     | 1               |

| INC Rn                | Increment register                       | 1     | 1               |

| INC direct            | Increment direct byte                    | 2     | 2               |

| INC @Ri               | Increment indirect RAM                   | 1     | 2               |

| DEC A                 | Decrement A                              | 1     | 1               |

| DEC Rn                | Decrement register                       | 1     | 1               |

| DEC direct            | Decrement direct byte                    | 2     | 2               |

| DEC @Ri               | Decrement indirect RAM                   | 1     | 2               |

| INC DPTR              | Increment Data Pointer                   | 1     | 1               |

| MUL AB                | Multiply A and B                         | 1     | 4               |

| DIV AB                | Divide A by B                            | 1     | 8               |

| DA A                  | Decimal adjust A                         | 1     | 1               |

| Logical Operations    | ,                                        |       |                 |

| ANL A, Rn             | AND Register to A                        | 1     | 1               |

| ANL A, direct         | AND direct byte to A                     | 2     | 2               |

| ANL A, @Ri            | AND indirect RAM to A                    | 1     | 2               |

| ANL A, #data          | AND immediate to A                       | 2     | 2               |

| ANL direct, A         | AND A to direct byte                     | 2     | 2               |

| ANL direct, #data     | AND immediate to direct byte             | 3     | 3               |

| ORL A, Rn             | OR Register to A                         | 1     | 1               |

| ORL A, direct         | OR direct byte to A                      | 2     | 2               |

| ORL A, @Ri            | OR indirect RAM to A                     | 1     | 2               |

| ORL A, #data          | OR immediate to A                        | 2     | 2               |

| ORL direct, A         | OR A to direct byte                      | 2     | 2               |

| ORL direct, #data     | OR immediate to direct byte              | 3     | 3               |

| XRL A, Rn             | Exclusive-OR Register to A               | 1     | 1               |

| XRL A, direct         | Exclusive-OR direct byte to A            | 2     | 2               |

| XRL A, @Ri            | Exclusive-OR indirect RAM to A           | 1     | 2               |

# SFR Definition 12.2. SFRPAGE: SFR Page

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|-----------------|---|---|---|---|---|---|--|

| Name  |   | SFRPAGE[7:0]    |   |   |   |   |   |   |  |

| Туре  |   | R/W             |   |   |   |   |   |   |  |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |

# SFR Address = 0xA7; SFR Page = All Pages

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SFRPAGE[7:0] | SFR Page Bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |              | Represents the SFR Page the C8051 core uses when reading or modifying SFRs.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |              | Write: Sets the SFR Page.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |              | Read: Byte is the SFR page the C8051 core is using.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |              | When enabled in the SFR Page Control Register (SFR0CN), the C8051 core will automatically switch to the SFR Page that contains the SFRs of the correspond-<br>ing peripheral/function that caused the interrupt, and return to the previous SFR page upon return from interrupt (unless SFR Stack was altered before a return-<br>ing from the interrupt). SFRPAGE is the top byte of the SFR Page Stack, and push/pop events of this stack are caused by interrupts (and not by reading/writ-<br>ing to the SFRPAGE register) |

# 13.3. External Interrupts INT0 and INT1

The INTO and INT1 external interrupt sources are configurable as active high or low, edge or level sensitive. The INOPL (INTO Polarity) and IN1PL (INT1 Polarity) bits in the IT01CF register select active high or active low; the IT0 and IT1 bits in TCON (Section "23.1. Timer 0 and Timer 1" on page 229) select level or edge sensitive. The table below lists the possible configurations.

| IT0 | IN0PL | INT0 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

| IT1 | IN1PL | INT1 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

INT0 and INT1 are assigned to Port pins as defined in the IT01CF register (see SFR Definition 13.7). Note that INT0 and INT0 Port pin assignments are independent of any Crossbar assignments. INT0 and INT1 will monitor their assigned Port pins without disturbing the peripheral that was assigned the Port pin via the Crossbar. To assign a Port pin only to INT0 and/or INT1, configure the Crossbar to skip the selected pin(s). This is accomplished by setting the associated bit in register XBR0 (see Section "18.3. Priority Crossbar Decoder" on page 150 for complete details on configuring the Crossbar).

IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flags for the INT0 and INT1 external interrupts, respectively. If an INT0 or INT1 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag remains logic 1 while the input is active as defined by the corresponding polarity bit (IN0PL or IN1PL); the flag remains logic 0 while the input is inactive. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

# 16.5. Comparator0 Reset

Comparator0 can be configured as a reset source by writing a 1 to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled and allowed to settle prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0–), the device is put into the reset state. After a Comparator0 reset, the CORSEF flag (RSTSRC.5) will read 1 signifying Comparator0 as the reset source; otherwise, this bit reads 0. The state of the RST pin is unaffected by this reset.

# 16.6. PCA Watchdog Timer Reset

The programmable Watchdog Timer (WDT) function of the Programmable Counter Array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in Section "24.4. Watchdog Timer Mode" on page 260; the WDT is enabled and clocked by SYSCLK/12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to 1. The state of the RST pin is unaffected by this reset.

### 16.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This may occur due to any of the following:

- A Flash write or erase is attempted above user code space. This occurs when PSWE is set to 1 and a MOVX write operation targets an address in or above the reserved space.

- A Flash read is attempted above user code space. This occurs when a MOVC operation targets an address in or above the reserved space.

- A Program read is attempted above user code space. This occurs when user code attempts to branch to an address in or above the reserved space.

- A Flash read, write or erase attempt is restricted due to a Flash security setting (see Section "14.3. Security Options" on page 119).

- A Flash read, write, or erase is attempted when the VDD Monitor is not enabled to the high threshold and set as a reset source.

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

### 16.8. Software Reset

Software may force a reset by writing a 1 to the SWRSF bit (RSTSRC.4). The SWRSF bit will read 1 following a software forced reset. The state of the RST pin is unaffected by this reset.

### 17.4.1. External Crystal Example

If a crystal or ceramic resonator is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 17.1, Option 1. The External Oscillator Frequency Control value (XFCN) should be chosen from the Crystal column of the table in SFR Definition 17.6 (OSCXCN register). For example, an 11.0592 MHz crystal requires an XFCN setting of 111b and a 32.768 kHz Watch Crystal requires an XFCN setting of 001b. After an external 32.768 kHz oscillator is stabilized, the XFCN setting can be switched to 000 to save power. It is recommended to enable the missing clock detector before switching the system clock to any external oscillator source.

When the crystal oscillator is first enabled, the oscillator amplitude detection circuit requires a settling time to achieve proper bias. Introducing a delay of 1 ms between enabling the oscillator and checking the XTLVLD bit will prevent a premature switch to the external oscillator as the system clock. Switching to the external oscillator before the crystal oscillator has stabilized can result in unpredictable behavior. The recommended procedure is: