Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), LINbus, SPI, UART/USART       |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 18                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 1.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                   |

| Data Converters            | A/D 18x12b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                             |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 24-WFQFN Exposed Pad                                           |

| Supplier Device Package    | 24-QFN (4x4)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f542-im |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 15. Power Management Modes                                              | 126 |

|-------------------------------------------------------------------------|-----|

| 15.1. Idle Mode                                                         | 126 |

| 15.2. Stop Mode                                                         |     |

| 15.3. Suspend Mode                                                      | 127 |

| 16. Reset Sources                                                       |     |

| 16.1. Power-On Reset                                                    |     |

| 16.2. Power-Fail Reset/VDD Monitor                                      |     |

| 16.3. External Reset                                                    |     |

| 16.4. Missing Clock Detector Reset                                      |     |

| 16.5. Comparator0 Reset                                                 |     |

| 16.6. PCA Watchdog Timer Reset                                          |     |

| 16.7. Flash Error Reset                                                 |     |

| 16.8. Software Reset                                                    |     |

| 17. Oscillators and Clock Selection                                     |     |

| 17.1. System Clock Selection                                            |     |

| 17.2. Programmable Internal Oscillator                                  |     |

| 17.3. Clock Multiplier                                                  |     |

| 17.4. External Oscillator Drive Circuit                                 |     |

| 18. Port Input/Output                                                   |     |

| 18.1. Port I/O Modes of Operation                                       |     |

| 18.2. Assigning Port I/O Pins to Analog and Digital Functions           |     |

| 18.3. Priority Crossbar Decoder                                         |     |

| 18.4. Port I/O Initialization                                           |     |

| 18.5. Port Match                                                        | -   |

| 18.6. Special Function Registers for Accessing and Configuring Port I/O |     |

| 19. Local Interconnect Network (LIN)                                    |     |

| 19.1. Software Interface with the LIN Controller                        |     |

| 19.2. LIN Interface Setup and Operation                                 |     |

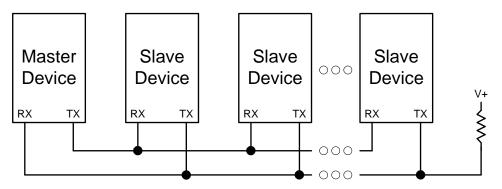

| 19.3. LIN Master Mode Operation                                         |     |

| 19.4. LIN Slave Mode Operation                                          |     |

| 19.5. Sleep Mode and Wake-Up                                            |     |

| 19.6. Error Detection and Handling                                      |     |

| 19.7. LIN Registers                                                     |     |

| 20. SMBus                                                               |     |

| 20.1. Supporting Documents                                              |     |

| 20.2. SMBus Configuration                                               |     |

| 20.3. SMBus Operation                                                   |     |

| 20.4. Using the SMBus                                                   | 190 |

| 20.5. SMBus Transfer Modes                                              |     |

| 20.6. SMBus Status Decoding                                             |     |

| 21. UART0                                                               |     |

| 21.1. Baud Rate Generator                                               |     |

| 21.2. Data Format                                                       |     |

| 21.3. Configuration and Operation                                       | 208 |

| 22. Enhanced Serial Peripheral Interface (SPI0)                         | 214 |

| Ordering Part Number | Flash Memory (kB) | LIN2.1       | Digital Port I/Os | Package |

|----------------------|-------------------|--------------|-------------------|---------|

| C8051F540-IQ         | 16                | $\checkmark$ | 25                | QFP32   |

| C8051F540-IM         | 16                | $\checkmark$ | 25                | QFN32   |

| C8051F541-IQ         | 16                | _            | 25                | QFP32   |

| C8051F541-IM         | 16                | _            | 25                | QFN32   |

| C8051F542-IM         | 16                | $\checkmark$ | 18                | QFN24   |

| C8051F543-IM         | 16                | _            | 18                | QFN24   |

| C8051F544-IQ         | 8                 | $\checkmark$ | 25                | QFP32   |

| C8051F544-IM         | 8                 | $\checkmark$ | 25                | QFN32   |

| C8051F545-IQ         | 8                 |              | 25                | QFP32   |

| C8051F545-IM         | 8                 | _            | 25                | QFN32   |

| C8051F546-IM         | 8                 | $\checkmark$ | 18                | QFN24   |

| C8051F547-IM         | 8                 | _            | 18                | QFN24   |

#### Table 2.1. Product Selection Guide

Note: The suffix of the part number indicates the device rating and the package. All devices are RoHS compliant.

All of these devices are also available in an automotive version. For the automotive version, the -I in the ordering part number is replaced with -A. For example, the automotive version of the C8051F540-IM is the C8051F540-AM.

The -AM and -AQ devices receive full automotive quality production status, including AEC-Q100 qualification, registration with International Material Data System (IMDS) and Part Production Approval Process (PPAP) documentation. PPAP documentation is available at www.silabs.com with a registered and NDA approved user account. The -AM and -AQ devices enable high volume automotive OEM applications with their enhanced testing and processing. Please contact Silicon Labs sales for more information regarding –AM and -AQ devices for your automotive project.

## Gain Register Definition 5.1. ADC0GNH: ADC0 Selectable Gain High Byte

| Bit    | 7                                                                                                    | 6                                                                         | 5          | 4 | 3        | 2 | 1 | 0 |  |  |

|--------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------|---|----------|---|---|---|--|--|

| Nam    | е                                                                                                    | GAINH[7:0]                                                                |            |   |          |   |   |   |  |  |

| Тур    | e                                                                                                    | W                                                                         |            |   |          |   |   |   |  |  |

| Rese   | et 1                                                                                                 | 1                                                                         | 1          | 1 | 1        | 1 | 0 | 0 |  |  |

| Indire | ct Address = (                                                                                       | 0x04;                                                                     |            |   |          |   |   |   |  |  |

| Bit    | Name                                                                                                 |                                                                           |            |   | Function |   |   |   |  |  |

| 7:0    | GAINH[7:0]                                                                                           | ADC0 Gain                                                                 | High Byte. |   |          |   |   |   |  |  |

|        |                                                                                                      | See Section 5.3.1 for details on calculating the value for this register. |            |   |          |   |   |   |  |  |

| Note:  | Note: This register is accessed indirectly; See Section 5.3.2 for details for writing this register. |                                                                           |            |   |          |   |   |   |  |  |

## Gain Register Definition 5.2. ADC0GNL: ADC0 Selectable Gain Low Byte

| Bit   | 7 | 6    | 5      | 4 | 3        | 2        | 1        | 0        |

|-------|---|------|--------|---|----------|----------|----------|----------|

| Name  |   | GAIN | L[3:0] |   | Reserved | Reserved | Reserved | Reserved |

| Туре  |   | V    | V      |   | W        | W        | W        | W        |

| Reset | 0 | 0    | 0      | 0 | 0        | 0        | 0        | 0        |

Indirect Address = 0x07;

| Bit   | Name                                                                                             | Function                                                                        |  |  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7:4   | GAINL[3:0]                                                                                       | ADC0 Gain Lower 4 Bits.                                                         |  |  |  |  |  |  |  |

|       |                                                                                                  | See Figure 5.3.1 for details for setting this register.                         |  |  |  |  |  |  |  |

|       |                                                                                                  | This register is only accessed indirectly through the ADC0H and ADC0L register. |  |  |  |  |  |  |  |

| 3:0   | Reserved                                                                                         | Must Write 0000b                                                                |  |  |  |  |  |  |  |

| Note: | : This register is accessed indirectly; See Section 5.3.2 for details for writing this register. |                                                                                 |  |  |  |  |  |  |  |

# C8051F54x

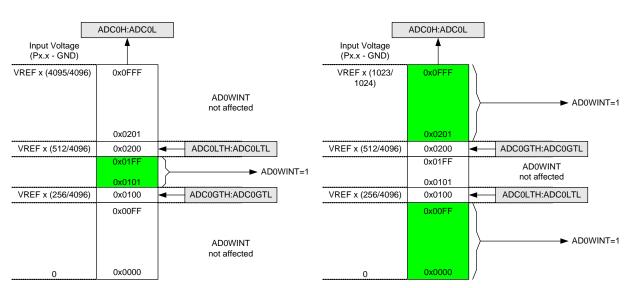

Figure 5.6. ADC Window Compare Example: Right-Justified Data

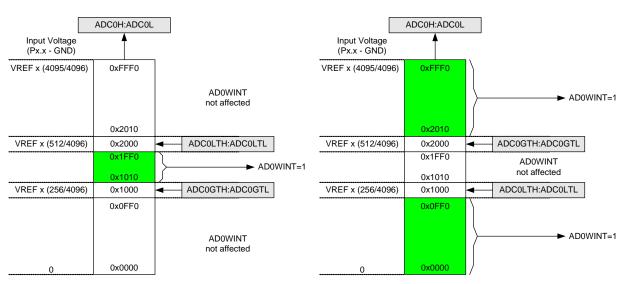

Figure 5.7. ADC Window Compare Example: Left-Justified Data

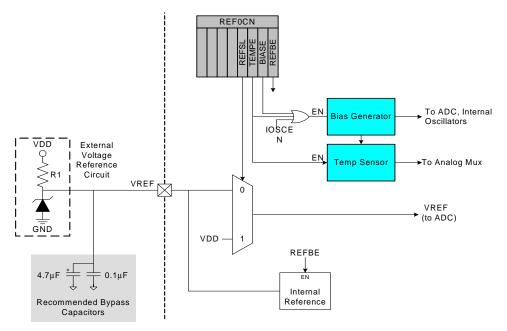

# 7. Voltage Reference

The Voltage reference multiplexer on the C8051F54x devices is configurable to use an externally connected voltage reference, the on-chip reference voltage generator routed to the VREF pin, or the V<sub>DD</sub> power supply voltage (see Figure 7.1). The REFSL bit in the Reference Control register (REF0CN, SFR Definition 7.1) selects the reference source for the ADC. For an external source or the on-chip reference, REFSL should be set to 0 to select the VREF pin. To use V<sub>DD</sub> as the reference source, REFSL should be set to 1.

The BIASE bit enables the internal voltage bias generator, which is used by the ADC, Temperature Sensor, and internal oscillator. This bias is automatically enabled when any peripheral which requires it is enabled, and it does not need to be enabled manually. The bias generator may be enabled manually by writing a 1 to the BIASE bit in register REFOCN. The electrical specifications for the voltage reference circuit are given in Table 6.11.

The on-chip voltage reference circuit consists of a temperature stable bandgap voltage reference generator and a gain-of-two output buffer amplifier. The output voltage is selectable between 1.5 V and 2.25 V. The on-chip voltage reference can be driven on the VREF pin by setting the REFBE bit in register REF0CN to a 1. The maximum load seen by the VREF pin must be less than 200  $\mu$ A to GND. Bypass capacitors of 0.1  $\mu$ F and 4.7  $\mu$ F are recommended from the VREF pin to GND. If the on-chip reference is not used, the REFBE bit should be cleared to 0. Electrical specifications for the on-chip voltage reference are given in Table 6.11.

**Important Note about the VREF Pin:** When using either an external voltage reference or the on-chip reference circuitry, the VREF pin should be configured as an analog pin and skipped by the Digital Crossbar. Refer to Section "18. Port Input/Output" on page 147 for the location of the VREF pin, as well as details of how to configure the pin in analog mode and to be skipped by the crossbar.

Figure 7.1. Voltage Reference Functional Block Diagram

# SFR Definition 8.5. CPT0MX: Comparator0 MUX Selection

| Bit   | 7             | 6                   | 5           | 4            | 3            | 2            | 1      | 0 |  |  |

|-------|---------------|---------------------|-------------|--------------|--------------|--------------|--------|---|--|--|

| Nam   | e             | CMX0                | N[3:0]      | 1            |              | CMX0         | P[3:0] |   |  |  |

| Туре  | 9             | R/                  | W           |              |              | R/           | W      |   |  |  |

| Rese  | et 0          | 1                   | 1           | 1            | 0            | 1            | 1      | 1 |  |  |

| SFR / | Address = 0x9 | 9C; SFR Page = 0x00 |             |              |              |              |        |   |  |  |

| Bit   | Name          |                     |             |              | Function     |              |        |   |  |  |

| 7:4   | CMX0N[3:0]    | Comparato           | -           | -            | Selection.   |              |        |   |  |  |

|       |               | 0000:               | P0.         |              |              |              |        |   |  |  |

|       |               | 0001:               | P0.         | 3            |              |              |        |   |  |  |

|       |               | 0010:               | P0.         | 5            |              |              |        |   |  |  |

|       |               | 0011:               | P0.         | 7            |              |              |        |   |  |  |

|       |               | 0100:               | P1.         | 1            |              |              |        |   |  |  |

|       |               | 0101:               | P1.         | 3            |              |              |        |   |  |  |

|       |               | 0110:               | P1.         | 5            |              |              |        |   |  |  |

|       |               | 0111:               | P1.         | 7            |              |              |        |   |  |  |

|       |               | 1000:               | P2.         | 1            |              |              |        |   |  |  |

|       |               | 1001:               | P2.         | 3 (only avai | able on 32-p | oin devices) |        |   |  |  |

|       |               | 1010:               | P2.         | 5 (only avai | able on 32-p | oin devices) |        |   |  |  |

|       |               | 1011:               | P2.         | 7 (only avai | able on 32-p | oin devices) |        |   |  |  |

|       |               | 1100–1111:          | Noi         | ne           |              |              |        |   |  |  |

| 3:0   | CMX0P[3:0]    | Comparato           | r0 Positive | Input MUX    | Selection.   |              |        |   |  |  |

|       |               | 0000:               | P0.         | 0            |              |              |        |   |  |  |

|       |               | 0001:               | P0.         | 2            |              |              |        |   |  |  |

|       |               | 0010:               | P0.         | 4            |              |              |        |   |  |  |

|       |               | 0011:               | P0.         | 6            |              |              |        |   |  |  |

|       |               | 0100:               | P1.         | 0            |              |              |        |   |  |  |

|       |               | 0101:               | P1.         | 2            |              |              |        |   |  |  |

|       |               | 0110:               | P1.         | 4            |              |              |        |   |  |  |

|       |               | 0111:               | P1.         | 6            |              |              |        |   |  |  |

|       |               | 1000:               | P2.         | 0            |              |              |        |   |  |  |

|       |               | 1001:               | P2.         | 2 (only avai | able on 32-p | oin devices) |        |   |  |  |

|       |               | 1010:               | P2.         | 4 (only avai | able on 32-p | in devices)  |        |   |  |  |

|       |               | 1011:               | P2.         | 6 (only avai | able on 32-p | in devices)  |        |   |  |  |

|       |               | 1100–1111:          | Noi         | ne           |              |              |        |   |  |  |

# 10. CIP-51 Microcontroller

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. The CIP-51 also includes on-chip debug hardware (see description in Section 25), and interfaces directly with the analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 10.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 50 MIPS Peak Throughput with 50 MHz Clock

- 0 to 50 MHz Clock Frequency

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

## 10.1. Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute, and usually have a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

#### 10.2. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>™</sup> instruction set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>™</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

#### 10.2.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 10.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

# Table 10.1. CIP-51 Instruction Set Summary (Continued)

| Mnemonic             | Description                                         | Bytes | Clock<br>Cycles |  |  |

|----------------------|-----------------------------------------------------|-------|-----------------|--|--|

| SETB C               | Set Carry                                           | 1     | 1               |  |  |

| SETB bit             | Set direct bit                                      | 2     | 2               |  |  |

| CPL C                | PL C Complement Carry                               |       |                 |  |  |

| CPL bit              | Complement direct bit                               | 2     | 2               |  |  |

| ANL C, bit           | AND direct bit to Carry                             | 2     | 2               |  |  |

| ANL C, /bit          | AND complement of direct bit to Carry               | 2     | 2               |  |  |

| ORL C, bit           | OR direct bit to carry                              | 2     | 2               |  |  |

| ORL C, /bit          | OR complement of direct bit to Carry                | 2     | 2               |  |  |

| MOV C, bit           | Move direct bit to Carry                            | 2     | 2               |  |  |

| MOV bit, C           | Move Carry to direct bit                            | 2     | 2               |  |  |

| JC rel               | Jump if Carry is set                                | 2     | 2/3*            |  |  |

| JNC rel              | Jump if Carry is not set                            | 2     | 2/3*            |  |  |

| JB bit, rel          | Jump if direct bit is set                           | 3     | 3/4*            |  |  |

| JNB bit, rel         | Jump if direct bit is not set                       | 3     | 3/4*            |  |  |

| JBC bit, rel         | Jump if direct bit is set and clear bit             | 3     | 3/4*            |  |  |

| Program Branching    |                                                     |       |                 |  |  |

| ACALL addr11         | Absolute subroutine call                            | 2     | 3*              |  |  |

| LCALL addr16         | Long subroutine call                                | 3     | 4*              |  |  |

| RET                  | Return from subroutine                              | 1     | 5*              |  |  |

| RETI                 | Return from interrupt                               | 1     | 5*              |  |  |

| AJMP addr11          | Absolute jump                                       | 2     | 3*              |  |  |

| LJMP addr16          | Long jump                                           | 3     | 4*              |  |  |

| SJMP rel             | Short jump (relative address)                       | 2     | 3*              |  |  |

| JMP @A+DPTR          | Jump indirect relative to DPTR                      | 1     | 3*              |  |  |

| JZ rel               | Jump if A equals zero                               | 2     | 2/3*            |  |  |

| JNZ rel              | Jump if A does not equal zero                       | 2     | 2/3             |  |  |

| CJNE A, direct, rel  | Compare direct byte to A and jump if not equal      | 3     | 4/5*            |  |  |

| CJNE A, #data, rel   | Compare immediate to A and jump if not equal        | 3     | 3/4*            |  |  |

| CJNE Rn, #data, rel  | Compare immediate to Register and jump if not equal | 3     | 3/4*            |  |  |

| CJNE @Ri, #data, rel | Compare immediate to indirect and jump if not equal | 3     | 4/5*            |  |  |

| DJNZ Rn, rel         | Decrement Register and jump if not zero             | 2     | 2/3*            |  |  |

| DJNZ direct, rel     | Decrement direct byte and jump if not zero          | 3     | 3/4*            |  |  |

| NOP                  | No operation                                        | 1     | 1               |  |  |

## Table 12.2. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register | Address | Description                     | Page |

|----------|---------|---------------------------------|------|

| SN0      | 0xF9    | Serial Number 0                 | 84   |

| SN1      | 0xFA    | Serial Number 1                 | 84   |

| SN2      | 0xFB    | Serial Number 2                 | 84   |

| SN3      | 0xFC    | Serial Number 3                 | 84   |

| SP       | 0x81    | Stack Pointer                   | 82   |

| SPI0CFG  | 0xA1    | SPI0 Configuration              | 221  |

| SPIOCKR  | 0xA2    | SPI0 Clock Rate Control         | 223  |

| SPI0CN   | 0xF8    | SPI0 Control                    | 222  |

| SPIODAT  | 0xA3    | SPI0 Data                       | 223  |

| TCON     | 0x88    | Timer/Counter Control           | 233  |

| TH0      | 0x8C    | Timer/Counter 0 High            | 236  |

| TH1      | 0x8D    | Timer/Counter 1 High            | 236  |

| TL0      | 0x8A    | Timer/Counter 0 Low             | 235  |

| TL1      | 0x8B    | Timer/Counter 1 Low             | 235  |

| TMOD     | 0x89    | Timer/Counter Mode              | 234  |

| TMR2CN   | 0xC8    | Timer/Counter 2 Control         | 240  |

| TMR2H    | 0xCD    | Timer/Counter 2 High            | 242  |

| TMR2L    | 0xCC    | Timer/Counter 2 Low             | 242  |

| TMR2RLH  | 0xCB    | Timer/Counter 2 Reload High     | 241  |

| TMR2RLL  | 0xCA    | Timer/Counter 2 Reload Low      | 241  |

| TMR3CN   | 0x91    | Timer/Counter 3 Control         | 246  |

| TMR3H    | 0x95    | Timer/Counter 3 High            | 248  |

| TMR3L    | 0x94    | Timer/Counter 3 Low             | 248  |

| TMR3RLH  | 0x93    | Timer/Counter 3 Reload High     | 247  |

| TMR3RLL  | 0x92    | Timer/Counter 3 Reload Low      | 247  |

| VDM0CN   | 0xFF    | V <sub>DD</sub> Monitor Control | 132  |

| XBR0     | 0xE1    | Port I/O Crossbar Control 0     | 154  |

| XBR1     | 0xE2    | Port I/O Crossbar Control 1     | 155  |

| XBR2     | 0xC7    | Port I/O Crossbar Control 2     | 156  |

## SFR Definition 13.1. IE: Interrupt Enable

| Bit   | 7   | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-------|-----|-----|-----|-----|-----|-----|

| Name  | EA  | ESPI0 | ET2 | ES0 | ET1 | EX1 | ET0 | EX0 |

| Туре  | R/W | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Address = 0xA8; Bit-Addressable; SFR Page = All Pages

| Bit | Name  | Function                                                                                                                                                                                                                                                              |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EA    | <ul> <li>Enable All Interrupts.</li> <li>Globally enables/disables all interrupts. It overrides individual interrupt mask settings.</li> <li>0: Disable all interrupt sources.</li> <li>1: Enable each interrupt according to its individual mask setting.</li> </ul> |

| 6   | ESPI0 | <ul> <li>Enable Serial Peripheral Interface (SPI0) Interrupt.</li> <li>This bit sets the masking of the SPI0 interrupts.</li> <li>0: Disable all SPI0 interrupts.</li> <li>1: Enable interrupt requests generated by SPI0.</li> </ul>                                 |

| 5   | ET2   | <ul> <li>Enable Timer 2 Interrupt.</li> <li>This bit sets the masking of the Timer 2 interrupt.</li> <li>0: Disable Timer 2 interrupt.</li> <li>1: Enable interrupt requests generated by the TF2L or TF2H flags.</li> </ul>                                          |

| 4   | ES0   | Enable UART0 Interrupt.<br>This bit sets the masking of the UART0 interrupt.<br>0: Disable UART0 interrupt.<br>1: Enable UART0 interrupt.                                                                                                                             |

| 3   | ET1   | <ul> <li>Enable Timer 1 Interrupt.</li> <li>This bit sets the masking of the Timer 1 interrupt.</li> <li>0: Disable all Timer 1 interrupt.</li> <li>1: Enable interrupt requests generated by the TF1 flag.</li> </ul>                                                |

| 2   | EX1   | <ul> <li>Enable External Interrupt 1.</li> <li>This bit sets the masking of External Interrupt 1.</li> <li>0: Disable external interrupt 1.</li> <li>1: Enable interrupt requests generated by the INT1 input.</li> </ul>                                             |

| 1   | ET0   | <ul> <li>Enable Timer 0 Interrupt.</li> <li>This bit sets the masking of the Timer 0 interrupt.</li> <li>0: Disable all Timer 0 interrupt.</li> <li>1: Enable interrupt requests generated by the TF0 flag.</li> </ul>                                                |

| 0   | EX0   | <ul> <li>Enable External Interrupt 0.</li> <li>This bit sets the masking of External Interrupt 0.</li> <li>0: Disable external interrupt 0.</li> <li>1: Enable interrupt requests generated by the INTO input.</li> </ul>                                             |

# 14. Flash Memory

On-chip, re-programmable Flash memory is included for program code and non-volatile data storage. The Flash memory can be programmed in-system, a single byte at a time, through the C2 interface or by software using the MOVX instruction. Once cleared to logic 0, a Flash bit must be erased to set it back to logic 1. Flash bytes would typically be erased (set to 0xFF) before being reprogrammed. The write and erase operations are automatically timed by hardware for proper execution; data polling to determine the end of the write/erase operation is not required. Code execution is stalled during a Flash write/erase operation. Refer to Table 6.5 for complete Flash memory electrical characteristics.

## 14.1. Programming the Flash Memory

The simplest means of programming the Flash memory is through the C2 interface using programming tools provided by Silicon Labs or a third party vendor. This is the only means for programming a non-initialized device. For details on the C2 commands to program Flash memory, see Section "25. C2 Interface" on page 269.

To ensure the integrity of Flash contents, it is strongly recommended that the on-chip  $V_{DD}$  Monitor be enabled in any system that includes code that writes and/or erases Flash memory from software. See Section 14.4 for more details. Before performing any Flash write or erase procedure, set the FLEWT bit in Flash Scale register (FLSCL) to '1'. Also, note that 8-bit MOVX instructions cannot be used to erase or write to Flash memory at addresses higher than 0x00FF

#### 14.1.1. Flash Lock and Key Functions

Flash writes and erases by user software are protected with a lock and key function. The Flash Lock and Key Register (FLKEY) must be written with the correct key codes, in sequence, before Flash operations may be performed. The key codes are: 0xA5, 0xF1. The timing does not matter, but the codes must be written in order. If the key codes are written out of order, or the wrong codes are written, Flash writes and erases will be disabled until the next system reset. Flash writes and erases will also be disabled if a Flash write or erase is attempted before the key codes have been written properly. The Flash lock resets after each write or erase; the key codes must be written again before a following Flash operation can be performed. The FLKEY register is detailed in SFR Definition 14.2.

#### 14.1.2. Flash Erase Procedure

The Flash memory can be programmed by software using the MOVX write instruction with the address and data byte to be programmed provided as normal operands. Before writing to Flash memory using MOVX, Flash write operations must be enabled by doing the following: (1) setting the PSWE Program Store Write Enable bit (PSCTL.0) to logic 1 (this directs the MOVX writes to target Flash memory); and (2) Writing the Flash key codes in sequence to the Flash Lock register (FLKEY). The PSWE bit remains set until cleared by software.

A write to Flash memory can clear bits to logic 0 but cannot set them; only an erase operation can set bits to logic 1 in Flash. **A byte location to be programmed should be erased before a new value is written.** The Flash memory is organized in 512-byte pages. The erase operation applies to an entire page (setting all bytes in the page to 0xFF). To erase an entire 512-byte page, perform the following steps:

- 1. Disable interrupts (recommended).

- 2. Set the PSEE bit (register PSCTL).

- 3. Set the PSWE bit (register PSCTL).

- 4. Write the first key code to FLKEY: 0xA5.

- 5. Write the second key code to FLKEY: 0xF1.

- 6. Using the MOVX instruction, write a data byte to any location within the 512-byte page to be erased.

- 7. Clear the PSWE and PSEE bits.

## SFR Definition 17.2. OSCICN: Internal Oscillator Control

| Bit   | 7     | 6       | 5       | 4     | 3        | 2         | 1 | 0 |

|-------|-------|---------|---------|-------|----------|-----------|---|---|

| Name  | IOSCE | EN[1:0] | SUSPEND | IFRDY | Reserved | IFCN[2:0] |   |   |

| Туре  | R/W   | R/W     | R/W     | R     | R        | R/W       |   |   |

| Reset | 1     | 1       | 0       | 1     | 0        | 0         | 0 | 0 |

#### SFR Address = 0xA1; SFR Page = 0x0F;

| Bit | Name        | Function                                                                                                                                                                            |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | IOSCEN[1:0] | Internal Oscillator Enable Bits.                                                                                                                                                    |

|     |             | 00: Oscillator Disabled.                                                                                                                                                            |

|     |             | 01: Reserved.                                                                                                                                                                       |

|     |             | 10: Reserved.                                                                                                                                                                       |

|     |             | 11: Oscillator enabled in normal mode and disabled in suspend mode.                                                                                                                 |

| 5   | SUSPEND     | Internal Oscillator Suspend Enable Bit.                                                                                                                                             |

|     |             | Setting this bit to logic 1 places the internal oscillator in SUSPEND mode. The inter-<br>nal oscillator resumes operation when one of the SUSPEND mode awakening<br>events occurs. |

| 4   | IFRDY       | Internal Oscillator Frequency Ready Flag.                                                                                                                                           |

|     |             | 0: Internal oscillator is not running at programmed frequency.                                                                                                                      |

|     |             | 1: Internal oscillator is running at programmed frequency.                                                                                                                          |

| 3   | Reserved    | Read = 0b; Write = 0b.                                                                                                                                                              |

| 2:0 | IFCN[2:0]   | Internal Oscillator Frequency Divider Control Bits.                                                                                                                                 |

|     |             | 000: SYSCLK derived from Internal Oscillator divided by 128.                                                                                                                        |

|     |             | 001: SYSCLK derived from Internal Oscillator divided by 64.                                                                                                                         |

|     |             | 010: SYSCLK derived from Internal Oscillator divided by 32.                                                                                                                         |

|     |             | 011: SYSCLK derived from Internal Oscillator divided by 16.                                                                                                                         |

|     |             | 100: SYSCLK derived from Internal Oscillator divided by 8.                                                                                                                          |

|     |             | 101: SYSCLK derived from Internal Oscillator divided by 4.                                                                                                                          |

|     |             | 110: SYSCLK derived from Internal Oscillator divided by 2.                                                                                                                          |

|     |             | 111: SYSCLK derived from Internal Oscillator divided by 1.                                                                                                                          |

# SFR Definition 17.5. CLKMUL: Clock Multiplier

| Bit   | 7     | 6       | 5      | 4 | 3           | 2           | 1 | 0 |

|-------|-------|---------|--------|---|-------------|-------------|---|---|

| Name  | MULEN | MULINIT | MULRDY |   | MULDIV[2:0] | MULSEL[1:0] |   |   |

| Туре  | R/W   | R/W     | R      |   | R/W         | R/W         |   |   |

| Reset | 0     | 0       | 0      | 0 | 0           | 0           | 0 | 0 |

#### SFR Address = 0x97; SFR Page = 0x0F;

| Bit   | Name        |                                                | Function                                                                                                                                                                                        |                                                                           |  |  |  |  |  |  |  |

|-------|-------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7     | MULEN       | Clock Multiplie                                |                                                                                                                                                                                                 |                                                                           |  |  |  |  |  |  |  |

|       |             |                                                | 0: Clock Multiplier disabled.                                                                                                                                                                   |                                                                           |  |  |  |  |  |  |  |

|       |             | •                                              | 1: Clock Multiplier enabled.                                                                                                                                                                    |                                                                           |  |  |  |  |  |  |  |

| 6     | MULINIT     | -                                              | Clock Multiplier Initialize.                                                                                                                                                                    |                                                                           |  |  |  |  |  |  |  |

|       |             | bit will initialize                            | This bit is 0 when the Clock Multiplier is enabled. Once enabled, writing a 1 to this bit will initialize the Clock Multiplier. The MULRDY bit reads 1 when the Clock Multiplier is stabilized. |                                                                           |  |  |  |  |  |  |  |

| 5     | MULRDY      | <b>Clock Multiplie</b>                         | r Ready.                                                                                                                                                                                        |                                                                           |  |  |  |  |  |  |  |

|       |             | 0: Clock Multipli                              | -                                                                                                                                                                                               |                                                                           |  |  |  |  |  |  |  |

|       |             | 1: Clock Multipli                              | er is ready (PLL is locked).                                                                                                                                                                    |                                                                           |  |  |  |  |  |  |  |

| 4:2   | MULDIV[2:0] |                                                | r Output Scaling Factor.                                                                                                                                                                        |                                                                           |  |  |  |  |  |  |  |

|       |             |                                                | iplier Output scaled by a factor o                                                                                                                                                              |                                                                           |  |  |  |  |  |  |  |

|       |             |                                                | iplier Output scaled by a factor o                                                                                                                                                              |                                                                           |  |  |  |  |  |  |  |

|       |             |                                                | iplier Output scaled by a factor o                                                                                                                                                              |                                                                           |  |  |  |  |  |  |  |

|       |             |                                                | plier Output scaled by a factor o<br>iplier Output scaled by a factor o                                                                                                                         |                                                                           |  |  |  |  |  |  |  |

|       |             |                                                | iplier Output scaled by a factor o                                                                                                                                                              | . ,                                                                       |  |  |  |  |  |  |  |

|       |             |                                                | plier Output scaled by a factor of                                                                                                                                                              |                                                                           |  |  |  |  |  |  |  |

|       |             |                                                | plier Output scaled by a factor of                                                                                                                                                              |                                                                           |  |  |  |  |  |  |  |

|       |             | *Note: The Cloc                                | ck Multiplier output duty cycle is i                                                                                                                                                            | not 50% for these settings.                                               |  |  |  |  |  |  |  |

| 1:0   | MULSEL[1:0] | Clock Multiplie                                | r Input Select.                                                                                                                                                                                 |                                                                           |  |  |  |  |  |  |  |

|       |             | These bits select                              | ct the clock supplied to the Clock                                                                                                                                                              | Multiplier                                                                |  |  |  |  |  |  |  |

|       |             | MULSEL[1:0]                                    | Selected Input Clock                                                                                                                                                                            | Clock Multiplier Output<br>for MULDIV[2:0] = 000b                         |  |  |  |  |  |  |  |

|       |             | 00                                             | Internal Oscillator                                                                                                                                                                             | Internal Oscillator x 2                                                   |  |  |  |  |  |  |  |

|       |             | 01                                             | External Oscillator                                                                                                                                                                             | External Oscillator x 2                                                   |  |  |  |  |  |  |  |

|       |             | 10                                             | 10 Internal Oscillator Internal Oscillator x 4                                                                                                                                                  |                                                                           |  |  |  |  |  |  |  |

|       |             | 11 External Oscillator External Oscillator x 4 |                                                                                                                                                                                                 |                                                                           |  |  |  |  |  |  |  |

| Notes |             |                                                | IHz, and so the Clock Multiplier outp<br>Oscillator x 2 is selected using the N                                                                                                                 | but should be scaled accordingly.<br>MULSEL bits, MULDIV[2:0] is ignored. |  |  |  |  |  |  |  |

| Port                           |      |        |         | P                 | 0                 |                  |   |   |   |   |                 | P                | 1    |                  |      |           |       |        |                 | P                | 2         |                  |   |   | P3                   |

|--------------------------------|------|--------|---------|-------------------|-------------------|------------------|---|---|---|---|-----------------|------------------|------|------------------|------|-----------|-------|--------|-----------------|------------------|-----------|------------------|---|---|----------------------|

| Special<br>Function<br>Signals | VREF | CNVSTR | XTAL1   | XTAL2             |                   |                  |   |   |   |   |                 |                  |      | ALE              | /RD  | <b>MR</b> |       |        | Pź              | 2.2-1            |           |                  |   |   | available on<br>ages |

| PIN I/O                        | 0    | 1      | 2       | 3                 | 4                 | 5                | 6 | 7 | 0 | 1 | 2               | 3                | 4    | 5                | 6    | 7         | 0     | 1      | 2               | 3                | 4         | 5                | 6 | 7 | 0                    |

| UART_TX                        |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

| UART_RX                        |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

| SCK                            |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

| MISO                           |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

| MOSI                           |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

| NSS                            |      |        |         |                   |                   |                  |   |   |   |   |                 | *NS              | S Is | s onl            | y pi | nneo      | d out | t in 4 | 1-wir           | e S              | PIN       | lode             |   |   |                      |

| SDA                            |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

| SCL                            |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

| CP0                            |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

| CP0A                           |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

| CP1                            |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

| CP1A                           |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

| SYSCLK                         |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

| CEX0                           |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

| CEX1                           |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

| CEX2                           |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

| CEX3                           |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

| CEX4                           |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

| CEX5                           |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

| ECI                            |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

| то                             |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      | İ                |      |           |       |        |                 |                  |           |                  |   |   |                      |

| T1                             |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

| LIN_TX                         |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

| LIN_RX                         |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |      |           |       |        |                 |                  |           |                  |   |   |                      |

|                                | 0    | 1      | 1<br>P( | 0<br>0 <b>5</b> K | 0<br>I <b>P[0</b> | 1<br>: <b>7]</b> | 0 | 0 | 0 | 0 | 0<br><b>P</b> 1 | 0<br>I <b>SK</b> |      | 0<br>: <b>7]</b> | 0    | 0         | 0     | 0      | 0<br><b>P</b> 2 | 0<br>2 <b>SK</b> | 0<br>IP[0 | 0<br>: <b>7]</b> | 0 | 0 | 0<br>P3SKIP[0]       |

Figure 18.4. Crossbar Priority Decoder in Example Configuration

## 18.4. Port I/O Initialization

Port I/O initialization consists of the following steps:

- 1. Select the input mode (analog or digital) for all Port pins, using the Port Input Mode register (PnMDIN).

- 2. Select the output mode (open-drain or push-pull) for all Port pins, using the Port Output Mode register (PnMDOUT).

- 3. Select any pins to be skipped by the I/O Crossbar using the Port Skip registers (PnSKIP).

- 4. Assign Port pins to desired peripherals.

- 5. Enable the Crossbar (XBARE = 1).

All Port pins must be configured as either analog or digital inputs. Any pins to be used as Comparator or ADC inputs should be configured as an analog inputs. When a pin is configured as an analog input, its weak pullup, digital driver, and digital receiver are disabled. This process saves power and reduces noise on the analog input. Pins configured as digital inputs may still be used by analog peripherals; however this practice is not recommended.

Additionally, all analog input pins should be configured to be skipped by the Crossbar (accomplished by setting the associated bits in PnSKIP). Port input mode is set in the PnMDIN register, where a 1 indicates a digital input, and a 0 indicates an analog input. All pins default to digital inputs on reset. See SFR Definition 18.13 for the PnMDIN register details.

## SFR Definition 18.8. P2MASK: Port 2 Mask Register

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|-------------|---|---|---|---|---|---|---|--|--|

| Name  | P2MASK[7:0] |   |   |   |   |   |   |   |  |  |

| Туре  | R/W         |   |   |   |   |   |   |   |  |  |

| Reset | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

SFR Address = 0xB2; SFR Page = 0x00

| Bit   | Name                                                  | Function                                                                                                                                                                                            |  |  |  |  |  |  |  |

|-------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7:0   | P2MASK[7:0]                                           | Port 2 Mask Value.                                                                                                                                                                                  |  |  |  |  |  |  |  |

|       |                                                       | Selects P2 pins to be compared to the corresponding bits in P2MAT.<br>0: P2.n pin logic value is ignored and cannot cause a Port Mismatch event.<br>1: P2.n pin logic value is compared to P2MAT.n. |  |  |  |  |  |  |  |

| Note: | te: Ports 2.2-P2.7 only available on 32-pin packages. |                                                                                                                                                                                                     |  |  |  |  |  |  |  |

## SFR Definition 18.9. P2MAT: Port 2 Match Register

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------------|---|---|---|---|---|---|---|--|--|

| Name  | P2MAT[7:0] |   |   |   |   |   |   |   |  |  |

| Туре  | R/W        |   |   |   |   |   |   |   |  |  |

| Reset | 1          | 1 | 1 | 1 | 1 | 1 | 1 | 1 |  |  |

SFR Address = 0xB1; SFR Page = 0x00

| Bit   | Name              | Function                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

|-------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 7:0   | P2MAT[7:0]        | Port 2 Match Value.                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|       |                   | Match comparison value used on Port 2 for bits in P2MAT which are set to 1.<br>0: P2.n pin logic value is compared with logic LOW.<br>1: P2.n pin logic value is compared with logic HIGH. |  |  |  |  |  |  |  |  |

| Note: | Ports 2.2-P2.7 on | Ports 2.2-P2.7 only available on 32-pin packages.                                                                                                                                          |  |  |  |  |  |  |  |  |

## SFR Definition 18.19. P1SKIP: Port 1 Skip

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|-------------|---|---|---|---|---|---|---|--|--|

| Name  | P1SKIP[7:0] |   |   |   |   |   |   |   |  |  |

| Туре  | R/W         |   |   |   |   |   |   |   |  |  |

| Reset | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

SFR Address = 0xD5; SFR Page = 0x0F

| Bit | Name        | Function                                                                                                                                                                                                                                                                              |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1SKIP[7:0] | Port 1 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                     |

|     |             | These bits select Port 1 pins to be skipped by the Crossbar Decoder. Port pins<br>used for analog, special functions or GPIO should be skipped by the Crossbar.<br>0: Corresponding P1.n pin is not skipped by the Crossbar.<br>1: Corresponding P1.n pin is skipped by the Crossbar. |

#### SFR Definition 18.20. P2: Port 2

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---------|---|---|---|---|---|---|---|--|--|

| Name  | P2[7:0] |   |   |   |   |   |   |   |  |  |

| Туре  | R/W     |   |   |   |   |   |   |   |  |  |

| Reset | 1       | 1 | 1 | 1 | 1 | 1 | 1 | 1 |  |  |

SFR Address = 0xA0; SFR Page = All Pages; Bit-Addressable

| Bit   | Name                                                       | Description                                                                                                                                  | Write                                                                         | Read                                                                    |  |  |  |  |  |  |

|-------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|--|--|

| 7:0   | P2[7:0]                                                    | <b>Port 2Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P2.n Port pin is logic<br>LOW.<br>1: P2.n Port pin is logic<br>HIGH. |  |  |  |  |  |  |

| Note: | lote: P2.2-P2.7 are only available on the 32-pin packages. |                                                                                                                                              |                                                                               |                                                                         |  |  |  |  |  |  |

## LIN Register Definition 19.7. LIN0ERR: LIN0 Error Register

| Bit   | 7 | 6 | 5 | 4     | 3    | 2    | 1   | 0      |

|-------|---|---|---|-------|------|------|-----|--------|

| Name  |   |   |   | SYNCH | PRTY | TOUT | СНК | BITERR |

| Туре  | R | R | R | R     | R    | R    | R   | R      |

| Reset | 0 | 0 | 0 | 0     | 0    | 0    | 0   | 0      |

Indirect Address = 0x0A

| Bit | Name   | Function                                                                                                                                                  |  |  |  |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7:5 | Unused | Read = 000b; Write = Don't Care                                                                                                                           |  |  |  |

| 4   | SYNCH  | Synchronization Error Bit (slave mode only).                                                                                                              |  |  |  |

|     |        | 0: No error with the SYNCH FIELD has been detected.                                                                                                       |  |  |  |

|     |        | 1: Edges of the SYNCH FIELD are outside of the maximum tolerance.                                                                                         |  |  |  |

| 3   | PRTY   | Parity Error Bit (slave mode only).                                                                                                                       |  |  |  |

|     |        | 0: No parity error has been detected.                                                                                                                     |  |  |  |

|     |        | 1: A parity error has been detected.                                                                                                                      |  |  |  |

| 2   | TOUT   | Timeout Error Bit.                                                                                                                                        |  |  |  |

|     |        | 0: A timeout error has not been detected.                                                                                                                 |  |  |  |

|     |        | 1: A timeout error has been detected. This error is detected whenever one of the fol-<br>lowing conditions is met:                                        |  |  |  |

|     |        | <ul> <li>The master is expecting data from a slave and the slave does not respond.</li> </ul>                                                             |  |  |  |

|     |        | The slave is expecting data but no data is transmitted on the bus.                                                                                        |  |  |  |

|     |        | • A frame is not finished within the maximum frame length.                                                                                                |  |  |  |

|     |        | • The application does not set the DTACK bit (LIN0CTRL.4) or STOP bit (LIN0CTRL.7) until the end of the reception of the first byte after the identifier. |  |  |  |

| 1   | СНК    | Checksum Error Bit.                                                                                                                                       |  |  |  |

|     |        | 0: Checksum error has not been detected.                                                                                                                  |  |  |  |

|     |        | 1: Checksum error has been detected.                                                                                                                      |  |  |  |

| 0   | BITERR | Bit Transmission Error Bit.                                                                                                                               |  |  |  |

|     |        | 0: No error in transmission has been detected.                                                                                                            |  |  |  |

|     |        | 1: The bit value monitored during transmission is different than the bit value sent.                                                                      |  |  |  |

meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 20.2 shows the minimum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary when SYSCLK is above 10 MHz.

| EXTHOLD                                                                                                                                                                                                                                                                                                          | Minimum SDA Setup Time                                                              | Minimum SDA Hold Time |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------|--|--|--|--|

| 0                                                                                                                                                                                                                                                                                                                | T <sub>low</sub> – 4 system clocks<br>or<br>1 system clock + s/w delay <sup>*</sup> | 3 system clocks       |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                | 11 system clocks                                                                    | 12 system clocks      |  |  |  |  |

| *Note: Setup Time for ACK bit transmissions and the MSB of all data transfers. When using software acknowledgement, the s/w delay occurs between the time SMB0DAT or ACK is written and when SI is cleared. Note that if SI is cleared in the same write that defines the outgoing ACK value, s/w delay is zero. |                                                                                     |                       |  |  |  |  |

Table 20.2. Minimum SDA Setup and Hold Times

With the SMBTOE bit set, Timer 3 should be configured to overflow after 25 ms in order to detect SCL low timeouts (see Section "20.3.4. SCL Low Timeout" on page 189). The SMBus interface will force Timer 3 to reload while SCL is high, and allow Timer 3 to count when SCL is low. The Timer 3 interrupt service routine should be used to reset SMBus communication by disabling and re-enabling the SMBus.

SMBus Free Timeout detection can be enabled by setting the SMBFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 20.4).

- 1. Clear RI0 to 0.

- 2. Read SBUF0.

- 3. Check RI0, and repeat at step 1 if RI0 is set to 1.

If the extra bit function is enabled (XBE0 = 1) and the parity function is disabled (PE0 = 0), the extra bit for the oldest byte in the FIFO can be read from the RBX0 bit (SCON0.2). If the extra bit function is not enabled, the value of the stop bit for the oldest FIFO byte will be presented in RBX0. When the parity function is enabled (PE0 = 1), hardware will check the received parity bit against the selected parity type (selected with S0PT[1:0]) when receiving data. If a byte with parity error is received, the PERR0 flag will be set to 1. This flag must be cleared by software. Note: when parity is enabled, the extra bit function is not available.

#### 21.3.3. Multiprocessor Communications