Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), LINbus, SPI, UART/USART       |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 1.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                   |

| Data Converters            | A/D 25x12b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                             |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 32-QFN (5x5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f544-im |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **List of Tables**

| Table 2.1. Product Selection Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Table 3.1. Pin Definitions for the C8051F54x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 18                                                                                                                                           |

| Table 4.1. QFP-32 Package Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23                                                                                                                                           |

| Table 4.2. QFP-32 Landing Diagram Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24                                                                                                                                           |

| Table 4.3. QFN-32 Package Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                              |

| Table 4.4. QFN-32 Landing Diagram Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 26                                                                                                                                           |

| Table 4.5. QFN-24 Package Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                              |

| Table 4.6. QFN-24 Landing Diagram Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                              |

| Table 6.1. Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                              |

| Table 6.2. Global Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                              |

| Table 6.3. Port I/O DC Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                              |

| Table 6.4. Reset Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                              |

| Table 6.5. Flash Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                              |

| Table 6.6. Internal High-Frequency Oscillator Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                              |

| Table 6.7. Clock Multiplier Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |

| Table 6.8. Voltage Regulator Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                              |

| Table 6.9. ADC0 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                              |

| Table 6.10. Temperature Sensor Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 56                                                                                                                                           |

| Table 6.11. Voltage Reference Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56                                                                                                                                           |

| Table 6.12. Comparator 0 and Comparator 1 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                              |

| Table 10.1. CIP-51 Instruction Set Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11                                                                                                                                           |

| Table 12.1. Special Function Register (SFR) Memory Map for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 100                                                                                                                                          |

| Pages 0x0 and 0xF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                              |

| Table 12.2. Special Function Registers         Table 12.1. Interrupt Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                              |

| Table 13.1. Interrupt Summary         Table 14.1. Elash Security Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                              |

| Table 14.1. Flash Security Summary       *         Table 18.1. Port I/O Assignment for Analog Functions       *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1/0                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                              |

| Table 18.2. Port I/O Assignment for Digital Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 149                                                                                                                                          |

| Table 18.2. Port I/O Assignment for Digital Functions       Table 18.3. Port I/O Assignment for External Digital Event Capture Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 149<br>150                                                                                                                                   |

| Table 18.2. Port I/O Assignment for Digital Functions       7         Table 18.3. Port I/O Assignment for External Digital Event Capture Functions       7         Table 19.1. Baud Rate Calculation Variable Ranges       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 149<br>150<br>171                                                                                                                            |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 149<br>150<br>171<br>173                                                                                                                     |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters Examples                                                                                                                                                                                                                                                                                                                                                                                                                                   | 149<br>150<br>171<br>173<br>174                                                                                                              |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)                                                                                                                                                                                                                                                                                                                                                                                | 149<br>150<br>171<br>173<br>174<br>179                                                                                                       |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source Selection                                                                                                                                                                                                                                                                                                                                        | 149<br>150<br>171<br>173<br>174<br>179<br>191                                                                                                |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source SelectionTable 20.2. Minimum SDA Setup and Hold Times                                                                                                                                                                                                                                                                                            | 149<br>150<br>171<br>173<br>174<br>179<br>191<br>192                                                                                         |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source SelectionTable 20.2. Minimum SDA Setup and Hold TimesTable 20.3. Sources for Hardware Changes to SMB0CN                                                                                                                                                                                                                                          | 149<br>150<br>171<br>173<br>174<br>179<br>191<br>192<br>196                                                                                  |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source SelectionTable 20.2. Minimum SDA Setup and Hold TimesTable 20.4. SMBus Status Decoding                                                                                                                                                                                                                                                           | <ul> <li>149</li> <li>150</li> <li>171</li> <li>173</li> <li>174</li> <li>179</li> <li>191</li> <li>192</li> <li>196</li> <li>202</li> </ul> |

| Table 18.2. Port I/O Assignment for Digital Functions       Table 18.3. Port I/O Assignment for External Digital Event Capture Functions         Table 19.1. Baud Rate Calculation Variable Ranges       Table 19.1. Baud Rate Calculation Variable Ranges         Table 19.2. Manual Baud Rate Parameters Examples       Table 19.3. Autobaud Parameters Examples         Table 19.4. LIN Registers* (Indirectly Addressable)       Table 20.1. SMBus Clock Source Selection         Table 20.2. Minimum SDA Setup and Hold Times       Table 20.3. Sources for Hardware Changes to SMB0CN         Table 20.4. SMBus Status Decoding       Table 21.1. Baud Rate Generator Settings for Standard Baud Rates | 149<br>150<br>171<br>173<br>174<br>179<br>191<br>192<br>196<br>202<br>206                                                                    |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source SelectionTable 20.2. Minimum SDA Setup and Hold TimesTable 20.3. Sources for Hardware Changes to SMB0CNTable 20.4. SMBus Status DecodingTable 21.1. Baud Rate Generator Settings for Standard Baud RatesTable 22.1. SPI Slave Timing Parameters                                                                                                  | 149<br>150<br>171<br>173<br>174<br>179<br>191<br>192<br>196<br>202<br>206<br>226                                                             |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source SelectionTable 20.2. Minimum SDA Setup and Hold TimesTable 20.3. Sources for Hardware Changes to SMB0CNTable 20.4. SMBus Status DecodingTable 21.1. Baud Rate Generator Settings for Standard Baud RatesTable 22.1. SPI Slave Timing ParametersTable 24.1. PCA Timebase Input Options                                                            | 149<br>150<br>171<br>173<br>174<br>179<br>191<br>192<br>196<br>202<br>206<br>226                                                             |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source SelectionTable 20.2. Minimum SDA Setup and Hold TimesTable 20.3. Sources for Hardware Changes to SMB0CNTable 20.4. SMBus Status DecodingTable 21.1. Baud Rate Generator Settings for Standard Baud RatesTable 22.1. SPI Slave Timing ParametersTable 24.1. PCA Timebase Input OptionsTable 24.2. PCA0CPM and PCA0PWM Bit Settings for            | 149<br>150<br>171<br>173<br>174<br>179<br>191<br>192<br>196<br>202<br>206<br>226<br>226                                                      |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source SelectionTable 20.2. Minimum SDA Setup and Hold TimesTable 20.3. Sources for Hardware Changes to SMB0CNTable 20.4. SMBus Status DecodingTable 21.1. Baud Rate Generator Settings for Standard Baud RatesTable 22.1. SPI Slave Timing ParametersTable 24.1. PCA Timebase Input Options                                                            | 149<br>150<br>171<br>173<br>174<br>179<br>191<br>192<br>202<br>206<br>226<br>250<br>250                                                      |

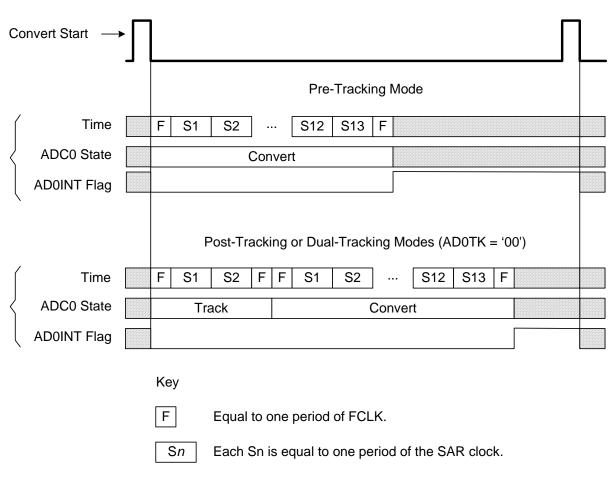

Figure 5.3. 12-Bit ADC Tracking Mode Example

### 5.1.4. Burst Mode

Burst Mode is a power saving feature that allows ADC0 to remain in a very low power state between conversions. When Burst Mode is enabled, ADC0 wakes from a very low power state, accumulates 1, 4, 8, or 16 samples using an internal Burst Mode clock (approximately 25 MHz), then re-enters a very low power state. Since the Burst Mode clock is independent of the system clock, ADC0 can perform multiple conversions then enter a very low power state within a single system clock cycle, even if the system clock is slow (e.g., 32.768 kHz), or suspended.

Burst Mode is enabled by setting BURSTEN to logic 1. When in Burst Mode, AD0EN controls the ADC0 idle power state (i.e. the state ADC0 enters when not tracking or performing conversions). If AD0EN is set to logic 0, ADC0 is powered down after each burst. If AD0EN is set to logic 1, ADC0 remains enabled after each burst. On each convert start signal, ADC0 is awakened from its Idle Power State. If ADC0 is powered down, it will automatically power up and wait the programmable Power-Up Time controlled by the AD0PWR bits. Otherwise, ADC0 will start tracking and converting immediately. Figure 5.4 shows an example of Burst Mode Operation with a slow system clock and a repeat count of 4.

Important Note: When Burst Mode is enabled, only Post-Tracking and Dual-Tracking modes can be used.

When Burst Mode is enabled, a single convert start will initiate a number of conversions equal to the repeat count. When Burst Mode is disabled, a convert start is required to initiate each conversion. In both modes, the ADC0 End of Conversion Interrupt Flag (AD0INT) will be set after "repeat count" conversions have

## SFR Definition 5.8. ADC0TK: ADC0 Tracking Mode Select

| Bit   | 7   | 6     | 5       | 4 | 3          | 2 | 1          | 0 |

|-------|-----|-------|---------|---|------------|---|------------|---|

| Name  |     | AD0PV | VR[3:0] |   | AD0TM[1:0] |   | AD0TK[1:0] |   |

| Туре  | R/W |       |         |   | R/         | W | R/         | W |

| Reset | 1   | 1     | 1       | 1 | 1          | 1 | 1          | 1 |

SFR Address = 0xBA; SFR Page = 0x00;

| Bit | Name        | Function                                                                                                                                                                           |  |  |  |  |  |  |  |  |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 7:4 | AD0PWR[3:0] | ADC0 Burst Power-Up Time.                                                                                                                                                          |  |  |  |  |  |  |  |  |

|     |             | For BURSTEN = 0: ADC0 Power state controlled by AD0EN                                                                                                                              |  |  |  |  |  |  |  |  |

|     |             | For BURSTEN = 1, AD0EN = 1: ADC0 remains enabled and does not enter the very low power state                                                                                       |  |  |  |  |  |  |  |  |

|     |             | For BURSTEN = 1, AD0EN = 0: ADC0 enters the very low power state and is enabled after each convert start signal. The Power-Up time is programmed according the following equation: |  |  |  |  |  |  |  |  |

|     |             | $PWR = \frac{Tstartup}{200ns} - 1  or Tstartup = (AD0PWR + 1)200ns$                                                                                                                |  |  |  |  |  |  |  |  |

| 3:2 | AD0TM[1:0]  | ADC0 Tracking Mode Enable Select Bits.                                                                                                                                             |  |  |  |  |  |  |  |  |

|     |             | 00: Reserved.                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|     |             | 01: ADC0 is configured to Post-Tracking Mode.                                                                                                                                      |  |  |  |  |  |  |  |  |

|     |             | 10: ADC0 is configured to Pre-Tracking Mode.                                                                                                                                       |  |  |  |  |  |  |  |  |

| 4.0 |             | 11: ADC0 is configured to Dual Tracking Mode.                                                                                                                                      |  |  |  |  |  |  |  |  |

| 1:0 | AD0TK[1:0]  | ADC0 Post-Track Time.                                                                                                                                                              |  |  |  |  |  |  |  |  |

|     |             | 00: Post-Tracking time is equal to 2 SAR clock cycles + 2 FCLK cycles.                                                                                                             |  |  |  |  |  |  |  |  |

|     |             | 01: Post-Tracking time is equal to 4 SAR clock cycles + 2 FCLK cycles.                                                                                                             |  |  |  |  |  |  |  |  |

|     |             | 10: Post-Tracking time is equal to 8 SAR clock cycles + 2 FCLK cycles.                                                                                                             |  |  |  |  |  |  |  |  |

|     |             | 11: Post-Tracking time is equal to 16 SAR clock cycles + 2 FCLK cycles.                                                                                                            |  |  |  |  |  |  |  |  |

### 5.4. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

### SFR Definition 5.11. ADC0LTH: ADC0 Less-Than Data High Byte

| D:4   | -              |              | F                                         | 4 | 2 | • |   | • |  |  |  |

|-------|----------------|--------------|-------------------------------------------|---|---|---|---|---|--|--|--|

| Bit   | 1              | 6            | 5                                         | 4 | 3 | 2 | 1 | 0 |  |  |  |

| Nam   | e              | ADC0LTH[7:0] |                                           |   |   |   |   |   |  |  |  |

| Туре  | Type R/W       |              |                                           |   |   |   |   |   |  |  |  |

| Rese  | et 0           | 0            | 0                                         | 0 | 0 | 0 | 0 | 0 |  |  |  |

| SFR A | Address = 0xC6 | ; SFR Page   | e = 0x00                                  |   |   |   |   |   |  |  |  |

| Bit   | Name           |              | Function                                  |   |   |   |   |   |  |  |  |

| 7:0   | ADC0LTH[7:0    | ] ADC0 Le    | ADC0 Less-Than Data Word High-Order Bits. |   |   |   |   |   |  |  |  |

#### SFR Definition 5.12. ADC0LTL: ADC0 Less-Than Data Low Byte

| Bit   | 7                                   | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|-------------------------------------|--------------|---|---|---|---|---|---|--|--|--|

| Name  | 9                                   | ADC0LTL[7:0] |   |   |   |   |   |   |  |  |  |

| Туре  |                                     | R/W          |   |   |   |   |   |   |  |  |  |

| Rese  | t 0                                 | 0            | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

| SFR A | SFR Address = 0xC5; SFR Page = 0x00 |              |   |   |   |   |   |   |  |  |  |

| Bit   | Name                                |              |   |   |   |   |   |   |  |  |  |

| 7:0 | ADC0LTL[7:0] | ADC0 Less-Than Data Word Low-Order Bits. |

|-----|--------------|------------------------------------------|

#### 5.4.1. Window Detector In Single-Ended Mode

window for Figure 5.6 shows two example comparisons right-justified data with ADC0LTH:ADC0LTL = 0x0200 (512d) and ADC0GTH:ADC0GTL = 0x0100 (256d). The input voltage can range from 0 to V<sub>REF</sub> x (4095/4096) with respect to GND, and is represented by a 12-bit unsigned integer value. The repeat count is set to one. In the left example, an AD0WINT interrupt will be generated if the ADC0 conversion word (ADC0H:ADC0L) is within the range defined by ADC0GTH:ADC0GTL and ADC0LTH:ADC0LTL (if 0x0100 < ADC0H:ADC0L < 0x0200). In the right example, and AD0WINT interrupt will be generated if the ADC0 conversion word is outside of the range defined by the ADC0GT and ADC0LT registers (if ADC0H:ADC0L < 0x0100 or ADC0H:ADC0L > 0x0200). Figure 5.7 shows an example using left-justified data with the same comparison values.

#### Table 6.2. Global Electrical Characteristics (Continued)

-40 to +125 °C, 24 MHz system clock unless otherwise specified.

| Parameter                                                                             | Conditions                                                  | Min | Тур  | Max | Units  |  |  |  |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------|-----|------|-----|--------|--|--|--|

| Digital Supply Current—CPU Inactive (Idle Mode, not fetching instructions from Flash) |                                                             |     |      |     |        |  |  |  |

| I <sub>DD</sub> <sup>4</sup>                                                          | V <sub>DD</sub> = 2.1 V, F = 200 kHz                        | _   | 50   | —   | μA     |  |  |  |

|                                                                                       | V <sub>DD</sub> = 2.1 V, F = 1.5 MHz                        | —   | 410  | —   | μA     |  |  |  |

|                                                                                       | V <sub>DD</sub> = 2.1 V, F = 25 MHz                         | —   | 6.5  | 8.0 | mA     |  |  |  |

|                                                                                       | V <sub>DD</sub> = 2.1 V, F = 50 MHz                         | —   | 13   | 16  | mA     |  |  |  |

| I <sub>DD</sub> <sup>4</sup>                                                          | V <sub>DD</sub> = 2.6 V, F = 200 kHz                        |     | 67   |     | μA     |  |  |  |

|                                                                                       | V <sub>DD</sub> = 2.6 V, F = 1.5 MHz                        | —   | 530  | —   | μA     |  |  |  |

|                                                                                       | V <sub>DD</sub> = 2.6 V, F = 25 MHz                         | —   | 8.0  | 15  | mA     |  |  |  |

|                                                                                       | V <sub>DD</sub> = 2.6 V, F = 50 MHz                         | —   | 16   | 25  | mA     |  |  |  |

| I <sub>DD</sub> Supply Sensitivity <sup>4</sup>                                       | F = 25 MHz                                                  | —   | 55   | —   | %/V    |  |  |  |

|                                                                                       | F = 1 MHz                                                   | —   | 58   | —   | 70/ V  |  |  |  |

| I <sub>DD</sub> Frequency Sensitivity 4.6                                             | $V_{DD}$ = 2.1V, F $\leq$ 12.5 MHz, T = 25 °C               | —   | 0.26 | —   |        |  |  |  |

|                                                                                       | $V_{DD}$ = 2.1V, F > 12.5 MHz, T = 25 °C                    | —   | 0.26 | —   |        |  |  |  |

|                                                                                       | $V_{DD}$ = 2.6V, F $\leq$ 12.5 MHz, T = 25 °C               | —   | 0.34 | —   | mA/MHz |  |  |  |

|                                                                                       | $V_{DD}$ = 2.6V, F > 12.5 MHz, T = 25 °C                    | —   | 0.34 | —   |        |  |  |  |

| Digital Supply Current <sup>4</sup><br>(Stop or Suspend Mode)                         | Oscillator not running,<br>V <sub>DD</sub> Monitor Disabled |     |      |     |        |  |  |  |

| , /                                                                                   | Temp = 25 °C                                                | —   | 1    | —   | μA     |  |  |  |

|                                                                                       | Temp = 60 °C                                                | —   | 6    |     |        |  |  |  |

|                                                                                       | Temp= 125 °C                                                | —   | 70   | —   |        |  |  |  |

| Notes:                                                                                |                                                             |     |      |     |        |  |  |  |

Given in Table 6.4 on page 52.

V<sub>IO</sub> should not be lower than the V<sub>DD</sub> voltage.

SYSCLK must be at least 32 kHz to enable debugging.

4. Guaranteed by characterization. Does not include oscillator supply current.

5. IDD estimation for different frequencies.

6. Idle IDD estimation for different frequencies.

# SFR Definition 6.3. ADC0MX: ADC0 Channel Select

| Name<br>Type |            |                |                              | 4              | 3            | 2             | 1        | 0 |  |  |  |  |  |  |

|--------------|------------|----------------|------------------------------|----------------|--------------|---------------|----------|---|--|--|--|--|--|--|

| Type         |            |                |                              |                | ADC0         | MX[5:0]       |          |   |  |  |  |  |  |  |

|              | R          | R              |                              |                |              | /W            |          |   |  |  |  |  |  |  |

| Reset        | 0          | 0              | 1                            | 1              | 1            | 1             | 1        | 1 |  |  |  |  |  |  |

|              |            | B; SFR Page =  | 0x00;                        |                |              |               |          |   |  |  |  |  |  |  |

| Bit          | Name       |                | Function                     |                |              |               |          |   |  |  |  |  |  |  |

| 7:6          | Unused     | -              | d = 00b; Write = Don't Care. |                |              |               |          |   |  |  |  |  |  |  |

| 5:0 A        | AMX0P[5:0] | AMUX0 Positiv  | -                            |                |              |               |          |   |  |  |  |  |  |  |

|              |            | 000000:        | P0.0                         |                |              |               |          |   |  |  |  |  |  |  |

|              |            | 000001:        | P0.1                         |                |              |               |          |   |  |  |  |  |  |  |

|              |            | 000010:        | P0.2                         |                |              |               |          |   |  |  |  |  |  |  |

|              |            | 000011:        | P0.3                         | 3              |              |               |          |   |  |  |  |  |  |  |

|              |            | 000100:        | P0.4                         |                |              |               |          |   |  |  |  |  |  |  |

|              |            | 000101:        | P0.5                         | 5              |              |               |          |   |  |  |  |  |  |  |

|              |            | 000110:        | P0.6                         | 6              |              |               |          |   |  |  |  |  |  |  |

|              |            | 000111:        | P0.7                         | 7              |              |               |          |   |  |  |  |  |  |  |

|              |            | 001000:        | P1.0                         | )              |              |               |          |   |  |  |  |  |  |  |

|              |            | 001001:        | P1.1                         |                |              |               |          |   |  |  |  |  |  |  |

|              |            | 001010:        | P1.2                         | 2              |              |               |          |   |  |  |  |  |  |  |

|              |            | 001011:        | P1.3                         | 3              |              |               |          |   |  |  |  |  |  |  |

|              |            | 001100:        | P1.4                         | ŀ              |              |               |          |   |  |  |  |  |  |  |

|              |            | 001101:        | P1.5                         | 5              |              |               |          |   |  |  |  |  |  |  |

|              |            | 001110:        | P1.6                         | 6              |              |               |          |   |  |  |  |  |  |  |

|              |            | 001111:        | P1.7                         | 7              |              |               |          |   |  |  |  |  |  |  |

|              |            | 010000:        | P2.0                         | )              |              |               |          |   |  |  |  |  |  |  |

|              |            | 010001:        | P2.1                         |                |              |               |          |   |  |  |  |  |  |  |

|              |            | 010010:        | P2.2                         | 2 (Only availa | able on 32-p | oin package o | devices) |   |  |  |  |  |  |  |

|              |            | 010011:        | P2.3                         | 3 (Only availa | able on 32-p | oin package o | devices) |   |  |  |  |  |  |  |

|              |            | 010100:        | P2.4                         | l (Only availa | able on 32-p | oin package o | devices) |   |  |  |  |  |  |  |

|              |            | 010101:        | P2.5                         | 5 (Only availa | able on 32-p | oin package o | devices) |   |  |  |  |  |  |  |

|              |            | 010110:        | P2.6                         | 6 (Only availa | able on 32-p | oin package o | devices) |   |  |  |  |  |  |  |

|              |            | 010111:        | P2.7                         | ' (Only availa | able on 32-p | oin package o | devices) |   |  |  |  |  |  |  |

|              |            | 011000:        | P3.0                         | ) (Only availa | able on 32-p | oin package o | devices) |   |  |  |  |  |  |  |

|              |            | 011001–101111  |                              | erved          |              | -             |          |   |  |  |  |  |  |  |

|              |            | 110000:        | Tem                          | p Sensor       |              |               |          |   |  |  |  |  |  |  |

|              |            | 110001:        | V <sub>DD</sub>              |                |              |               |          |   |  |  |  |  |  |  |

|              |            | 110010-111111: |                              |                |              |               |          |   |  |  |  |  |  |  |

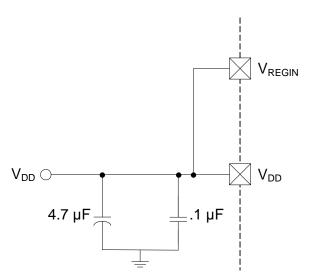

Figure 9.2. External Capacitors for Voltage Regulator Input/Output—Regulator Disabled

## SFR Definition 9.1. REG0CN: Regulator Control

| Bit   | 7      | 6        | 5 | 4      | 3 | 2 | 1 | 0       |

|-------|--------|----------|---|--------|---|---|---|---------|

| Name  | REGDIS | Reserved |   | REG0MD |   |   |   | DROPOUT |

| Туре  | R/W    | R/W      | R | R/W    | R | R | R | R       |

| Reset | 0      | 1        | 0 | 1      | 0 | 0 | 0 | 0       |

SFR Address = 0xC9; SFR Page = 0x00

| Bit | Name     | Function                                                                     |

|-----|----------|------------------------------------------------------------------------------|

| 7   | REGDIS   | Voltage Regulator Disable Bit.                                               |

|     |          | 0: Voltage Regulator Enabled<br>1: Voltage Regulator Disabled                |

| 6   | Reserved | Read = 1b; Must Write 1b.                                                    |

| 5   | Unused   | Read = 0b; Write = Don't Care.                                               |

| 4   | REG0MD   | Voltage Regulator Mode Select Bit.                                           |

|     |          | 0: Voltage Regulator Output is 2.1V.<br>1: Voltage Regulator Output is 2.6V. |

| 3:1 | Unused   | Read = 000b. Write = Don't Care.                                             |

| 0   | DROPOUT  | Voltage Regulator Dropout Indicator.                                         |

|     |          | 0: Voltage Regulator is not in dropout                                       |

|     |          | 1: Voltage Regulator is in or near dropout.                                  |

## **13.2. Interrupt Register Descriptions**

The SFRs used to enable the interrupt sources and set their priority level are described in this section. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

# SFR Definition 13.3. EIE1: Extended Interrupt Enable 1

| Bit   | 7     | 6   | 5    | 4    | 3     | 2     | 1      | 0     |

|-------|-------|-----|------|------|-------|-------|--------|-------|

| Name  | ELIN0 | ET3 | ECP1 | ECP0 | EPCA0 | EADC0 | EWADC0 | ESMB0 |

| Туре  | R/W   | R/W | R/W  | R/W  | R/W   | R/W   | R/W    | R/W   |

| Reset | 0     | 0   | 0    | 0    | 0     | 0     | 0      | 0     |

#### SFR Address = 0xE6; SFR Page = All Pages

| Bit | Name   | Function                                                                                                                                                                                                                                                                          |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ELIN0  | <ul> <li>Enable LIN0 Interrupt.</li> <li>This bit sets the masking of the LIN0 interrupt.</li> <li>0: Disable LIN0 interrupts.</li> <li>1: Enable interrupt requests generated by the LIN0INT flag.</li> </ul>                                                                    |

| 6   | ET3    | <ul> <li>Enable Timer 3 Interrupt.</li> <li>This bit sets the masking of the Timer 3 interrupt.</li> <li>0: Disable Timer 3 interrupts.</li> <li>1: Enable interrupt requests generated by the TF3L or TF3H flags.</li> </ul>                                                     |

| 5   | ECP1   | <ul> <li>Enable Comparator1 (CP1) Interrupt.</li> <li>This bit sets the masking of the CP1 interrupt.</li> <li>0: Disable CP1 interrupts.</li> <li>1: Enable interrupt requests generated by the CP1RIF or CP1FIF flags.</li> </ul>                                               |

| 4   | ECP0   | Enable Comparator0 (CP0) Interrupt.<br>This bit sets the masking of the CP0 interrupt.<br>0: Disable CP0 interrupts.<br>1: Enable interrupt requests generated by the CP0RIF or CP0FIF flags.                                                                                     |

| 3   | EPCA0  | <ul> <li>Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> </ul>                                              |

| 2   | EADC0  | <ul> <li>Enable ADC0 Conversion Complete Interrupt.</li> <li>This bit sets the masking of the ADC0 Conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> </ul>          |

| 1   | EWADC0 | <ul> <li>Enable Window Comparison ADC0 Interrupt.</li> <li>This bit sets the masking of ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> <li>1: Enable interrupt requests generated by ADC0 Window Compare flag (AD0WINT).</li> </ul> |

| 0   | ESMB0  | Enable SMBus (SMB0) Interrupt.<br>This bit sets the masking of the SMB0 interrupt.<br>0: Disable all SMB0 interrupts.<br>1: Enable interrupt requests generated by SMB0.                                                                                                          |

# SFR Definition 13.4. EIP1: Extended Interrupt Priority 1

| Bit   | 7     | 6   | 5    | 4    | 3     | 2     | 1      | 0     |

|-------|-------|-----|------|------|-------|-------|--------|-------|

| Name  | PLIN0 | PT3 | PCP1 | PCP0 | PPCA0 | PADC0 | PWADC0 | PSMB0 |

| Туре  | R/W   | R/W | R/W  | R/W  | R/W   | R/W   | R/W    | R/W   |

| Reset | 0     | 0   | 0    | 0    | 0     | 0     | 0      | 0     |

#### SFR Address = 0xF6; SFR Page = 0x00 and 0x0F

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                     |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | PLIN0  | LIN0 Interrupt Priority Control.<br>This bit sets the priority of the LIN0 interrupt.<br>0: LIN0 interrupts set to low priority level.<br>1: LIN0 interrupts set to high priority level.                                                                                                                     |

| 6   | PT3    | Timer 3 Interrupt Priority Control.This bit sets the priority of the Timer 3 interrupt.0: Timer 3 interrupts set to low priority level.1: Timer 3 interrupts set to high priority level.                                                                                                                     |

| 5   | PCP1   | Comparator0 (CP1) Interrupt Priority Control.<br>This bit sets the priority of the CP1 interrupt.<br>0: CP1 interrupt set to low priority level.<br>1: CP1 interrupt set to high priority level.                                                                                                             |

| 4   | PCP0   | Comparator0 (CP0) Interrupt Priority Control.<br>This bit sets the priority of the CP0 interrupt.<br>0: CP0 interrupt set to low priority level.<br>1: CP0 interrupt set to high priority level.                                                                                                             |

| 3   | PPCA0  | <ul> <li>Programmable Counter Array (PCA0) Interrupt Priority Control.</li> <li>This bit sets the priority of the PCA0 interrupt.</li> <li>0: PCA0 interrupt set to low priority level.</li> <li>1: PCA0 interrupt set to high priority level.</li> </ul>                                                    |

| 2   | PADC0  | <ul> <li>ADC0 Conversion Complete Interrupt Priority Control.</li> <li>This bit sets the priority of the ADC0 Conversion Complete interrupt.</li> <li>0: ADC0 Conversion Complete interrupt set to low priority level.</li> <li>1: ADC0 Conversion Complete interrupt set to high priority level.</li> </ul> |

| 1   | PWADC0 | <ul> <li>ADC0 Window Comparator Interrupt Priority Control.</li> <li>This bit sets the priority of the ADC0 Window interrupt.</li> <li>0: ADC0 Window interrupt set to low priority level.</li> <li>1: ADC0 Window interrupt set to high priority level.</li> </ul>                                          |

| 0   | PSMB0  | <ul> <li>SMBus (SMB0) Interrupt Priority Control.</li> <li>This bit sets the priority of the SMB0 interrupt.</li> <li>0: SMB0 interrupt set to low priority level.</li> <li>1: SMB0 interrupt set to high priority level.</li> </ul>                                                                         |

### 14.2. Non-volatile Data Storage

The Flash memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX write instruction and read using the MOVC instruction. Note: MOVX read instructions always target XRAM.

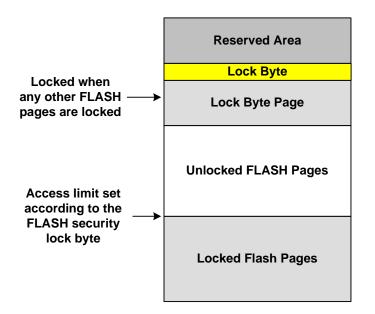

#### 14.3. Security Options

The CIP-51 provides security options to protect the Flash memory from inadvertent modification by software as well as to prevent the viewing of proprietary program code and constants. The Program Store Write Enable (bit PSWE in register PSCTL) and the Program Store Erase Enable (bit PSEE in register PSCTL) bits protect the Flash memory from accidental modification by software. PSWE must be explicitly set to 1 before software can modify the Flash memory; both PSWE and PSEE must be set to 1 before software can erase Flash memory. Additional security features prevent proprietary program code and data constants from being read or altered across the C2 interface.

A Security Lock Byte located at the last byte of Flash user space offers protection of the Flash program memory from access (reads, writes, or erases) by unprotected code or the C2 interface. The Flash security mechanism allows the user to lock n 512-byte Flash pages, starting at page 0 (addresses 0x0000 to 0x01FF), where n is the ones complement number represented by the Security Lock Byte. Note that the page containing the Flash Security Lock Byte is unlocked when no other Flash pages are locked (all bits of the Lock Byte are 1) and locked when any other Flash pages are locked (any bit of the Lock Byte is 0). See example in Figure 14.1.

| Security Lock Byte: | 11111101b                                  |

|---------------------|--------------------------------------------|

| 1s Complement:      | 0000010b                                   |

| Flash pages locked: | 3 (First two Flash pages + Lock Byte Page) |

Figure 14.1. Flash Program Memory Map

# 15. Power Management Modes

The C8051F54x devices have three software programmable power management modes: Idle, Stop, and Suspend. Idle mode and Stop mode are part of the standard 8051 architecture, while Suspend mode is an enhanced power-saving mode implemented by the high-speed oscillator peripheral.

Idle mode halts the CPU while leaving the peripherals and clocks active. In Stop mode, the CPU is halted, all interrupts and timers (except the Missing Clock Detector) are inactive, and the internal oscillator is stopped (analog peripherals remain in their selected states; the external oscillator is not affected). Suspend mode is similar to Stop mode in that the internal oscillator and CPU are halted, but the device can wake on events such as a Port Match or Comparator low output. Since clocks are running in Idle mode, power consumption is dependent upon the system clock frequency and the number of peripherals left in active mode before entering Idle. Stop mode and Suspend mode consume the least power because the majority of the device is shut down with no clocks active. SFR Definition 15.1 describes the Power Control Register (PCON) used to control the C8051F54x devices' Stop and Idle power management modes. Suspend mode is controlled by the SUSPEND bit in the OSCICN register (SFR Definition 17.2).

Although the C8051F54x has Idle, Stop, and Suspend modes available, more control over the device power can be achieved by enabling/disabling individual peripherals as needed. Each analog peripheral can be disabled when not in use and placed in low power mode. Digital peripherals, such as timers or serial buses, draw little power when they are not in use. Turning off oscillators lowers power consumption considerably, at the expense of reduced functionality.

#### 15.1. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the hardware to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

Note: If the instruction following the write of the IDLE bit is a single-byte instruction and an interrupt occurs during the execution phase of the instruction that sets the IDLE bit, the CPU may not wake from Idle mode when a future interrupt occurs. Therefore, instructions that set the IDLE bit should be followed by an instruction that has two or more opcode bytes, for example:

| // in `C':<br>PCON  = 0x01;<br>PCON = PCON;        | <pre>// set IDLE bit // followed by a 3-cycle dummy instruction</pre> |

|----------------------------------------------------|-----------------------------------------------------------------------|

| ; in assembly:<br>ORL PCON, #01h<br>MOV PCON, PCON | ; set IDLE bit<br>; followed by a 3-cycle dummy instruction           |

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the Idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the Idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to Section "16.6. PCA Watchdog Timer Reset" on page 133 for more information on the use and configuration of the WDT.

# LIN Register Definition 19.6. LIN0ST: LIN0 Status Register

| Bit   | 7      | 6       | 5     | 4     | 3      | 2     | 1      | 0    |

|-------|--------|---------|-------|-------|--------|-------|--------|------|

| Name  | ACTIVE | IDLTOUT | ABORT | DTREQ | LININT | ERROR | WAKEUP | DONE |

| Туре  | R      | R       | R     | R     | R      | R     | R      | R    |

| Reset | 0      | 0       | 0     | 0     | 0      | 0     | 0      | 0    |

Indirect Address = 0x09

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                          |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ACTIVE | LIN Active Indicator Bit.                                                                                                                                                                                                                                                                                         |

|     |        | 0: No transmission activity detected on the LIN bus.                                                                                                                                                                                                                                                              |

|     |        | 1: Transmission activity detected on the LIN bus.                                                                                                                                                                                                                                                                 |

| 6   | IDLT   | Bus Idle Timeout Bit. (slave mode only)                                                                                                                                                                                                                                                                           |

|     |        | 0: The bus has not been idle for four seconds.                                                                                                                                                                                                                                                                    |

|     |        | 1: No bus activity has been detected for four seconds, but the bus is not yet in Sleep mode.                                                                                                                                                                                                                      |