Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                          |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 50MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), LINbus, SPI, UART/USART        |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 25                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 1.25К х 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                    |

| Data Converters            | A/D 25x12b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                              |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 32-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 32-QFN (5x5)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f544-imr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 15. Power Management Modes                                              | 126 |

|-------------------------------------------------------------------------|-----|

| 15.1. Idle Mode                                                         | 126 |

| 15.2. Stop Mode                                                         |     |

| 15.3. Suspend Mode                                                      | 127 |

| 16. Reset Sources                                                       |     |

| 16.1. Power-On Reset                                                    |     |

| 16.2. Power-Fail Reset/VDD Monitor                                      |     |

| 16.3. External Reset                                                    |     |

| 16.4. Missing Clock Detector Reset                                      |     |

| 16.5. Comparator0 Reset                                                 |     |

| 16.6. PCA Watchdog Timer Reset                                          |     |

| 16.7. Flash Error Reset                                                 |     |

| 16.8. Software Reset                                                    |     |

| 17. Oscillators and Clock Selection                                     |     |

| 17.1. System Clock Selection                                            |     |

| 17.2. Programmable Internal Oscillator                                  |     |

| 17.3. Clock Multiplier                                                  |     |

| 17.4. External Oscillator Drive Circuit                                 |     |

| 18. Port Input/Output                                                   |     |

| 18.1. Port I/O Modes of Operation                                       |     |

| 18.2. Assigning Port I/O Pins to Analog and Digital Functions           |     |

| 18.3. Priority Crossbar Decoder                                         |     |

| 18.4. Port I/O Initialization                                           |     |

| 18.5. Port Match                                                        | -   |

| 18.6. Special Function Registers for Accessing and Configuring Port I/O |     |

| 19. Local Interconnect Network (LIN)                                    |     |

| 19.1. Software Interface with the LIN Controller                        |     |

| 19.2. LIN Interface Setup and Operation                                 |     |

| 19.3. LIN Master Mode Operation                                         |     |

| 19.4. LIN Slave Mode Operation                                          |     |

| 19.5. Sleep Mode and Wake-Up                                            |     |

| 19.6. Error Detection and Handling                                      |     |

| 19.7. LIN Registers                                                     |     |

| 20. SMBus                                                               |     |

| 20.1. Supporting Documents                                              |     |

| 20.2. SMBus Configuration                                               |     |

| 20.3. SMBus Operation                                                   |     |

| 20.4. Using the SMBus                                                   | 190 |

| 20.5. SMBus Transfer Modes                                              |     |

| 20.6. SMBus Status Decoding                                             |     |

| 21. UART0                                                               |     |

| 21.1. Baud Rate Generator                                               |     |

| 21.2. Data Format                                                       |     |

| 21.3. Configuration and Operation                                       | 208 |

| 22. Enhanced Serial Peripheral Interface (SPI0)                         | 214 |

# C8051F54x

| Figure 24.3. PCA Interrupt Block Diagram               | 252 |

|--------------------------------------------------------|-----|

| Figure 24.4. PCA Capture Mode Diagram                  | 254 |

| Figure 24.5. PCA Software Timer Mode Diagram           | 255 |

| Figure 24.6. PCA High-Speed Output Mode Diagram        | 256 |

| Figure 24.7. PCA Frequency Output Mode                 | 257 |

| Figure 24.8. PCA 8-Bit PWM Mode Diagram                |     |

| Figure 24.9. PCA 9, 10 and 11-Bit PWM Mode Diagram     | 259 |

| Figure 24.10. PCA 16-Bit PWM Mode                      | 260 |

| Figure 24.11. PCA Module 2 with Watchdog Timer Enabled | 261 |

| Figure 25.1. Typical C2 Pin Sharing                    | 272 |

| SFR Definition 16.1. VDM0CN: VDD Monitor Control                     | 132 |

|----------------------------------------------------------------------|-----|

| SFR Definition 16.2. RSTSRC: Reset Source                            | 134 |

| SFR Definition 17.1. CLKSEL: Clock Select                            |     |

| SFR Definition 17.2. OSCICN: Internal Oscillator Control             | 138 |

| SFR Definition 17.3. OSCICRS: Internal Oscillator Coarse Calibration | 139 |

| SFR Definition 17.4. OSCIFIN: Internal Oscillator Fine Calibration   | 139 |

| SFR Definition 17.5. CLKMUL: Clock Multiplier                        | 141 |

| SFR Definition 17.6. OSCXCN: External Oscillator Control             | 143 |

| SFR Definition 18.1. XBR0: Port I/O Crossbar Register 0              | 154 |

| SFR Definition 18.2. XBR1: Port I/O Crossbar Register 1              |     |

| SFR Definition 18.3. XBR2: Port I/O Crossbar Register 1              | 156 |

| SFR Definition 18.4. P0MASK: Port 0 Mask Register                    |     |

| SFR Definition 18.5. P0MAT: Port 0 Match Register                    | 157 |

| SFR Definition 18.6. P1MASK: Port 1 Mask Register                    | 158 |

| SFR Definition 18.7. P1MAT: Port 1 Match Register                    | 158 |

| SFR Definition 18.8. P2MASK: Port 2 Mask Register                    | 159 |

| SFR Definition 18.9. P2MAT: Port 2 Match Register                    | 159 |

| SFR Definition 18.10. P3MASK: Port 3 Mask Register                   | 160 |

| SFR Definition 18.11. P3MAT: Port 3 Match Register                   | 160 |

| SFR Definition 18.12. P0: Port 0                                     |     |

| SFR Definition 18.13. P0MDIN: Port 0 Input Mode                      |     |

| SFR Definition 18.14. P0MDOUT: Port 0 Output Mode                    | 162 |

| SFR Definition 18.15. P0SKIP: Port 0 Skip                            |     |

| SFR Definition 18.16. P1: Port 1                                     |     |

| SFR Definition 18.17. P1MDIN: Port 1 Input Mode                      |     |

| SFR Definition 18.18. P1MDOUT: Port 1 Output Mode                    |     |

| SFR Definition 18.19. P1SKIP: Port 1 Skip                            |     |

| SFR Definition 18.20. P2: Port 2                                     |     |

| SFR Definition 18.21. P2MDIN: Port 2 Input Mode                      |     |

| SFR Definition 18.22. P2MDOUT: Port 2 Output Mode                    | 166 |

| SFR Definition 18.23. P2SKIP: Port 2 Skip                            |     |

| SFR Definition 18.24. P3: Port 3                                     |     |

| SFR Definition 18.25. P3MDIN: Port 3 Input Mode                      | 168 |

| SFR Definition 18.26. P3MDOUT: Port 3 Output Mode                    | 168 |

| SFR Definition 18.27. P3SKIP: Port 3Skip                             | 169 |

| SFR Definition 19.1. LIN0ADR: LIN0 Indirect Address Register         | 177 |

| SFR Definition 19.2. LIN0DAT: LIN0 Indirect Data Register            | 177 |

| SFR Definition 19.3. LIN0CF: LIN0 Control Mode Register              | 178 |

| SFR Definition 20.1. SMB0CF: SMBus Clock/Configuration               |     |

| SFR Definition 20.2. SMB0CN: SMBus Control                           |     |

| SFR Definition 20.3. SMB0DAT: SMBus Data                             | 197 |

| SFR Definition 21.1. SCON0: Serial Port 0 Control                    |     |

| SFR Definition 21.2. SMOD0: Serial Port 0 Control                    |     |

| SFR Definition 21.3. SBUF0: Serial (UART0) Port Data Buffer          |     |

| SFR Definition 21.4. SBCON0: UART0 Baud Rate Generator Control       | 212 |

|                                                                      |     |

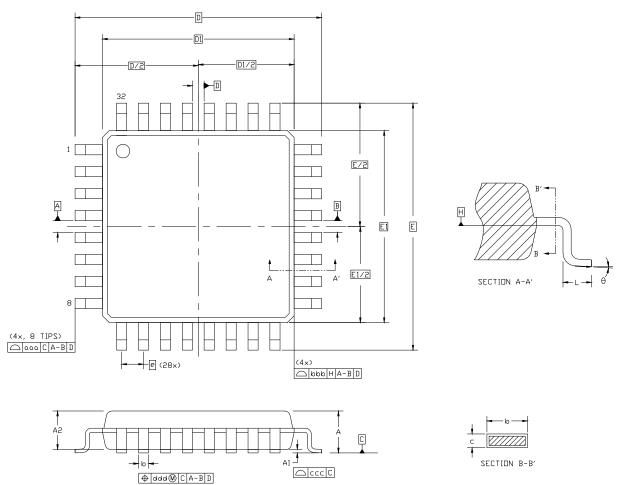

# 4. Package Specifications

# 4.1. QFP-32 Package Specifications

## Figure 4.1. QFP-32 Package Drawing

#### Table 4.1. QFP-32 Package Dimensions

| Dimension | Min         | Тур       | Max  | Dimension | Min  | Тур       | Max  |

|-----------|-------------|-----------|------|-----------|------|-----------|------|

| A         | _           | _         | 1.60 | E         |      | 9.00 BSC. |      |

| A1        | 0.05        | _         | 0.15 | E1        |      | 7.00 BSC. |      |

| A2        | 1.35        | 1.40      | 1.45 | L         | 0.45 | 0.60      | 0.75 |

| b         | 0.30        | 0.37      | 0.45 | aaa       |      | 0.20      |      |

| С         | 0.09 — 0.20 |           |      | bbb       |      | 0.20      |      |

| D         | 9.00 BSC.   |           |      | CCC       |      | 0.10      |      |

| D1        | 7.00 BSC.   |           |      | ddd       |      | 0.20      |      |

| е         |             | 0.80 BSC. |      | θ         | 0°   | 3.5°      | 7°   |

#### Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to the JEDEC outline MS-026, variation BBA.

- Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

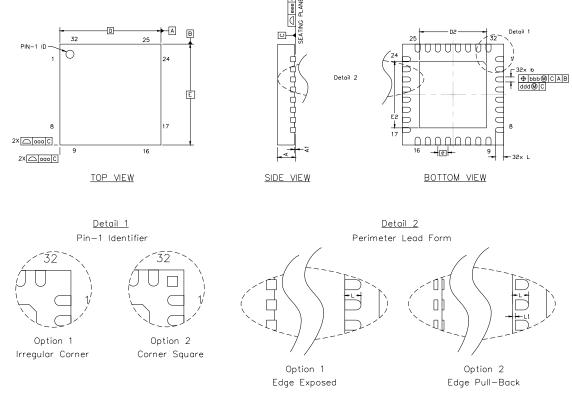

## 4.2. QFN-32 Package Specifications

Figure 4.3. QFN-32 Package Drawing

| Dimension | Min       | Тур  | Max  | Dimension | Min  | Тур  | Max  |

|-----------|-----------|------|------|-----------|------|------|------|

| A         | 0.80      | 0.9  | 1.00 | E2        | 3.20 | 3.30 | 3.40 |

| A1        | 0.00      | 0.02 | 0.05 | L         | 0.30 | 0.40 | 0.50 |

| b         | 0.18      | 0.25 | 0.30 | L1        | 0.00 | _    | 0.15 |

| D         | 5.00 BSC. |      |      | aaa       | _    | _    | 0.15 |

| D2        | 3.20      | 3.30 | 3.40 | bbb       | _    | _    | 0.15 |

| е         | 0.50 BSC. |      |      | ddd       | _    | —    | 0.05 |

| E         | 5.00 BSC. |      |      | eee       |      |      | 0.08 |

#### Table 4.3. QFN-32 Package Dimensions

Notes:

- **1.** All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- **3.** This drawing conforms to the JEDEC Solid State Outline MO-220, variation VHHD except for custom features D2, E2, and L which are toleranced per supplier designation.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

# 6. Electrical Characteristics

# 6.1. Absolute Maximum Specifications

## Table 6.1. Absolute Maximum Ratings

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                  | Conditions | Min  | Тур | Max                   | Units |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|-----|-----------------------|-------|--|

| Ambient Temperature under Bias                                                                                                                                                                                                                                                                                                                                                                             |            | -55  | _   | 135                   | °C    |  |

| Storage Temperature                                                                                                                                                                                                                                                                                                                                                                                        |            | -65  | _   | 150                   | °C    |  |

| Voltage on V <sub>REGIN</sub> with Respect to GND                                                                                                                                                                                                                                                                                                                                                          |            | -0.3 | _   | 5.5                   | V     |  |

| Voltage on V <sub>DD</sub> with Respect to GND                                                                                                                                                                                                                                                                                                                                                             |            | -0.3 | _   | 2.8                   | V     |  |

| Voltage on VDDA with Respect to GND                                                                                                                                                                                                                                                                                                                                                                        |            | -0.3 |     | 2.8                   | V     |  |

| Voltage on V <sub>IO</sub> with Respect to GND                                                                                                                                                                                                                                                                                                                                                             |            | -0.3 | _   | 5.5                   | V     |  |

| Voltage on any Port I/O Pin or $\overline{RST}$ with Respect to GND                                                                                                                                                                                                                                                                                                                                        |            | -0.3 | _   | V <sub>IO</sub> + 0.3 | V     |  |

| Maximum Total Current through V <sub>REGIN</sub> or GND                                                                                                                                                                                                                                                                                                                                                    |            |      | _   | 500                   | mA    |  |

| Maximum Output Current Sunk by $\overline{RST}$ or any Port Pin                                                                                                                                                                                                                                                                                                                                            |            |      |     | 100                   | mA    |  |

| Maximum Output Current Sourced by any Port Pin                                                                                                                                                                                                                                                                                                                                                             |            | —    | _   | 100                   | mA    |  |

| Note: Stresses outside of the range of the "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions outside of those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. |            |      |     |                       |       |  |

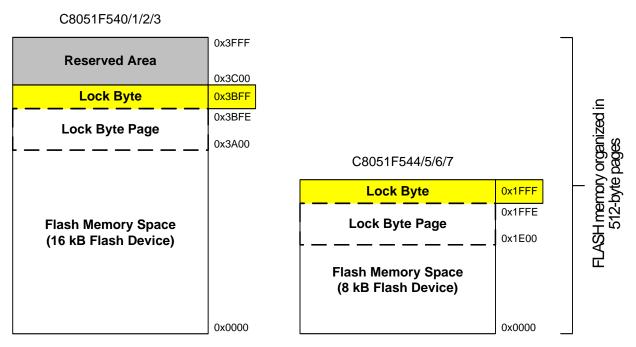

Figure 11.2. Flash Program Memory Map

## 11.1.1. MOVX Instruction and Program Memory

The MOVX instruction in an 8051 device is typically used to access external data memory. On the C8051F54x devices, the MOVX instruction is normally used to read and write on-chip XRAM, but can be re-configured to write and erase on-chip Flash memory space. MOVC instructions are always used to read Flash memory, while MOVX write instructions are used to erase and write Flash. This Flash access feature provides a mechanism for the C8051F54x to update program code and use the program memory space for non-volatile data storage. Refer to Section "14. Flash Memory" on page 117 for further details.

## 11.2. Data Memory

The C8051F54x devices include 1280 bytes of RAM data memory. 256 bytes of this memory is mapped into the internal RAM space of the 8051. The other 1024 bytes of this memory is on-chip "external" memory. The data memory map is shown in Figure 11.1 for reference.

#### 11.2.1. Internal RAM

There are 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The lower 128 bytes of data memory are used for general purpose registers and scratch pad memory. Either direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00 through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight byte-wide registers. The next 16 bytes, locations 0x20 through 0x2F, may either be addressed as bytes or as 128 bit locations accessible with the direct addressing mode.

The upper 128 bytes of data memory are accessible only by indirect addressing. This region occupies the same address space as the Special Function Registers (SFR) but is physically separate from the SFR space. The addressing mode used by an instruction when accessing locations above 0x7F determines whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F access the upper 128 bytes of data memory organization of the C8051F54x.

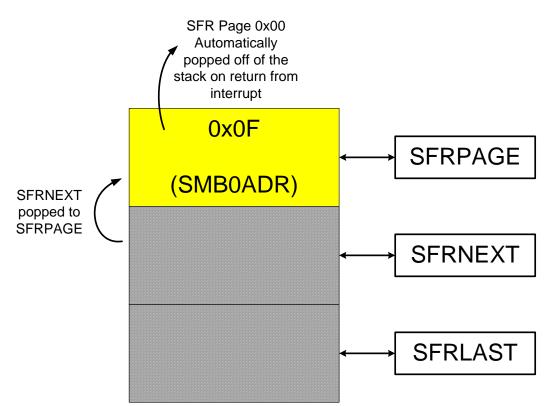

Figure 12.6. SFR Page Stack Upon Return From SPI0 Interrupt

In the example above, all three bytes in the SFR Page Stack are accessible via the SFRPAGE, SFRNEXT, and SFRLAST special function registers. If the stack is altered while servicing an interrupt, it is possible to return to a different SFR Page upon interrupt exit than selected prior to the interrupt call. Direct access to the SFR Page stack can be useful to enable real-time operating systems to control and manage context switching between multiple tasks.

Push operations on the SFR Page Stack only occur on interrupt service, and pop operations only occur on interrupt exit (execution on the RETI instruction). The automatic switching of the SFRPAGE and operation of the SFR Page Stack as described above can be disabled in software by clearing the SFR Automatic Page Enable Bit (SFRPGEN) in the SFR Page Control Register (SFR0CN). See SFR Definition 12.1.

# Table 12.2. Special Function Registers (Continued)

| SERs are listed in alphabetical order    | All undefined SFR locations are reserved |

|------------------------------------------|------------------------------------------|

| SI INS are listed in alphabetical order. |                                          |

| Register | Address | Description                       | Page |

|----------|---------|-----------------------------------|------|

| PCA0CPH5 | 0xCF    | PCA Capture 5 High                | 268  |

| PCA0CPL0 | 0xFB    | PCA Capture 0 Low                 | 268  |

| PCA0CPL1 | 0xE9    | PCA Capture 1 Low                 | 268  |

| PCA0CPL2 | 0xEB    | PCA Capture 2 Low                 | 268  |

| PCA0CPL3 | 0xED    | PCA Capture 3 Low                 | 268  |

| PCA0CPL4 | 0xFD    | PCA Capture 4 Low                 | 268  |

| PCA0CPL5 | 0xCE    | PCA Capture 5 Low                 | 268  |

| PCA0CPM0 | 0xDA    | PCA Module 0 Mode Register        | 266  |

| PCA0CPM1 | 0xDB    | PCA Module 1 Mode Register        | 266  |

| PCA0CPM2 | 0xDC    | PCA Module 2 Mode Register        | 266  |

| PCA0CPM3 | 0xDD    | PCA Module 3 Mode Register        | 266  |

| PCA0CPM4 | 0xDE    | PCA Module 4 Mode Register        | 266  |

| PCA0CPM5 | 0xDF    | PCA Module 5 Mode Register        | 266  |

| PCA0H    | 0xFA    | PCA Counter High                  | 267  |

| PCA0L    | 0xF9    | PCA Counter Low                   | 267  |

| PCA0MD   | 0xD9    | PCA Mode                          | 264  |

| PCA0PWM  | 0xD9    | PCA PWM Configuration             | 265  |

| PCON     | 0x87    | Power Control                     | 128  |

| PSCTL    | 0x8F    | Program Store R/W Control         | 122  |

| PSW      | 0xD0    | Program Status Word               | 83   |

| REF0CN   | 0xD1    | Voltage Reference Control         | 62   |

| REG0CN   | 0xC9    | Voltage Regulator Control         | 73   |

| RSTSRC   | 0xEF    | Reset Source Configuration/Status | 134  |

| SBCON0   | 0xAB    | UART0 Baud Rate Generator Control | 212  |

| SBRLH0   | 0xAD    | UART0 Baud Rate Reload High Byte  | 213  |

| SBRLL0   | 0xAC    | UART0 Baud Rate Reload Low Byte   | 213  |

| SBUF0    | 0x99    | UART0 Data Buffer                 | 212  |

| SCON0    | 0x98    | UART0 Control                     | 210  |

| SFR0CN   | 0x84    | SFR Page Control                  | 96   |

| SFRLAST  | 0x86    | SFR Stack Last Page               | 99   |

| SFRNEXT  | 0x85    | SFR Stack Next Page               | 98   |

| SFRPAGE  | 0xA7    | SFR Page Select                   | 97   |

| SMB0CF   | 0xC1    | SMBus0 Configuration              | 193  |

| SMB0CN   | 0xC0    | SMBus0 Control                    | 195  |

| SMB0DAT  | 0xC2    | SMBus0 Data                       | 197  |

| SMOD0    | 0xA9    | UART0 Mode                        | 211  |

## **13.2. Interrupt Register Descriptions**

The SFRs used to enable the interrupt sources and set their priority level are described in this section. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

#### 14.1.3. Flash Write Procedure

Flash bytes are programmed by software with the following sequence:

- 1. Disable interrupts (recommended).

- 2. Erase the 512-byte Flash page containing the target location, as described in Section 14.1.2.

- 3. Set the PSWE bit (register PSCTL).

- 4. Clear the PSEE bit (register PSCTL).

- 5. Write the first key code to FLKEY: 0xA5.

- 6. Write the second key code to FLKEY: 0xF1.

- 7. Using the MOVX instruction, write a single data byte to the desired location within the 512-byte sector.

- 8. Clear the PSWE bit.

Steps 5–7 must be repeated for each byte to be written. After Flash writes are complete, PSWE should be cleared so that MOVX instructions do not target program memory.

#### 14.1.4. Flash Write Optimization

The Flash write procedure includes a block write option to optimize the time to perform consecutive byte writes. When block write is enabled by setting the CHBLKW bit (CCH0CN.0), writes to two consecutive bytes in Flash require the same amount of time as a single byte write. This is performed by caching the first byte that is written to Flash and then committing both bytes to Flash when the second byte is written. When block writes are enabled, if the second write does not occur, the first data byte written is not actually written to Flash. Flash bytes with block write enabled are programmed by software with the following sequence:

- 1. Disable interrupts (recommended).

- 2. Erase the 512-byte Flash page containing the target location, as described in Section 14.1.2.

- 3. Set the CHBLKW bit (register CCH0CN).

- 4. Set the PSWE bit (register PSCTL).

- 5. Clear the PSEE bit (register PSCTL).

- 6. Write the first key code to FLKEY: 0xA5.

- 7. Write the second key code to FLKEY: 0xF1.

- 8. Using the MOVX instruction, write the first data byte to the desired location within the 512-byte sector.

- 9. Write the first key code to FLKEY: 0xA5.

- 10. Write the second key code to FLKEY: 0xF1.

- 11. Using the MOVX instruction, write the second data byte to the desired location within the 512-byte sector. The location of the second byte must be the next higher address from the first data byte.

- 12.Clear the PSWE bit.

- 13.Clear the CHBLKW bit.

## 14.4. Flash Write and Erase Guidelines

Any system which contains routines which write or erase Flash memory from software involves some risk that the write or erase routines will execute unintentionally if the CPU is operating outside its specified operating range of  $V_{DD}$ , system clock frequency, or temperature. This accidental execution of Flash modifying code can result in alteration of Flash memory contents causing a system failure that is only recoverable by re-Flashing the code in the device.

The following guidelines are recommended for any system which contains routines which write or erase Flash from code.

#### 14.4.1. $V_{DD}$ Maintenance and the $V_{DD}$ monitor

- 1. If the system power supply is subject to voltage or current "spikes," add sufficient transient protection devices to the power supply to ensure that the supply voltages listed in the Absolute Maximum Ratings table are not exceeded.

- 2. Enable the on-chip V<sub>DD</sub> monitor and enable the V<sub>DD</sub> monitor as a reset source as early in code as possible. This should be the first set of instructions executed after the Reset Vector. For C-based systems, this will involve modifying the startup code added by the C compiler. See your compiler documentation for more details. Make certain that there are no delays in software between enabling the V<sub>DD</sub> monitor and enabling the V<sub>DD</sub> monitor as a reset source. Code examples showing this can be found in "AN201: Writing to Flash from Firmware", available from the Silicon Laboratories web site.

- 3. As an added precaution, explicitly enable the V<sub>DD</sub> monitor and enable the V<sub>DD</sub> monitor as a reset source inside the functions that write and erase Flash memory. The V<sub>DD</sub> monitor enable instructions should be placed just after the instruction to set PSWE to a 1, but before the Flash write or erase operation instruction.

- 4. Make certain that all writes to the RSTSRC (Reset Sources) register use direct assignment operators and explicitly DO NOT use the bit-wise operators (such as AND or OR). For example, "RSTSRC = 0x02" is correct. "RSTSRC |= 0x02" is incorrect.

- 5. Make certain that all writes to the RSTSRC register explicitly set the PORSF bit to a 1. Areas to check are initialization code which enables other reset sources, such as the Missing Clock Detector or Comparator, for example, and instructions which force a Software Reset. A global search on "RSTSRC" can quickly verify this.

#### 14.4.2. PSWE Maintenance

- 1. Reduce the number of places in code where the PSWE bit (b0 in PSCTL) is set to a 1. There should be exactly one routine in code that sets PSWE to a 1 to write Flash bytes and one routine in code that sets PSWE and PSEE both to a 1 to erase Flash pages.

- Minimize the number of variable accesses while PSWE is set to a 1. Handle pointer address updates and loop variable maintenance outside the "PSWE = 1;... PSWE = 0;" area. Code examples showing this can be found in "AN201: Writing to Flash from Firmware" available from the Silicon Laboratories web site.

- 3. Disable interrupts prior to setting PSWE to a 1 and leave them disabled until after PSWE has been reset to '0'. Any interrupts posted during the Flash write or erase operation will be serviced in priority order after the Flash operation has been completed and interrupts have been re-enabled by software.

- Make certain that the Flash write and erase pointer variables are not located in XRAM. See your compiler documentation for instructions regarding how to explicitly locate variables in different memory areas.

- 5. Add address bounds checking to the routines that write or erase Flash memory to ensure that a routine called with an illegal address does not result in modification of the Flash.

# SFR Definition 17.2. OSCICN: Internal Oscillator Control

| Bit   | 7     | 6       | 5       | 4     | 3        | 2 | 1         | 0 |

|-------|-------|---------|---------|-------|----------|---|-----------|---|

| Name  | IOSCE | EN[1:0] | SUSPEND | IFRDY | Reserved |   | IFCN[2:0] |   |

| Туре  | R/W   | R/W     | R/W     | R     | R        |   | R/W       |   |

| Reset | 1     | 1       | 0       | 1     | 0        | 0 | 0         | 0 |

## SFR Address = 0xA1; SFR Page = 0x0F;

| Bit | Name        | Function                                                                                                                                                                            |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | IOSCEN[1:0] | Internal Oscillator Enable Bits.                                                                                                                                                    |

|     |             | 00: Oscillator Disabled.                                                                                                                                                            |

|     |             | 01: Reserved.                                                                                                                                                                       |

|     |             | 10: Reserved.                                                                                                                                                                       |

|     |             | 11: Oscillator enabled in normal mode and disabled in suspend mode.                                                                                                                 |

| 5   | SUSPEND     | Internal Oscillator Suspend Enable Bit.                                                                                                                                             |

|     |             | Setting this bit to logic 1 places the internal oscillator in SUSPEND mode. The inter-<br>nal oscillator resumes operation when one of the SUSPEND mode awakening<br>events occurs. |

| 4   | IFRDY       | Internal Oscillator Frequency Ready Flag.                                                                                                                                           |

|     |             | 0: Internal oscillator is not running at programmed frequency.                                                                                                                      |

|     |             | 1: Internal oscillator is running at programmed frequency.                                                                                                                          |

| 3   | Reserved    | Read = 0b; Write = 0b.                                                                                                                                                              |

| 2:0 | IFCN[2:0]   | Internal Oscillator Frequency Divider Control Bits.                                                                                                                                 |

|     |             | 000: SYSCLK derived from Internal Oscillator divided by 128.                                                                                                                        |

|     |             | 001: SYSCLK derived from Internal Oscillator divided by 64.                                                                                                                         |

|     |             | 010: SYSCLK derived from Internal Oscillator divided by 32.                                                                                                                         |

|     |             | 011: SYSCLK derived from Internal Oscillator divided by 16.                                                                                                                         |

|     |             | 100: SYSCLK derived from Internal Oscillator divided by 8.                                                                                                                          |

|     |             | 101: SYSCLK derived from Internal Oscillator divided by 4.                                                                                                                          |

|     |             | 110: SYSCLK derived from Internal Oscillator divided by 2.                                                                                                                          |

|     |             | 111: SYSCLK derived from Internal Oscillator divided by 1.                                                                                                                          |

## 17.4. External Oscillator Drive Circuit

The external oscillator circuit may drive an external crystal, ceramic resonator, capacitor, or RC network. A CMOS clock may also provide a clock input. For a crystal or ceramic resonator configuration, the crystal/resonator must be wired across the XTAL1 and XTAL2 pins as shown in Option 1 of Figure 17.1. A 10 M $\Omega$  resistor also must be wired across the XTAL2 and XTAL1 pins for the crystal/resonator configuration. In RC, capacitor, or CMOS clock configuration, the clock source should be wired to the XTAL2 pin as shown in Option 2, 3, or 4 of Figure 17.1. The type of external oscillator must be selected in the OSCXCN register, and the frequency control bits (XFCN) must be selected appropriately (see SFR Definition 17.6).

**Important Note on External Oscillator Usage:** Port pins must be configured when using the external oscillator circuit. When the external oscillator drive circuit is enabled in crystal/resonator mode, Port pins P0.2 and P0.3 are used as XTAL1 and XTAL2 respectively. When the external oscillator drive circuit is enabled in capacitor, RC, or CMOS clock mode, Port pin P0.3 is used as XTAL2. The Port I/O Crossbar should be configured to skip the Port pins used by the oscillator circuit; see Section "18.3. Priority Crossbar Decoder" on page 150 for Crossbar configuration. Additionally, when using the external oscillator circuit in crystal/resonator, capacitor, or RC mode, the associated Port pins should be configured as **analog inputs**. In CMOS clock mode, the associated pin should be configured as a **digital input**. See Section "18.4. Port I/O Initialization" on page 152 for details on Port input mode selection.

meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 20.2 shows the minimum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary when SYSCLK is above 10 MHz.

| EXTHOLD                                                                                                                                                                                                                                                                                                          | Minimum SDA Setup Time                                                              | Minimum SDA Hold Time |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------|--|--|--|--|

| 0                                                                                                                                                                                                                                                                                                                | T <sub>low</sub> – 4 system clocks<br>or<br>1 system clock + s/w delay <sup>*</sup> | 3 system clocks       |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                | 11 system clocks                                                                    | 12 system clocks      |  |  |  |  |

| *Note: Setup Time for ACK bit transmissions and the MSB of all data transfers. When using software acknowledgement, the s/w delay occurs between the time SMB0DAT or ACK is written and when SI is cleared. Note that if SI is cleared in the same write that defines the outgoing ACK value, s/w delay is zero. |                                                                                     |                       |  |  |  |  |

Table 20.2. Minimum SDA Setup and Hold Times

With the SMBTOE bit set, Timer 3 should be configured to overflow after 25 ms in order to detect SCL low timeouts (see Section "20.3.4. SCL Low Timeout" on page 189). The SMBus interface will force Timer 3 to reload while SCL is high, and allow Timer 3 to count when SCL is low. The Timer 3 interrupt service routine should be used to reset SMBus communication by disabling and re-enabling the SMBus.

SMBus Free Timeout detection can be enabled by setting the SMBFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 20.4).

# SFR Definition 23.1. CKCON: Clock Control

| Bit   | 7    | 6    | 5    | 4    | 3   | 2   | 1   | 0     |

|-------|------|------|------|------|-----|-----|-----|-------|

| Name  | ТЗМН | T3ML | T2MH | T2ML | T1M | ТОМ | SCA | [1:0] |

| Туре  | R/W  | R/W  | R/W  | R/W  | R/W | R/W | R/  | W     |

| Reset | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0     |

## SFR Address = 0x8E; SFR Page = All Pages

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                          |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ТЗМН     | Timer 3 High Byte Clock Select.                                                                                                                                                                                                                                                                                   |

|     |          | Selects the clock supplied to the Timer 3 high byte (split 8-bit timer mode only).<br>0: Timer 3 high byte uses the clock defined by the T3XCLK bit in TMR3CN.<br>1: Timer 3 high byte uses the system clock.                                                                                                     |

| 6   | T3ML     | Timer 3 Low Byte Clock Select.                                                                                                                                                                                                                                                                                    |

|     |          | <ul> <li>Selects the clock supplied to Timer 3. Selects the clock supplied to the lower 8-bit timer in split 8-bit timer mode.</li> <li>0: Timer 3 low byte uses the clock defined by the T3XCLK bit in TMR3CN.</li> <li>1: Timer 3 low byte uses the system clock.</li> </ul>                                    |

| 5   | T2MH     |                                                                                                                                                                                                                                                                                                                   |

| 5   | TZINIT   | <ul> <li>Timer 2 High Byte Clock Select.</li> <li>Selects the clock supplied to the Timer 2 high byte (split 8-bit timer mode only).</li> <li>0: Timer 2 high byte uses the clock defined by the T2XCLK bit in TMR2CN.</li> <li>1: Timer 2 high byte uses the system clock.</li> </ul>                            |

| 4   | T2ML     | Timer 2 Low Byte Clock Select.                                                                                                                                                                                                                                                                                    |

|     |          | <ul> <li>Selects the clock supplied to Timer 2. If Timer 2 is configured in split 8-bit timer mode, this bit selects the clock supplied to the lower 8-bit timer.</li> <li>0: Timer 2 low byte uses the clock defined by the T2XCLK bit in TMR2CN.</li> <li>1: Timer 2 low byte uses the system clock.</li> </ul> |

| 3   | T1       | Timer 1 Clock Select.                                                                                                                                                                                                                                                                                             |

|     |          | Selects the clock source supplied to Timer 1. Ignored when C/T1 is set to 1.<br>0: Timer 1 uses the clock defined by the prescale bits SCA[1:0].<br>1: Timer 1 uses the system clock.                                                                                                                             |

| 2   | Т0       | Timer 0 Clock Select.                                                                                                                                                                                                                                                                                             |

|     |          | Selects the clock source supplied to Timer 0. Ignored when C/T0 is set to 1.<br>0: Counter/Timer 0 uses the clock defined by the prescale bits SCA[1:0].<br>1: Counter/Timer 0 uses the system clock.                                                                                                             |

| 1:0 | SCA[1:0] | Timer 0/1 Prescale Bits.                                                                                                                                                                                                                                                                                          |

|     |          | These bits control the Timer 0/1 Clock Prescaler:<br>00: System clock divided by 12<br>01: System clock divided by 4<br>10: System clock divided by 48<br>11: External clock divided by 8 (synchronized with the system clock)                                                                                    |

# C8051F54x

This mode allows software to determine the external oscillator frequency when an RC network or capacitor is used to generate the clock source.

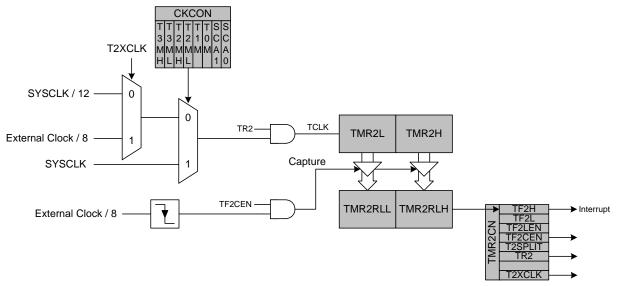

Figure 23.6. Timer 2 External Oscillator Capture Mode Block Diagram

# SFR Definition 23.13. TMR3CN: Timer 3 Control

| Bit   | 7    | 6    | 5      | 4      | 3       | 2   | 1 | 0      |

|-------|------|------|--------|--------|---------|-----|---|--------|

| Name  | TF3H | TF3L | TF3LEN | TF3CEN | T3SPLIT | TR3 |   | T3XCLK |

| Туре  | R/W  | R/W  | R/W    | R/W    | R/W     | R/W | R | R/W    |

| Reset | 0    | 0    | 0      | 0      | 0       | 0   | 0 | 0      |

## SFR Address = 0x91; SFR Page = 0x00

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF3H    | <b>Timer 3 High Byte Overflow Flag.</b><br>Set by hardware when the Timer 3 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 3 overflows from 0xFFFF to 0x0000. When the Timer 3 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 3                                                                                                                                                                                  |

|     |         | interrupt service routine. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6   | TF3L    | Timer 3 Low Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |         | Set by hardware when the Timer 3 low byte overflows from 0xFF to 0x00. TF3L will be set when the low byte overflows regardless of the Timer 3 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                            |

| 5   | TF3LEN  | Timer 3 Low Byte Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |         | When set to 1, this bit enables Timer 3 Low Byte interrupts. If Timer 3 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 3 overflows.                                                                                                                                                                                                                                                                                                       |

| 4   | TF3CEN  | Timer 3 Capture Mode Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |         | 0: Timer 3 Capture Mode is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |         | 1: Timer 3 Capture Mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3   | T3SPLIT | Timer 3 Split Mode Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |         | When this bit is set, Timer 3 operates as two 8-bit timers with auto-reload.<br>0: Timer 3 operates in 16-bit auto-reload mode.                                                                                                                                                                                                                                                                                                                                                   |

|     |         | 1: Timer 3 operates as two 8-bit auto-reload timers.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2   | TR3     | Timer 3 Run Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |         | Timer 3 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables TMR3H only; TMR3L is always enabled in split mode.                                                                                                                                                                                                                                                                                                                                          |

| 1   | Unused  | Read = 0b; Write = Don't Care                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0   | T3XCLK  | Timer 3 External Clock Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |         | This bit selects the external clock source for Timer 3. If Timer 3 is in 8-bit mode, this bit selects the external oscillator clock source for both timer bytes. However, the Timer 3 Clock Select bits (T3MH and T3ML in register CKCON) may still be used to select between the external clock and the system clock for either timer.<br>0: Timer 3 clock is the system clock divided by 12.<br>1: Timer 3 clock is the external clock divided by 8 (synchronized with SYSCLK). |

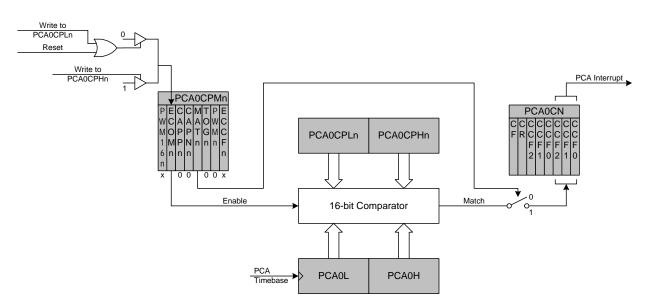

Figure 24.5. PCA Software Timer Mode Diagram

#### 24.3.3. High-Speed Output Mode

In High-Speed Output mode, a module's associated CEXn pin is toggled each time a match occurs between the PCA Counter and the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the TOGn, MATn, and ECOMn bits in the PCA0CPMn register enables the High-Speed Output mode. If ECOMn is cleared, the associated pin will retain its state, and not toggle on the next match event.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

# C2 Register Definition 25.4. FPCTL: C2 Flash Programming Control

| Bit   | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------------|---|---|---|---|---|---|---|

| Name  | FPCTL[7:0]      |   |   |   |   |   |   |   |

| Туре  | R/W             |   |   |   |   |   |   |   |

| Reset | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |   |

C2 Address: 0x02

| Bit | Name       | Function                                                                                                                                                                                                                                                                    |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | FPCTL[7:0] | Flash Programming Control Register.                                                                                                                                                                                                                                         |

|     |            | This register is used to enable Flash programming via the C2 interface. To enable C2 Flash programming, the following codes must be written in order: 0x02, 0x01. Note that once C2 Flash programming is enabled, a system reset must be issued to resume normal operation. |

# C2 Register Definition 25.5. FPDAT: C2 Flash Programming Data

| Bit   | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------------|---|---|---|---|---|---|---|

| Name  | FPDAT[7:0]      |   |   |   |   |   |   |   |

| Туре  | R/W             |   |   |   |   |   |   |   |

| Reset | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |   |

C2 Address: 0xB4

| Bit | Name       | Function                                                                                                                   |                   |  |  |  |  |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|--|--|

| 7:0 | FPDAT[7:0] | C2 Flash Programming Data Register.                                                                                        |                   |  |  |  |  |

|     |            | This register is used to pass Flash commands, addresses, and data during C2 Fla accesses. Valid commands are listed below. |                   |  |  |  |  |

|     |            | Code Command                                                                                                               |                   |  |  |  |  |

|     |            | 0x06                                                                                                                       | Flash Block Read  |  |  |  |  |

|     |            | 0x07                                                                                                                       | Flash Block Write |  |  |  |  |

|     |            | 0x08 Flash Page Erase                                                                                                      |                   |  |  |  |  |

|     |            | 0x03                                                                                                                       | Device Erase      |  |  |  |  |