Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                          |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 50MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 25                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 1.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                    |

| Data Converters            | A/D 25x12b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                              |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 32-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 32-QFN (5x5)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f545-imr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **List of Tables**

| Table 2.1. Product Selection Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Table 3.1. Pin Definitions for the C8051F54x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 18                                                                                                                                           |

| Table 4.1. QFP-32 Package Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23                                                                                                                                           |

| Table 4.2. QFP-32 Landing Diagram Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24                                                                                                                                           |

| Table 4.3. QFN-32 Package Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                              |

| Table 4.4. QFN-32 Landing Diagram Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 26                                                                                                                                           |

| Table 4.5. QFN-24 Package Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                              |

| Table 4.6. QFN-24 Landing Diagram Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                              |

| Table 6.1. Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                              |

| Table 6.2. Global Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                              |

| Table 6.3. Port I/O DC Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                              |

| Table 6.4. Reset Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                              |

| Table 6.5. Flash Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                              |

| Table 6.6. Internal High-Frequency Oscillator Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                              |

| Table 6.7. Clock Multiplier Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |

| Table 6.8. Voltage Regulator Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                              |

| Table 6.9. ADC0 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                              |

| Table 6.10. Temperature Sensor Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 56                                                                                                                                           |

| Table 6.11. Voltage Reference Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56                                                                                                                                           |

| Table 6.12. Comparator 0 and Comparator 1 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                              |

| Table 10.1. CIP-51 Instruction Set Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11                                                                                                                                           |

| Table 12.1. Special Function Register (SFR) Memory Map for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 100                                                                                                                                          |

| Pages 0x0 and 0xF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                              |

| Table 12.2. Special Function Registers         Table 12.1. Interrupt Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                              |

| Table 13.1. Interrupt Summary         Table 14.1. Elash Security Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                              |

| Table 14.1. Flash Security Summary       *         Table 18.1. Port I/O Assignment for Analog Functions       *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1/0                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                              |

| Table 18.2. Port I/O Assignment for Digital Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 149                                                                                                                                          |

| Table 18.2. Port I/O Assignment for Digital Functions       Table 18.3. Port I/O Assignment for External Digital Event Capture Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 149<br>150                                                                                                                                   |

| Table 18.2. Port I/O Assignment for Digital Functions       7         Table 18.3. Port I/O Assignment for External Digital Event Capture Functions       7         Table 19.1. Baud Rate Calculation Variable Ranges       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 149<br>150<br>171                                                                                                                            |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 149<br>150<br>171<br>173                                                                                                                     |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters Examples                                                                                                                                                                                                                                                                                                                                                                                                                                   | 149<br>150<br>171<br>173<br>174                                                                                                              |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)                                                                                                                                                                                                                                                                                                                                                                                | 149<br>150<br>171<br>173<br>174<br>179                                                                                                       |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source Selection                                                                                                                                                                                                                                                                                                                                        | 149<br>150<br>171<br>173<br>174<br>179<br>191                                                                                                |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source SelectionTable 20.2. Minimum SDA Setup and Hold Times                                                                                                                                                                                                                                                                                            | 149<br>150<br>171<br>173<br>174<br>179<br>191<br>192                                                                                         |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source SelectionTable 20.2. Minimum SDA Setup and Hold TimesTable 20.3. Sources for Hardware Changes to SMB0CN                                                                                                                                                                                                                                          | 149<br>150<br>171<br>173<br>174<br>179<br>191<br>192<br>196                                                                                  |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source SelectionTable 20.2. Minimum SDA Setup and Hold TimesTable 20.4. SMBus Status Decoding                                                                                                                                                                                                                                                           | <ul> <li>149</li> <li>150</li> <li>171</li> <li>173</li> <li>174</li> <li>179</li> <li>191</li> <li>192</li> <li>196</li> <li>202</li> </ul> |

| Table 18.2. Port I/O Assignment for Digital Functions       Table 18.3. Port I/O Assignment for External Digital Event Capture Functions         Table 19.1. Baud Rate Calculation Variable Ranges       Table 19.1. Baud Rate Calculation Variable Ranges         Table 19.2. Manual Baud Rate Parameters Examples       Table 19.3. Autobaud Parameters Examples         Table 19.4. LIN Registers* (Indirectly Addressable)       Table 20.1. SMBus Clock Source Selection         Table 20.2. Minimum SDA Setup and Hold Times       Table 20.3. Sources for Hardware Changes to SMB0CN         Table 20.4. SMBus Status Decoding       Table 21.1. Baud Rate Generator Settings for Standard Baud Rates | 149<br>150<br>171<br>173<br>174<br>179<br>191<br>192<br>196<br>202<br>206                                                                    |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source SelectionTable 20.2. Minimum SDA Setup and Hold TimesTable 20.3. Sources for Hardware Changes to SMB0CNTable 20.4. SMBus Status DecodingTable 21.1. Baud Rate Generator Settings for Standard Baud RatesTable 22.1. SPI Slave Timing Parameters                                                                                                  | 149<br>150<br>171<br>173<br>174<br>179<br>191<br>192<br>196<br>202<br>206<br>226                                                             |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source SelectionTable 20.2. Minimum SDA Setup and Hold TimesTable 20.3. Sources for Hardware Changes to SMB0CNTable 20.4. SMBus Status DecodingTable 21.1. Baud Rate Generator Settings for Standard Baud RatesTable 22.1. SPI Slave Timing ParametersTable 24.1. PCA Timebase Input Options                                                            | 149<br>150<br>171<br>173<br>174<br>179<br>191<br>192<br>196<br>202<br>206<br>226                                                             |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source SelectionTable 20.2. Minimum SDA Setup and Hold TimesTable 20.3. Sources for Hardware Changes to SMB0CNTable 20.4. SMBus Status DecodingTable 21.1. Baud Rate Generator Settings for Standard Baud RatesTable 22.1. SPI Slave Timing ParametersTable 24.1. PCA Timebase Input OptionsTable 24.2. PCA0CPM and PCA0PWM Bit Settings for            | 149<br>150<br>171<br>173<br>174<br>179<br>191<br>192<br>196<br>202<br>206<br>226<br>226                                                      |

| Table 18.2. Port I/O Assignment for Digital FunctionsTable 18.3. Port I/O Assignment for External Digital Event Capture FunctionsTable 19.1. Baud Rate Calculation Variable RangesTable 19.2. Manual Baud Rate Parameters ExamplesTable 19.3. Autobaud Parameters ExamplesTable 19.4. LIN Registers* (Indirectly Addressable)Table 20.1. SMBus Clock Source SelectionTable 20.2. Minimum SDA Setup and Hold TimesTable 20.3. Sources for Hardware Changes to SMB0CNTable 20.4. SMBus Status DecodingTable 21.1. Baud Rate Generator Settings for Standard Baud RatesTable 22.1. SPI Slave Timing ParametersTable 24.1. PCA Timebase Input Options                                                            | 149<br>150<br>171<br>173<br>174<br>179<br>191<br>192<br>202<br>206<br>226<br>250<br>250                                                      |

# List of Registers

|     |               |        | DC0CF: ADC0 Configuration                       |    |

|-----|---------------|--------|-------------------------------------------------|----|

|     |               |        | DC0H: ADC0 Data Word MSB                        |    |

| SFR | Definition &  | 5.6. A | DC0L: ADC0 Data Word LSB                        | 41 |

| SFR | Definition \$ | 5.7. A | DC0CN: ADC0 Control                             | 42 |

| SFR | Definition &  | 5.8. A | DC0TK: ADC0 Tracking Mode Select                | 43 |

| SFR | Definition &  | 5.9. A | DC0GTH: ADC0 Greater-Than Data High Byte        | 44 |

| SFR | Definition &  | 5.10.  | ADC0GTL: ADC0 Greater-Than Data Low Byte        | 44 |

| SFR | Definition \$ | 5.11.  | ADC0LTH: ADC0 Less-Than Data High Byte          | 45 |

| SFR | Definition &  | 5.12.  | ADC0LTL: ADC0 Less-Than Data Low Byte           | 45 |

|     |               |        | DC0MX: ADC0 Channel Select                      |    |

|     |               |        | EF0CN: Reference Control                        |    |

| SFR | Definition 8  | 8.1. C | PT0CN: Comparator0 Control                      | 65 |

|     |               |        | PT0MD: Comparator0 Mode Selection               |    |

| SFR | Definition 8  | 8.3. C | PT1CN: Comparator1 Control                      | 67 |

|     |               |        | PT1MD: Comparator1 Mode Selection               |    |

|     |               |        | PT0MX: Comparator0 MUX Selection                |    |

|     |               |        | PT1MX: Comparator1 MUX Selection                |    |

|     |               |        | EG0CN: Regulator Control                        |    |

|     |               |        | DPL: Data Pointer Low Byte                      |    |

|     |               |        | DPH: Data Pointer High Byte                     |    |

|     |               |        | SP: Stack Pointer                               |    |

|     |               |        | ACC: Accumulator                                |    |

|     |               |        | B: B Register                                   |    |

|     |               |        | PSW: Program Status Word                        |    |

|     |               |        | SNn: Serial Number n                            |    |

|     |               |        | EMIOCN: External Memory Interface Control       |    |

|     |               |        | SFR0CN: SFR Page Control                        |    |

|     |               |        | SFRPAGE: SFR Page                               |    |

|     |               |        | SFRNEXT: SFR Next                               |    |

|     |               |        | SFRLAST: SFR Last                               |    |

|     |               |        | IE: Interrupt Enable1                           |    |

|     |               |        | IP: Interrupt Priority1                         |    |

|     |               |        | EIE1: Extended Interrupt Enable 11              |    |

|     |               |        | EIP1: Extended Interrupt Priority 11            |    |

|     |               |        | EIE2: Extended Interrupt Enable 21              |    |

|     |               |        | EIP2: Extended Interrupt Priority Enabled 2     |    |

|     |               |        | IT01CF: INT0/INT1 Configuration                 |    |

|     |               |        | PSCTL: Program Store R/W Control                |    |

|     |               |        | FLKEY: Flash Lock and Key1                      |    |

|     |               |        | FLSCL: Flash Scale 1<br>CCH0CN: Cache Control 1 |    |

|     |               |        |                                                 |    |

|     |               |        | ONESHOT: Flash Oneshot Period1                  |    |

| SFK | Definition '  | 15.1.  | PCON: Power Control 1                           | 28 |

## SFR Definition 5.4. ADC0CF: ADC0 Configuration

| Bit   | 7 | 6         | 5          | 4     | 3       | 2      | 1 | 0 |

|-------|---|-----------|------------|-------|---------|--------|---|---|

| Name  |   |           | AD0SC[4:0] | ADORI | PT[1:0] | GAINEN |   |   |

| Туре  |   |           | R/W        | R/W   | R/W     | R/W    |   |   |

| Reset | 1 | 1 1 1 1 0 |            |       |         |        |   |   |

SFR Address = 0xBC; SFR Page = 0x00

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7:3 | AD0SC[4:0] | ADC0 SAR Conversion Clock Period Bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|     |            | SAR Conversion clock is derived from system clock by the following equation, where<br><i>AD0SC</i> refers to the 5-bit value held in bits AD0SC4–0. SAR Conversion clock<br>requirements are given in the ADC specification table<br>BURSTEN = 0: FCLK is the current system clock<br>BURSTEN = 1: FCLK is a maximum of 30 MHz, independent of the current system<br>clock                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|     |            | $AD0SC = \frac{FCLK}{CLK_{SAR}} - 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|     |            | Note: Round up the result of the calculation for AD0SC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| 2:1 | A0RPT[1:0] | ADC0 Repeat Count                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|     |            | Controls the number of conversions taken and accumulated between ADC0 End of<br>Conversion (ADCINT) and ADC0 Window Comparator (ADCWINT) interrupts. A con-<br>vert start is required for each conversion unless Burst Mode is enabled. In Burst<br>Mode, a single convert start can initiate multiple self-timed conversions. Results in<br>both modes are accumulated in the ADC0H:ADC0L register. When AD0RPT1–0 are<br>set to a value other than '00', the AD0LJST bit in the ADC0CN register must be<br>set to '0' (right justified).<br>00: 1 conversion is performed.<br>01: 4 conversions are performed and accumulated.<br>10: 8 conversions are performed and accumulated.<br>11: 16 conversions are performed and accumulated. |  |  |  |  |  |  |  |

| 0   | GAINEN     | Gain Enable Bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|     |            | Controls the gain programming. Refer to Section "5.3. Selectable Gain" on page 35 for information about using this bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

## SFR Definition 7.1. REF0CN: Reference Control

| Bit   | 7 | 6 | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|---|---|-------|-------|-------|-------|-------|-------|

| Name  |   |   | ZTCEN | REFLV | REFSL | TEMPE | BIASE | REFBE |

| Туре  | R | R | R     | R     | R/W   | R/W   | R/W   | R/W   |

| Reset | 0 | 0 | 0     | 0     | 0     | 0     | 0     | 0     |

#### SFR Address = 0xD1; SFR Page = 0x00

| Bit | Name   | Function                                                                                                                                                                                                                                                           |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused | Read = 00b; Write = don't care.                                                                                                                                                                                                                                    |

| 5   | ZTCEN  | <ul> <li>Zero Temperature Coefficient Bias Enable Bit.</li> <li>This bit must be set to 1b before entering oscillator suspend mode.</li> <li>0: ZeroTC Bias Generator automatically enabled when required.</li> <li>1: ZeroTC Bias Generator forced on.</li> </ul> |

| 4   | REFLV  | Voltage Reference Output Level Select.This bit selects the output voltage level for the internal voltage reference0: Internal voltage reference set to 1.5 V.1: Internal voltage reference set to 2.20 V.                                                          |

| 3   | REFSL  | Voltage Reference Select.This bit selects the ADCs voltage reference.0: V <sub>REF</sub> pin used as voltage reference.1: V <sub>DD</sub> used as voltage reference.                                                                                               |

| 2   | TEMPE  | Temperature Sensor Enable Bit.0: Internal Temperature Sensor off.1: Internal Temperature Sensor on.                                                                                                                                                                |

| 1   | BIASE  | Internal Analog Bias Generator Enable Bit.<br>0: Internal Bias Generator off.<br>1: Internal Bias Generator on.                                                                                                                                                    |

| 0   | REFBE  | <ul> <li>On-chip Reference Buffer Enable Bit.</li> <li>0: On-chip Reference Buffer off.</li> <li>1: On-chip Reference Buffer on. Internal voltage reference driven on the V<sub>REF</sub> pin.</li> </ul>                                                          |

## SFR Definition 8.2. CPT0MD: Comparator0 Mode Selection

| Bit   | 7 | 6 | 5      | 4      | 3 | 2 | 1          | 0 |

|-------|---|---|--------|--------|---|---|------------|---|

| Name  |   |   | CP0RIE | CP0FIE |   |   | CP0MD[1:0] |   |

| Туре  | R | R | R/W    | R/W    | R | R | R/W        |   |

| Reset | 0 | 0 | 0      | 0      | 0 | 0 | 1          | 0 |

### SFR Address = 0x9B; SFR Page = 0x00

| Bit | Name       | Function                                                                                                                                                                                                                                                            |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused     | Read = 00b, Write = Don't Care.                                                                                                                                                                                                                                     |

| 5   | CP0RIE     | Comparator0 Rising-Edge Interrupt Enable.<br>0: Comparator0 Rising-edge interrupt disabled.<br>1: Comparator0 Rising-edge interrupt enabled.                                                                                                                        |

| 4   | CP0FIE     | Comparator0 Falling-Edge Interrupt Enable.<br>0: Comparator0 Falling-edge interrupt disabled.<br>1: Comparator0 Falling-edge interrupt enabled.                                                                                                                     |

| 3:2 | Unused     | Read = 00b, Write = don't care.                                                                                                                                                                                                                                     |

| 1:0 | CP0MD[1:0] | Comparator0 Mode Select.<br>These bits affect the response time and power consumption for Comparator0.<br>00: Mode 0 (Fastest Response Time, Highest Power Consumption)<br>01: Mode 1<br>10: Mode 2<br>11: Mode 3 (Slowest Response Time, Lowest Power Consumption) |

## SFR Definition 8.3. CPT1CN: Comparator1 Control

| Bit   | 7     | 6      | 5      | 4      | 3           | 2 | 1           | 0 |

|-------|-------|--------|--------|--------|-------------|---|-------------|---|

| Name  | CP1EN | CP1OUT | CP1RIF | CP1FIF | CP1HYP[1:0] |   | CP1HYN[1:0] |   |

| Туре  | R/W   | R      | R/W    | R/W    | R/W         |   | R/          | W |

| Reset | 0     | 0      | 0      | 0      | 0           | 0 | 0           | 0 |

### SFR Address = 0x9D; SFR Page = 0x00

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | CP1EN       | Comparator1 Enable Bit.                                                       |

|     |             | 0: Comparator1 Disabled.                                                      |

|     |             | 1: Comparator1 Enabled.                                                       |

| 6   | CP1OUT      | Comparator1 Output State Flag.                                                |

|     |             | 0: Voltage on CP1+ < CP1–.                                                    |

|     |             | 1: Voltage on CP1+ > CP1                                                      |

| 5   | CP1RIF      | Comparator1 Rising-Edge Flag. Must be cleared by software.                    |

|     |             | 0: No Comparator1 Rising Edge has occurred since this flag was last cleared.  |

|     |             | 1: Comparator1 Rising Edge has occurred.                                      |

| 4   | CP1FIF      | Comparator1 Falling-Edge Flag. Must be cleared by software.                   |

|     |             | 0: No Comparator1 Falling-Edge has occurred since this flag was last cleared. |

|     |             | 1: Comparator1 Falling-Edge has occurred.                                     |

| 3:2 | CP1HYP[1:0] | Comparator1 Positive Hysteresis Control Bits.                                 |

|     |             | 00: Positive Hysteresis Disabled.                                             |

|     |             | 01: Positive Hysteresis = 5 mV.                                               |

|     |             | 10: Positive Hysteresis = 10 mV.                                              |

|     |             | 11: Positive Hysteresis = 20 mV.                                              |

| 1:0 | CP1HYN[1:0] | Comparator1 Negative Hysteresis Control Bits.                                 |

|     |             | 00: Negative Hysteresis Disabled.                                             |

|     |             | 01: Negative Hysteresis = 5 mV.                                               |

|     |             | 10: Negative Hysteresis = 10 mV.                                              |

|     |             | 11: Negative Hysteresis = 20 mV.                                              |

## 10. CIP-51 Microcontroller

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. The CIP-51 also includes on-chip debug hardware (see description in Section 25), and interfaces directly with the analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 10.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 50 MIPS Peak Throughput with 50 MHz Clock

- 0 to 50 MHz Clock Frequency

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

### 10.1. Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute, and usually have a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

## **11. Memory Organization**

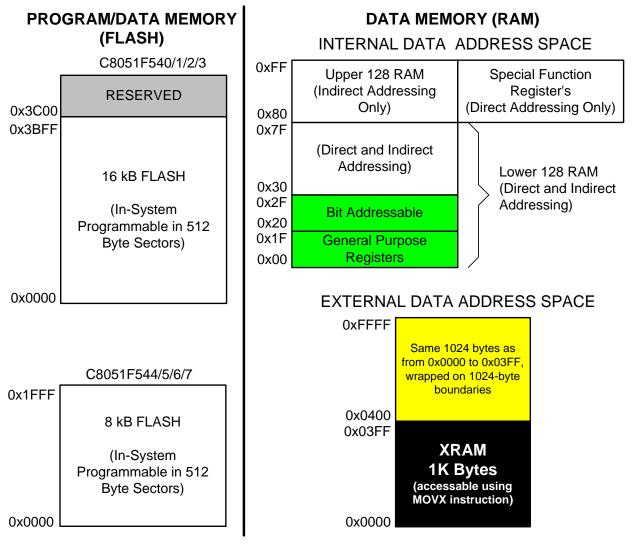

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. The memory organization is shown in Figure 11.1

Figure 11.1. C8051F54x Memory Map

### 11.1. Program Memory

The CIP-51 core has a 64 kB program memory space. The C8051F54x devices implement 16 kB or 8 kB of this program memory space as in-system, re-programmable Flash memory, organized in a contiguous block from addresses 0x0000 to 0x3FFF in 16 kB devices and addresses 0x0000 to 0x1FFF in 8 kB devices. The address 0x3BFF in 16 kB devices and 0x1FFF in 8 kB devices serves as the security lock byte for the device. Addresses above 0x3BFF are reserved in the 16 kB devices.

#### **13.1.1. Interrupt Priorities**

Each interrupt source can be individually programmed to one of two priority levels: low or high. A low priority interrupt service routine can be preempted by a high priority interrupt. A high priority interrupt cannot be preempted. Each interrupt has an associated interrupt priority bit in an SFR (IE, EIP1, or EIP2) used to configure its priority level. Low priority is the default. If two interrupts are recognized simultaneously, the interrupt with the higher priority is serviced first. If both interrupts have the same priority level, a fixed priority order is used to arbitrate, given in Table 13.1.

#### 13.1.2. Interrupt Latency

Interrupt response time depends on the state of the CPU when the interrupt occurs. Pending interrupts are sampled and priority decoded each system clock cycle. Therefore, the fastest possible response time is 5 system clock cycles: 1 clock cycle to detect the interrupt and 4 clock cycles to complete the LCALL to the ISR. If an interrupt is pending when a RETI is executed, a single instruction is executed before an LCALL is made to service the pending interrupt. Therefore, the maximum response time for an interrupt (when no other interrupt is currently being serviced or the new interrupt is of greater priority) occurs when the CPU is performing an RETI instruction followed by a DIV as the next instruction. In this case, the response time is 18 system clock cycles: 1 clock cycle to detect the interrupt, 5 clock cycles to execute the RETI, 8 clock cycles to complete the DIV instruction and 4 clock cycles to execute the LCALL to the ISR. If the CPU is executing an ISR for an interrupt with equal or higher priority, the new interrupt will not be serviced until the current ISR completes, including the RETI and following instruction.

## SFR Definition 17.6. OSCXCN: External Oscillator Control

| Bit   | 7      | 6   | 5          | 4  | 3 | 2         | 1   | 0 |

|-------|--------|-----|------------|----|---|-----------|-----|---|

| Name  | XTLVLD | ×   | (OSCMD[2:0 | )] |   | XFCN[2:0] |     |   |

| Туре  | R      | R/W |            |    | R |           | R/W |   |

| Reset | 0      | 0   | 0          | 0  | 0 | 0 0       |     |   |

### SFR Address = 0x9F; SFR Page = 0x0F;

| Bit | Name        |          |                                               | Function                                  |                 |

|-----|-------------|----------|-----------------------------------------------|-------------------------------------------|-----------------|

| 7   | XTLVLD      | Crystal  | Oscillator Valid Flag.                        |                                           |                 |

|     |             | •        | nly when XOSCMD = 11                          |                                           |                 |

|     |             | -        | al Oscillator is unused of                    | •                                         |                 |

|     |             | -        | al Oscillator is running a                    |                                           |                 |

| 6:4 | XOSCMD[2:0] |          | I Oscillator Mode Sele                        |                                           |                 |

|     |             |          | ternal Oscillator circuit of                  |                                           |                 |

|     |             |          | ternal CMOS Clock Mod<br>ernal CMOS Clock Mod |                                           |                 |

|     |             |          | Oscillator Mode.                              |                                           |                 |

|     |             | 101: Ca  | pacitor Oscillator Mode.                      |                                           |                 |

|     |             | -        | stal Oscillator Mode.                         |                                           |                 |

|     |             | 111: Cry | stal Oscillator Mode with                     | n divide by 2 stage.                      |                 |

| 3   | Unused      | Read =   | 0b; Write =0b                                 |                                           |                 |

| 2:0 | XFCN[2:0]   | Externa  | I Oscillator Frequency                        | Control Bits.                             |                 |

|     |             |          | •                                             | quency for Crystal or RC                  | mode.           |

|     |             | Set acc  | ording to the desired K F                     | actor for C mode.                         |                 |

|     |             | XFCN     | Crystal Mode                                  | RC Mode                                   | C Mode          |

|     |             | 000      | f ≤ 32 kHz                                    | f ≤ 25 kHz                                | K Factor = 0.87 |

|     |             | 001      | 32 kHz < f ≤ 84 kHz                           | 25 kHz < f ≤ 50 kHz                       | K Factor = 2.6  |

|     |             | 010      | 84 kHz < f ≤ 225 kHz                          | 50 kHz < f ≤ 100 kHz                      | K Factor = 7.7  |

|     |             | 011      | 225 kHz < f ≤ 590 kHz                         | 100 kHz < f ≤ 200 kHz                     | K Factor = 22   |

|     |             | 100      | 590 kHz < f ≤ 1.5 MHz                         | 200 kHz < f ≤ 400 kHz                     | K Factor = 65   |

|     |             | 101      | $1.5 \text{ MHz} < f \le 4 \text{ MHz}$       | 400 kHz < f ≤ 800 kHz                     | K Factor = 180  |

|     |             | 110      | $4 \text{ MHz} < f \le 10 \text{ MHz}$        | 800 kHz < f ≤ 1.6 MHz                     | K Factor = 664  |

|     |             | 111      | $10 \text{ MHz} < f \le 30 \text{ MHz}$       | $1.6 \text{ MHz} < f \le 3.2 \text{ MHz}$ | K Factor = 1590 |

| Port                           |      |        |         | P                 | 0                 |                  |   |   |   |   |                 | P                | 1    |                  |       |      |       |        |                 | P                | 2         |                  |   |   | P3                   |

|--------------------------------|------|--------|---------|-------------------|-------------------|------------------|---|---|---|---|-----------------|------------------|------|------------------|-------|------|-------|--------|-----------------|------------------|-----------|------------------|---|---|----------------------|

| Special<br>Function<br>Signals | VREF | CNVSTR | XTAL1   | XTAL2             |                   |                  |   |   |   |   |                 |                  |      | ALE              | /RD   | /WR  |       |        | Pź              | 2.2-1            |           |                  |   |   | available on<br>ages |

| PIN I/O                        | 0    | 1      | 2       | 3                 | 4                 | 5                | 6 | 7 | 0 | 1 | 2               | 3                | 4    | 5                | 6     | 7    | 0     | 1      | 2               | 3                | 4         | 5                | 6 | 7 | 0                    |

| UART_TX                        |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| UART_RX                        |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| SCK                            |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| MISO                           |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| MOSI                           |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| NSS                            |      |        |         |                   |                   |                  |   |   |   |   |                 | *NS              | S Is | onl              | y pir | nneo | d out | t in 4 | 4-wir           | e S              | PIN       | lode             |   |   |                      |

| SDA                            |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| SCL                            |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| CP0                            |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| CP0A                           |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| CP1                            |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| CP1A                           |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| SYSCLK                         |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| CEX0                           |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| CEX1                           |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| CEX2                           |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| CEX3                           |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| CEX4                           |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| CEX5                           |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| ECI                            |      |        |         |                   |                   |                  |   |   | l |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| то                             |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| T1                             |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| LIN_TX                         |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

| LIN_RX                         |      |        |         |                   |                   |                  |   |   |   |   |                 |                  |      |                  |       |      |       |        |                 |                  |           |                  |   |   |                      |

|                                | 0    | 1      | 1<br>P( | 0<br>0 <b>5</b> K | 0<br>I <b>P[0</b> | 1<br>: <b>7]</b> | 0 | 0 | 0 | 0 | 0<br><b>P</b> 1 | 0<br>I <b>SK</b> |      | 0<br>: <b>7]</b> | 0     | 0    | 0     | 0      | 0<br><b>P</b> 2 | 0<br>2 <b>SK</b> | 0<br>IP[0 | 0<br>: <b>7]</b> | 0 | 0 | 0<br>P3SKIP[0]       |

Figure 18.4. Crossbar Priority Decoder in Example Configuration

### 18.4. Port I/O Initialization

Port I/O initialization consists of the following steps:

- 1. Select the input mode (analog or digital) for all Port pins, using the Port Input Mode register (PnMDIN).

- 2. Select the output mode (open-drain or push-pull) for all Port pins, using the Port Output Mode register (PnMDOUT).

- 3. Select any pins to be skipped by the I/O Crossbar using the Port Skip registers (PnSKIP).

- 4. Assign Port pins to desired peripherals.

- 5. Enable the Crossbar (XBARE = 1).